### THAT 1200, 1203, 1206

# **FEATURES**

- High CMRR: typ. 90 dB at 60 Hz

- Extremely high common-mode input impedance

Maintains balance under real-world conditions

- Transformer-like performance in an IC

- Excellent audio performance

Wide bandwidth: typ. > 22 MHz

- High slew rate: typ. 12 V/us

- Low distortion: typ. 0.0005 % THD

- Low noise: typ. -106 dBu

- Several gains: 0 dB, -3 dB, & -6 dB

**APPLICATIONS**

- Balanced Audio Line Receivers

- Instrumentation Amplifiers

- Differential Amplifiers

- Transformer Front-End Replacements

- ADC Front-Ends

# **Description**

The THAT 1200-series InGenius balanced line receivers overcome a serious limitation of conventional balanced input stages: poor common mode rejection in real-world applications. While conventional input stages measure well in the lab and perform well on paper, they fail to live up to their CMRR specs when fed from even slightly unbalanced source impedances — a common situation in almost any pro sound environment. This is because conventional stages have low common-mode input impedance, which interacts with imbalances in source impedance to unbalance common-mode signals, making them indistinguishable from desired, balanced signals. Developed by Bill Whitlock of Jensen Transformers, the patented InGenius input stage uses clever bootstrapping to raise its common-mode input impedance into the megohm range without the noise penalty from the obvious solution of using high-valued resistors. Like transformers, InGenius line receivers maintain their high CMRR over a wide range of source impedance imbalances — even when fed from single-ended sources. But unlike transformers, these wide bandwidth solid state devices offer dc-coupling, low distortion, and transparent sound in a small package at reasonable cost.

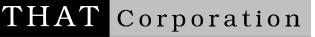

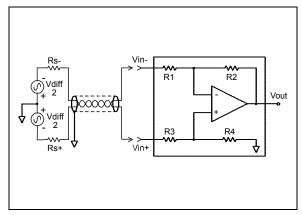

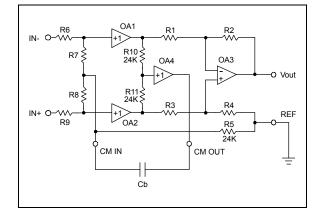

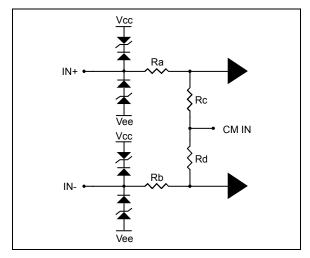

Figure 1. THAT 1200-series equivalent circuit diagram

| Pin Name | DIP Pin | SO Pin |

|----------|---------|--------|

| Ref      | 1       | 1      |

| In-      | 2       | 2      |

| In+      | 3       | 3      |

| Vee      | 4       | 4      |

| CM In    | 5       | 5      |

| Vout     | 6       | 6      |

| Vcc      | 7       | 7      |

| CM Out   | 8       | 8      |

Table 1. 1200-series pin assignments

| Gain  | Plastic DIP | Plastic SO |

|-------|-------------|------------|

| 0 dB  | 1200P       | 1200S      |

| -3 dB | 1203P       | 1203S      |

| -6 dB | 1206P       | 1206S      |

Table 2. Ordering information

Protected under U.S. Patent Numbers, 5,568,561 and 6,160,451. Additional patents pending. InGenius is a registered trademark of THAT Corporation. Page 2 of 12

| <u>Absolute Maximum Ratings (T<sub>A</sub> = 25°C)</u> |                |                                        |                            |             |  |  |

|--------------------------------------------------------|----------------|----------------------------------------|----------------------------|-------------|--|--|

| Positive Supply Voltage ( $V_{CC}$ )                   | +20 V          | Output Short-Circuit D                 | uration (t <sub>SH</sub> ) | Continuous  |  |  |

| Negative Supply Voltage ( $V_{EE}$ )                   | -20 V          | Operating Temperatur                   | e Range (T <sub>OP</sub> ) | 0 to +85 °C |  |  |

| Storage Temperature Range $(T_{ST})$                   | -40 to +125 °C | Junction Temperature (T <sub>J</sub> ) |                            | 125 °C      |  |  |

|                                                        | THAT1200       | THAT1203                               | THAT1206                   |             |  |  |

| Input Voltage (V <sub>IN</sub> )                       | ± 25 V         | ± 31 V                                 | ± 31 V                     |             |  |  |

| Electrical Characteristics <sup>2,3,4</sup> |                                            |                                                        |                      |              |       |          |

|---------------------------------------------|--------------------------------------------|--------------------------------------------------------|----------------------|--------------|-------|----------|

| Parameter                                   | Symbol                                     | Conditions                                             | Min                  | Тур          | Max   | Units    |

| Supply Current                              | I <sub>cc</sub>                            | No Signal                                              | —                    | 4.7          | 8.0   | mA       |

| Supply Voltage                              | $V_{CC}, V_{EE}$                           |                                                        | ±3                   |              | ±18   | V        |

| Input Bias Current                          | Ι <sub>Β</sub>                             | No signal; Either input connected to GND               | _                    | 700          | 1,400 | nA       |

| Input Offset Current                        | I <sub>B-OFF</sub>                         | No signal                                              |                      |              | ±300  | nA       |

| Input Voltage Range                         | V <sub>IN-CM</sub><br>V <sub>IN-DIFF</sub> | Common mode<br>Differential (equal and opposite swing) | ±12.5                | ±13.0        | _     | V        |

|                                             |                                            | THAT 1200                                              | 21.0                 | 21.5         |       | dBu      |

|                                             |                                            | THAT 1203                                              | 24.0                 | 24.5         | _     | dBu      |

|                                             |                                            | THAT 1206                                              | 24.0                 | 24.5         | —     | dBu      |

| Input Impedance                             |                                            | Differential                                           |                      | 48.0         |       | kΩ       |

|                                             | Z <sub>IN-CM</sub>                         | Common mode                                            | W                    | ith bootstra | ар    |          |

|                                             |                                            | 60 Hz<br>20 kHz                                        |                      | 10.0<br>3.2  |       | ΜΩ<br>ΜΩ |

| Common Mode Rejection Ratio                 | CMRR <sub>1</sub>                          | Matched source impedances; $V_{CM} = \pm 2$            | 10V                  |              |       |          |

|                                             |                                            | DC                                                     | 70                   | 90           | _     | dB       |

|                                             |                                            | 60 Hz                                                  | 70                   | 90           |       | dB       |

|                                             |                                            | 20 kHz                                                 |                      | 85           | —     | dB       |

| Common Mode Rejection Ratio <sup>5</sup>    |                                            | 10 $\Omega$ unmatched source impedances;               | $V_{CM} = \pm 10$    |              |       | 10       |

|                                             |                                            | DC                                                     | —                    | 90           | —     | dB       |

|                                             |                                            | 60 Hz<br>20 kHz                                        | _                    | 90<br>85     | _     | dB<br>dB |

| Common Mode Rejection Ratio                 | CMRR <sub>2</sub>                          | 600Ω unmatched source impedances;                      | V <sub>CM</sub> = +1 | 0V           |       |          |

|                                             | <b>0</b>                                   | 60 Hz                                                  |                      | 70           |       | dB       |

|                                             |                                            | 20 kHz                                                 | _                    | 65           | —     | dB       |

| Power Supply Rejection Ratio <sup>6</sup>   | PSRR                                       | At 60 Hz, with $V_{CC}$ = - $V_{EE}$                   |                      |              |       |          |

|                                             |                                            | THAT 1200                                              | —                    | 82           | _     | dB       |

|                                             |                                            | THAT 1203                                              | —                    | 80           |       | dB       |

|                                             |                                            | THAT 1206                                              | —                    | 80           | _     | dB       |

<sup>1</sup> All specifications subject to change without notice.

<sup>2</sup> Unless otherwise noted,  $T_A = 25^{\circ}$ C,  $V_{CC} = +15$ V,  $V_{EE} = -15$ V

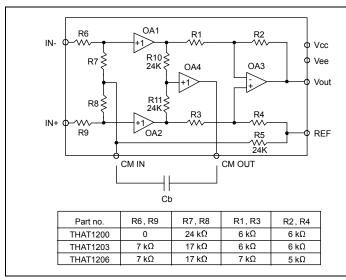

<sup>3</sup> See test circuit in Figure 2.

$^{4}$  0 dBu = 0.775 Vrms

$^5$  Per IEC Standard 60268-3 for testing CMRR of balanced inputs.

<sup>6</sup> Defined with respect to differential gain.

| Electrical Characteristics (con't) |                                                                     |                                                                                    |                |                      |           |                   |

|------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------|----------------------|-----------|-------------------|

| Parameter                          | Symbol                                                              | Conditions                                                                         | Min.           | Тур.                 | Max       | Units             |

| Total Harmonic Distortion          | THD                                                                 | $V_{IN\_DIFF}$ = 10 dBu; BW = 20 kHz; f<br>R <sub>L</sub> = 2 kΩ                   | = 1 kHz<br>    | 0.0005               | _         | %                 |

| Output Noise                       | e <sub>N(OUT)</sub>                                                 | BW = 20 kHz<br>THAT1200<br>THAT1203<br>THAT1206                                    |                | -105<br>-104<br>-106 |           | dBu<br>dBu<br>dBu |

| Output Offset Voltage              | V <sub>OFF</sub>                                                    | No signal                                                                          | _              | _                    | ±10       | mV                |

| Slew Rate                          | SR                                                                  | $R_L$ = 2 k $\Omega$ ; $C_L$ = 300 pF                                              | 7              | 12                   | _         | V/µs              |

| Small Signal Bandwidth             | BW <sub>-3dB</sub>                                                  | R <sub>L</sub> = 10 kΩ; C <sub>L</sub> = 10 pF<br>THAT1200<br>THAT1203<br>THAT1206 |                | 22<br>27<br>34       |           | MHz<br>MHz<br>MHz |

| Output Gain Error                  | G <sub>ER(OUT)</sub>                                                | f = 1 kHz, $R_L$ = 2 k $\Omega$                                                    | _              | 0                    | ±0.05     | dB                |

| Maximum Output Voltage             | Vo                                                                  | At max differential input<br>THAT1200<br>THAT1203<br>THAT1206                      | 21<br>21<br>18 | 21.5<br>21.5<br>18.5 |           | dBu<br>dBu<br>dBu |

| Output Short Circuit Current       | I <sub>SC</sub><br>I <sub>CMSC</sub>                                | $R_L = R_{Lcm} = 0 \Omega$<br>At CM output                                         | _              | ±25<br>±10           | _         | mA<br>mA          |

| Minimum Resistive Load             | $\begin{array}{c} R_{\text{Lmin}} \\ R_{\text{LCMmin}} \end{array}$ | At CM output                                                                       | 2<br>10        | _                    | _         | kΩ<br>kΩ          |

| Maximum Capacitive Load            | $\begin{array}{c} C_{\text{Lmax}} \\ C_{\text{LCmax}} \end{array}$  | At CM output                                                                       | _              | _                    | 300<br>50 | pF<br>pF          |

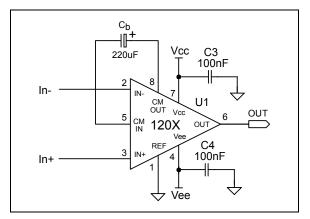

Figure 2. THAT 1200-series test circuit

# **Theory of Operation**

The InGenius concept was invented to overcome limitations of traditional approaches to active input stage design. Because of the many misconceptions about the performance of conventional input stages, and to set the stage for discussion of InGenius, we will begin by discussing conventional approaches.

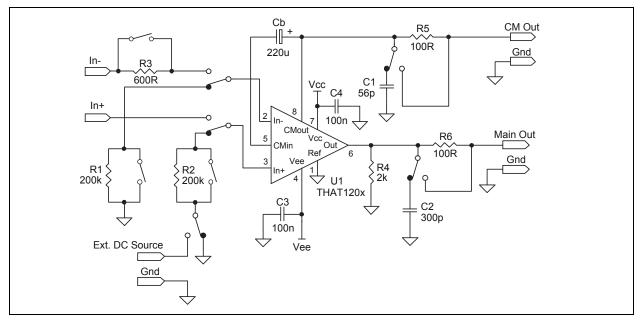

Figure 3. Basic differential amplifier

## **Traditional Balanced Input Stages**

The typical balanced input stage used in most professional audio products is shown in Figure 3. It amplifies differential signals but rejects common-mode interference based on the precision of the match in the ratios  $R_2/R_1$  and  $R_4/R_3$ . In this circuit,

$$V_{out} = (V_{in+}) \left( 1 + \frac{R_2}{R_1} \right) \frac{R_4}{R_3 + R_4} + (V_{in-}) \frac{R_2}{R_1}$$

In modern integrated circuits (such as the THAT 1240 series), these resistor ratios are trimmed (usually with a laser) to extreme precision, resulting in typical match of  $\pm 0.005\%$ . So, one can assume that  $R_2/R_1=R_4/R_3$ . In this case, we can simplify this formula as follows:

$$V_{out} = (V_{in+}) \left( 1 + \frac{R_2}{R_1} \right) \left( \frac{R_2}{R_1} \right) \frac{1}{\left( 1 + \frac{R_2}{R_1} \right)} + (V_{in-}) \frac{R_2}{R_1}$$

vielding:

yielding:

$$V_{out} = [(V_{in+}) + (V_{in-})]\frac{R_2}{R_1}$$

#### CMRR Depends on Resistor Match

When driven from a theoretical, true voltage source, the precisely matched resistor ratios deliver extremely high CMRR. With perfectly matched resistor ratios, for  $V_{in+}=-V_{in-}$  (this corresponds to a pure differential input signal), then  $V_{out}=2^*(V_{in+})^*R_2/R_1$ . On the other hand, for  $V_{in+}=V_{in-}$  (this corresponds to a pure common mode signal), then  $V_{out}=0$ . This produces an infinite common

mode rejection ratio. Any difference between the ratios  $R_2/R_1$  and  $R_4/R_3$  will lead to less than perfect CMRR.

#### The Impact of Driving Source Impedance

However, in the real world, where sources have nonzero output impedance, the situation is more complicated. Figure 4 shows the equivalent circuit of a real-world differential application. In this case, the source connected to the differential receiver has source impedance of  $R_{\rm s+}$  in the positive side, and  $R_{\rm s-}$  in the negative side. Because these two resistive elements are in series with each other, they only serve to attenuate the signal  $V_{\rm diff}$  relative to the input impedance of the differential stage. Even if they ( $R_{\rm s+}$  and  $R_{\rm s-}$ ) are mismatched, this attenuation is the only consequence of non-zero source impedance.

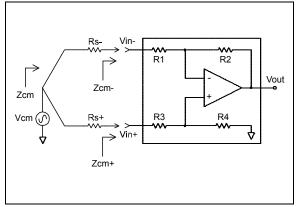

Figure 4. Basic differential amplifier showing mismatched source impedances

However, the same cannot be said for common-mode interference. Common-mode signals appear in phase between the two input terminals. For in-phase signals, the source impedances can have significant impact. As shown in Figure 5, this is because each leg of the source impedance forms a voltage divider when it interacts with the input impedance of its respective input of the differential amplifier.

Because the + and - inputs of the operational amplifier are forced by feedback to maintain the same voltage, the individual common-mode impedances of each side of the differential stage are:

$$Z_{CM+}=R_3+R_4$$

; and

$$Z_{CM-}=\frac{R_3+R_4}{\frac{R_3}{R_1}}\,.$$

So long as  $R_1=R_3$ , these impedances, which form a load for common-mode input signals, are identical. (This is why, in discrete applications, it is wise to choose  $R_1=R_3$ , and why, in all integrated applications, these resistors are chosen to be the same value.)

The total common-mode input impedance is

THAT Corporation; 45 Summer Street; Milford, Massachusetts 01757-1656; USA Tel: +1 508 478-9200; Fax +1 508 478-0990; Web: <u>www.thatcorp.com</u> Copyright © 2017, THAT Corporation; All rights reserved.

$$Z_{CM} = \frac{R_3 + R_4}{1 + \frac{R_3}{R_1}}$$

#### Source Impedance Mismatches Ruin Good CMRR

Even if  $R_1$  perfectly matches  $R_3$ , any mismatch in the source impedances  $R_{S^+}$  and  $R_{S^-}$  will cause the voltage dividers to be unequal between the two input legs. This means that  $V_{\rm in}$  and  $V_{\rm in+}$  in Figure 5 are no longer equal to each other. Essentially, imbalances in the two source impedances convert the common mode signal to a differential signal, which will not be rejected by the input stage no matter how high its theoretical CMRR is.

To see how this plays out in practice, consider the case of a typical unity-gain conventional balanced line receiver with common-mode input impedance of 10 k $\Omega$ . In such cases, a source impedance imbalance of only 10  $\Omega$  can degrade CMRR to no better than 66 dB. A 10  $\Omega$  mismatch could be caused by tolerances in coupling capacitors or output build-out resistors. The situation becomes much worse when a conventional balanced line receiver is driven from an unbalanced source, where it is common to use at least 100  $\Omega$  in series with the output for protection. (With a 100  $\Omega$  unbalanced output impedance, and a 10 k $\Omega$  common-mode input impedance no more than 46 dB CMRR!)

Figure 5. Basic differential amplifier driven by common-mode input signal

The best solution to this problem is to increase the line receiver's common-mode input impedance enough to minimize the unbalancing effect of the voltage divider. Preferably, this means achieving input impedances on the order of several megohms. However, in a conventional differential amplifier, this requires high-value resistances in the circuit. High resistance carries with it a high noise penalty, making this straightforward approach impractical for quality audio devices.

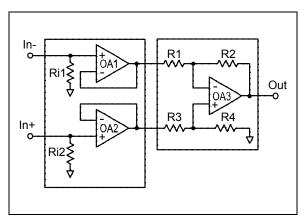

#### Instrumentation Amplifiers

Some designers prefer the more elaborate approach of an instrumentation amplifier, as shown in Figure 6. In this circuit, it is possible to raise the input impedance (both common-mode and differential) of the stage because the load seen by the source is decoupled by  $OA_1$

Figure 6. Instrumentational amplifier

and OA<sub>2</sub> from the balanced stage (OA<sub>3</sub> along with R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>, and R<sub>4</sub>). In this circuit,  $Z_{CM-} = R_{11}$ , and  $Z_{CM+} = R_{12}$ .

To retain 90 dB CMRR in the face of a 10  $\Omega$  mismatch in source impedance would require  $R_{i1}$  and  $R_{i2}$  to be  $>317~k\Omega$ . Of course, any difference in the values of  $R_{i1}$  and  $R_{i2}$  themselves would further unbalance common mode signals as well, so these resistors would ideally be trimmed just like the resistors in the single opamp stage of Figure 3. Unfortunately for this approach, it is difficult and expensive to make precision trimmed resistors with such high values.

Furthermore, since the input bias current for amplifiers  $OA_1$  and  $OA_2$  flows through these resistors, their input currents must be extremely low if they are not to cause significant offsets. Practically, this necessitates using FET input stages for  $OA_1$  and  $OA_2$ . While FETs may be a viable alternative, it is difficult to achieve with them the low noise performance of modern bipolar input stages.

### Transformer Input Stages

From the point of view of common mode input impedance, as well as that of electrical isolation, a transformer in front of the first active input stage is really the best possible solution. Transformers are the only approach of which we are aware that provides true electrical isolation with reasonable fidelity. Furthermore, their common-mode input impedance is easily extremely high (tens of Megohms), and almost completely decoupled from their differential input impedance.

But, transformers have many other limitations. They do not offer dc coupling, and suffer from saturation at low frequencies unless they are physically large and carefully made. Again, unless they are carefully made (which usually equates to high cost), they introduce phase shift at high audio-band frequencies. Furthermore, they tend to be big and heavy and pick up external magnetic fields, sometimes making it difficult to locate transformer-coupled equipment to avoid interference.

Fortunately, audio equipment usually does not require true electrical isolation. In most cases, transformers out-perform conventional input stages only because they excel at rejecting common-mode signals in realworld situations. It is no coincidence that the InGenius concept was developed by an individual responsible for manufacturing the world's premier line of audio transformers (Bill Whitlock, of Jensen Transformers). Bill's InGenius technology offers all the advantages of solid state input stages, including dc coupling, negligible phase shift from dc to beyond the edge of the audio band, and vanishingly low distortion, along with the primary advantage of a transformer: extremely high common-mode input impedance.

#### The InGenius Approach

The InGenius approach to balanced line receivers uses bootstrapping to increase common mode input impedance. With bootstrapping, we first create a replica of the common mode signal, and then feed it back appropriately to the inputs to increase the input impedance. Because doing this in a differential amplifier involves additional complications, it is useful to review the bootstrap concept with a single-ended design first. We will then show how Bill Whitlock applied that concept to the differential case.

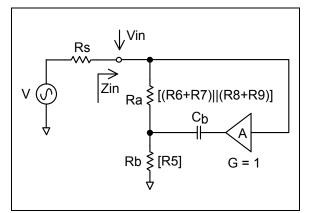

#### Bootstrapping: a Simple Single-Ended Example

To illustrate the concept behind bootstrapping, consider the the single-ended bootstrap shown in Figure 7. In this circuit, amplifier A is configured for unity gain, and can be considered to have infinite input impedance. Capacitor  $C_b$  blocks DC, so at DC, the input impedance,  $Z_{\rm in}$ , is  $R_a+R_b$ .

However, for high-frequency AC signals (where  $C_{\rm b}$  is effectively a short), amplifier A drives the junction of  $R_{\rm a}$  and  $R_{\rm b}$  through  $C_{\rm b}$  to nearly the same AC voltage as  $V_{\rm in}$ . As a result, practically no AC current flows through  $R_{\rm a}$ . This effectively increases the input impedance seen at  $Z_{\rm in}$ .

Figure 7. Single-ended bootstrap topology

The cutoff frequency of the filter formed by  $C_b$  and  $R_a/R_b$  is determined primarily by the values of  $C_b$  and  $R_b.$  (Because so little current flows in  $R_a$ , it is hardly involved in this filter.)

Input impedance  $Z_{in}$ ; at frequency f, is described the following equation:

$$Z_{in} = (R_a + R_b) \sqrt{\frac{1 + \left(\frac{f}{f_n}\right)^2}{1 + (1 - G)^2 \left(\frac{f}{f_D}\right)^2}}$$

where

$$f_n = \frac{1}{2\pi \left(\frac{R_a \cdot R_b}{R_a + R_b}\right) C_b}$$

$$f_D = \frac{1}{2\pi R_b C_b}$$

For example, if  $R_a$  and  $R_b$  are 10 k $\Omega$  each,  $Z_{inDC}$  is 20 k $\Omega$ . This resistance provides a DC path for amplifier bias current. At higher frequencies, the bootstrap greatly increases the input impedance, limited ultimately by how close gain G approaches unity.

Figure 8. THAT 1200-series equivalent circuit diagram

## Common Mode Bootstrapping in an Instrumentation Amplifier = InGenius

The genius behind Bill Whitlock's invention was to recognize that in an instrumentation amplifier, it is possible bootstrap the common-mode signal to increase common-mode input impedance. This is the concept behind the InGenius patents. To see how this works, refer to the circuit of Figure 8.

Like Figure 1, Figure 8 shows an equivalent circuit for the THAT 1200-series ICs.  $OA_1$  and  $OA_2$  are high input-impedance, unity-gain buffers feeding differential amplifier  $OA_3$  in an instrumentation amplifier configuration.  $OA_4$  is a third high input-impedance, unity-gain buffer. With  $R_{10} = R_{11}$ , the voltage at the input to  $OA_4$ will be equal to the common-mode component of the input signal.  $OA_4$  buffers this signal, and feeds it back to both inputs via capacitor  $C_b$  and resistors  $R_6$ ,  $R_7$ ,  $R_8$ ,  $R_9$ , and  $R_5$ . Note that in most applications  $C_b$  is large (>100  $\mu$ f). Similarly to the single-ended application above, at high frequencies, the junction of  $R_7$ ,  $R_8$ , and  $R_5$  is driven through  $C_b$  to the same potential as the common-mode input voltage. Hence at high frequencies, no commonmode current flows in resistors  $R_6$  and  $R_7$ , or  $R_8$  and  $R_9$ . Since  $OA_1$  and  $OA_2$  have high input impedances, this effectively raises the input impedance seen at In+ and In- to high-frequency common-mode signals. Of course, for differential signals, the input impedance is  $(R_6+R_7+R_8+R_9)$ . And, at DC, the common-mode input impedance is:

$$Z_{CM_{DC}} = \frac{(R_6 + R_7)(R_8 + R_9)}{R_6 + R_7 + R_8 + R_9} + R5.$$

DC bias for  $\text{OA}_1$  and  $\text{OA}_2$  is supplied through  $R_5$  and either  $R_7$  or  $R_8.$

For the resistor values chosen for the 1200-series ICs, the input impedances  $Z_{\rm CM}$  and  $Z_{\rm diff}$ , are described by the following equations:

$$Z_{CM_{DC}} = 36 \ k\Omega$$

$$Z_{CM}(f) = 36 \ k\Omega \sqrt{\frac{1 + (50240 \cdot C_b \cdot f)^2}{1 + (73.8 \cdot C_b \cdot f)^2}}; \text{ where f is the}$$

input frequency,

$$Z_{diff} = R_6 + R_7 + R_8 + R_9 = 48 \ k\Omega$$

In order to get the most out of this topology,  $OA_1$  and  $OA_2$  must have high input impedance, and the commonmode gain loop ( $OA_1$ ,  $OA_2$ ,  $R_{10}/R_{11}$  and  $OA_4$ ) must have precisely unity gain over the entire audio band. THAT Corporation integrated the InGenius parts in our complimentary dielectric isolation process because it offers very high bandwidth and low noise for relatively high-voltage applications like this one. This in turn makes it easier to meet these requirements, and typically, results in a maximum mid-audio-band  $Z_{\rm inCM}$  of  $>20~M\Omega.$

Because  $OA_1$  and  $OA_2$  isolate the differential amplifier ( $OA_3$ ) from the effects of external source impedances, the CMRR of  $OA_3$  and its associated four resistors is determined solely by  $OA_3$ 's bandwidth and the precision of the resistor matching. Our complimentary DI process contributes to high bandwidth in  $OA_3$ , and we use on-chip laser trimming to ensure extremely good matching, as well as precise gain, in those four thin-film resistors.

Finally, perhaps the most common interfering signals that a good differential line receiver must reject is the power-line frequency: usually either 50 or 60 Hz and its harmonics. So, it is essential that the common-mode input impedance remain high down to 50 Hz, and up to at least to the edge of the audio band. While THAT's process and circuit design ensure the latter condition, the value of  $C_b$  will determine how low in frequency the common-mode input impedance will be increased. To maintain at least a 1 M $\Omega$  common-mode input impedance,  $C_b$  should be at least 10  $\mu$ f.

It is possible to solve the above equation for  $C_b$  in terms of the desired  $Z_{\rm CM}$  for a specific frequency. However, reaching a general closed-form solution is difficult and results in a very complex formula. The relatively simple formula below takes advantage of some approximation, and yields good results for  $Z_{\rm CM}$  between about 100 k $\Omega$  and 10 M $\Omega$ .

$$C_b \cong 0.553 \times 10^{-3} \ \frac{Z_{CM}}{f}$$

For additional information refer to:

Balanced Lines in Audio Systems - Fact, Fiction, and Transformers, by Bill Whitlock, AES 97th Convention, Preprint 3917, October 1994

<u>A New Balanced Audio Input Circuit for Maximum Common-mode Rejection in Real-world Environments</u>, by Bill Whitlock, AES 101st Convention Preprint 4372, 1996.

Common-Mode to Differential-Mode Conversion in Shielded Twisted-pair Cables (Shield-Current-Induced Noise), by Jim Brown & Bill Whitlock, AES 114th Convention, Preprint 5747, February 2003

# **Applications**

## **Basic Application**

At its most basic, THAT's 1200-series ICs need very little external support circuitry. As is shown in the basic application circuit of Figure 9, they need little else beyond positive and negative power supplies, a ground reference, the common-mode bootstrap capacitor, and input and output connections. Because all 1200-series ICs are wide bandwidth parts, it is important to provide bypass capacitors for both positive and negative supply rails within an inch or so of the part. Sharing supply bypass capacitors across several 1200-series ICs separated by several inches on a circuit board (as, for example, along the back panel of a multi-input product) is not recommended<sup>1</sup>.

Figure 9. Basic 1200-series application circuit

### Bootstrap Capacitor Polarity

Because the bootstrap capacitor,  $C_{\rm b}$ , will usually be large (see formula on page 7) an electrolytic or tantalum capacitor is a logical choice. Such capacitors are normally polarized, though non-polarized types are available at higher cost. For the 1200-series, a polarized capacitor is appropriate, with the positive end towards  $CM_{out}$  (pin 8), because of the direction of the input bias currents for internal opamps  $OA_1$  and  $OA_2$ . Furthermore, because  $C_{\rm b}$  never has much voltage across it<sup>2</sup>, it only needs to support a few tens of mV. Therefore, we recommend a 220 uF, 3 V capacitor for  $C_{\rm b}$ .

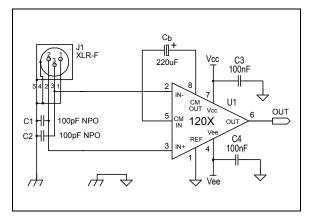

#### RFI Protection<sup>3</sup>

As an input stage, the 1200-series ICs are susceptible to RF interference (RFI). Like most semiconductor devices, if high levels of RF are permitted at the input pins of 1200-series parts, they may become nonlinear, which can create audible interference. Therefore, it is good design practice to filter unwanted high frequencies at the input of any product in which the 1200-series is used. The objective should be to prevent RF from entering the chassis, and especially, the circuit board of any devices using a 1200-series part. Generally, this is done by means of small capacitors connected between the signal inputs and chassis ground, with the capacitors located as physically close to the input connectors as possible.

Figure 10 shows a basic, simple application circuit to protect the 1200 series against RFI. For many nondemanding applications, this simple circuit will suffice.  $C_1$  and  $C_2$  provide RF bypassing from pins 2 and 3 of the input XLR connector to chassis ground and the XLR connector's shell (which are tied together, ideally only at the XLR connector jack). RF picked up on the cable plugged into the connector is conducted by  $C_1$  and  $C_2$  to chassis ground. Chassis ground should connect to circuit ground through one (and only one) low inductance path, usually at the power supply connector.

Figure 10. THAT 1200 application with simple RFI protection

<sup>1</sup> Lack of proper bypassing may not cause obvious problems at normal temperatures. We have seen cases in which improperly bypassed parts begin to draw excessive current when operated near their upper temperature limits. Close bypassing prevents this phenomenon.

<sup>2</sup> Even at DC, C<sub>b</sub> will not see much voltage, because the signal at the junction of  $R_7$  and  $R_8$  should closely equal the signal at the junction of  $R_{10}$  and  $R_{11}$ . With OA<sub>4</sub> configured for unity gain, both ends of C<sub>b</sub> see the same signal - AC and DC - except for offsets.

<sup>3</sup> Good practice to protect inputs against RFI is a science in itself, and it is beyond the scope of this data sheet to provide more than a glimpse of this complex subject. We refer the interested reader to:

Considerations in Grounding and Shielding Audio Devices, by Stephan R. Macatee, JAES Volume 43, Number 6, pp.472-483; June 1995;

Noise Susceptibility in Analog and Digital Signal Processing Systems, by Neil A. Muncy, AES 97th Convention Preprint 3930, October 1996.

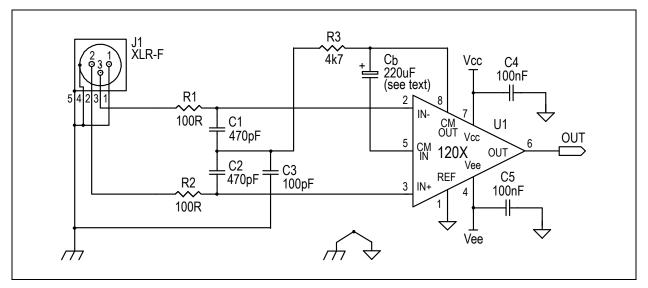

Figure 11. THAT1200 application with recommended RFI protection.

The one drawback to this circuit is that  $C_1$  and  $C_2$  will reduce the common-mode input impedance of the 1200 stage to  $\sim 80~k\Omega$  at 20 kHz. Of course, this figure drops by a factor of ten for each decade increase in frequency. Additionally, any mismatch between these capacitors can unbalance an interfering common-mode signal, thus making it impossible for the 1200 to reject it.

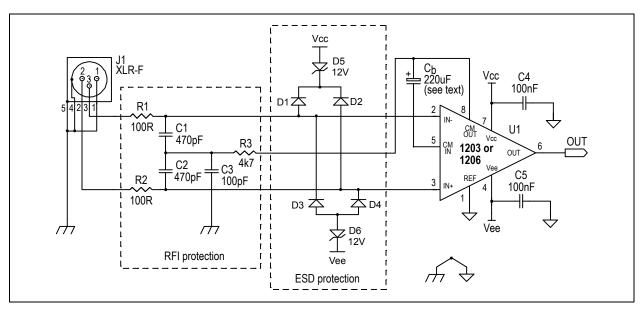

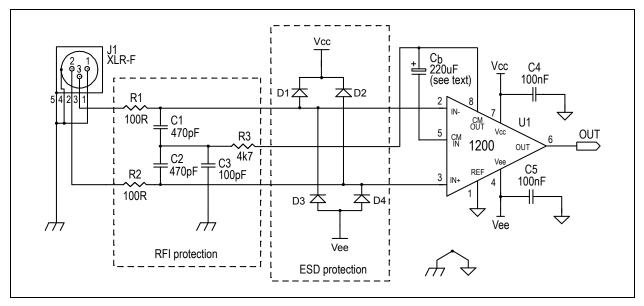

Figure 11 shows a more elaborate and robust circuit for RFI protection. While more complex, it offers many improvements over the circuit of Figure 10 that make it worth serious consideration. First, C1 and C2 are larger than their counterparts in Figure 10. Because they are in series with each other, they act as a 235 pf capacitor across pins 2 and 3 of the XLR. This allows them to be effective at lower frequencies. Second, because their center point ties to chassis ground through a smaller, common capacitor ( $C_3$ , 100 pf), any mismatch in their values has less tendency to unbalance common-mode signals compared to the circuit of Figure 10<sup>4</sup>. Third, because they are driven from the common-mode bootstrap circuit through R<sub>3</sub>, this common point gains the benefit of the InGenius common-mode bootstrapping. Finally,  $R_1$  and  $R_2$  provide some additional buildout impedance against which the bypass capacitors can work, making the entire network more effective against strong RF signals.

### **ESD** Protection

All the 1200-series ICs contain internal over-voltage protection circuitry for the two input pins. Figure 12 is an equivalent circuit of this circuitry.

These internal diodes provide modest protection against common low-voltage ESD incidents. However, because these ICs are intended to be connected directly

<sup>4</sup> For additional information refer to the publications listed on page 7.

to the input connectors of electronic products, they may be exposed to unpredictable and possibly extreme ESD. For ESD to affect the InGenius operation, it would have to be conducted via one of the input connectors to the device itself. This is unlikely, but certainly not impossible. Not surprisingly, THAT's own testing indicates that repeated exposure to high levels (above 1 kV) of ESD through pins 2 and/or 3 of the input XLR connector can adversely affect the device's CMRR, and may cause failure if the ESD reaches sufficiently high levels.

If the application requires surviving such ESD incidents, THAT recommends the circuit of either Figure 13 or 14. Figure 13 is appropriate for the 1203 and 1206, both of which support input signals that swing higher than the supply rails. This arrangement of signal and Zener diodes permits the maximum allowable (audio) input signal to reach the IC's input pins, but directs high-energy ESD impulses to the rails. So long as the

Figure 12. Internal input protection circuitry

THAT Corporation; 45 Summer Street; Milford, Massachusetts 01757-1656; USA Tel: +1 508 478-9200; Fax +1 508 478-0990; Web: <u>www.thatcorp.com</u> Copyright © 2017, THAT Corporation; All rights reserved.

Figure 13. RFI and ESD protection for the 1203 and 1206

supply rails are adequately decoupled and the diodes themselves are reasonably robust, all but the most drastic ESD events will not affect the 1203/6 IC itself. Figure 14, which works similarly, is appropriate for the 1200, which is limited to input signals up to about the supply rails.

D1 through D4 in Figures 13 and 14 can be 1N4148 types, while the 12 V Zener diodes should be  $\frac{1}{2}$  watt to allow them to support relatively high currents with 12 V across them for the short duration of an ESD pulse.

We will continue to work to find real world solutions to the often difficult problem of ESD protection. Please look to our web site for future application notes regarding this subject.

Note that we know of no circuit that will protect against really strong ESD, such as lightning, so please do not take this advice as suggesting that the circuits of Figures 13 and 14 are completely immune to ESD!

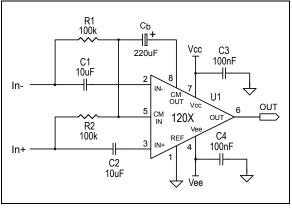

# **AC Coupling Inputs**

It is not necessary to AC couple the 1200-series inputs. However, if desired, we recommend the circuit of Figure 15. In this circuit Resistors  $R_1$  and  $R_2$  benefit from the common-mode bootstrap via their connection to  $CM_{in}$ . This reduces their impact on common-mode input impedance, preserving the benefit of InGenius, while providing a discharge path for charge in the input

Figure 14. RFI and ESD protection for the 1200

Figure 15. AC coupling 1200-series inputs

coupling capacitor. Choose capacitors large enough to present minimal impedance to the lowest signals of interest, compared to the differential input impedance of the InGenius IC (48 k $\Omega$ ). If desired, this may be combined with the RF protection of Figures 10 or 11, and ESD protection of Figures 13 or 14.

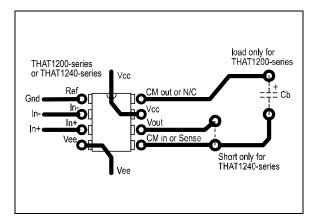

# **Dual Layout Option**

InGenius ICs are available only from THAT Corporation. Should a manufacturer wish to provide some alternatives to the 1200 series, it is possible to lay out the circuit board for a 1200 such that a THAT 1240series (conventional) balanced input stage could be substituted in a pinch. Since the 1240 series is pincompatible with similar parts available from other

Figure 16. Dual PCB layout for THAT120X and THAT124X

manufacturers, this offers the possibility of several reduced-performance second sources if 1200-series ICs were for unavailable for any reason.

The PCB layout shown in Figure 16 provides manufacturers with the option to load a PCB with either of these input stages. Note that these figures are not to scale. The interconnects should be as short as practical, constrained only by component size and relevant manufacturing considerations.

When a THAT 1200-series IC is installed, capacitor  $C_b$  is connected between  $CM_{\rm in}$  and  $CM_{out}$ . No connection is made between  $V_{out}$  and  $CM_{\rm in}$ . When the THAT 1240-series is used, capacitor  $C_b$  is removed, and a jumper connects the  $V_{out}$  and Sense pins.

Information furnished by THAT Corporation is believed to be accurate and reliable. However no responsibility is assumed by THAT Corporation for its use nor for any infringements of patents or other rights of third parties which may result from its use.

### LIFE SUPPORT POLICY

THAT Corporation products are not designed for use in life support equipment where malfunction of such products can reasonably be expected to result in personal injury or death. The buyer uses or sells such products for life suport application at the buyer's own risk and agrees to hold harmless THAT Corporation from all damages, claims, suits or expense resulting from such use.

### CAUTION: THIS IS AN ESD (ELECTROSTATIC DISCHARGE) SENSITIVE DEVICE.

It can be damaged by the currents generated by electrostatic discharge. Static charge and therefore dangerous voltages can accumulate and discharge without detection causing a loss of function or performance to occur.

Use ESD preventative measures when storing and handling this device. Unused devices should be stored in conductive packaging. Packaging should be discharged before the devices are removed. ESD damage can occur to these devices even after they are installed in a board-level assembly. Circuits should include specific and appropriate ESD protection.

| Revision | ECO  | Date     | Changes                                                                                                                               | Page |

|----------|------|----------|---------------------------------------------------------------------------------------------------------------------------------------|------|

| 00       | —    | 10/18/04 | Initial Release                                                                                                                       | —    |

| 01       | 3004 | 05/11/17 | Corrections to application figures 11, 13, 14; Added the Packaging<br>Characteristics table; Corrected the Output Noise spec; Redrawn | —    |

|          |      |          |                                                                                                                                       |      |

# **Revision History**