## **Clock Generator for Wireless Charge Module**

#### **Description**

The 6P40368 is a small form factor clock generator with integrated crystal that is intended for low-power, consumer, wearable and smart devices.

The device is designed to support a single 1.8V LVCMOS clock output and a dynamic frequency control for two frequency options. The frequency can be selected by one output pin. The 6P40368 has an embedded crystal to offer a more reliable clock source with small board space requirements.

#### **Features**

- No input clock source requirement

- Dynamic Frequency Control (DFC) is used for output frequency selection

- 1.8V operating voltage

- I<sup>2</sup>C interface

- 2.5 × 2.5 mm 12-DFN package, small form factor

## **Typical Applications**

Wireless charge module

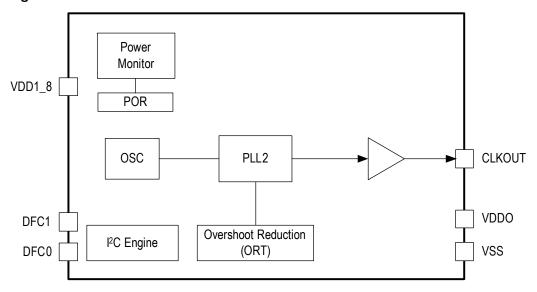

## **Block Diagram**

Figure 1. Block Diagram

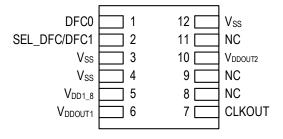

## **Pin Assignments**

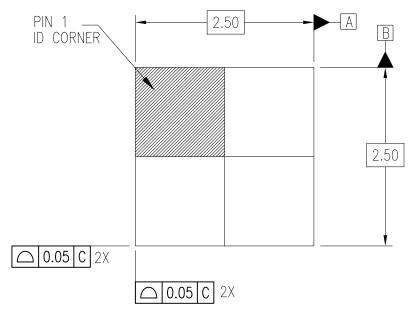

Figure 2. Pin Assignments for 2.5 × 2.5 mm 12-DFN Package

2.5 × 2.5 mm 12-DFN

#### **Pin Descriptions**

**Table 1. Pin Descriptions**

| Number | Name                | Туре   | Description                                                            |

|--------|---------------------|--------|------------------------------------------------------------------------|

| 1      | DFC0                | Input  | Dynamic frequency control pin.                                         |

| 2      | SEL_DFC/DFC1        | Input  | Dynamic frequency control pin selected by SEL_DFC at power-on default. |

| 3      | V <sub>SS</sub>     | Power  | Ground pin.                                                            |

| 4      | V <sub>SS</sub>     | Power  | Ground pin.                                                            |

| 5      | V <sub>DD1_8</sub>  | Power  | 1.8V power rail.                                                       |

| 6      | V <sub>DDOUT1</sub> | Power  | Power supply pin for OUT1 output (1.8V).                               |

| 7      | CLKOUT              | Output | 1.8V LVCMOS clock output.                                              |

| 8      | NC                  | _      | No connect.                                                            |

| 9      | NC                  | _      | No connect.                                                            |

| 10     | V <sub>DDOUT2</sub> | Power  | Output clock power supply pin 1.8V.                                    |

| 11     | NC                  | _      | No connect.                                                            |

| 12     | V <sub>SS</sub>     | Power  | Ground pin.                                                            |

## **Frequency Selection**

**Table 2: Frequency Selection**

| SEL_DFC | DFC1 | DFC0 | CLKOUT (MHz) |

|---------|------|------|--------------|

| 0       | 0    | 0    | 6.16791      |

| 0       | 0    | 1    | 6.1298496    |

| 0       | 1    | 0    | N/A          |

| 0       | 1    | 1    | N/A          |

| 1       | Х    | Х    | Х            |

## **ORT - VCO Overshoot Reduction Technology**

The 6P40368 supports the VCO overshoot reduction technology to prevent an output clock frequency spike when the device is changing frequency on-the-fly or doing DFC (Dynamic Frequency Control) function. The VCO frequency changes are controlled instead of free-run to targeted frequency.

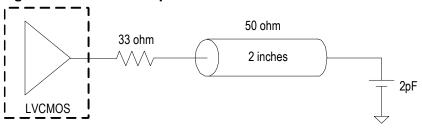

## **Output Clock Test Conditions**

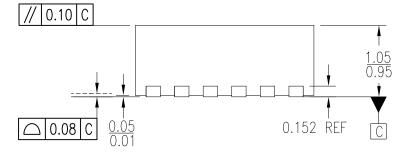

Figure 3. LVCMOS Output Clock Test Condition

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 6P40368. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

Table 3. Absolute Maximum Ratings<sup>1</sup>

| Item                                                     | Rating                                            |

|----------------------------------------------------------|---------------------------------------------------|

| Supply Voltage, V <sub>DD1_8</sub> , V <sub>DDOUTx</sub> | -0.5V to 2.2V                                     |

| Inputs                                                   |                                                   |

| Other inputs                                             | -0.5V to V <sub>DD1_8</sub> / V <sub>DDOUTx</sub> |

| Outputs, V <sub>DDOUTx</sub> (LVCMOS)                    | -0.5V to V <sub>DDOUTx</sub> + 0.5V               |

| Outputs, IO (SDA)                                        | 10mA                                              |

| Package Thermal Impedance, Θ <sub>JA</sub>               | 42°C/W (0mps)                                     |

| Package Thermal Impedance, $\Theta_{\text{JC}}$          | 41.8°C/W (0mps)                                   |

| Storage Temperature, T <sub>STG</sub>                    | -65°C to 150°C                                    |

| ESD Human Body Model                                     | 2000V                                             |

| Junction Temperature                                     | 125°C                                             |

<sup>&</sup>lt;sup>1</sup> Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Recommended Operating Conditions**

**Table 4. Recommended Operating Conditions**

| Symbol                | Parameter                                                                                                  | Minimum | Typical | Maximum | Units |

|-----------------------|------------------------------------------------------------------------------------------------------------|---------|---------|---------|-------|

| V <sub>DDOUT1</sub>   | Power Supply Voltage for supporting OUT1                                                                   | 1       | _       | 1.89    | V     |

| V <sub>DDOUT2</sub>   | Power Supply Voltage for supporting OUT2                                                                   | 1.71    | 1.8     | 1.89    |       |

| V <sub>DD1_8</sub>    | Power Supply Voltage for Core Logic functions                                                              | 1.71    | 1.8     | 1.89    | V     |

| T <sub>A</sub>        | Ambient Operating Temperature                                                                              | -40     | _       | 85      | °C    |

| C <sub>LOAD_OUT</sub> | Maximum Load Capacitance (1.8V LVCMOS only)                                                                | _       | 5       | _       | pF    |

| t <sub>PU</sub>       | Power-up Time for all V <sub>DD</sub> s to reach minimum specified voltage (power ramps must be monotonic) | 0.05    | _       | 3       | ms    |

# Input Capacitance, LVCMOS Output Impedance, and Internal Pull-down Resistance ( $T_A$ = +25 °C)

Table 5. Input Capacitance, LVCMOS Output Impedance, and Internal Pull-down Resistance

| Symbol             | Parameter                                                   | Minimum | Typical | Maximum | Units |

|--------------------|-------------------------------------------------------------|---------|---------|---------|-------|

| C <sub>IN</sub>    | Input Capacitance (OE, SDA, SCL)                            | _       | 3       | 7       | pF    |

| Pull-down Resistor | OE                                                          | _       | 150     | _       | kΩ    |

| R <sub>OUT</sub>   | LVCMOS Output Driver Impedance (V <sub>DDOUTx</sub> = 1.8V) | _       | 50      | _       | Ω     |

#### **Integrated Crystal Characteristics**

**Table 6. Crystal Characteristics**

| Parameter                          | Test Conditions | Minimum | Typical | Maximum | Units |

|------------------------------------|-----------------|---------|---------|---------|-------|

| Mode of Oscillation                | -               |         | Fundame | ntal    |       |

| Frequency                          | _               | _       | 26      | _       | MHz   |

| Frequency Tolerance <sup>1</sup>   | _               | _       | _       | ±20     | ppm   |

| Equivalent Series Resistance (ESR) | _               | _       | 10      | 100     | Ω     |

| Shunt Capacitance                  | _               | _       | 2       | 7       | pF    |

| Load Capacitance (C <sub>L</sub> ) | _               | 6       | 8       | 10      | pF    |

| Maximum Crystal Drive Level        | _               | _       | _       | 100     | μW    |

<sup>&</sup>lt;sup>1</sup> Frequency tolerance includes initial frequency, over-temperature range and aging data.

#### **Electrical Characteristics**

Table 7. DC Electrical Characteristics 1,2

| Symbol            | Parameter                | Conditions                                                               | Minimum | Typical | Maximum | Units |

|-------------------|--------------------------|--------------------------------------------------------------------------|---------|---------|---------|-------|

| 1                 | Operation Supply Current | $V_{DD} = V_{DDOUTx} = V_{DD1_8} = 1.8V$ ; OUT = 6.1679100MHz with load. | _       | 2.5     | _       | mA    |

| IDD               | Operation Supply Current | $V_{DD} = V_{DDOUTx} = V_{DD1_8} = 1.8V$ ; OUT = 6.1298496MHz with load. | _       | 2.5     | _       | mA    |

| I <sub>DDPD</sub> | Power Down Current       | PD asserted with V <sub>DD1_8</sub> and V <sub>DDOUTx</sub> on.          | _       | 390     | _       | μA    |

<sup>&</sup>lt;sup>1</sup> Single CMOS driver active.

<sup>&</sup>lt;sup>2</sup> OUT current measured with 2-inch transmission line and 2pF load.

#### Table 8. Input Parameters <sup>1</sup>

Supply Voltage  $V_{DD1\_8}$  = 1.8V ±5%,  $V_{DDOUTx}$  = 1.8V ±5%,  $T_A$  = -40°C to +85°C.

| Symbol          | Parameter                          | Conditions                          | Minimum | Typical | Maximum | Units |

|-----------------|------------------------------------|-------------------------------------|---------|---------|---------|-------|

| I <sub>IL</sub> | Input Leakage Low Current for OE1  | V <sub>IN</sub> = GND at OE1 pin.   | 150     | _       | 5       | μΑ    |

| I <sub>IH</sub> | Input Leakage High Current for OE1 | V <sub>IN</sub> = 1.89V.            | _       | _       | 20      | μΑ    |

| I_OE1           | Input Leakage Current              | V <sub>IN</sub> = 1.89V at OE1 pin. |         | 1       | 120     | μA    |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

#### Table 9. DC Electrical Characteristics for 1.8V LVCMOS

$V_{DDOUTx} = 1.8V \pm 5\%$ ,  $T_A = -40$ °C to 85°C.

| Symbol            | Parameter              | Conditions                                      | Minimum                    | Typical | Maximum                    | Units |

|-------------------|------------------------|-------------------------------------------------|----------------------------|---------|----------------------------|-------|

| V <sub>OH</sub>   | Output High Voltage    | I <sub>OH</sub> = -8mA.                         | 0.7 × V <sub>DDOUTx</sub>  | _       | V <sub>DDOUTx</sub>        | V     |

| V <sub>OL</sub>   | Output Low Voltage     | I <sub>OL</sub> = 8mA.                          | 0.1                        | _       | 0.15                       | V     |

| I <sub>OZDD</sub> | Output Leakage Current | Tri-state outputs, V <sub>DDOUTx</sub> = 1.89V. | _                          | _       | 3                          | μA    |

| V <sub>IH</sub>   | Input High Voltage     | Single-ended inputs – OE, SDA, SCL.             | 0.65 × V <sub>DDOUTx</sub> | _       | V <sub>DDOUTx</sub> + 0.3  | V     |

| V <sub>IL</sub>   | Input Low Voltage      | Single-ended inputs – OE, SDA, SCL.             | GND - 0.3                  | _       | 0.35 × V <sub>DDOUTx</sub> | V     |

#### **AC Electrical Characteristics**

#### **Table 10. AC Timing Electrical Characteristics**

$V_{DD1~8}$  = 1.8V ±5%,  $V_{DDOUTx}$  = 1.8V ±5%,  $T_A$  = -40°C to +85°C; spread spectrum = off.

| Symbol             | Parameter              | Conditions                                                                                                                       | Minimum | Typical   | Maximum | Units |

|--------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------|-----------|---------|-------|

| f 1                | Output Frequency       | SEL_DFC = 0, DFC[1:0] = 01.                                                                                                      | _       | 6.16791   | _       | MHz   |

| f <sub>OUT</sub> 1 | Output Frequency       | SEL_DFC = 0, DFC[1:0] = 00.                                                                                                      | _       | 6.1298496 | _       | MHz   |

| t0                 | Accuracy <sup>4</sup>  | Average.                                                                                                                         | _       | _         | 50      | ppm   |

| t1                 | Output Duty Cycle      | LVCMOS clock < 120MHz.                                                                                                           | 45      | _         | 55      | %     |

| t2                 | Rise/Fall, SLEW[0] = 1 | Single-ended LVCMOS output clock rise and fall time, 20% to 80% of V <sub>DDOUT</sub> 1.8V.                                      | _       | 2.5       | _       | ns    |

| t3                 | Clock Jitter           | Cycle-to-cycle jitter (peak-to-peak), multiple output frequencies switching, differential outputs (1.8V nominal output voltage). | _       | 50        | 150     | ps    |

| t4 <sup>2</sup>    | Lock Time              | PLL lock time from power-up.                                                                                                     | _       | _         | 20      | ms    |

| t5 <sup>3</sup>    | Lock Time              | PLL lock time from shutdown mode.                                                                                                | _       | 0.1       | 2       | ms    |

<sup>&</sup>lt;sup>1</sup> Practical lower frequency is determined by loop filter settings.

<sup>&</sup>lt;sup>2</sup> Includes loading the configuration bits from OTP to PLL registers. It does not include OTP programming/write time.

<sup>&</sup>lt;sup>3</sup> Actual PLL lock time depends on the loop configuration.

<sup>&</sup>lt;sup>4</sup> Includes initial frequency, over-temperature range and aging data.

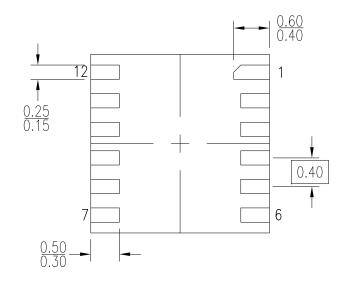

## Package Outline Drawings

The package outline drawings are located at the end of this document. The package information is the most current data available.

#### **Ordering Information**

| Orderable Part Number | Package                          | Shipping Packaging | Temperature   |

|-----------------------|----------------------------------|--------------------|---------------|

| 6P40368NDGI           | 2.5 × 2.5 mm, 0.4mm pitch 12-DFN | Cut Tape           | -40° to +85°C |

| 6P40368NDGI8          | 2.5 × 2.5 mm, 0.4mm pitch 12-DFN | Reel               | -40° to +85°C |

#### **Marking Diagram**

- 1. Line 1 is the truncated part number.

- 2. "Y" is the last digit of the year the part was assembled.

- 3. "\*\*" denotes sequential lot number.

## **Revision History**

| Revision Date    | Description of Change                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------|

| August 16, 2018  | <ul> <li>Updated Absolute Maximum Ratings table.</li> <li>Updated Package Outline Drawings section.</li> </ul> |

| October 30, 2017 | Initial release.                                                                                               |

**Corporate Headquarters** 6024 Silver Creek Valley Road

San Jose, CA 95138 USA

www.IDT.com

Sales

1-800-345-7015 or 408-284-8200

Fax: 408-284-2775

www.IDT.com/go/sales

**Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. Integrated Device Technology, Inc. All rights reserved.

|   | DATE<br>CREATED | REVISIONS |                               |      |        |

|---|-----------------|-----------|-------------------------------|------|--------|

|   |                 | REV       | DESCRIPTION                   |      | AUTHOR |

|   | 06/21/16        | 00        | INITIAL RELEASE               |      | JH     |

| ı | 12/08/17        | 01        | CORRECT DIMEMSION             |      | JH     |

|   | NOTE            | REFE      | R TO DOP FOR OFFICIAL RELEASE | DATE |        |

TOP VIEW

SIDE VIEW (ROTATE 90 DEG.)

BOTTOM VIEW

#### NOTE:

- 1. DIMENSIONING AND TOLERANCING CONFORM TO ASMEY14.5-2009.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.