# Wire Bondable Automotive Vertical SiCap WASC 0202 1nF BV150

#### General description

The WAS Capacitor has been qualified according to AECQ-100 up to 68V, Grade 0 ( -40°C/+150°C) 2000 cycles TMCL. Qualification report of the BV150 technology according to AECQ100 requirements is available on request.

Target applications are decoupling and filtering of active devices when miniaturization and low ESL are required. This product is a single 1nF capacitor in 0.50 x 0.50mm package size. Other capacitance values and other package size are available as a single die or capacitor array; please feel free to contact us. The WAS Capacitor is based on PICS Integrated Passive technology. Standard PCB FR4 can be used.

**Assembly:** WASC capacitors are directly mounted on the PCB application using die attach and wire bonding.

WASC capacitors have the bottom electrode in Ti (0.1 µm)/Ni (0.3µm)/Au (0.2µm) and top electrode in gold, other top finishing are available on request such as Aluminum.

#### Key features

- AECQ-100 Qualification

- Full compatible Monolithic ceramic capacitors for replacement

- Ultra-high stability of capacitance value:

- Temperature 60ppm/K (-55 °C to +150 °C)

- Voltage <0.02%/Volts</li>

- o Negligible capacitance loss through ageing

- Low profile 0.25mm or 0.1mm, but other thicknesses possible on request

- Small size 0.50 x 0.50mm (0202 format)

- Break down voltage > 150V

- · Low leakage current

- · High reliability

- High operating temperature (up to 150 °C)

- Compatible with high temperature cycling during manufacturing operations (exceeding 300 °C)

- Compatible with EIA 0202 footprint

- Applicable for standard wire bonding assembly (ball and wedge)

#### Key applications

- Any demanding automotive applications, such as ADAS sensors (Lidars, Radars) as well as all Automotive SiP devices (Mems, sensors, TPMS...)

- Supply decoupling / filtering of active device

- High reliability applications

- Devices with battery operations

- High temperature applications

- High volumetric efficiency (i.e. capacitance per unit volume)

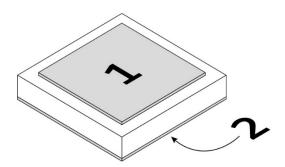

### **Functional diagram**

The next figure provides implementation set-up diagram.

Figure 1 Block Diagram

# Electrical performances

| Symbol                  | Parameter                         | Conditions                               | Min. | Тур. | Max.                                   | Unit              |

|-------------------------|-----------------------------------|------------------------------------------|------|------|----------------------------------------|-------------------|

| С                       | Capacitance value                 | @+25°C                                   | -    | 1    | -                                      | nF                |

| $\Delta C_{P}$          | Capacitance tolerance (1)         | @+25°C                                   | -15  |      | +15                                    | %                 |

| T <sub>OP</sub>         | Operating temperature             |                                          | -55  | 20   | 150                                    | °C                |

| T <sub>STG</sub>        | Storage temperature (2)           |                                          | -70  | -    | 165                                    | ů                 |

| $\Delta C_{T}$          | Capacitance temperature variation | -55 °C to 150 °C                         | _    | 60   | -                                      | ppm/K             |

| $RV_{DC}$               | Rated voltage (3)                 |                                          | -    |      | 68 <sup>(4)</sup><br>61 <sup>(5)</sup> | $V_{DC}$          |

| BV                      | Break down voltage                | @+25°C                                   | 150  | -    | -                                      | V                 |

| $\Delta C_{	ext{RVDC}}$ | Capacitance voltage variation     | From 0 V to RV <sub>DC</sub> ,<br>@+25°C | -    | -    | -0.02                                  | %/V <sub>DC</sub> |

| IR                      | Insulation resistor               | @RV <sub>DC</sub> , +25°C, 120s          | -    | 10   | -                                      | GΩ                |

| ESL                     | Equivalent Serial Inductance (6)  | @+25°C, SRF shunt mode                   | -    | 10   | -                                      | рН                |

| ESR                     | Equivalent Serial Resistance (6)  | @+25°C, shunt mode                       | -    | 10   | -                                      | mOhm              |

| ESD                     | HBM stress (6)                    | JS-001-2017                              | 2    | -    | -                                      | kV                |

Table 1 - Electrical performances

- (1): other tolerance available upon request

- (2): without packaging

(3): Lifetime is voltage and temperature dependent, please refer to application note 'Lifetime of 3D capacitors'

(4): 10 years of intrinsic life time prediction at 100°C continuous operation

- (5): 10 years of intrinsic life time prediction at 150°C continuous operation

- (6): please refer to application note 'ESD Challenge in 3D Murata Integrated Passive technology'

# Pinning definition

Figure 2 Pinning definition

| pin# | Description                                                         |

|------|---------------------------------------------------------------------|

| 1    | Top side<br>Electrode finishing: Au                                 |

| 2    | Back side<br>Electrode finishing: Ti (0.1 μm)/Ni (0.3μm)/Au (0.2μm) |

Table 2 - Pining description..

# **Ordering Information**

Murata Integrated Passive Devices delivers products with AQL level II (0.65).

| Part number         |           | Package                    |                   |                                                   |  |

|---------------------|-----------|----------------------------|-------------------|---------------------------------------------------|--|

| (16NC)              |           | Packaging                  | Finishing         | Description                                       |  |

| 935 147 521 410-F1T | WO0202410 | 6" FFC                     | Au <sup>(1)</sup> | 1nF BV150 – 1 bondpad –<br>0.50 x 0.50mm x 0.25mm |  |

| 935 147 521 410-T3T | WO0202410 | T&R 1Kunits <sup>(3)</sup> | Au <sup>(1)</sup> | 1nF BV150 – 1 bondpad –<br>0.50 x 0.50mm x 0.25mm |  |

| 935 148 521 410-F1T | WO0202410 | 6" FFC                     | Au <sup>(1)</sup> | 1nF BV150 – 1 bondpad –<br>0.50 x 0.50mm x 0.1mm  |  |

| 935 148 521 410-T3T | WO0202410 | T&R 1Kunits <sup>(2)</sup> | Au <sup>(1)</sup> | 1nF BV150 – 1 bondpad –<br>0.50 x 0.50mm x 0.1mm  |  |

Table 3 - Packaging and ordering information

- Au = TiW (0.3μm) / Au (3μm) missing capacitors can reach 0.5%

#### Pad Metallization

The standard pad finishing metallization is Au for the top pad and Ti  $(0.1 \mu m)/Ni$   $(0.3\mu m)/Au$   $(0.2\mu m)$  for the bottom pad.

Other Metallization, such as Thick Gold or Aluminum pads are possible on request.

# Material regulation

This product is RoHS compliant at the time of publication. For further information about regulation compliancy, please ask your sales representative

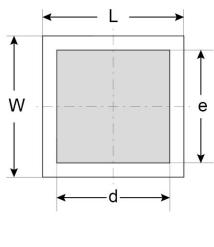

#### Package outline

The product is delivered as a bare silicon die, with passivation opening for contacts.

Figure 3 - Package outline drawing

Figure 4 - Package isometric view

| L (mm)     | W (mm)     | T (mm)             | d (mm) | e (mm) |

|------------|------------|--------------------|--------|--------|

| 0.50 ±0.03 | 0.50 ±0.03 | 0.25 or 0.10 ±0.01 | 0.4    | 0.4    |

Table 4 - Dimensions and tolerances

#### Assembly

The attachment techniques recommended by Murata on the customer's substrates are fully detailed in specific documents available on our website. To assure the correct use and proper functioning of Murata capacitors please download the assembly instructions on <a href="https://www.murata.com/en-us/products/capacitor/siliconcapacitors">https://www.murata.com/en-us/products/capacitor/siliconcapacitors</a> and read them carefully.

Figure 5 Scan this QR Code to access the Murata Silicon Capacitor web page

# Packaging format

Please refer to application note 'Products Storage Conditions and Shelf Life'.

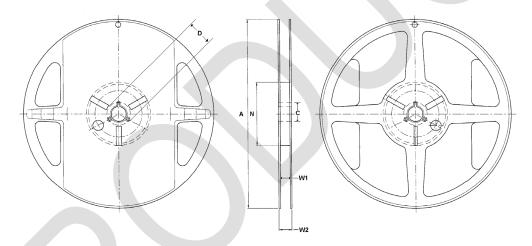

# Tape and Reel:

Figure 6 - Reel drawing

| Tape<br>Width | Diameter<br>A     | С    | D    | Hub<br>N | W1 | W2   |

|---------------|-------------------|------|------|----------|----|------|

| 8             | 178<br>(7 inches) | 13.5 | 20.2 | 60       | 9  | 11.5 |

Table 5 – Reel dimensions (mm)

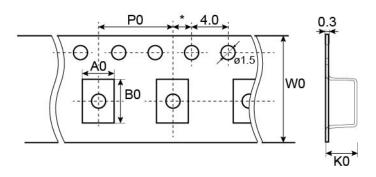

Figure 7 - Tape drawing

| Cav  | ity dimensi | ions | Carrier tape | Carrier tape |

|------|-------------|------|--------------|--------------|

| Ao   | Во          | Ko   | width W0     | pitch P0     |

| 0.56 | 0.56        | 0.31 | 8 mm         | 4mm          |

Table 6 - Tape dimensions (mm)

#### Film frame carrier:

With UV curable dicing tape (UV performed)

Good dies are identified using the appropriate e-mapping format. No ink is added on wafer to label other dies.

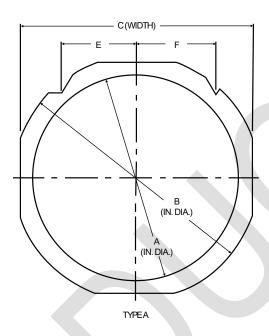

Figure 8 – Film frame drawing

| Wafer<br>diameter | Inside<br>diameter<br>A | Outside<br>diameter<br>B | Width<br>C | Thickness | Pin<br>location<br>E | Pin<br>location<br>F | Frame<br>style |

|-------------------|-------------------------|--------------------------|------------|-----------|----------------------|----------------------|----------------|

| 6"                | 7.639"                  | 8.976"                   | 8.346"     | 0.048"    | 2.370"               | 2.5"                 | DTF-2-6-1      |

Table 7 - Frame dimensions (inches)

# Waffle pack

Please refer to application note 'Waffle Pack Chip Carrier Handling & Opening Procedure'.

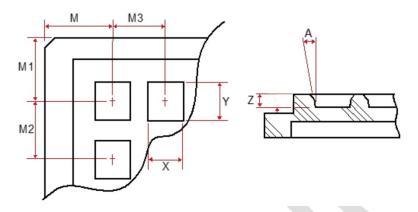

Figure 9 Waffle pack drawing

| External dimensions | Max. capacity | Pocket<br>length X | Pocket<br>width Y | Pocket<br>depth Z |

|---------------------|---------------|--------------------|-------------------|-------------------|

| 2 inches            | 20 x 20       | 0.64 ±0.05         | 0.64 ±0.05        | 0.36 ±0.05        |

Table 8 - Waffle pack dimensions (mm) for 250µm thick product

| M          | M1         | M2         | М3         | Α         |

|------------|------------|------------|------------|-----------|

| 4.65 ±0.08 | 4.65 ±0.08 | 2.18 ±0.05 | 2.18 ±0.05 | 15° ±1/2° |

Table 9 - Waffle pack dimensions (mm) for 250µm thick product

| External dimensions | Max. capacity | Pocket<br>length X | Pocket<br>width Y | Pocket<br>depth Z |

|---------------------|---------------|--------------------|-------------------|-------------------|

| 2 inches            | 20 x 20       | 0.58 ±0.05         | 0.58 ±0.05        | 0.28 ±0.05        |

Table 10 - Waffle pack dimensions (mm) for 100µm thick product

| M          | M1         | M2         | М3         | A         |

|------------|------------|------------|------------|-----------|

| 4.89 ±0.08 | 4.89 ±0.08 | 2.16 ±0.05 | 2.16 ±0.05 | 18° ±1/2° |

Table 11 - Waffle pack dimensions (mm) for 100µm thick product