# RENESAS 4-Output 1.8V PCIe Zero-Delay/Fanout Clock Buffer with Zo = 330hms

DATASHEET

### **Description**

The 9DBV0431 is a member of Renesas' SOC-Friendly 1.8V Very-Low-Power (VLP) PCIe family. It can also be used for 50M or 125M Ethernet Applications via software frequency selection. The device has 4 output enables for clock management, and 3 selectable SMBus addresses.

# Recommended Application

1.8V PCIe Gen1–5 Zero-Delay/Fan-out Buffer (ZDB/FOB)

# **Output Features**

Four 1–200Hz Low-Power (LP) HCSL DIF pairs with Zo = 33ohms

# **Key Specifications**

- DIF cycle-to-cycle jitter < 50ps</li>

- DIF output-to-output skew < 50ps

- PCIe Gen5 CC additive phase jitter < 40fs RMS</li>

- 12kHz-20MHz additive phase jitter = 156fs RMS at 156.25MHz (typical)

#### Features/Benefits

- LP-HCSL outputs save 8 resistors; minimal board space and BOM cost

- 53mW typical power consumption in PLL mode; minimal power consumption

- OE# pins; support DIF power management

- HCSL compatible differential input; can be driven by common clock sources

- · Programmable Slew rate for each output; allows tuning for various line lengths

- Programmable output amplitude; allows tuning for various application environments

- Pin/software selectable PLL bandwidth and PLL Bypass; minimize phase jitter for each application

- Outputs blocked until PLL is locked; clean system start-up

- Software selectable 50MHz or 125MHz PLL operation; useful for Ethernet applications

- Configuration can be accomplished with strapping pins; SMBus interface not required for device control

- 3.3V tolerant SMBus interface works with legacy controllers

- Space saving 5 x 5mm 32-VFQFPN; minimal board space

- Selectable SMBus addresses; multiple devices can easily share an SMBus segment

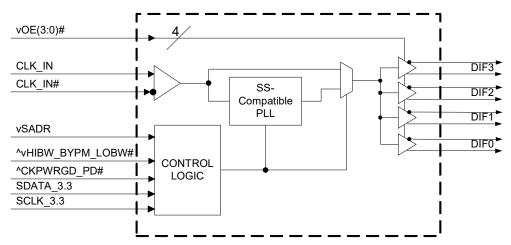

# **Block Diagram**

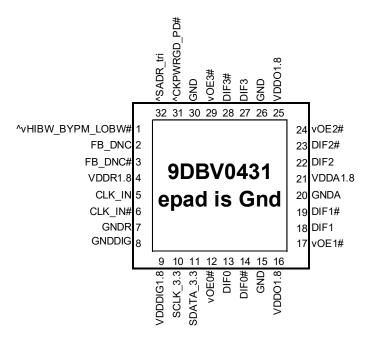

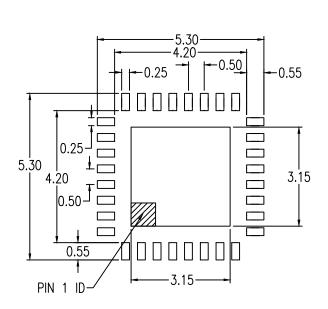

# **Pin Configuration**

#### 32-pin VFQFPN, 5x5 mm, 0.5mm pitch

^ prefix indicates internal 120KOhm pull up resistor ^v prefix indicates internal 120KOhm pull up AND pull down resistor (biased to VDD/2) v prefix indicates internal 120KOhm pull down resistor

#### **SMBus Address Selection Table**

|                                                   | SADR | Address | + Read/Write bit |

|---------------------------------------------------|------|---------|------------------|

| State of SADR on first application of CKPWRGD_PD# | 0    | 1101011 | X                |

|                                                   | M    | 1101100 | X                |

|                                                   | 1    | 1101101 | X                |

#### **Power Management Table**

| CKPWRGD PD# | CLK IN  | SMBus   | OEx# Pin  | DIFx        |         | PLL             |  |

|-------------|---------|---------|-----------|-------------|---------|-----------------|--|

| CKFWKGD_FD# | OLK_IN  | OEx bit | OLX# FIII | True O/P Co |         | FLL             |  |

| 0           | X       | Х       | Х         | Low         | Low     | Off             |  |

| 1           | Running | 0       | X         | Low         | Low     | On <sup>1</sup> |  |

| 1           | Running | 1       | 0         | Running     | Running | On <sup>1</sup> |  |

| 1           | Running | 1       | 1         | Low         | Low     | On <sup>1</sup> |  |

<sup>1.</sup> If Bypass mode is selected, the PLL will be off, and outputs will be running.

#### **Power Connections**

| Pin Numb | er          | Description           |

|----------|-------------|-----------------------|

| VDD      | GND         | Description           |

| 4        | 7           | Input receiver analog |

| 9        | 8           | Digital Power         |

| 16, 25   | 15,20,26,30 | DIF outputs           |

| 21       | 20          | PLL Analog            |

#### **PLL Operating Mode**

| HiBW_BypM_LoBW# | MODE      | Byte1 [7:6]<br>Readback | Byte1 [4:3]<br>Control |

|-----------------|-----------|-------------------------|------------------------|

| 0               | PLL Lo BW | 00                      | 00                     |

| М               | Bypass    | 01                      | 01                     |

| 1               | PLL Hi BW | 11                      | 11                     |

#### **Frequency Select Table**

| •            |          |          |

|--------------|----------|----------|

| FSEL         | CLK_IN   | DIFx     |

| Byte3 [4:3]  | (MHz)    | (MHz)    |

| 00 (Default) | 100.00   | CLK_IN   |

| 01           | 50.00    | CLK_IN   |

| 10           | 125.00   | CLK_IN   |

| 11           | Reserved | Reserved |

# **Pin Descriptions**

| Pin# | Pin Name        | Type                                                                                 | Pin Description                                                                      |

|------|-----------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 4    | ^vHIBW BYPM LOB | LATCHED                                                                              | Trilevel input to select High BW, Bypass or Low BW mode.                             |

| 1    |                 | IN                                                                                   | See PLL Operating Mode Table for Details.                                            |

| 2    | ED DNC          | DNC                                                                                  | True clock of differential feedback. The feedback output and feedback input are      |

|      | FB_DNC          | DNC                                                                                  | connected internally on this pin. Do not connect anything to this pin.               |

| 3    | ED DNC#         | DNC                                                                                  | Complement clock of differential feedback. The feedback output and feedback          |

| 3    | FB_DNC#         | DNC                                                                                  | input are connected internally on this pin. Do not connect anything to this pin.     |

| 4    | VDDR1.8         | 1.8V power for differential input clock (receiver). This VDD should be treated as an |                                                                                      |

| -    | VDDIX1.0        | PWR                                                                                  | Analog power rail and filtered appropriately.                                        |

| 5    | CLK_IN          | IN                                                                                   | True Input for differential reference clock.                                         |

| 6    | CLK_IN#         | IN                                                                                   | Complementary Input for differential reference clock.                                |

| 7    | GNDR            | GND                                                                                  | Analog Ground pin for the differential input (receiver)                              |

| 8    | GNDDIG          | GND                                                                                  | Ground pin for digital circuitry                                                     |

| 9    | VDDDIG1.8       | PWR                                                                                  | 1.8V digital power (dirty power)                                                     |

| 10   | SCLK_3.3        | IN                                                                                   | Clock pin of SMBus circuitry, 3.3V tolerant.                                         |

| 11   | SDATA_3.3       | I/O                                                                                  | Data pin for SMBus circuitry, 3.3V tolerant.                                         |

| 12   | vOE0#           | IN                                                                                   | Active low input for enabling DIF pair 0. This pin has an internal pull-down.        |

|      |                 | 11.4                                                                                 | 1 =disable outputs, 0 = enable outputs                                               |

| 13   | DIF0            | OUT                                                                                  | Differential true clock output                                                       |

| 14   | DIF0#           | OUT                                                                                  | Differential Complementary clock output                                              |

| 15   | GND             | GND                                                                                  | Ground pin.                                                                          |

| 16   | VDDO1.8         | PWR                                                                                  | Power supply for outputs, nominally 1.8V.                                            |

| 17   | vOE1#           | IN                                                                                   | Active low input for enabling DIF pair 1. This pin has an internal pull-down.        |

|      |                 |                                                                                      | 1 =disable outputs, 0 = enable outputs                                               |

| 18   | DIF1            | OUT                                                                                  | Differential true clock output                                                       |

| 19   | DIF1#           | OUT                                                                                  | Differential Complementary clock output                                              |

| 20   | GNDA            | GND                                                                                  | Ground pin for the PLL core.                                                         |

| 21   | VDDA1.8         | PWR                                                                                  | 1.8V power for the PLL core.                                                         |

| 22   | DIF2            | OUT                                                                                  | Differential true clock output                                                       |

| 23   | DIF2#           | OUT                                                                                  | Differential Complementary clock output                                              |

| 24   | vOE2#           | IN                                                                                   | Active low input for enabling DIF pair 2. This pin has an internal pull-down.        |

|      |                 |                                                                                      | 1 =disable outputs, 0 = enable outputs                                               |

| 25   | VDDO1.8         | PWR                                                                                  | Power supply for outputs, nominally 1.8V.                                            |

| 26   | GND             | GND                                                                                  | Ground pin.                                                                          |

|      | DIF3            | OUT                                                                                  | Differential true clock output                                                       |

| 28   | DIF3#           | OUT                                                                                  | Differential Complementary clock output                                              |

| 29   | vOE3#           | IN                                                                                   | Active low input for enabling DIF pair 3. This pin has an internal pull-down.        |

|      |                 |                                                                                      | 1 =disable outputs, 0 = enable outputs                                               |

| 30   | GND             | GND                                                                                  | Ground pin.                                                                          |

|      |                 |                                                                                      | Input notifies device to sample latched inputs and start up on first high assertion. |

| 31   | ^CKPWRGD_PD#    | IN                                                                                   | Low enters Power Down Mode, subsequent high assertions exit Power Down Mode.         |

|      |                 |                                                                                      | This pin has internal pull-up resistor.                                              |

| 32   | ^SADR_tri       | LATCHED                                                                              | Tri-level latch to select SMBus Address. See SMBus Address Selection Table.          |

|      |                 | IN                                                                                   | THE CVC INITION TO SCIOOL SINIBUS AUDIESS. SEE SINIBUS AUDIESS SEIECTION TABLE.      |

| 33   | ePad            | GND                                                                                  | Connect epad to ground.                                                              |

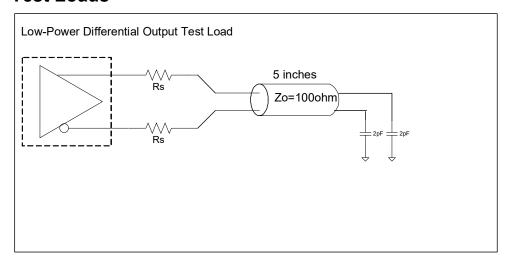

# **Test Loads**

### **Alternate Differential Output Terminations**

|    | <b>.</b> |         |

|----|----------|---------|

| Rs | Zo       | Units   |

| 33 | 100      | Ohms    |

| 27 | 85       | Offilis |

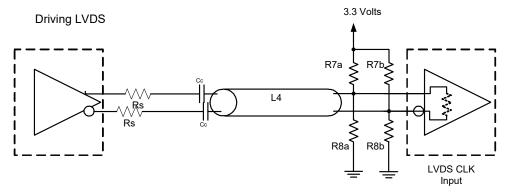

# **Driving LVDS**

#### Driving LVDS inputs with the 9DBV0431

| Briting 2 v Bo inputs with the 0 B v 0 + 0 1 |              |                   |      |  |  |  |  |

|----------------------------------------------|--------------|-------------------|------|--|--|--|--|

|                                              | ,            |                   |      |  |  |  |  |

|                                              | Receiver has | Receiver does not |      |  |  |  |  |

| Component                                    | termination  | have termination  | Note |  |  |  |  |

| R7a, R7b                                     | 10K ohm      | 140 ohm           |      |  |  |  |  |

| R8a, R8b                                     | 5.6K ohm     | 75 ohm            |      |  |  |  |  |

| Сс                                           | 0.1 uF       | 0.1 uF            |      |  |  |  |  |

| Vcm                                          | 1.2 volts    | 1.2 volts         |      |  |  |  |  |

# **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 9DBV0431. These ratings, which are standard values for Renesas commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER                 | SYMBOL      | CONDITIONS                | MIN  | TYP | MAX               | UNITS | NOTES |

|---------------------------|-------------|---------------------------|------|-----|-------------------|-------|-------|

| Power supply voltage      | VDDxx       | Applies to all VDD pins   | -0.5 |     | 2.5               | V     | 1,2   |

| Input Voltage             | $V_{IN}$    |                           | -0.5 |     | $V_{DD}$ +0.5 $V$ | V     | 1, 3  |

| Input High Voltage, SMBus | $V_{IHSMB}$ | SMBus clock and data pins |      |     | 3.6V              | V     | 1     |

| Storage Temperature       | Ts          |                           | -65  |     | 150               | °C    | 1     |

| Junction Temperature      | Tj          |                           |      |     | 125               | °C    | 1     |

| Input ESD protection      | ESD prot    | Human Body Model          | 2000 |     |                   | V     | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

# **Electrical Characteristics-Clock Input Parameters**

T<sub>A</sub> = T<sub>COM</sub> or T<sub>IND</sub>. Supply Voltage per VDD of normal operation conditions. See Test Loads for Loading Conditions

|                                    | 0 1                | •                                                  |                       |     |      |       |       |

|------------------------------------|--------------------|----------------------------------------------------|-----------------------|-----|------|-------|-------|

| PARAMETER                          | SYMBOL             | CONDITIONS                                         | MIN                   | TYP | MAX  | UNITS | NOTES |

| Input High Voltage - DIF_IN        | $V_{IHDIF}$        | Differential inputs (single-ended measurement)     | 600                   | 800 | 1150 | mV    | 1     |

| Input Low Voltage - DIF_IN         | $V_{ILDIF}$        | Differential inputs (single-ended measurement)     | V <sub>SS</sub> - 300 | 0   | 300  | mV    | 1     |

| Input Common Mode Voltage - DIF_IN | $V_{COM}$          | Common Mode Input Voltage                          | 300                   |     | 725  | mV    | 1     |

| Input Amplitude - DIF_IN           | V <sub>SWING</sub> | Peak to Peak value (VIHDIF - VILDIF), single-ended | 300                   |     | 1450 | mV    | 1     |

| Input Slew Rate - DIF_IN           | dv/dt              | Measured differentially                            | 0.4                   |     |      | V/ns  | 1,2   |

| Input Leakage Current              | I <sub>IN</sub>    | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                 | -5                    |     | 5    | uA    | 1     |

| Input Duty Cycle                   | d <sub>tin</sub>   | Measurement from differential waveform             | 45                    |     | 55   | %     | 1     |

| Input Jitter - Cycle to Cycle      | $J_{DIFIn}$        | Differential Measurement                           | 0                     |     | 150  | ps    | 1     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

<sup>&</sup>lt;sup>3</sup> Not to exceed 2.5V.

<sup>&</sup>lt;sup>2</sup> Slew rate measured through +/-75mV window centered around differential zero.

# Electrical Characteristics–Input/Supply/Common Parameters–Normal Operating Conditions

$T_A = T_{COM}$  or  $T_{IND}$ . Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                        | SYMBOL                | CONDITIONS                                                                                                                          | MIN                  | TYP  | MAX                  | UNITS  | NOTES |

|----------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|----------------------|--------|-------|

| 1.8V Supply Voltage              | VDD                   | Supply voltage for core, analog and LVCMOS outputs                                                                                  | 1.7                  | 1.8  | 1.9                  | ٧      | 1     |

| Ambient Operating                | T <sub>COM</sub>      | Commercial range                                                                                                                    | 0                    | 25   | 70                   | °C     | 1     |

| Temperature                      | $T_{IND}$             | Industrial range                                                                                                                    | -40                  | 25   | 85                   | °C     | 1     |

| Input High Voltage               | $V_{IH}$              | Single-ended inputs, except SMBus                                                                                                   | 0.75 V <sub>DD</sub> |      | $V_{DD} + 0.3$       | V      | 1     |

| Input Mid Voltage                | $V_{IM}$              | Single-ended tri-level inputs ('_tri' suffix)                                                                                       | $0.4~V_{DD}$         |      | 0.6 V <sub>DD</sub>  | V      | 1     |

| Input Low Voltage                | $V_{IL}$              | Single-ended inputs, except SMBus                                                                                                   | -0.3                 |      | 0.25 V <sub>DD</sub> | V      | 1     |

|                                  | I <sub>IN</sub>       | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = VDD$                                                                                | -5                   |      | 5                    | uA     | 1     |

| Input Current                    | I <sub>INP</sub>      | Single-ended inputs $V_{IN}$ = 0 V; Inputs with internal pull-up resistors $V_{IN}$ = VDD; Inputs with internal pull-down resistors | -200                 |      | 200                  | uA     | 1     |

|                                  | $F_{ibyp}$            | Bypass mode                                                                                                                         | 1                    |      | 200                  | MHz    | 2     |

| Input Frequency                  | F <sub>ipII100</sub>  | 100MHz PLL mode                                                                                                                     | 50                   | 100  | 140                  | MHz    | 2     |

| input Frequency                  | F <sub>ipll125</sub>  | 125MHz PLL mode                                                                                                                     | 62.5                 | 125  | 175                  | MHz    | 2     |

|                                  | F <sub>ipll62</sub>   | 50MHz PLL mode                                                                                                                      | 25                   | 50   | 65                   | MHz    | 2     |

| Pin Inductance                   | L <sub>pin</sub>      |                                                                                                                                     |                      |      | 7                    | nΗ     | 1     |

|                                  | C <sub>IN</sub>       | Logic Inputs, except DIF_IN                                                                                                         | 1.5                  |      | 5                    | pF     | 1     |

| Capacitance                      | C <sub>INDIF_IN</sub> | DIF_IN differential clock inputs                                                                                                    | 1.5                  |      | 2.7                  | pF     | 1,6   |

|                                  | C <sub>OUT</sub>      | Output pin capacitance                                                                                                              |                      |      | 6                    | pF     | 1     |

| Clk Stabilization                | T <sub>STAB</sub>     | From V <sub>DD</sub> Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock                               |                      | 0.6  | 1                    | ms     | 1,2   |

| Input SS Modulation<br>Frequency | f <sub>MODIN</sub>    | Allowable Frequency<br>(Triangular Modulation)                                                                                      | 30                   | 31.5 | 33                   | kHz    | 1     |

| OE# Latency                      | t <sub>LATOE#</sub>   | DIF start after OE# assertion DIF stop after OE# deassertion                                                                        | 1                    |      | 3                    | clocks | 1,3   |

| Tdrive_PD#                       | t <sub>DRVPD</sub>    | DIF output enable after PD# de-assertion                                                                                            |                      | 175  | 300                  | us     | 1,3   |

| Tfall                            | t <sub>F</sub>        | Fall time of single-ended control inputs                                                                                            |                      |      | 5                    | ns     | 1,2   |

| Trise                            | $t_R$                 | Rise time of single-ended control inputs                                                                                            |                      |      | 5                    | ns     | 1,2   |

| SMBus Input Low Voltage          | $V_{ILSMB}$           | $V_{DDSMB}$ = 3.3V, see note 4 for $V_{DDSMB}$ < 3.3V                                                                               |                      |      | 0.8                  | >      | 1,4   |

| SMBus Input High Voltage         | $V_{IHSMB}$           | $V_{DDSMB}$ = 3.3V, see note 5 for $V_{DDSMB}$ < 3.3V                                                                               | 2.1                  |      | 3.6                  | V      | 1,5   |

| SMBus Output Low Voltage         | $V_{OLSMB}$           | At I <sub>PULLUP</sub>                                                                                                              |                      |      | 0.4                  | V      | 1     |

| SMBus Sink Current               | I <sub>PULLUP</sub>   | At V <sub>OL</sub>                                                                                                                  | 4                    |      |                      | mA     | 1     |

| Nominal Bus Voltage              | V <sub>DDSMB</sub>    |                                                                                                                                     | 1.7                  |      | 3.6                  | V      | 1     |

| SCLK/SDATA Rise Time             | t <sub>RSMB</sub>     | (Max VIL - 0.15) to (Min VIH + 0.15)                                                                                                |                      |      | 1000                 | ns     | 1     |

| SCLK/SDATA Fall Time             | t <sub>FSMB</sub>     | (Min VIH + 0.15) to (Max VIL - 0.15)                                                                                                |                      |      | 300                  | ns     | 1     |

| SMBus Operating Frequency        | f <sub>MAXSMB</sub>   | Maximum SMBus operating frequency                                                                                                   |                      |      | 400                  | kHz    | 1,7   |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup>Control input must be monotonic from 20% to 80% of input swing.

<sup>&</sup>lt;sup>3</sup>Time from deassertion until outputs are > 200 mV.

$<sup>^4</sup>$  For  $V_{DDSMB}$  < 3.3V,  $V_{ILSMB}$  <= 0.25 $V_{DDSMB}$ .

$<sup>^{5}</sup>$  For  $V_{DDSMB} < 3.3V$ ,  $V_{IHSMB} >= 0.7V_{DDSMB}$ .

<sup>&</sup>lt;sup>6</sup>DIF IN input.

<sup>&</sup>lt;sup>7</sup>The differential input clock must be running for the SMBus to be active.

# **Electrical Characteristics-DIF 0.7V Low Power HCSL Outputs**

TA = T<sub>COM</sub> or T<sub>IND:</sub> Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER              | SYMBOL            | CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNITS  | NOTES   |

|------------------------|-------------------|-----------------------------------------------------------------------------------------|------|------|------|--------|---------|

| 01 1                   | T.                | Scope averaging on 3.0V/ns setting                                                      | 2    | 3.2  | 4    | V/ns   | 1, 2, 3 |

| Slew rate              | Trf               | Scope averaging on 2.0V/ns setting                                                      | 1.3  | 2.3  | 3.3  | V/ns   | 1, 2, 3 |

| Slew rate matching     | ∆Trf              | Slew rate matching, Scope averaging on                                                  |      | 5.4  | 20   | %      | 1, 2, 4 |

| Voltage High           | V <sub>HIGH</sub> | Statistical measurement on single-ended signal using oscilloscope math function. (Scope | 660  | 779  | 850  | mV     | 1,7     |

| Voltage Low            | $V_{LOW}$         | using oscilloscope math function. (Scope – averaging on)                                |      | 21   | 150  | ] "" [ | 1,7     |

| Max Voltage            | Vmax              | Measurement on single ended signal using                                                |      | 835  | 1150 | mV     | 1       |

| Min Voltage            | Vmin              | absolute value. (Scope averaging off)                                                   | -300 | -42  |      | ] '''' | 1       |

| Vswing                 | Vswing            | Scope averaging off                                                                     | 300  | 1515 |      | mV     | 1,2,7   |

| Crossing Voltage (abs) | Vcross_abs        | Scope averaging off                                                                     | 250  | 409  | 550  | mV     | 1,5,7   |

| Crossing Voltage (var) | ∆-Vcross          | Scope averaging off                                                                     |      | 14   | 140  | mV     | 1, 6    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.  $C_L$  = 2pF with  $R_S$  = 33Ω for Zo = 50Ω (100Ω differential trace impedance).

# **Electrical Characteristics-Current Consumption**

TA = T<sub>COM</sub> or T<sub>IND</sub>, Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                | SYMBOL             | CONDITIONS                     | MIN | TYP   | MAX | UNITS | NOTES |

|--------------------------|--------------------|--------------------------------|-----|-------|-----|-------|-------|

| Operating Supply Current | I <sub>DDROP</sub> | VDDR, @100MHz                  |     | 4.2   | 6   | mA    | 1     |

| (PLL Mode)               | I <sub>DDOP</sub>  | VDDA + VDD1.8, @100MHz         |     | 27    | 33  | mA    | 1     |

| Operating Supply Current | I <sub>DDROP</sub> | VDDR, @100MHz                  |     | 2.2   | 3   | mA    | 1     |

| (PLL-Bypass Mode)        | I <sub>DDOP</sub>  | VDDA + VDD1.8, @100MHz         |     | 20    | 25  | mA    | 1     |

| Powerdown Current        | I <sub>DDRPD</sub> | VDDR, CKPWRGD_PD# = 0          |     | 0.014 | 0.3 | mA    | 1,2   |

| Powerdown Current        | I <sub>DDPD</sub>  | VDDA + VDD1.8, CKPWRGD_PD# = 0 |     | 0.95  | 1.2 | mA    | 1, 2  |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

<sup>&</sup>lt;sup>7</sup> At default SMBus settings.

<sup>&</sup>lt;sup>2</sup> Input clock stopped, and CKPWRGD\_PD# pin low.

# Electrical Characteristics-Output Duty Cycle, Jitter, Skew and PLL Characteristics

TA = T<sub>COM</sub> or T<sub>IND</sub>: Supply Voltage per VDD of normal operation conditions, See Test Loads for Loading Conditions

|                        |                       | •                                                |      |      |      |       |       |

|------------------------|-----------------------|--------------------------------------------------|------|------|------|-------|-------|

| PARAMETER              | SYMBOL                | CONDITIONS                                       | MIN  | TYP  | MAX  | UNITS | NOTES |

| PLL Bandwidth          | BW                    | -3dB point in High BW Mode                       | 2    | 2.7  | 4    | MHz   | 1,5   |

| FLL Balldwidth         | DVV                   | -3dB point in Low BW Mode                        | 1    | 1.4  | 2    | MHz   | 1,5   |

| PLL Jitter Peaking     | t <sub>JPEAK</sub>    | Peak Pass band Gain                              |      | 1.2  | 2    | dB    | 1     |

| Duty Cycle             | t <sub>DC</sub>       | Measured differentially, PLL Mode                | 45   | 50.1 | 55   | %     | 1     |

| Duty Cycle Distortion  | t <sub>DCD</sub>      | Measured differentially, Bypass Mode @100MHz     | -1   | -0.1 | 1    | %     | 1,3   |

| Skew, Input to Output  | t <sub>pdBYP</sub>    | Bypass Mode, V <sub>T</sub> = 50%                | 2550 | 3370 | 4200 | ps    | 1     |

| Skew, Input to Output  | t <sub>pdPLL</sub>    | PLL Mode V <sub>T</sub> = 50%                    | 0    | 112  | 200  | ps    | 1,4   |

| Skew, Output to Output | 4                     | Commercial Operating Range, V <sub>T</sub> = 50% |      | 33   | 50   | ps    | 1,4   |

| Skew, Output to Output | t <sub>sk3</sub>      | Industrial Operating Range, V <sub>T</sub> = 50% |      | 33   | 55   | ps    | 1,4   |

| Jitter, Cycle to cycle | t.                    | PLL mode                                         |      | 13   | 50   | ps    | 1,2   |

| Jitter, Cycle to Cycle | t <sub>jcyc-cyc</sub> | Additive Jitter in Bypass Mode                   |      | 0.1  | 1    | ps    | 1,2   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

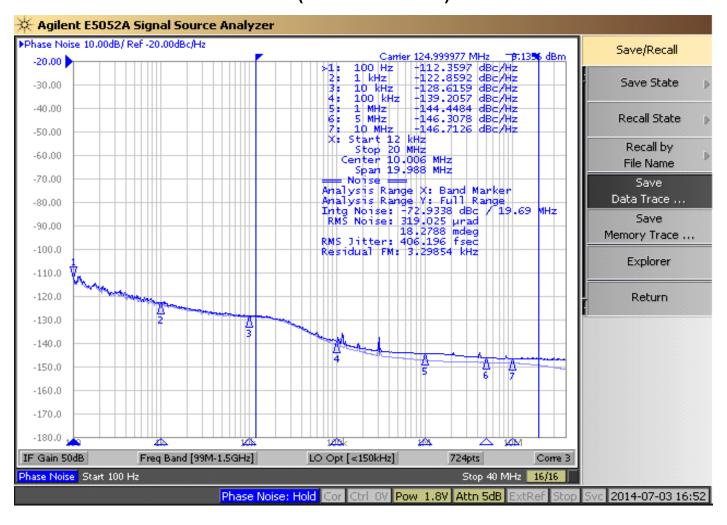

#### Electrical Characteristics-Phase Jitter Parameters - 12kHz to 20MHz

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions. See Test Loads for loading conditions.

| Parameter                      | Symbol        | Conditions           | Minimum | Typical | Maximum | Specification<br>Limit | Units | Notes   |

|--------------------------------|---------------|----------------------|---------|---------|---------|------------------------|-------|---------|

| 12k-20M Additive Phase Jitter, | +             | Fan-out Buffer Mode, |         | 156     |         | nla                    | fs    | 1 2 3   |

| Fan-out Buffer Mode            | §ph12k-20MFOB | SSC OFF, 156.25MHz   |         | 130     |         | n/a                    | (rms) | 1, 2, 3 |

#### Notes:

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>&</sup>lt;sup>4</sup> All outputs at default slew rate

<sup>&</sup>lt;sup>5</sup> The MIN/TYP/MAX values of each BW setting track each other, i.e., Low BW MAX will never occur with Hi BW MIN.

<sup>1.</sup> Applies to all differential outputs, guaranteed by design and characterization. See Test Loads for measurement setup details.

<sup>2. 12</sup>kHz to 20MHz brick wall filter.

<sup>3.</sup> For RMS values additive jitter is calculated by solving for b where  $[b = sqrt(c^2 - a^2)]$ , a is rms input jitter and c is rms total jitter.

# Electrical Characteristics-Additive PCIe Phase Jitter for Fanout Buffer Mode<sup>[7]</sup>

T<sub>AMB</sub> = over the specified operating range. Supply Voltages per normal operation conditions. See Test Loads for loading conditions.

| Parameter                                          | Symbol                    | Conditions                    | Minimum | Typical | Maximum | Limit | Units       | Notes      |

|----------------------------------------------------|---------------------------|-------------------------------|---------|---------|---------|-------|-------------|------------|

|                                                    | tjphPCleG1-CC             | PCIe Gen 1 (2.5 GT/s)         |         | 1.7     | 3.0     | 86    | ps<br>(p-p) | 1, 2       |

|                                                    | t . po. 00 00             | PCIe Gen 2 Hi Band (5.0 GT/s) |         | 0.033   | 0.049   | 3     | ps<br>(RMS) | 1, 2       |

| Additive PCIe Phase Jitter,<br>Fan-out Buffer Mode | tjphPCleG2-CC             | PCle Gen 2 Lo Band (5.0 GT/s) |         | 0.122   | 0.199   | 3.1   | ps<br>(RMS) | 1, 2       |

| (Common Clocked Architecture)                      | tjphPCleG3-CC             | PCIe Gen 3 (8.0 GT/s)         |         | 0.059   | 0.098   | 1     | ps<br>(RMS) | 1, 2       |

|                                                    | <sup>t</sup> jphPCleG4-CC | PCIe Gen 4 (16.0 GT/s)        |         | 0.059   | 0.098   | 0.5   | ps<br>(RMS) | 1, 2, 3, 4 |

|                                                    | tjphPCleG5-CC             | PCIe Gen 5 (32.0 GT/s)        |         | 0.023   | 0.038   | 0.15  | ps<br>(RMS) | 1, 2, 3, 5 |

|                                                    | tjphPCleG1-SRIS           | PCIe Gen 1 (2.5 GT/s)         |         | 0.175   | 0.038   | n/a   | ps<br>(RMS) | 1, 2, 6    |

| Additive PCIe Phase Jitter,                        | tjphPCleG2-SRIS           | PCIe Gen 2 (5.0 GT/s)         |         | 0.156   | 0.275   | n/a   | ps<br>(RMS) | 1, 2, 6    |

| Fan-out Buffer Mode (SRIS Architecture)            | tjphPCleG3-SRIS           | PCIe Gen 3 (8.0 GT/s)         |         | 0.041   | 0.247   | n/a   | ps<br>(RMS) | 1, 2, 6    |

| (ONO Aramedure)                                    | tjphPCleG4-SRIS           | PCIe Gen 4 (16.0 GT/s)        |         | 0.043   | 0.064   | n/a   | ps<br>(RMS) | 1, 2, 6    |

|                                                    | tjphPCleG5-SRIS           | PCIe Gen 5 (32.0 GT/s)        |         | 0.036   | 0.066   | n/a   | ps<br>(RMS) | 1, 2, 6    |

#### Notes:

- 1. The Refclk jitter is measured after applying the filter functions found in PCI Express Base Specification 5.0, Revision 1.0. See the Test Loads section of the data sheet for the exact measurement setup. The total Ref Clk jitter limits for each data rate are listed for convenience. The worst case results for each data rate are summarized in this table. If oscilloscope data is used, equipment noise is removed from all results.

- 2. Jitter measurements shall be made with a capture of at least 100,000 clock cycles captured by a real-time oscilloscope (RTO) with a sample rate of 20 GS/s or greater. Broadband oscilloscope noise must be minimized in the measurement. The measured PP jitter is used (no extrapolation) for RTO measurements. Alternately Jitter measurements may be used with a Phase Noise Analyzer (PNA) extending (flat) and integrating and folding the frequency content up to an offset from the carrier frequency of at least 200 MHz (at 300 MHz absolute frequency) below the Nyquist frequency. For PNA measurements for the 2.5 GT/s data rate, the RMS jitter is converted to peak to peak jitter using a multiplication factor of 8.83. In the case where real-time oscilloscope and PNA measurements have both been done and produce different results the RTO result must be used.

- 3. SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2 MHz taking care to minimize removal of any non-SSC content.

- 4. Note that 0.7 ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 5. Note that 0.25 ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 6. The PCI Express Base Specification 5.0, Revision 1.0 provides the filters necessary to calculate SRIS jitter values, however, it does not provide specification limits, hence the n/a in the Limit column. SRIS values are informative only. In general, a clock operating in an SRIS system must be twice as good as a clock operating in a Common Clock system. For RMS values, twice as good is equivalent to dividing the CC value by  $\sqrt{2}$ . And additional consideration is the value for which to divide by  $\sqrt{2}$ . The conservative approach is to divide the ref clock jitter limit, and the case can be made for dividing the channel simulation values by  $\sqrt{2}$ , if the ref clock is close to the Tx clock input. An example for Gen4 is as follows. A "rule-of-thumb" SRIS limit would be either 0.5ps RMS/ $\sqrt{2}$  = 0.35ps RMS if the clock chip is far from the clock input, or 0.7ps RMS/ $\sqrt{2}$  = 0.5ps RMS if the clock chip is near the clock input.

- 7. Additive jitter for RMS values is calculated by solving for b where  $b = \sqrt{(c^2 a^2)}$ , and a is rms input jitter and c is rms output jitter.

# Additive Phase Jitter Plot: 125M (12kHz to 20MHz)

### **General SMBus Serial Interface Information**

#### **How to Write**

- · Controller (host) sends a start bit

- · Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- Controller (host) sends the byte count = X

- Renesas clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- Renesas clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

|           | Index Blo  | ock V  | Vrite Operation          |

|-----------|------------|--------|--------------------------|

| Controll  | er (Host)  |        | Renesas (Slave/Receiver) |

| Т         | starT bit  |        |                          |

| Slave /   | Address    |        |                          |

| WR        | WRite      |        |                          |

|           |            |        | ACK                      |

| Beginnin  | g Byte = N |        |                          |

|           |            |        | ACK                      |

| Data Byte | Count = X  |        |                          |

|           |            |        | ACK                      |

| Beginnir  | ng Byte N  | ×      |                          |

|           |            | X Byte | ACK                      |

| 0         |            |        |                          |

| 0         |            |        | 0                        |

| 0         |            |        | 0                        |

|           |            |        | 0                        |

| Byte N    | l + X - 1  |        |                          |

|           |            |        | ACK                      |

| Р         | stoP bit   |        |                          |

Note: SMBus address is latched on SADR pin.

#### How to Read

- Controller (host) will send a start bit

- Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- · Controller (host) will send a separate start bit

- · Controller (host) sends the read address

- Renesas clock will acknowledge

- Renesas clock will send the data byte count = X

- Renesas clock sends Byte N+X-1

- Renesas clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- · Controller (host) will need to acknowledge each byte

- · Controller (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

|      | Index Block Read Operation |        |                   |  |  |  |  |  |

|------|----------------------------|--------|-------------------|--|--|--|--|--|

| Co   | ntroller (Host)            |        | Renesas           |  |  |  |  |  |

| Т    | starT bit                  |        |                   |  |  |  |  |  |

| SI   | Slave Address              |        |                   |  |  |  |  |  |

| WR   | WRite                      |        |                   |  |  |  |  |  |

|      |                            |        | ACK               |  |  |  |  |  |

| Begi | nning Byte = N             |        |                   |  |  |  |  |  |

|      |                            |        | ACK               |  |  |  |  |  |

| RT   | Repeat starT               |        |                   |  |  |  |  |  |

| SI   | ave Address                |        |                   |  |  |  |  |  |

| RD   | ReaD                       |        |                   |  |  |  |  |  |

|      |                            |        | ACK               |  |  |  |  |  |

|      |                            |        |                   |  |  |  |  |  |

|      |                            |        | Data Byte Count=X |  |  |  |  |  |

|      | ACK                        |        |                   |  |  |  |  |  |

|      |                            |        | Beginning Byte N  |  |  |  |  |  |

|      | ACK                        |        |                   |  |  |  |  |  |

|      |                            | क      | 0                 |  |  |  |  |  |

|      | 0                          | X Byte | 0                 |  |  |  |  |  |

|      | 0                          | ×      | 0                 |  |  |  |  |  |

|      | 0                          |        |                   |  |  |  |  |  |

|      |                            |        | Byte N + X - 1    |  |  |  |  |  |

| N    | Not acknowledge            |        |                   |  |  |  |  |  |

| Р    | stoP bit                   |        |                   |  |  |  |  |  |

SMBus Table: Output Enable Register <sup>1</sup>

| Byte 0 | Name     | Control Function | Type | 0       | 1       | Default |

|--------|----------|------------------|------|---------|---------|---------|

| Bit 7  |          | Reserved         |      |         |         | 1       |

| Bit 6  | DIF OE3  | Output Enable    | RW   | Low/Low | Enabled | 1       |

| Bit 5  | DIF OE2  | Output Enable    | RW   | Low/Low | Enabled | 1       |

| Bit 4  | Reserved |                  |      |         |         |         |

| Bit 3  | DIF OE1  | Output Enable    | RW   | Low/Low | Enabled | 1       |

| Bit 2  |          | Reserved         |      |         |         | 1       |

| Bit 1  | DIF OE0  | Output Enable    | RW   | Low/Low | Enabled | 1       |

| Bit 0  |          | Reserved         |      |         |         | 1       |

<sup>1.</sup> A low on these bits will override the OE# pin and force the differential output Low/Low

SMBus Table: PLL Operating Mode and Output Amplitude Control Register

| Byte 1 | Name            | Control Function                                 | Type            | 0                            | 1                 | Default |

|--------|-----------------|--------------------------------------------------|-----------------|------------------------------|-------------------|---------|

| Bit 7  | PLLMODERB1      | PLL Mode Readback Bit 1                          | R               | See PLL Operating Mode Table |                   | Latch   |

| Bit 6  | PLLMODERB0      | PLL Mode Readback Bit 0                          | R               | See Fill Opera               | ing wode rable    | Latch   |

| Bit 5  | PLLMODE SWCNTRL | Enable SW control of PLL Mode                    | D///            | Values in B1[7:6]            | Values in B1[4:3] | 0       |

| ыгэ    | FEEWODE_SWONTKE | Lilable 3W control of FEE Wode                   | 1700            | set PLL Mode                 | set PLL Mode      | O       |

| Bit 4  | PLLMODE1        | PLL Mode Control Bit 1                           | RW <sup>1</sup> | See PLL Operat               | ting Mode Table   | 0       |

| Bit 3  | PLLMODE0        | PLL Mode Control Bit 0                           | RW <sup>1</sup> | See FLL Opera                | iling Mode Table  | 0       |

| Bit 2  |                 | Reserved                                         |                 |                              |                   | 1       |

| Bit 1  | AMPLITUDE 1     | Centrale Output Amplitude RW 00 = 0.6V 01 = 0.7V |                 | 01 = 0.7V                    | 1                 |         |

| Bit 0  | AMPLITUDE 0     | Controls Output Amplitude                        | RW              | 10= 0.8V                     | 11 = 0.9V         | 0       |

<sup>1.</sup> B1[5] must be set to a 1 for these bits to have any effect on the part.

#### SMBus Table: DIF Slew Rate Control Register

| Byte 2 | Name             | Control Function    | Type | 0      | 1      | Default |

|--------|------------------|---------------------|------|--------|--------|---------|

| Bit 7  |                  | Reserved            |      |        |        | 1       |

| Bit 6  | SLEWRATESEL DIF3 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |

| Bit 5  | SLEWRATESEL DIF2 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |

| Bit 4  | Reserved         |                     |      |        |        |         |

| Bit 3  | SLEWRATESEL DIF1 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |

| Bit 2  |                  | Reserved            |      |        |        | 1       |

| Bit 1  | SLEWRATESEL DIF0 | Slew Rate Selection | RW   | 2 V/ns | 3 V/ns | 1       |

| Bit 0  |                  | Reserved            |      |        |        | 1       |

### SMBus Table: Frequency Select Control Register

| Byte 3 | Name           | Control Function                 | Туре            | 0                                                        | 1              | Default |

|--------|----------------|----------------------------------|-----------------|----------------------------------------------------------|----------------|---------|

| Bit 7  |                | Reserved                         |                 |                                                          |                | 1       |

| Bit 6  | Reserved       |                                  |                 |                                                          |                |         |

| Bit 5  | FREQ_SEL_EN    | Enable SW selection of frequency | RW              | SW frequency SW frequency change disabled change enabled |                | 0       |

| Bit 4  | FSEL1          | Freq. Select Bit 1               | RW <sup>1</sup> | See Frequency                                            | v Select Table | 0       |

| Bit 3  | FSEL0          | Freq. Select Bit 0               | RW <sup>1</sup> | See Hequello                                             | y Select Table | 0       |

| Bit 2  |                | Reserved                         |                 |                                                          |                | 1       |

| Bit 1  | Reserved       |                                  |                 |                                                          |                | 1       |

| Bit 0  | SLEWRATESEL FB | Adjust Slew Rate of FB           | RW              | 2 V/ns                                                   | 3 V/ns         | 1       |

<sup>1.</sup> B3[5] must be set to a 1 for these bits to have any effect on the part.

#### Byte 4 is Reserved and reads back 'hFF

SMBus Table: Revision and Vendor ID Register

| Byte 5 | Name | Control Function | Type | 0            | 1          | Default |

|--------|------|------------------|------|--------------|------------|---------|

| Bit 7  | RID3 |                  | R    |              | 0          |         |

| Bit 6  | RID2 | Revision ID      | R    | A rev =      | 0          |         |

| Bit 5  | RID1 |                  | R    | A 16V -      | 0          |         |

| Bit 4  | RID0 |                  | R    |              | 0          |         |

| Bit 3  | VID3 |                  | R    |              |            | 0       |

| Bit 2  | VID2 | VENDOR ID        | R    | 0001         | 0001 = IDT |         |

| Bit 1  | VID1 | VENDOR ID        | R    | 1 0001 - 101 |            | 0       |

| Bit 0  | VID0 |                  | R    |              |            | 1       |

SMBus Table: Device Type/Device ID

| Byte 6 | Name         | Control Function | Type | 0             | 1            | Default |

|--------|--------------|------------------|------|---------------|--------------|---------|

| Bit 7  | Device Type1 | Device Type      | R    | 00 = FGV,     | 01 = DBV,    | 0       |

| Bit 6  | Device Type0 | Device Type      | R    | 10 = DMV, 1   | 1            |         |

| Bit 5  | Device ID5   |                  | R    |               |              | 0       |

| Bit 4  | Device ID4   |                  | R    |               | 0            |         |

| Bit 3  | Device ID3   | Device ID        | R    | 000100 bina   | ny or 04 boy | 0       |

| Bit 2  | Device ID2   | Device iD        | R    | 000 100 billa | ry or o4 nex | 1       |

| Bit 1  | Device ID1   |                  | R    | 1             |              | 0       |

| Bit 0  | Device ID0   |                  | R    |               |              | 0       |

SMBus Table: Byte Count Register

| Ombas Table: Byte Count Register |          |                        |      |                       |                        |         |  |

|----------------------------------|----------|------------------------|------|-----------------------|------------------------|---------|--|

| Byte 7                           | Name     | Control Function       | Type | 0                     | 1                      | Default |  |

| Bit 7                            | Reserved |                        |      |                       |                        | 0       |  |

| Bit 6                            | Reserved |                        |      |                       |                        | 0       |  |

| Bit 5                            | Reserved |                        |      |                       |                        | 0       |  |

| Bit 4                            | BC4      |                        | RW   |                       |                        | 0       |  |

| Bit 3                            | BC3      |                        | RW   | Writing to this regis | ter will configure how | 1       |  |

| Bit 2                            | BC2      | Byte Count Programming | RW   | many bytes will be    | read back, default is  | 0       |  |

| Bit 1                            | BC1      |                        | RW   | = 8                   | bytes.                 | 0       |  |

| Bit 0                            | BC0      |                        | RW   |                       |                        | 0       |  |

# **Marking Diagrams**

#### Notes:

- 1. "LOT" is the lot sequence number.

- 2. "COO" denotes country of origin.

- 3. YYWW is the last two digits of the year and week that the part was assembled.

- 4. Line 2: truncated part number

- 5. "L" denotes RoHS compliant package.

- 6. "I" denotes industrial temperature range device.

# **Thermal Characteristics**

| PARAMETER          | SYMBOL                | CONDITIONS                      | PKG              | TYP<br>VALUE | UNITS | NOTES |

|--------------------|-----------------------|---------------------------------|------------------|--------------|-------|-------|

|                    | $\theta_{JC}$         | Junction to Case                | 142<br>2.4<br>39 | 42           | °C/W  | 1     |

|                    | $\theta_{Jb}$         | Junction to Base                |                  | °C/W         | 1     |       |

| Thermal Resistance | $\theta_{JA0}$        | Junction to Air, still air      |                  | °C/W         | 1     |       |

| memai Resistance   | $\theta_{\text{JA1}}$ | Junction to Air, 1 m/s air flow | INLG32           | 33           | °C/W  | 1     |

|                    | $\theta_{JA3}$        | Junction to Air, 3 m/s air flow |                  | 28           | °C/W  | 1     |

|                    | $\theta_{JA5}$        | Junction to Air, 5 m/s air flow |                  | 27           | °C/W  | 1     |

<sup>&</sup>lt;sup>1</sup>ePad soldered to board

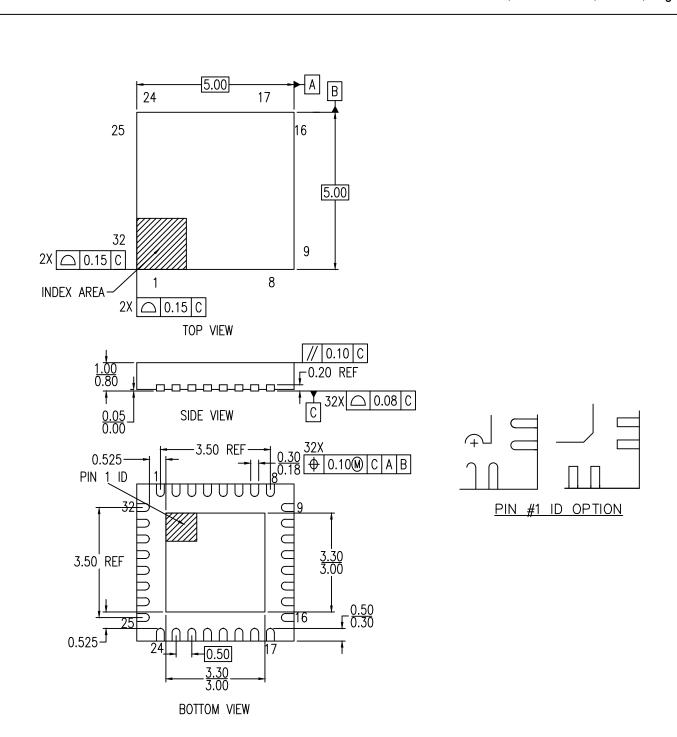

# **Package Outline Drawings**

The package outline drawings are located at the end of this document and are accessible from the Renesas website. The package information is the most current data available and is subject to change without revision of this document.

32-VFQFPN (NLG32P1)

# **Ordering Information**

| Part/Order Number | Part/Order Number   Shipping Packaging |               | Temperature   |  |

|-------------------|----------------------------------------|---------------|---------------|--|

| 9DBV0431AKLF      | Trays                                  | 32-pin VFQFPN | 0 to +70° C   |  |

| 9DBV0431AKLFT     | Tape and Reel                          | 32-pin VFQFPN | 0 to +70° C   |  |

| 9DBV0431AKILF     | Trays                                  | 32-pin VFQFPN | -40 to +85° C |  |

| 9DBV0431AKILFT    | Tape and Reel                          | 32-pin VFQFPN | -40 to +85° C |  |

<sup>&</sup>quot;LF" suffix to the part number are the Pb-Free configuration and are RoHS compliant.

<sup>&</sup>quot;A" is the device revision designator (will not correlate with the datasheet revision).

# **Revision History**

| Revision Date     | Description                                                                                                                                         |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | 1. Removed "Differential" from DS title and Recommended Application, corrected typo's in Description.                                               |  |  |  |

|                   | 2. Corrected spelling error in pullup/pulldown text under pinout                                                                                    |  |  |  |

|                   | 3. Updated all electrical tables and added "Industry Limit" column to "Phase Jitter Parameters".                                                    |  |  |  |

| August 13, 2012   | 4. Updated Byte3[0] to be consistent with Byte 2. Updated Byte6[7:6] definition.                                                                    |  |  |  |

|                   | 5. Added thermal data to page 12.                                                                                                                   |  |  |  |

|                   | 6. Added NLG32 to "Package Outline and Package Dimensions" on page 13.                                                                              |  |  |  |

|                   | 7. Move to final                                                                                                                                    |  |  |  |

|                   | 1. "Input/Supply/Common Parameters" table modified as follows:                                                                                      |  |  |  |

|                   | a. Updated Single-ended input logic thresholds to include missing mid-level on tri-level inputs. Adjusted logic                                     |  |  |  |

|                   | thresholds as follows:                                                                                                                              |  |  |  |

|                   | i. Changed VIH min. from 0.65*VDD to 0.75*VDD                                                                                                       |  |  |  |

|                   | ii. Changed VIL max. from 0.35*VDD to 0.25*VDD                                                                                                      |  |  |  |

|                   | iii. Added missing mid-level input voltage spec (VIM) of 0.4*VDD to 0.6*VDD.                                                                        |  |  |  |

|                   | iv. Clarified conditions for these specifications, accordingly.                                                                                     |  |  |  |

|                   | b. Clarified the operating conditions and voltages of the SMBus to make it clear that the SMBus operates at <3.3V                                   |  |  |  |

|                   | by addition of footnotes 4 and 5 to "Input/Supply/Common Parameters" table.                                                                         |  |  |  |

|                   | 2. Slight modifications of Slew Rates and typical values in the "DIF 0.7V Low Power Differential Outputs" table.                                    |  |  |  |

|                   | 3. "Current Consumption" table modifed as follows:                                                                                                  |  |  |  |

|                   | a. Overall current consumption values lowered                                                                                                       |  |  |  |

| February 28, 2013 | b. VDDA is now grouped with VDD1.8 instead of VDDR                                                                                                  |  |  |  |

| ,                 | c. Added separate current specs for PLL bypass mode.                                                                                                |  |  |  |

|                   | d. Clarified that CKPWRDG PD# is low for power down current.                                                                                        |  |  |  |

|                   | 4. "Output Duty Cycle, Jitter, Skew and PLL Characterisitics" table modifed as follows:                                                             |  |  |  |

|                   | a. Bypass mode Input-to-Output skew changed from 3000 to 4500ps to 2550 to 4200ps. Typical value reduced                                            |  |  |  |

|                   | from 3500ps to 3370ps.                                                                                                                              |  |  |  |

|                   | b. Separate Output-to-Output skew spec added for Industrial temp.                                                                                   |  |  |  |

|                   | c. Additive cycle-to-cycle jitter spec reduced to 1ps max.                                                                                          |  |  |  |

|                   | 5. "Phase Jitter Parameters" modifed as follows:                                                                                                    |  |  |  |

|                   | a. Corrected typo in PLL Mode conditions for tjPHSGMII. Frequency integration range is 1.5MHz to 10MHz. Bypass                                      |  |  |  |

|                   | mode conditions were correct.                                                                                                                       |  |  |  |

|                   | b. Removed old footnote 4 for PCle Gen3 specs that indicated "Pending ratification by PCI SIG". The PCle Gen3                                       |  |  |  |

|                   | specs are ratified. Footnotes renumbered accordingly.                                                                                               |  |  |  |

|                   | Updated front page text for consistency and updated block diagram resistor colors to highlight internal resistors.                                  |  |  |  |

|                   | 2. Updated max frequency of 100MHz PLL mode from 110MHz to 140MHz                                                                                   |  |  |  |

|                   | 3. Updated max frequency of 125MHz PLL mode from 137.5MHz to 175MHz                                                                                 |  |  |  |

| November 26, 2014 | 4. Updated max frequency of 50MHz PLL mode from 55MHz to 65MHz                                                                                      |  |  |  |

|                   | 5. Updated Key Specifications with addtive phase jitter.                                                                                            |  |  |  |

|                   | 6. Added additive phase jitter plot to specifications.                                                                                              |  |  |  |

|                   | Added additive priase files plot to specifications.     Updated block diagram with new format showing individual outputs instead of bussed outputs. |  |  |  |

| April 3, 2015     | Updated pin out and pin descriptions to show ePad on package connected to ground.                                                                   |  |  |  |

|                   | Updated max frequency of 100MHz PLL mode to 140MHz                                                                                                  |  |  |  |

| April 22 2016     |                                                                                                                                                     |  |  |  |

| April 22, 2016    | 2. Updated max frequency of 125MHz PLL mode to 175MHz                                                                                               |  |  |  |

|                   | 3. Updated max frequency of 50MHz PLL mode to 65MHz                                                                                                 |  |  |  |

|                   | 1. Updated document title.                                                                                                                          |  |  |  |

| lulu 00 0004      | 2. Updated Recommended Applications.                                                                                                                |  |  |  |

| July 29, 2021     | 3. Updated Key Specifications.                                                                                                                      |  |  |  |

|                   | 4. Updated Package Outline Drawings section.                                                                                                        |  |  |  |

|                   | 5. Updated Phase Jitter tables.                                                                                                                     |  |  |  |

# 32-VFQFPN, Package Outline Drawing

5.0 x 5.0 x 0.90 mm Body, Epad 3.15 x 3.15 mm. NLG32P1, PSC-4171-01, Rev 02, Page 1

#### NOTE:

- 1. ALL DIMENSION ARE IN MM. ANGLES IN DEGREES.

- 2. COPLANARITY APPLIE TO THE EXPOSED PAD AS WELL AS THE TERMINALS. COPLANARITY SHALL NOT EXCEED 0.08 MM.

- 3. WARPAGE SHALL NOT EXCEED 0.10 MM.

- 4. PIN LOCATION IS UNDENTIFIED BY EITHER CHAMFER OR NOTCH.

# 32-VFQFPN, Package Outline Drawing

5.0 x 5.0 x 0.90 mm Body, Epad 3.15 x 3.15 mm. NLG32P1, PSC-4171-01, Rev 02, Page 2

#### RECOMMENDED LAND PATTERN DIMENSION

- 1. ALL DIMENSIONS ARE IN MM. ANGLES IN DEGREES. 2. TOP DOWN VIEW. AS VIEWED ON PCB.

- 3. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| Package Revision History |                            |                 |  |  |

|--------------------------|----------------------------|-----------------|--|--|

| Date Created Rev No.     |                            | Description     |  |  |

| April 12, 2018           | 12, 2018 Rev 02 New Format |                 |  |  |

| Feb 8, 2016              | Rev 01                     | Added "k: Value |  |  |