# **RENESAS** 19-Output Differential Zbuffer for PCIe Gen2/3 and QPI

# 9ZX21901C

# DATASHEET

# **General Description**

The 9ZX21901 is Intel DB1900Z Differential Buffer suitable for PCI-Express Gen3 or QPI applications. The part is backwards compatible to PCIe Gen1 and Gen2. A fixed external feedback maintains low drift for critical QPI applications. In bypass mode, the 9ZX21901 can provide outputs up to 400MHz.

# **Recommended Application**

• 19-output PCIe Gen3/QPI buffer with fixed feedback for Romley platforms

# **Output Features**

19 – 0.7V current mode differential HCSL output pairs

### **Key Specifications**

- Cycle-to-cycle jitter: < 50ps

- Output-to-output skew: <65ps</li>

- Input-to-output delay: Fixed at 0 ps

- Input-to-output delay variation: <50ps</li>

- Phase jitter: PCIe Gen3 < 1ps rms</li>

- Phase jitter: QPI 9.6GB/s < 0.2ps rms</li>

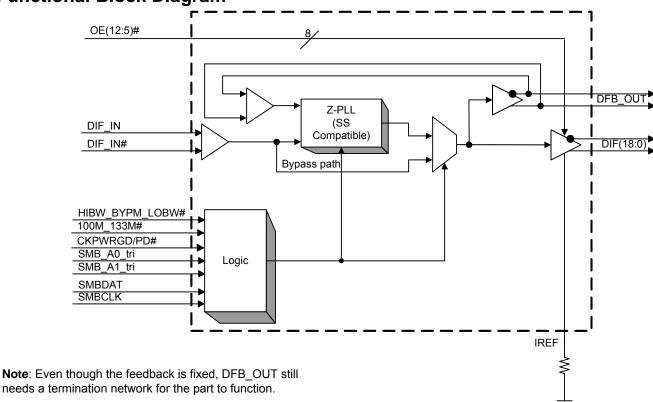

## **Functional Block Diagram**

### Features/Benefits

- Fixed feedback path/ 0ps input-to-output delay

- 9 Selectable SMBus addresses; Multiple devices can share same SMBus segment

- 8 dedicated OE# pins; hardware control of outputs

- PLL or bypass mode; PLL can dejitter incoming clock

- Selectable PLL BW; minimizes jitter peaking in downstream PLL's

- Spread spectrum compatible; tracks spreading input clock for EMI reduction

- SMBus Interface; unused outputs can be disabled

- 100MHz & 133.33MHz PLL mode; legacy QPI support

- Undriven differential outputs in Power Down mode for maximum power savings

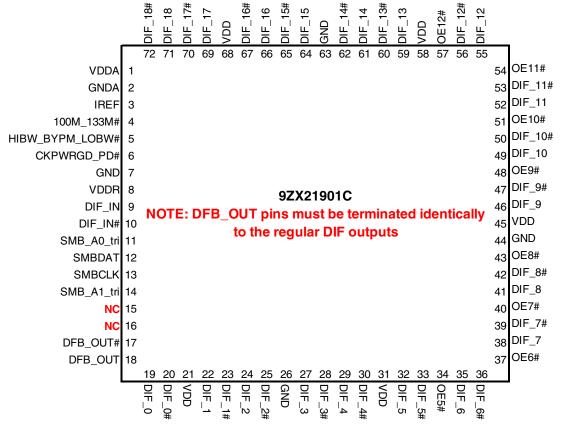

# **Pin Configuration**

72-pin VFQFPN

#### Functionality at Power Up (PLL Mode)

| 100M_133M# | DIF_IN<br>(MHz) | DIF_x<br>(MHz) |  |  |

|------------|-----------------|----------------|--|--|

| 1          | 100.00          | DIF_IN         |  |  |

| 0          | 133.33          | DIF_IN         |  |  |

### PLL Operating Mode Readback Table

| HiBW_BypM_LoBW# | Byte0, bit 7 | Byte 0, bit 6 |

|-----------------|--------------|---------------|

| Low (Low BW)    | 0            | 0             |

| Mid (Bypass)    | 0            | 1             |

| High (High BW)  | 1            | 1             |

#### **PLL Operating Mode**

| HiBW_BypM_LoBW# | MODE      |

|-----------------|-----------|

| Low             | PLL Lo BW |

| Mid             | Bypass    |

| High            | PLL Hi BW |

NOTE: PLL is OFF in Bypass Mode

#### **Tri-level Input Thresholds**

| Level | Voltage                           |

|-------|-----------------------------------|

| Low   | <0.8V                             |

| Mid   | 1.2 <vin<1.8v< td=""></vin<1.8v<> |

| High  | Vin > 2.2V                        |

**Power Connections**

| Pin Nu                | umber      |              |

|-----------------------|------------|--------------|

| VDD                   | GND        | Description  |

| 1                     | 2          | Analog PLL   |

| 8                     | 7          | Analog Input |

| 21, 31, 45,<br>58, 68 | 26, 44, 63 | DIF clocks   |

#### 9ZX21901 SMBus Addressing

| Pi         | n          | SMBus Address    |

|------------|------------|------------------|

| SMB_A1_tri | SMB_A0_tri | (Rd/Wrt bit = 0) |

| 0          | 0          | D8               |

| 0          | М          | DA               |

| 0          | 1          | DE               |

| М          | 0          | C2               |

| М          | М          | C4               |

| М          | 1          | C6               |

| 1          | 0          | CA               |

| 1          | М          | CC               |

| 1          | 1          | CE               |

# **Pin Descriptions**

| PIN # | PIN NAME        | <b>PIN TYPE</b> | DESCRIPTION                                                                                                                                                                                                                                                              |

|-------|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VDDA            | PWR             | 3.3V power for the PLL core.                                                                                                                                                                                                                                             |

| 2     | GNDA            | GND             | Ground pin for the PLL core.                                                                                                                                                                                                                                             |

| 3     | IREF            | OUT             | This pin establishes the reference for the differential current-mode output pairs.<br>It requires a fixed precision resistor to ground. 4750hm is the standard value<br>for 1000hm differential impedance. Other impedances require different values.<br>See data sheet. |

| 4     | 100M_133M#      | IN              | Input to select operating frequency<br>1 = 100MHz, 0 = 133.33MHz                                                                                                                                                                                                         |

| 5     | HIBW_BYPM_LOBW# | IN              | Trilevel input to select High BW, Bypass or Low BW mode.<br>See PLL Operating Mode Table for Details.                                                                                                                                                                    |

| 6     | CKPWRGD_PD#     | IN              | 3.3V Input notifies device to sample latched inputs and start up on first high assertion, or exit Power Down Mode on subsequent assertions. Low enters Power Down Mode.                                                                                                  |

| 7     | GND             | GND             | Ground pin.                                                                                                                                                                                                                                                              |

| 8     | VDDR            | PWR             | 3.3V power for differential input clock (receiver). This VDD should be treated as an analog power rail and filtered appropriately.                                                                                                                                       |

| 9     | DIF_IN          | IN              | 0.7 V Differential True input                                                                                                                                                                                                                                            |

| 10    | DIF_IN#         | IN              | 0.7 V Differential Complementary Input                                                                                                                                                                                                                                   |

| 11    | SMB_A0_tri      | IN              | SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A1 to decode 1 of 9 SMBus Addresses.                                                                                                                                                 |

| 12    | SMBDAT          | I/O             | Data pin of SMBUS circuitry, 5V tolerant                                                                                                                                                                                                                                 |

| 13    | SMBCLK          | IN              | Clock pin of SMBUS circuitry, 5V tolerant                                                                                                                                                                                                                                |

| 14    | SMB_A1_tri      | IN              | SMBus address bit. This is a tri-level input that works in conjunction with the SMB_A0 to decode 1 of 9 SMBus Addresses.                                                                                                                                                 |

| 15    | NC              | N/A             | No Connection.                                                                                                                                                                                                                                                           |

| 16    | NC              | N/A             | No Connection.                                                                                                                                                                                                                                                           |

| 17    | DFB_OUT#        | OUT             | Complementary half of differential feedback output, provides feedback signal to the PLL for synchronization with input clock to eliminate phase error.                                                                                                                   |

| 18    | DFB_OUT         | OUT             | True half of differential feedback output, provides feedback signal to the PLL for synchronization with the input clock to eliminate phase error.                                                                                                                        |

| 19    | DIF_0           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 20    | DIF_0#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

| 21    | VDD             | PWR             | Power supply, nominal 3.3V                                                                                                                                                                                                                                               |

| 22    | DIF_1           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 23    | DIF_1#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

| 24    | DIF_2           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 25    | DIF_2#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

| 26    | GND             | GND             | Ground pin.                                                                                                                                                                                                                                                              |

| 27    | DIF_3           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 28    | DIF_3#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

| 29    | DIF_4           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 30    | DIF_4#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

| 31    | VDD             | PWR             | Power supply, nominal 3.3V                                                                                                                                                                                                                                               |

| 32    | DIF_5           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 33    | DIF_5#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

| 34    | OE5#            | IN              | Active low input for enabling DIF pair 5.<br>1 =disable outputs, 0 = enable outputs                                                                                                                                                                                      |

| 35    | DIF_6           | OUT             | 0.7V differential true clock output                                                                                                                                                                                                                                      |

| 36    | DIF_6#          | OUT             | 0.7V differential Complementary clock output                                                                                                                                                                                                                             |

# Pin Descriptions (cont.)

| PIN #        | PIN NAME    | PIN TYPE | DESCRIPTION                                                       |

|--------------|-------------|----------|-------------------------------------------------------------------|

| 37           | OE6#        | IN       | Active low input for enabling DIF pair 6.                         |

| 37           | OE0#        | IIN      | 1 =disable outputs, 0 = enable outputs                            |

| 38           | DIF_7       | OUT      | 0.7V differential true clock output                               |

| 39           | DIF_7#      | OUT      | 0.7V differential Complementary clock output                      |

| 40           | OE7#        | IN       | Active low input for enabling DIF pair 7.                         |

| 40           |             |          | 1 =disable outputs, 0 = enable outputs                            |

| 41           | DIF_8       | OUT      | 0.7V differential true clock output                               |

| 42           | DIF_8#      | OUT      | 0.7V differential Complementary clock output                      |

| 43           | OE8#        | IN       | Active low input for enabling DIF pair 8.                         |

|              |             |          | 1 =disable outputs, 0 = enable outputs                            |

| 44           | GND         | GND      | Ground pin.                                                       |

| 45           | VDD         | PWR      | Power supply, nominal 3.3V                                        |

| 46           | DIF_9       | OUT      | 0.7V differential true clock output                               |

| 47           | DIF_9#      | OUT      | 0.7V differential Complementary clock output                      |

| 48           | OE9#        | IN       | Active low input for enabling DIF pair 9.                         |

|              |             |          | 1 =disable outputs, 0 = enable outputs                            |

| 49           | DIF_10      | OUT      | 0.7V differential true clock output                               |

| 50           | DIF_10#     | OUT      | 0.7V differential Complementary clock output                      |

| 51           | OE10#       | IN       | Active low input for enabling DIF pair 10.                        |

| 50           |             |          | 1 =disable outputs, 0 = enable outputs                            |

| 52           | DIF_11      | OUT      | 0.7V differential true clock output                               |

| 53           | DIF_11#     | OUT      | 0.7V differential Complementary clock output                      |

| 54           | OE11#       | IN       | Active low input for enabling DIF pair 11.                        |

|              |             | OUT      | 1 =disable outputs, 0 = enable outputs                            |

| 55           | DIF_12      | OUT      | 0.7V differential true clock output                               |

| 56           | DIF_12#     | OUT      | 0.7V differential Complementary clock output                      |

| 57           | OE12#       | IN       | Active low input for enabling DIF pair 12.                        |

| 50           | VDD         | PWR      | 1 =disable outputs, 0 = enable outputs                            |

| 58<br>59     | DIF_13      | OUT      | Power supply, nominal 3.3V<br>0.7V differential true clock output |

| - 59<br>- 60 | DIF_13#     | OUT      | 0.7V differential Complementary clock output                      |

| 61           | DIF_14      | OUT      | 0.7V differential complementaly clock output                      |

| 62           | DIF_14#     | OUT      | 0.7V differential Complementary clock output                      |

| 63           |             | GND      | Ground pin.                                                       |

| 64           | DIF_15      | OUT      | 0.7V differential true clock output                               |

| 65           | <br>DIF_15# | OUT      | 0.7V differential Complementary clock output                      |

| 66           | DIF_16      | OUT      | 0.7V differential true clock output                               |

| 67           | <br>DIF_16# | OUT      | 0.7V differential Complementary clock output                      |

| 68           | VDD         | PWR      | Power supply, nominal 3.3V                                        |

| 69           | DIF_17      | OUT      | 0.7V differential true clock output                               |

| 70           | DIF_17#     | OUT      | 0.7V differential Complementary clock output                      |

| 71           | DIF_18      | OUT      | 0.7V differential true clock output                               |

| 72           | DIF_18#     | OUT      | 0.7V differential Complementary clock output                      |

# **Electrical Characteristics – Absolute Maximum Ratings**

| PARAMETER                 | SYMBOL          | CONDITIONS                 | MIN     | TYP | МАХ            | UNITS | NOTES |

|---------------------------|-----------------|----------------------------|---------|-----|----------------|-------|-------|

| 3.3V Core Supply Voltage  | VDDA            |                            |         |     | 4.6            | V     | 1,2   |

| 3.3V Logic Supply Voltage | VDD             |                            |         |     | 4.6            | V     | 1,2   |

| Input Low Voltage         | V <sub>IL</sub> |                            | GND-0.5 |     |                | V     | 1     |

| Input High Voltage        | V <sub>IH</sub> | Except for SMBus interface |         |     | $V_{DD}$ +0.5V | V     | 1     |

| Input High Voltage        | VIHSMB          | SMBus clock and data pins  |         |     | 5.5V           | V     | 1     |

| Storage Temperature       | Ts              |                            | -65     |     | 150            | °C    | 1     |

| Junction Temperature      | Tj              |                            |         |     | 125            | °C    | 1     |

| Case Temperature          | Тс              |                            |         |     | 110            | °C    | 1     |

| Input ESD protection      | ESD prot        | Human Body Model           | 2000    |     |                | V     | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

### **Electrical Characteristics – DIF\_IN Clock Input Parameters**

T<sub>AMB</sub>=T<sub>COM</sub> unless otherwise indicated, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                           | SYMBOL             | CONDITIONS                             | MIN | TYP | MAX | UNITS | NOTES |

|-------------------------------------|--------------------|----------------------------------------|-----|-----|-----|-------|-------|

| Input Crossover Voltage -<br>DIF_IN | V <sub>CROSS</sub> | Cross Over Voltage                     | 150 |     | 900 | mV    | 1     |

| Input Swing - DIF_IN                | V <sub>SWING</sub> | Differential value                     | 300 |     |     | mV    | 1     |

| Input Slew Rate - DIF_IN            | dv/dt              | Measured differentially                | 0.4 |     | 8   | V/ns  | 1,2   |

| Input Leakage Current               | I <sub>IN</sub>    | $V_{IN} = V_{DD}, V_{IN} = GND$        | -5  |     | 5   | uA    |       |

| Input Duty Cycle                    | d <sub>tin</sub>   | Measurement from differential wavefrom | 45  |     | 55  | %     | 1     |

| Input Jitter - Cycle to Cycle       | J <sub>DIFIn</sub> | Differential Measurement               | 0   |     | 125 | ps    | 1     |

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Slew rate measured through +/-75mV window centered around differential zero

### **Electrical Characteristics – Current Consumption**

TA = T<sub>COM:</sub> Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

| PARAMETER                | SYMBOL                | CONDITIONS                                     | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|-----------------------|------------------------------------------------|-----|-----|-----|-------|-------|

| Operating Supply Current | I <sub>DD3.3OP</sub>  | All outputs active @100MHz, $C_L = Full load;$ |     | 407 | 500 | mA    | 1     |

| Powerdown Current        | I <sub>DD3.3PDZ</sub> | All differential pairs tri-stated              |     | 12  | 36  | mA    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

### **Electrical Characteristics – Input/Supply/Common Parameters**

TA =  $T_{COM}$ ; Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

| PARAMETER                        | SYMBOL              | CONDITIONS                                                                                                                                           | MIN       | TYP    | MAX                   | UNITS  | NOTES |

|----------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|-----------------------|--------|-------|

| Ambient Operating<br>Temperature | T <sub>COM</sub>    | Commmercial range                                                                                                                                    | 0         |        | 70                    | °C     | 1     |

| Input High Voltage               | $V_{\text{IH}}$     | Single-ended inputs, except SMBus, low<br>threshold and tri-level inputs                                                                             | 2         |        | V <sub>DD</sub> + 0.3 | v      | 1     |

| Input Low Voltage                | V <sub>IL</sub>     | Single-ended inputs, except SMBus, low<br>threshold and tri-level inputs                                                                             | GND - 0.3 |        | 0.8                   | v      | 1     |

|                                  | I <sub>IN</sub>     | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = VDD$                                                                                                 | -5        |        | 5                     | uA     | 1     |

| Input Current                    | I <sub>INP</sub>    | Single-ended inputs $V_{IN} = 0 \text{ V}$ ; Inputs with internal pull-up resistors $V_{IN} = \text{VDD}$ ; Inputs with internal pull-down resistors | -200      |        | 200                   | uA     | 1     |

|                                  | F <sub>ibyp</sub>   | $V_{DD} = 3.3 V$ , Bypass mode                                                                                                                       | 33        |        | 400                   | MHz    | 2     |

| Input Frequency                  | F <sub>ipll</sub>   | $V_{DD} = 3.3 V$ , 100MHz PLL mode                                                                                                                   | 90        | 100.00 | 105                   | MHz    | 2     |

|                                  | F <sub>ipll</sub>   | V <sub>DD</sub> = 3.3 V, 133.33MHz PLL mode                                                                                                          | 120       | 133.33 | 140                   | MHz    | 2     |

| Pin Inductance                   | L <sub>pin</sub>    |                                                                                                                                                      |           |        | 7                     | nH     | 1     |

|                                  | CIN                 | Logic Inputs, except DIF_IN                                                                                                                          | 1.5       |        | 5                     | pF     | 1     |

| Capacitance                      | $C_{INDIF_IN}$      | DIF_IN differential clock inputs                                                                                                                     | 1.5       |        | 2.7                   | pF     | 1,4   |

|                                  | C <sub>OUT</sub>    | Output pin capacitance                                                                                                                               |           |        | 6                     | pF     | 1     |

| Clk Stabilization                | T <sub>STAB</sub>   | From $V_{DD}$ Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock                                                       |           |        | 1.8                   | ms     | 1,2   |

| Input SS Modulation<br>Frequency | f <sub>MODIN</sub>  | Allowable Frequency<br>(Triangular Modulation)                                                                                                       | 30        |        | 33                    | kHz    | 1     |

| OE# Latency                      | t <sub>LATOE#</sub> | DIF start after OE# assertion<br>DIF stop after OE# deassertion                                                                                      | 4         |        | 12                    | clocks | 1,3   |

| Tdrive_PD#                       | t <sub>DRVPD</sub>  | DIF output enable after<br>PD# de-assertion                                                                                                          |           |        | 300                   | us     | 1,3   |

| Tfall                            | t <sub>F</sub>      | Fall time of control inputs                                                                                                                          |           |        | 5                     | ns     | 1,2   |

| Trise                            | t <sub>R</sub>      | Rise time of control inputs                                                                                                                          |           |        | 5                     | ns     | 1,2   |

| SMBus Input Low Voltage          | VILSMB              |                                                                                                                                                      |           |        | 0.8                   | V      | 1     |

| SMBus Input High Voltage         | VIHSMB              |                                                                                                                                                      | 2.1       |        | V <sub>DDSMB</sub>    | V      | 1     |

| SMBus Output Low Voltage         | VOLSMB              | @ I <sub>PULLUP</sub>                                                                                                                                |           |        | 0.4                   | V      | 1     |

| SMBus Sink Current               | I <sub>PULLUP</sub> | @ V <sub>OL</sub>                                                                                                                                    | 4         |        |                       | mA     | 1     |

| Nominal Bus Voltage              | V <sub>DDSMB</sub>  | 3V to 5V +/- 10%                                                                                                                                     | 2.7       |        | 5.5                   | V      | 1     |

| SCLK/SDATA Rise Time             | t <sub>RSMB</sub>   | (Max VIL - 0.15) to (Min VIH + 0.15)                                                                                                                 |           |        | 1000                  | ns     | 1     |

| SCLK/SDATA Fall Time             | t <sub>FSMB</sub>   | (Min VIH + 0.15) to (Max VIL - 0.15)                                                                                                                 |           |        | 300                   | ns     | 1     |

| SMBus Operating<br>Frequency     | f <sub>MAXSMB</sub> | Maximum SMBus operating frequency                                                                                                                    |           |        | 100                   | kHz    | 1,5   |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Control input must be monotonic from 20% to 80% of input swing.

<sup>3</sup>Time from deassertion until outputs are >200 mV

<sup>4</sup> DIF\_IN input

<sup>5</sup>The differential input clock must be running for the SMBus to be active

### **Electrical Characteristics – DIF 0.7V Current Mode Differential Outputs**

| PARAMETER                      | SYMBOL     | CONDITIONS                                                                              | MIN    | TYP | MAX  |      | NOTES   |

|--------------------------------|------------|-----------------------------------------------------------------------------------------|--------|-----|------|------|---------|

| TANAMETER                      |            |                                                                                         | IVIIIN |     | WIAA |      |         |

| Slew rate                      | dV/dt      | Scope averaging on                                                                      | 1      | 2.5 | 4    | V/ns | 1, 2, 3 |

| Slew rate matching             | ∆dV/dt     | Slew rate matching, Scope averaging on                                                  |        |     | 20   | %    | 1, 2, 4 |

| <b>Rise/Fall Time Matching</b> | ΔTrf       | Rise/fall matching, Scope averaging off                                                 |        |     | 125  | ps   | 1, 7, 8 |

| Voltage High                   | VHigh      | Statistical measurement on single-ended signal using oscilloscope math function. (Scope | 660    | 750 | 850  | mV   | 1       |

| Voltage Low                    | VLow       | averaging on)                                                                           | -150   |     | 150  |      | 1       |

| Max Voltage                    | Vmax       | Measurement on single ended signal using                                                |        |     | 1150 |      | 1       |

| Min Voltage                    | Vmin       | absolute value. (Scope averaging off)                                                   | -300   |     |      | mV   | 1       |

| Vswing                         | Vswing     | Scope averaging off                                                                     | 300    |     |      | mV   | 1, 2    |

| Crossing Voltage (abs)         | Vcross_abs | Scope averaging off                                                                     | 250    |     | 550  | mV   | 1, 5    |

| Crossing Voltage (var)         | ∆-Vcross   | Scope averaging off                                                                     |        |     | 140  | mV   | 1, 6    |

TA =  $T_{COM}$  Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production. IREF = VDD/( $3xR_R$ ). For  $R_R = 475\Omega$  (1%),  $I_{REF} = 2.32mA$ .  $I_{OH} = 6 \times I_{REF}$  and  $V_{OH} = 0.7V$  @  $Z_O = 50\Omega$  (100 $\Omega$  differential impedance).

<sup>2</sup> Measured from differential waveform

<sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of V\_cross\_min/max (V\_cross absolute) allowed. The intent is to limit Vcross induced modulation by setting V\_cross\_delta to be smaller than V\_cross absolute.

<sup>7</sup> Measured from single-ended waveform

<sup>8</sup> Measured with scope averaging off, using statistics function. Variation is difference between min and max.

### **Electrical Characteristics – Skew and Differential Jitter Parameters**

| PARAMETER              | SYMBOL                 | CONDITIONS                                                                              | MIN  | TYP | MAX | UNITS       | NOTES     |

|------------------------|------------------------|-----------------------------------------------------------------------------------------|------|-----|-----|-------------|-----------|

| CLK_IN, DIF[x:0]       | t <sub>SPO_PLL</sub>   | Input-to-Output Skew in PLL mode<br>nominal value @ 25°C, 3.3V                          | -100 | 0   | 100 | ps          | 1,2,4,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>PD_BYP</sub>    | Input-to-Output Skew in Bypass mode<br>nominal value @ 25°C, 3.3V                       | 2.5  | 3.5 | 4.5 | ns          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DSPO_PLL</sub>  | Input-to-Output Skew Varation in PLL mode<br>across voltage and temperature             |      | 0   | 50  | ps          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DSPO_BYP</sub>  | Input-to-Output Skew Varation in Bypass mode<br>across voltage and temperature          | -250 |     | 250 | ps          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DTE</sub>       | Random Differential Tracking error beween two<br>9ZX devices in Hi BW Mode              |      | 3   | 5   | ps<br>(rms) | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]       | t <sub>DSSTE</sub>     | Random Differential Spread Spectrum Tracking error beween two 9ZX devices in Hi BW Mode |      | 15  | 75  | ps          | 1,2,3,5,8 |

| DIF{x:0]               | t <sub>SKEW_ALL</sub>  | Output-to-Output Skew across all outputs<br>(Common to Bypass and PLL mode)             |      | 37  | 65  | ps          | 1,2,3,8   |

| PLL Jitter Peaking     | j <sub>peak-hibw</sub> | LOBW#_BYPASS_HIBW = 1                                                                   | 0    | 1.3 | 2.5 | dB          | 7,8       |

| PLL Jitter Peaking     | j <sub>peak-lobw</sub> | LOBW#_BYPASS_HIBW = 0                                                                   | 0    | 0.8 | 2   | dB          | 7,8       |

| PLL Bandwidth          | pll <sub>HIBW</sub>    | LOBW#_BYPASS_HIBW = 1                                                                   | 2    | 3   | 4   | MHz         | 8,9       |

| PLL Bandwidth          | pll <sub>LOBW</sub>    | LOBW#_BYPASS_HIBW = 0                                                                   | 0.7  | 1.1 | 1.4 | MHz         | 8,9       |

| Duty Cycle             | t <sub>DC</sub>        | Measured differentially, PLL Mode                                                       | 45   | 50  | 55  | %           | 1         |

| Duty Cycle Distortion  | t <sub>DCD</sub>       | Measured differentially, Bypass Mode<br>@100MHz                                         | -2   | 0   | 2   | %           | 1,10      |

| Jitter, Cycle to cycle | t <sub>icyc-cyc</sub>  | PLL mode                                                                                |      | 41  | 50  | ps          | 1,11      |

| , <b>, ,</b>           | J0,0-0,0               | Additive Jitter in Bypass Mode                                                          |      | 20  | 50  | ps          | 1,11      |

TA = T<sub>COM</sub>. Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

### Notes for preceding table:

<sup>1</sup> Measured into fixed 2 pF load cap. Input to output skew is measured at the first output edge following the corresponding input.

<sup>2</sup> Measured from differential cross-point to differential cross-point. This parameter can be tuned with external feedback path, if present.

<sup>3</sup> All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

<sup>4</sup> This parameter is deterministic for a given device

<sup>5</sup> Measured with scope averaging on to find mean value. DIF\_IN slew rate must be matched to DIF output slew rate.

<sup>6</sup>.t is the period of the input clock

<sup>7</sup> Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

<sup>8.</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>9</sup> Measured at 3 db down or half power point.

<sup>10</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>11</sup> Measured from differential waveform

### **Electrical Characteristics – Phase Jitter Parameters**

TA = T<sub>COM</sub>: Supply Voltage VDD/VDDA = 3.3 V +/-5%, See Test Loads for Loading Conditions

| PARAMETER                                    | SYMBOL                  | CONDITIONS                                             | MIN | TYP  | MAX | UNITS       | Notes   |

|----------------------------------------------|-------------------------|--------------------------------------------------------|-----|------|-----|-------------|---------|

|                                              | t <sub>jphPCleG1</sub>  | PCIe Gen 1                                             |     | 39   | 86  | ps (p-p)    | 1,2,3   |

|                                              |                         | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz               |     | 1.1  | 3   | ps<br>(rms) | 1,2     |

|                                              | t <sub>jphPCleG2</sub>  | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)   |     | 2.6  | 3.1 | ps<br>(rms) | 1,2     |

| Jitter, Phase                                | t <sub>jphPCleG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz)          |     | 0.6  | 1   | ps<br>(rms) | 1,2,4   |

|                                              |                         | QPI & SMI<br>(100MHz or 133MHz, 4.8Gb/s, 6.4Gb/s 12UI) |     | 0.36 | 0.5 | ps<br>(rms) | 1,5     |

|                                              | t <sub>jphQPI_SMI</sub> | QPI & SMI<br>(100MHz, 8.0Gb/s, 12UI)                   |     | 0.23 | 0.3 | ps<br>(rms) | 1,5     |

|                                              |                         | QPI & SMI<br>(100MHz, 9.6Gb/s, 12UI)                   |     | 0.18 | 0.2 | ps<br>(rms) | 1,5     |

|                                              | t <sub>jphPCleG1</sub>  | PCIe Gen 1                                             |     | 4    | 10  | ps (p-p)    | 1,2,3   |

|                                              |                         | PCIe Gen 2 Lo Band<br>10kHz < f < 1.5MHz               |     | 0.25 | 0.3 | ps<br>(rms) | 1,2,6   |

|                                              | t <sub>jphPCleG2</sub>  | PCIe Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)   |     | 0.57 | 0.7 | ps<br>(rms) | 1,2,6   |

| <i>Additive</i> Phase Jitter,<br>Bypass mode | t <sub>jphPCleG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, CDR = 10MHz)          |     | 0.20 | 0.3 | ps<br>(rms) | 1,2,4,6 |

|                                              |                         | QPI & SMI<br>(100MHz or 133MHz, 4.8Gb/s, 6.4Gb/s 12UI) |     | 0.22 | 0.3 | ps<br>(rms) | 1,5,6   |

|                                              | t <sub>jphQPI_SMI</sub> | QPI & SMI<br>(100MHz, 8.0Gb/s, 12UI)                   |     | 0.08 | 0.1 | ps<br>(rms) | 1,5,6   |

|                                              |                         | QPI & SMI<br>(100MHz, 9.6Gb/s, 12UI)                   |     | 0.08 | 0.1 | ps<br>(rms) | 1,5,6   |

<sup>1</sup> Applies to all outputs.

<sup>2</sup> See http://www.pcisig.com for complete specs

<sup>3</sup> Sample size of at least 100K cycles. This figures extrapolates to 108ps pk-pk @ 1M cycles for a BER of 1-12.

<sup>4</sup> Subject to final radification by PCI SIG.

<sup>5</sup> Calculated from Intel-supplied Clock Jitter Tool v 1.6.3

<sup>6</sup> For RMS figures, additive jitter is calculated by solving the following equation: (Additive jitter)<sup>2</sup> = (total jitter)<sup>2</sup> - (input jitter)<sup>2</sup>

### **Power Management Table**

| Inputs      |                    | Control Bit     | s/Pins  |                          | Outputs            |                      |              |

|-------------|--------------------|-----------------|---------|--------------------------|--------------------|----------------------|--------------|

| CKPWRGD_PD# | DIF_IN/<br>DIF_IN# | SMBus<br>EN bit | OE# Pin | DIF(5:12)/<br>DIF(5:12)# | Other DIF/<br>DIF# | DFB_OUT/<br>DFB_OUT# | PLL<br>State |

| 0           | Х                  | Х               | Х       | Hi-Z <sup>1</sup>        | Hi-Z <sup>1</sup>  | Hi-Z <sup>1</sup>    | OFF          |

|             |                    | 0               | Х       | Hi-Z <sup>1</sup>        | Hi-Z <sup>1</sup>  | Running              | ON           |

| 1           | Running            | 1               | 0       | Running                  | Running            | Running              | ON           |

|             |                    | 1               | 1       | Hi-Z <sup>1</sup>        | Running            | Running              | ON           |

NOTE: 1. Due to external pull down resistors, HI-Z results in Low/Low on the True/Complement outputs

### Clock Periods – Differential Outputs with Spread Spectrum Disabled

|         |                        | Quarter                      |                                      | Measurement Window                   |                            |                                      |                                      |                              |          |       |       |

|---------|------------------------|------------------------------|--------------------------------------|--------------------------------------|----------------------------|--------------------------------------|--------------------------------------|------------------------------|----------|-------|-------|

|         |                        |                              | 1 Clock                              | 1us                                  | 0.1s                       | 0.1s                                 | 0.1s                                 | 1us                          | 1 Clock  |       |       |

| SSC OFF | Center<br>Freq.<br>MHz | -c2c jitter<br>AbsPer<br>Min | -SSC<br>Short-Term<br>Average<br>Min | - ppm<br>Long-Term<br>Average<br>Min | 0 ppm<br>Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Max | +SSC<br>Short-Term<br>Average<br>Max | +c2c jitter<br>AbsPer<br>Max | Units    | Notes |       |

|         | DIF                    | 100.00                       | 9.94900                              |                                      | 9.99900                    | 10.00000                             | 10.00100                             |                              | 10.05100 | ns    | 1,2,3 |

|         | DIF                    | 133.33                       | 7.44925                              |                                      | 7.49925                    | 7.50000                              | 7.50075                              |                              | 7.55075  | ns    | 1,2,4 |

### **Clock Periods – Differential Outputs with Spread Spectrum Enabled**

|        |        |                              | Measurement Window                   |                                      |                            |                                      |                                      |                              |       |       |

|--------|--------|------------------------------|--------------------------------------|--------------------------------------|----------------------------|--------------------------------------|--------------------------------------|------------------------------|-------|-------|

| SSC ON | Center | 1 Clock                      | 1us                                  | 0.1s                                 | 0.1s                       | 0.1s                                 | 1us                                  | 1 Clock                      |       |       |

|        |        | -c2c jitter<br>AbsPer<br>Min | -SSC<br>Short-Term<br>Average<br>Min | - ppm<br>Long-Term<br>Average<br>Min | 0 ppm<br>Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Max | +SSC<br>Short-Term<br>Average<br>Max | +c2c jitter<br>AbsPer<br>Max | Units | Notes |

| DIF    | 99.75  | 9.94906                      | 9.99906                              | 10.02406                             | 10.02506                   | 10.02607                             | 10.05107                             | 10.10107                     | ns    | 1,2,3 |

| DIF    | 133.00 | 7.44930                      | 7.49930                              | 7.51805                              | 7.51880                    | 7.51955                              | 7.53830                              | 7.58830                      | ns    | 1,2,4 |

### Notes:

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with CK420BQ/CK410B+ accuracy requirements (+/-100ppm). The 96Z61027 itself does not contribute to ppm error.

<sup>3</sup> Driven by SRC output of main clock, 100 MHz PLL Mode or Bypass mode

<sup>4</sup> Driven by CPU output of main clock, 133 MHz PLL Mode or Bypass mode

### **Thermal Characteristics**

| Parameter                              | Symbol | Conditions     | Min. | Тур. | Max. | Units |

|----------------------------------------|--------|----------------|------|------|------|-------|

| Thermal Resistance Junction to Ambient | θJA    | Still air      |      | 26.2 |      | °C/W  |

|                                        | θJA    | 1 m/s air flow |      | 23.1 |      | °C/W  |

|                                        | θJA    | 3 m/s air flow |      | 19.6 |      | °C/W  |

| Thermal Resistance Junction to Case    | θJC    |                |      | 10.4 |      | °C/W  |

| Thermal Resistance Junction to Board   | θJB    |                |      | 0.3  |      | °C/W  |

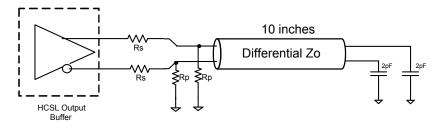

### **Differential Output Termination Table**

| DIF Zo (Ω) | Iref (Ω) | Rs $(\Omega)$ | Rp (Ω)       |

|------------|----------|---------------|--------------|

| 100        | 475      | 33            | 50           |

| 85         | 412      | 27            | 42.2 or 43.2 |

9ZX21901 Differential Test Loads

### General SMBus Serial Interface Information (see also 9ZX21901 SMBus Addressing on page 2)

### How to Write

- Controller (host) sends a start bit

- Controller (host) sends the write address XX<sub>(H)</sub>

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) sends the byte count = X

- IDT clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- IDT clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

|           | Index Bl   | ock \  | Write Operation      |

|-----------|------------|--------|----------------------|

| Controll  | er (Host)  |        | IDT (Slave/Receiver) |

| Т         | starT bit  |        |                      |

| Slave A   | Address    |        |                      |

| WR        | WRite      |        |                      |

|           |            |        | ACK                  |

| Beginning | g Byte = N |        |                      |

|           |            |        | ACK                  |

| Data Byte | Count = X  |        |                      |

|           |            |        | ACK                  |

| Beginnin  | ig Byte N  |        |                      |

|           |            |        | ACK                  |

| 0         |            | ×      |                      |

| 0         |            | X Byte | 0                    |

| 0         |            | e      | 0                    |

|           |            |        | 0                    |

| Byte N    | + X - 1    |        |                      |

|           |            |        | ACK                  |

| Р         | stoP bit   |        |                      |

### Note: XX<sub>(H)</sub> is defined by SMBus Address select pins.

### How to Read

- Controller (host) will send a start bit

- Controller (host) sends the write address XX<sub>(H)</sub>

- IDT clock will acknowledge

- Controller (host) sends the beginning byte location = N

- IDT clock will acknowledge

- Controller (host) will send a separate start bit

- Controller (host) sends the read address YY<sub>(H)</sub>

- IDT clock will acknowledge

- IDT clock will send the data byte count = X

- IDT clock sends Byte N+X-1

- IDT clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

|     | Index Block F   | Read O | peration             |

|-----|-----------------|--------|----------------------|

| Co  | ntroller (Host) |        | IDT (Slave/Receiver) |

| Т   | starT bit       |        |                      |

| S   | lave Address    |        |                      |

| WR  | WRite           |        |                      |

|     |                 |        | ACK                  |

| Beg | inning Byte = N |        |                      |

|     |                 |        | ACK                  |

| RT  | Repeat starT    |        |                      |

| S   | lave Address    |        |                      |

| RD  | ReaD            |        |                      |

|     |                 |        | ACK                  |

|     |                 |        |                      |

|     |                 |        | Data Byte Count=X    |

|     | ACK             |        |                      |

|     |                 |        | Beginning Byte N     |

|     | ACK             |        |                      |

|     |                 | e      | 0                    |

|     | 0               | X Byte | 0                    |

|     | 0               | ×      | 0                    |

|     | 0               |        |                      |

|     |                 |        | Byte N + X - 1       |

| Ν   | Not acknowledge |        |                      |

| Р   | stoP bit        |        |                      |

| Byte  | e 0 Pin # | Name       | Control Function                 | Туре             | 0                      | 1        | Default |  |

|-------|-----------|------------|----------------------------------|------------------|------------------------|----------|---------|--|

| Bit 7 | 5         | PLL Mode 1 | PLL Operating Mode Rd back 1     | R                | See PLL Operating Mode |          | Latch   |  |

| Bit 6 | 5         | PLL Mode 0 | PLL Operating Mode Rd back 0     | R Readback Table |                        | ck Table | Latch   |  |

| Bit 5 | 72/71     | DIF_18_En  | Output Control overrides OE# pin | RW               | Hi-Z                   | Enable   | 1       |  |

| Bit 4 | 70/69     | DIF_17_En  | Output Control overrides OE# pin | RW               | Hi-Z                   | Enable   | 1       |  |

| Bit 3 | 67/66     | DIF_16_En  | Output Control overrides OE# pin | RW               | Hi-Z                   | Enable   | 1       |  |

| Bit 2 |           |            | Reserved                         |                  |                        |          | 0       |  |

| Bit 1 |           | Reserved   |                                  |                  |                        |          |         |  |

| Bit 0 | 4         | 100M_133M# | Frequency Select Readback        | R                | 133MHz                 | 100MHz   | Latch   |  |

### SMBusTable: PLL Mode, and Frequency Select Register

#### SMBusTable: Output Control Register

|                   |         | eenaernogietei |                                  |      | -    | -      |         |

|-------------------|---------|----------------|----------------------------------|------|------|--------|---------|

| Byte <sup>·</sup> | 1 Pin # | Name           | Control Function                 | Туре | 0    | 1      | Default |

| Bit 7             | 39/38   | DIF_7_En       | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 6             | 35/36   | DIF_6_En       | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 5             | 32/33   | DIF_5_En       | Output Control overrides OE# pin | RW   | ]    |        | 1       |

| Bit 4             | 29/30   | DIF_4_En       | Output Control overrides OE# pin | RW   | Hi-Z | Enable | 1       |

| Bit 3             | 27/28   | DIF_3_En       | Output Control overrides OE# pin | RW   |      |        | 1       |

| Bit 2             | 24/25   | DIF_2_En       | Output Control overrides OE# pin | RW   | ]    |        | 1       |

| Bit 1             | 22/23   | DIF_1_En       | Output Control overrides OE# pin | RW   | ]    |        | 1       |

| Bit 0             | 19/20   | DIF_0_En       | Output Control overrides OE# pin | RW   | Ţ    |        | 1       |

#### SMBusTable: Output Control Register

| Byte 2 | Pin # | Name      | Control Function                 | Туре | 0    | 1       | Default |

|--------|-------|-----------|----------------------------------|------|------|---------|---------|

| Bit 7  | 65/64 | DIF_15_En | Output Control overrides OE# pin | RW   |      |         | 1       |

| Bit 6  | 62/61 | DIF_14_En | Output Control overrides OE# pin | RW   | ]    |         | 1       |

| Bit 5  | 60/59 | DIF_13_En | Output Control overrides OE# pin | RW   | ]    |         | 1       |

| Bit 4  | 56/55 | DIF_12_En | Output Control overrides OE# pin | RW   | Hi-Z | Enable  | 1       |

| Bit 3  | 53/52 | DIF_11_En | Output Control overrides OE# pin | RW   |      | LIIADIE | 1       |

| Bit 2  | 50/49 | DIF_10_En | Output Control overrides OE# pin | RW   | ]    |         | 1       |

| Bit 1  | 47/46 | DIF_9_En  | Output Control overrides OE# pin | RW   | ]    |         | 1       |

| Bit 0  | 42/41 | DIF_8_En  | Output Control overrides OE# pin | RW   | ]    |         | 1       |

### SMBusTable: Output Enable Pin Status Readback Register

| Byte  | 3 Pin # | Name    | Control Function            | Туре | 0 | 1            | Default   |  |  |

|-------|---------|---------|-----------------------------|------|---|--------------|-----------|--|--|

| Bit 7 | 57      | OE_RB12 | Real Time readback of OE#12 | R    |   |              | Real time |  |  |

| Bit 6 | 54      | OE_RB11 | Real Time readback of OE#11 | R    |   |              | Real time |  |  |

| Bit 5 | 51      | OE_RB10 | Real Time readback of OE#10 | R    |   |              | Real time |  |  |

| Bit 4 | 48      | OE_RB9  | Real Time readback of OE#9  | R    |   | OE# Pin High | Real time |  |  |

| Bit 3 | 43      | OE_RB8  | Real Time readback of OE#8  | R    |   |              | Real time |  |  |

| Bit 2 | 40      | OE_RB7  | Real Time readback of OE#7  | R    |   |              | Real time |  |  |

| Bit 1 | 37      | OE_RB6  | Real Time readback of OE#6  | R    |   |              | Real time |  |  |

| Bit 0 | 34      | OE_RB5  | Real Time readback of OE#5  | R    | 1 |              | Real time |  |  |

### SMBusTable: Reserved Register

| Byte  | e 4 | Pin # | Name     | Control Function | Туре | 0 | 1 | Default |

|-------|-----|-------|----------|------------------|------|---|---|---------|

| Bit 7 |     |       |          | Reserved         |      |   |   | 0       |

| Bit 6 |     |       | Reserved |                  |      |   |   |         |

| Bit 5 |     |       | Reserved |                  |      |   |   |         |

| Bit 4 |     |       | Reserved |                  |      |   |   | 0       |

| Bit 3 |     |       | Reserved |                  |      |   |   | 0       |

| Bit 2 |     |       | Reserved |                  |      |   |   |         |

| Bit 1 |     |       | Reserved |                  |      |   |   |         |

| Bit 0 |     |       | Reserved |                  |      |   |   |         |

### SMBusTable: Vendor & Revision ID Register

| Byte 5 | 5 Pin # | Name | Control Function | Туре | 0     | 1      | Default |

|--------|---------|------|------------------|------|-------|--------|---------|

| Bit 7  | -       | RID3 |                  | R    |       |        | Х       |

| Bit 6  | -       | RID2 | REVISION ID      | R    | B rev | Х      |         |

| Bit 5  | -       | RID1 |                  | R    | C Rev | = 0010 | Х       |

| Bit 4  | -       | RID0 |                  | R    |       |        | Х       |

| Bit 3  | -       | VID3 |                  | R    | -     | -      | 0       |

| Bit 2  | -       | VID2 | VENDOR ID        | R    | -     | -      | 0       |

| Bit 1  | -       | VID1 |                  | R    | -     | -      | 0       |

| Bit 0  | -       | VID0 |                  | R    | -     | -      | 1       |

### SMBusTable: DEVICE ID

| Byte 6 |   |    | Туре             | 0 | 1              | Default |   |

|--------|---|----|------------------|---|----------------|---------|---|

| Bit 7  | - | De | evice ID 7 (MSB) | R |                |         | 1 |

| Bit 6  | - |    | Device ID 6      | R |                |         | 1 |

| Bit 5  | - |    | Device ID 5      | R |                | 0       |   |

| Bit 4  | - |    | Device ID 4      | R | Device ID is 2 | 1       |   |

| Bit 3  | - |    | Device ID 3      | R | DB             | hex.    | 1 |

| Bit 2  | - |    | Device ID 2      | R |                |         | 0 |

| Bit 1  | - |    | Device ID 1      | R |                |         | 1 |

| Bit 0  | - |    | Device ID 0      | R |                | 1       |   |

### SMBusTable: Byte Count Register

| Byte  | e 7 | 7 Pin # Name |          | Control Function                        | Туре | 0                | 1                | Default |

|-------|-----|--------------|----------|-----------------------------------------|------|------------------|------------------|---------|

| Bit 7 |     |              | Reserved |                                         |      |                  |                  |         |

| Bit 6 |     |              |          | Reserved                                |      |                  |                  | 0       |

| Bit 5 |     |              | Reserved |                                         |      |                  |                  | 0       |

| Bit 4 |     | -            | BC4      |                                         | RW   |                  |                  | 0       |

| Bit 3 |     | -            | BC3      | Writing to this register configures how | RW   | Default value    | is 8 hex, so 9   | 1       |

| Bit 2 |     | -            | BC2      | <b>v</b>                                | RW   | bytes (0 to 8) w | ill be read back | 0       |

| Bit 1 |     | -            | BC1      | many bytes will be read back.           | RW   | by de            | by default.      |         |

| Bit 0 |     | -            | BC0      |                                         | RW   |                  |                  | 0       |

### SMBusTable: Reserved Register

| Byte  | e 8 | Pin # | Name     | Control Function | Туре | 0 | 1 | Default |  |  |

|-------|-----|-------|----------|------------------|------|---|---|---------|--|--|

| Bit 7 |     |       |          | Reserved         |      |   |   | 0       |  |  |

| Bit 6 |     |       |          | Reserved         |      |   |   |         |  |  |

| Bit 5 |     |       | Reserved |                  |      |   |   |         |  |  |

| Bit 4 |     |       | Reserved |                  |      |   |   |         |  |  |

| Bit 3 |     |       |          | Reserved         |      |   |   | 0       |  |  |

| Bit 2 |     |       | Reserved |                  |      |   |   | 0       |  |  |

| Bit 1 |     |       | Reserved |                  |      |   |   |         |  |  |

| Bit 0 |     |       | Reserved |                  |      |   |   |         |  |  |

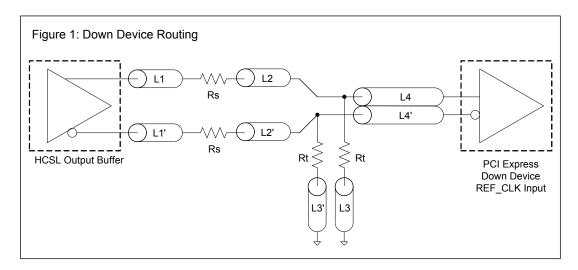

| DIF Reference Clock                             |                    |      |        |  |  |  |  |

|-------------------------------------------------|--------------------|------|--------|--|--|--|--|

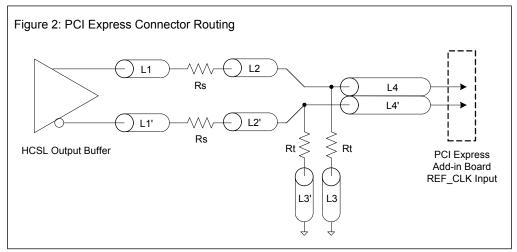

| Common Recommendations for Differential Routing | Dimension or Value | Unit | Figure |  |  |  |  |

| L1 length, route as non-coupled 50ohm trace     | 0.5 max            | inch | 1      |  |  |  |  |

| L2 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |  |  |  |  |

| L3 length, route as non-coupled 50ohm trace     | 0.2 max            | inch | 1      |  |  |  |  |

| Rs                                              | 33                 | ohm  | 1      |  |  |  |  |

| Rt                                              | 49.9               | ohm  | 1      |  |  |  |  |

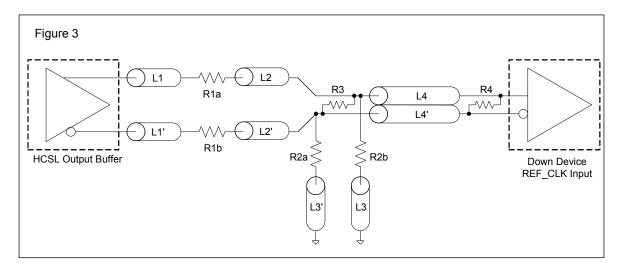

| Down Device Differential Routing                                 |                     |      |   |

|------------------------------------------------------------------|---------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 2 min to 16 max     | inch | 1 |

| L4 length, route as coupled stripline 100ohm differential trace  | 1.8 min to 14.4 max | inch | 1 |

| Differential Routing to PCI Express Connector                    |                       |      |   |

|------------------------------------------------------------------|-----------------------|------|---|

| L4 length, route as coupled microstrip 100ohm differential trace | 0.25 to 14 max        | inch | 2 |

| L4 length, route as coupled stripline 100ohm differential trace  | 0.225 min to 12.6 max | inch | 2 |

|              | Alternative Termination for LVDS and other Common Differential Signals (figure 3) |      |    |      |      |     |                                |  |

|--------------|-----------------------------------------------------------------------------------|------|----|------|------|-----|--------------------------------|--|

| Vdiff        | Vp-р                                                                              | Vcm  | R1 | R2   | R3   | R4  | Note                           |  |

| 0.45v        | 0.22v                                                                             | 1.08 | 33 | 150  | 100  | 100 |                                |  |

| 0.58         | 0.28                                                                              | 0.6  | 33 | 78.7 | 137  | 100 |                                |  |

| 0.80         | 0.40                                                                              | 0.6  | 33 | 78.7 | none | 100 | ICS874003i-02 input compatible |  |

| 0.60         | 0.3                                                                               | 1.2  | 33 | 174  | 140  | 100 | Standard LVDS                  |  |

| $R_{12} = R$ | 1h = R1                                                                           | •    | •  | -    |      |     |                                |  |

R1a = R1b = R1R2a = R2b = R2

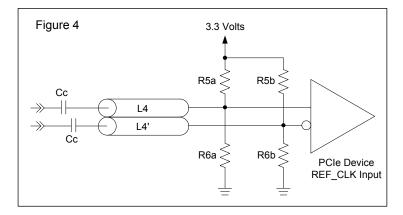

| Cable Connected AC Coupled Application (figure 4) |             |      |  |  |  |  |  |

|---------------------------------------------------|-------------|------|--|--|--|--|--|

| Component                                         | Value       | Note |  |  |  |  |  |

| R5a, R5b                                          | 8.2K 5%     |      |  |  |  |  |  |

| R6a, R6b                                          | 1K 5%       |      |  |  |  |  |  |

| Cc                                                | 0.1 µF      |      |  |  |  |  |  |

| Vcm                                               | 0.350 volts |      |  |  |  |  |  |

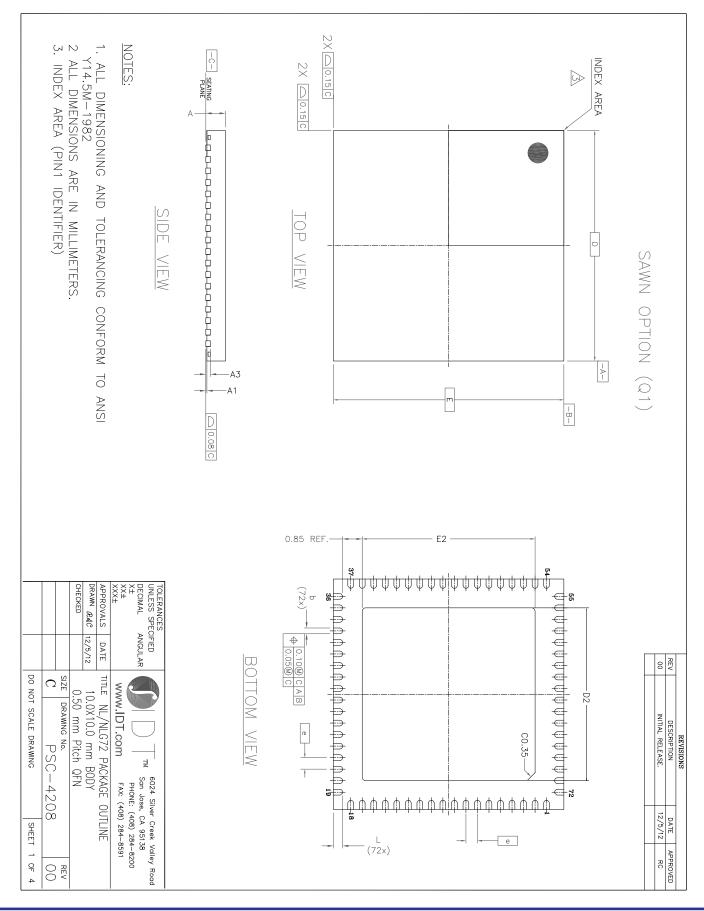

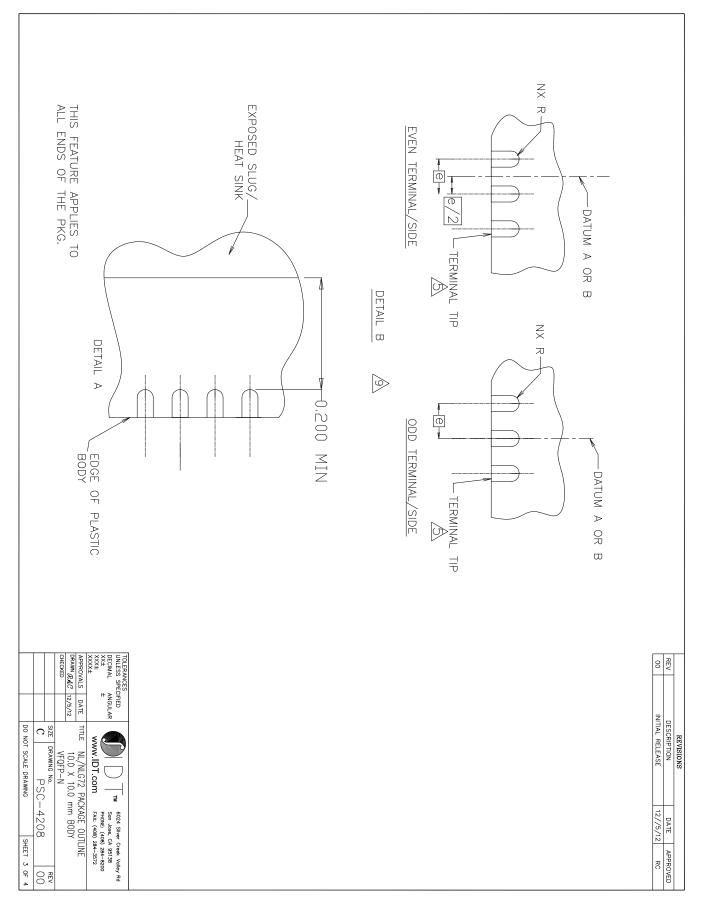

### Package Outline and Dimensions (NL72)

# Package Outline and Dimensions (NL72), cont.

# Package Outline and Dimensions (NL72) cont. – use EPAD Option P3 and Lead Option Z2

| Image: ToleFrance of Form & Position       MIN.       NOM.         SYMBOL       0.40mm       0.50mm $inclean       0.10       0.10       inclean       in$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.20                                             | MIN. NOM. MAX.   | SAW VERSION:                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|--------------------------------------|

| A.<br>AND E<br>AND E<br>NOM.<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50<br>0.50 | LEAD OPTION                                      | 7 MIN.<br>7 NOM. | EPAD OPTION:                         |