## **Description**

The 9ZXL0651 is a low-power 6-output differential buffer that meets all the performance requirements of the Intel DB1200Z specification. It consumes 50% less power than standard HCSL devices and has internal terminations to allow direct connection to  $85\Omega$  transmission lines. It is suitable for PCI-Express Gen1/2/3 or QPI/UPI applications, and uses a fixed external feedback to maintain low drift for demanding QPI/UPI applications.

## **Applications**

Buffer for Romley, Grantley and Purley Servers, SSDs and PCle

## **Output Features**

6 – LP-HCSL Output Pairs w/integrated terminations (Zo = 85Ω)

#### **Features**

- 25MHz PFT clock delay management

- Low-Power-HCSL outputs with Zo =  $85\Omega$ ; save power and board space no termination resistors required. Ideal for blade servers.

- Space-saving 40-pin VFQFPN package

- · Fixed feedback path for 0ps input-to-output delay

- 6 OE# pins; hardware control of each output

- PLL or bypass mode; PLL can dejitter incoming clock

- Selectable PLL bandwidth; minimizes jitter peaking in downstream PLLs

- Spread spectrum compatible; tracks spreading input clock for low EMI

## **Key Specifications**

- Cycle-to-cycle jitter < 50ps

- Output-to-output skew < 65ps

- Input-to-output delay variation < 50ps

- PCIe Gen3 phase jitter < 1.0ps RMS

- QPI/UPI 9.6GT/s 12UI phase jitter < 0.2ps RMS

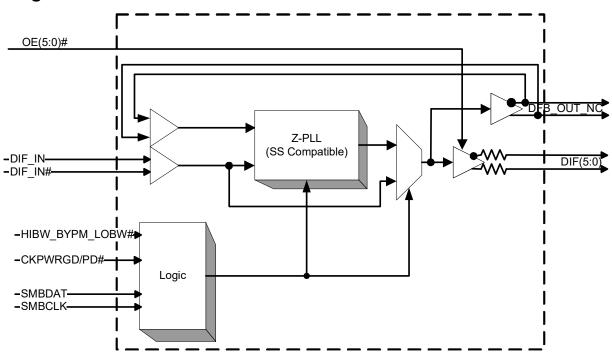

## **Block Diagram**

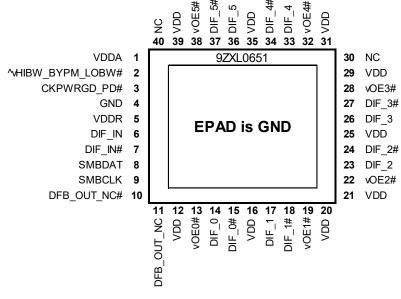

# **Pin Configuration**

#### 40-VFQFPN

^ prefix indicates internal Pull-Up Resistor v prefix indicates Internal Pull-Dow n Resistor ^v prefix indicates Internal Pull-Up/Dow n Resistor (biased to VDD/2)

5mm x 5mm 0.4mm pin pitch

## **Power Management Table**

| CKPWRGD_PD# | DIF_IN/<br>DIF_IN# | SMBus<br>EN bit | DIF(5:0)/<br>DIF(5:0)# | PLL STATE<br>IF NOT IN<br>BYPASS<br>MODE |

|-------------|--------------------|-----------------|------------------------|------------------------------------------|

| 0           | Х                  | Х               | Low/Low                | OFF                                      |

| 4           | Dunning            | 0               | Low/Low                | ON                                       |

| l l         | Running            | 1               | Running                | ON                                       |

## **PLL Operating Mode**

| HiBW_BypM_LoBW# | MODE      |

|-----------------|-----------|

| Low             | PLL Lo BW |

| Mid             | Bypass    |

| Hiah            | PLL Hi BW |

NOTE: PLL is OFF in Bypass Mode

#### **Power Connections**

| Pin N                          | umber |              |

|--------------------------------|-------|--------------|

| VDD                            | GND   | Description  |

| 1                              | 41    | Analog PLL   |

| 5                              | 4     | Analog Input |

| 12,16,20,24,27<br>,31,32,36,40 | 41    | DIF clocks   |

## **PLL Operating Mode Readback Table**

| HiBW_BypM_LoBW# | Byte0, bit 7 | Byte 0, bit 6 |

|-----------------|--------------|---------------|

| Low (Low BW)    | 0            | 0             |

| Mid (Bypass)    | 0            | 1             |

| High (High BW)  | 1            | 1             |

## **Tri-level Input Thresholds**

| Level | Voltage                           |

|-------|-----------------------------------|

| Low   | <0.8V                             |

| Mid   | 1.2 <vin<1.8v< th=""></vin<1.8v<> |

| High  | Vin > 2.2V                        |

#### 9ZXL0651 SMBus Address

| 1101100 | + Read/Write bit |

|---------|------------------|

# **Pin Descriptions**

| Sexit Power Down Mode on subsequent                                                                                                                                                                                                                                                                        | ails.  ched inputs and start up on first high assertion, or assertions. Low enters Power Down Mode.  receiver). This VDD should be treated as an |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 NOR DIN See PLL Operating Mode Table for Deta 3 CKPWRGD_PD# Trays 3.3V Input notifies device to sample lat exit Power Down Mode on subsequent 4 GND Ground pin. 5 VDDR PWR 3.3V power for differential input clock (ranalog power rail and filtered appropriat 6 DIF_IN IN 0.7 V Differential True input | ails.  ched inputs and start up on first high assertion, or assertions. Low enters Power Down Mode.  receiver). This VDD should be treated as an |

| exit Power Down Mode on subsequent  4 GND GND Ground pin.  5 VDDR PWR 3.3V power for differential input clock (ranalog power rail and filtered appropriat  6 DIF_IN IN 0.7 V Differential True input                                                                                                       | assertions. Low enters Power Down Mode. receiver). This VDD should be treated as an                                                              |

| 5 VDDR PWR 3.3V power for differential input clock (ranalog power rail and filtered appropriat  6 DIF_IN IN 0.7 V Differential True input                                                                                                                                                                  | · ·                                                                                                                                              |

| 5 VDDR analog power rail and filtered appropriat 6 DIF_IN IN 0.7 V Differential True input                                                                                                                                                                                                                 | ·                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                            |                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                            |                                                                                                                                                  |

| 7 DIF_IN# IN 0.7 V Differential Complementary Input                                                                                                                                                                                                                                                        |                                                                                                                                                  |

| 8 SMBDAT I/O Data pin of SMBUS circuitry, 5V toleral                                                                                                                                                                                                                                                       | nt                                                                                                                                               |

| 9 SMBCLK IN Clock pin of SMBUS circuitry, 5V tolera                                                                                                                                                                                                                                                        |                                                                                                                                                  |

| 10 DFB_OUT_NC# OUT for synchronization with input clock to e connected on the circuit board, the feed                                                                                                                                                                                                      |                                                                                                                                                  |

| 11 DFB_OUT_NC OUT synchronization with the input clock to connected on the circuit board, the feed                                                                                                                                                                                                         | r, provides feedback signal to the PLL for eliminate phase error. This pin should NOT be dback is internal to the package.                       |

| 12 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 13 vOE0# IN Active low input for enabling DIF pair 0. 1 = disable outputs, 0 = enable outputs                                                                                                                                                                                                              |                                                                                                                                                  |

| 14 DIF_0 OUT 0.7V differential true clock output                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 15 DIF_0# OUT 0.7V differential Complementary clock                                                                                                                                                                                                                                                        | output                                                                                                                                           |

| 16 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 17 DIF_1 OUT 0.7V differential true clock output                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 18 DIF_1# OUT 0.7V differential Complementary clock                                                                                                                                                                                                                                                        | output                                                                                                                                           |

| 19 vOE1# IN Active low input for enabling DIF pair 1. 1 = disable outputs, 0 = enable outputs                                                                                                                                                                                                              |                                                                                                                                                  |

| 20 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 21 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 22 vOE2# IN Active low input for enabling DIF pair 2. 1 = disable outputs, 0 = enable outputs                                                                                                                                                                                                              |                                                                                                                                                  |

| 23 DIF 2 OUT 0.7V differential true clock output                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 24 DIF 2# OUT 0.7V differential Complementary clock                                                                                                                                                                                                                                                        | output                                                                                                                                           |

| 25 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 26 DIF_3 OUT 0.7V differential true clock output                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 27 DIF_3# OUT 0.7V differential Complementary clock                                                                                                                                                                                                                                                        | output                                                                                                                                           |

| 28 vOE3# IN Active low input for enabling DIF pair 3. 1 = disable outputs, 0 = enable outputs                                                                                                                                                                                                              |                                                                                                                                                  |

| 29 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 30 NC N/A No Connection.                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |

| 31 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 32 vOE4# IN Active low input for enabling DIF pair 4. 1 = disable outputs, 0 = enable outputs                                                                                                                                                                                                              |                                                                                                                                                  |

| 33 DIF_4 OUT 0.7V differential true clock output                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 34 DIF 4# OUT 0.7V differential Complementary clock                                                                                                                                                                                                                                                        | output                                                                                                                                           |

| 35 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 36 DIF_5 OUT 0.7V differential true clock output                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 37 DIF_5# OUT 0.7V differential Complementary clock                                                                                                                                                                                                                                                        | output                                                                                                                                           |

| 38 vOE5# IN Active low input for enabling DIF pair 5. 1 =disable outputs, 0 = enable outputs                                                                                                                                                                                                               | This pin has an internal pull-down.                                                                                                              |

| 39 VDD PWR Power supply, nominal 3.3V                                                                                                                                                                                                                                                                      |                                                                                                                                                  |

| 40 NC N/A No Connection.                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |

| 41 EPAD GND Ground Pad.                                                                                                                                                                                                                                                                                    |                                                                                                                                                  |

# **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the 9ZXL0651. These ratings, which are standard values for Renesas commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| PARAMETER                | SYMBOL             | CONDITIONS                 | MIN     | TYP | MAX                   | UNITS | NOTES |

|--------------------------|--------------------|----------------------------|---------|-----|-----------------------|-------|-------|

|                          | VDD, VDDA,         |                            |         |     |                       |       |       |

| 3.3V Core Supply Voltage | VDDR               | VDD for core logic and PLL |         |     | 4.6                   | V     | 1,2   |

| Input Low Voltage        | $V_{IL}$           |                            | GND-0.5 |     |                       | V     | 1     |

| Input High Voltage       | V <sub>IH</sub>    | Except for SMBus interface |         |     | V <sub>DD</sub> +0.5V | V     | 1     |

| Input High Voltage       | V <sub>IHSMB</sub> | SMBus clock and data pins  |         |     | 5.5V                  | ٧     | 1     |

| Storage Temperature      | Ts                 |                            | -65     |     | 150                   | °C    | 1     |

| Junction Temperature     | Tj                 |                            |         |     | 125                   | °C    | 1     |

| Input ESD protection     | ESD prot           | Human Body Model           | 2000    |     |                       | V     | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

## **Electrical Characteristics-DIF\_IN Clock Input Parameters**

$T_A = T_{COM}$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

|                                  |                    |                                        | 1   |     |     |       |       |

|----------------------------------|--------------------|----------------------------------------|-----|-----|-----|-------|-------|

| PARAMETER                        | SYMBOL             | CONDITIONS                             | MIN | TYP | MAX | UNITS | NOTES |

| Input Crossover Voltage - DIF_IN | V <sub>CROSS</sub> | Crossover Voltage                      | 150 |     | 900 | mV    | 1     |

| Input Swing - DIF_IN             | $V_{SWING}$        | Differential value                     | 300 |     |     | mV    | 1     |

| Input Slew Rate - DIF_IN         | dv/dt              | Measured differentially                | 0.4 |     | 8   | V/ns  | 1,2   |

| Input Leakage Current            | I <sub>IN</sub>    | $V_{IN} = V_{DD}$ , $V_{IN} = GND$     | -5  |     | 5   | uA    |       |

| Input Duty Cycle                 | $d_{tin}$          | Measurement from differential waveform | 45  |     | 55  | %     | 1     |

| Input Jitter - Cycle to Cycle    | $J_{DIFIn}$        | Differential Measurement               | 0   |     | 125 | ps    | 1     |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

$<sup>^{2}</sup>$  Slew rate measured through +/-75mV window centered around differential zero.

# **Electrical Characteristics-Input/Supply/Common Parameters**

$T_A = T_{COM}$ ; Supply Voltage  $V_{DD} = 3.3 V + -5\%$

| PARAMETER                        | SYMBOL                | CONDITIONS                                                                                                                                                                               | MIN       | TYP    | MAX                   | UNITS  | NOTES |

|----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|-----------------------|--------|-------|

| Ambient Operating Temperature    | T <sub>COM</sub>      | Commercial range                                                                                                                                                                         | 0         | 35     | 70                    | °C     | 1     |

| Input High Voltage               | $V_{IH}$              | Single-ended inputs, except SMBus, low threshold and tri-level inputs                                                                                                                    | 2         |        | V <sub>DD</sub> + 0.3 | V      | 1     |

| Input Low Voltage                | V <sub>IL</sub>       | Single-ended inputs, except SMBus, low threshold and tri-level inputs                                                                                                                    | GND - 0.3 |        | 0.8                   | V      | 1     |

|                                  | I <sub>IN</sub>       | Single-ended inputs, $V_{IN}$ = GND, $V_{IN}$ = VDD                                                                                                                                      | -5        |        | 5                     | uA     | 1     |

| Input Current                    | I <sub>INP</sub>      | $\label{eq:single-ended} Single-ended inputs \\ V_{IN} = 0 \ V; \ Inputs \ with internal \ pull-up \ resistors \\ V_{IN} = \ VDD; \ Inputs \ with \ internal \ pull-down \ resistors \\$ | -200      |        | 200                   | uA     | 1     |

| Input Frequency                  | $F_{ibyp}$            | V <sub>DD</sub> = 3.3 V, Bypass mode                                                                                                                                                     | 25        |        | 150                   | MHz    | 2     |

| input Frequency                  | F <sub>ipll</sub>     | V <sub>DD</sub> = 3.3 V, 100MHz PLL mode                                                                                                                                                 | 25        | 100.00 | 110                   | MHz    | 2     |

| Pin Inductance                   | L <sub>pin</sub>      |                                                                                                                                                                                          |           |        | 7                     | nH     | 1     |

|                                  | C <sub>IN</sub>       | Logic Inputs, except DIF_IN                                                                                                                                                              | 1.5       |        | 5                     | pF     | 1     |

| Capacitance                      | C <sub>INDIF_IN</sub> | DIF_IN differential clock inputs                                                                                                                                                         | 1.5       |        | 2.7                   | pF     | 1,4   |

|                                  | C <sub>OUT</sub>      | Output pin capacitance                                                                                                                                                                   |           |        | 6                     | pF     | 1     |

| Clk Stabilization                | T <sub>STAB</sub>     | From V <sub>DD</sub> Power-Up and after input clock stabilization or de-assertion of PD# to 1st clock                                                                                    |           | 0.53   | 1                     | ms     | 1,2   |

| Input SS Modulation<br>Frequency | f <sub>MODIN</sub>    | Allowable Frequency<br>(Triangular Modulation)                                                                                                                                           | 30        |        | 33                    | kHz    | 1     |

| OE# Latency                      | t <sub>LATOE#</sub>   | DIF start after OE# assertion DIF stop after OE# deassertion                                                                                                                             | 4         | 8      | 12                    | cycles | 1,3   |

| Tdrive_PD#                       | t <sub>DRVPD</sub>    | DIF output enable after<br>PD# de-assertion                                                                                                                                              |           |        | 300                   | us     | 1,3   |

| Tfall                            | $t_{F}$               | Fall time of control inputs                                                                                                                                                              |           |        | 10                    | ns     | 1,2   |

| Trise                            | $t_R$                 | Rise time of control inputs                                                                                                                                                              |           |        | 10                    | ns     | 1,2   |

| SMBus Input Low Voltage          | $V_{ILSMB}$           |                                                                                                                                                                                          |           |        | 0.8                   | V      | 1     |

| SMBus Input High Voltage         | $V_{IHSMB}$           |                                                                                                                                                                                          | 2.1       |        | V <sub>DDSMB</sub>    | V      | 1     |

| SMBus Output Low Voltage         | $V_{OLSMB}$           | At I <sub>PULLUP</sub>                                                                                                                                                                   |           |        | 0.4                   | V      | 1     |

| SMBus Sink Current               | I <sub>PULLUP</sub>   | At V <sub>OL</sub>                                                                                                                                                                       | 4         |        |                       | mA     | 1     |

| Nominal Bus Voltage              | $V_{DDSMB}$           | 3V to 5V +/- 10%                                                                                                                                                                         | 2.7       |        | 5.5                   | V      | 1     |

| SCLK/SDATA Rise Time             | t <sub>RSMB</sub>     | (Max VIL - 0.15) to (Min VIH + 0.15)                                                                                                                                                     |           |        | 1000                  | ns     | 1     |

| SCLK/SDATA Fall Time             | t <sub>FSMB</sub>     | (Min VIH + 0.15) to (Max VIL - 0.15)                                                                                                                                                     |           |        | 300                   | ns     | 1     |

| SMBus Operating<br>Frequency     | f <sub>MAXSMB</sub>   | Maximum SMBus operating frequency                                                                                                                                                        |           |        | 100                   | kHz    | 1,5   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

$<sup>^{2}\,\</sup>mbox{Control}$  input must be monotonic from 20% to 80% of input swing.

$<sup>^3</sup>$  Time from deassertion until outputs are > 200mV.

<sup>&</sup>lt;sup>4</sup> DIF\_IN input.

$<sup>^{\</sup>rm 5}$  The differential input clock must be running for the SMBus to be active.

# **Electrical Characteristics-DIF 0.7V Low Power HCSL Outputs**

$T_A = T_{COM}$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER              | SYMBOL     | CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNITS  | NOTES   |

|------------------------|------------|-----------------------------------------------------------------------------------------|------|------|------|--------|---------|

| Slew rate              | Trf        | Scope averaging on                                                                      | 1    | 2.9  | 4    | V/ns   | 1, 2, 3 |

| Slew rate matching     | ΔTrf       | Slew rate matching, Scope averaging on                                                  |      | 7    | 20   | %      | 1, 2, 4 |

| Voltage High           | VHigh      | Statistical measurement on single-ended signal using oscilloscope math function. (Scope | 660  | 754  | 850  | mV     | 1       |

| Voltage Low            | VLow       | averaging on)                                                                           | -150 | 62   | 150  | ] '''V | 1       |

| Max Voltage            | Vmax       | Measurement on single ended signal using                                                |      | 827  | 1150 | mV     | 1       |

| Min Voltage            | Vmin       | absolute value. (Scope averaging off)                                                   | -300 | 10   |      | IIIV   | 1       |

| Vswing                 | Vswing     | Scope averaging off                                                                     | 300  | 1395 |      | mV     | 1, 2    |

| Crossing Voltage (abs) | Vcross_abs | Scope averaging off                                                                     | 300  | 453  | 550  | mV     | 1, 5    |

| Crossing Voltage (var) | Δ-Vcross   | Scope averaging off                                                                     |      | 14   | 140  | mV     | 1, 6    |

$<sup>^{1}</sup>$ Guaranteed by design and characterization, not 100% tested in production.  $C_L$  = 2pF, Zo = 85 $\Omega$  differential trace impedance).

# **Electrical Characteristics-Current Consumption**

$T_A = T_{COM}$ ; Supply Voltage  $V_{DD} = 3.3 V + /-5\%$

| PARAMETER         | SYMBOL                 | CONDITIONS                     | MIN | TYP | MAX | UNITS                           | NOTES |

|-------------------|------------------------|--------------------------------|-----|-----|-----|---------------------------------|-------|

|                   | I <sub>DDVDDR</sub>    | 100MHz, VDDR rail              |     | 4   | 6   | mA                              | 1     |

| Operating Current | I <sub>DDVDDAPLL</sub> | 100MHz, VDDA rail, PLL Mode    |     | 14  | 20  | mA                              | 1     |

| Operating Current | I <sub>DDVDDABYP</sub> | 100MHz, VDDA rail, Bypass Mode |     | 3   | 5   | mA                              | 1     |

|                   | I <sub>DDVDD</sub>     | 100MHz, VDD rail               |     | 41  | 50  | mA                              | 1     |

|                   | I <sub>DDVDDRPD</sub>  | Power Down, VDDR Rail          |     | 3.5 | 5   | mA                              | 1     |

| Powerdown Current | I <sub>DDVDDAPD</sub>  | Power Down, VDDA Rail          |     | 1.6 | 3   | mA                              | 1     |

|                   | I <sub>DDVDDPD</sub>   | Power Down, VDD Rail           |     | 0.3 | 2   | 20 mA<br>5 mA<br>50 mA<br>55 mA | 1     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0V. This results in a +/-150mV window around differential 0V.

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a +/-75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

$<sup>^{2}</sup>$  C<sub>L</sub> = 2pF, Zo = 85 $\Omega$  differential trace impedance

## **Electrical Characteristics-Skew and Differential Jitter Parameters**

$T_A = T_{COM}$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                   | SYMBOL                | CONDITIONS                                                                               | MIN  | TYP  | MAX | UNITS       | NOTES     |

|-----------------------------|-----------------------|------------------------------------------------------------------------------------------|------|------|-----|-------------|-----------|

| CLK_IN, DIF[x:0]            | t <sub>SPO_PLL</sub>  | In-to-Out Skew in PLL mode @ 100MHz<br>nominal value @35°C, 3.3V                         | -100 | 53   | 100 | ps          | 1,2,4,5,8 |

| CLK_IN, DIF[x:0]            | t <sub>PD_BYP</sub>   | In-to-Out Skew in Bypass mode @ 100MHz<br>nominal value @ 35°C, 3.3V                     | 2.5  | 3.4  | 4.5 | ns          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]            | t <sub>DSPO_PLL</sub> | In-to-Out Skew Variation in PLL mode across voltage and temperature                      | -50  | 0    | 50  | ps          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]            | t <sub>DSPO_BYP</sub> | In-to-Out Skew Variation in Bypass mode across voltage and temperature                   | -250 | 0    | 250 | ps          | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]            | t <sub>DTE</sub>      | Random Differential Tracking error between two 9ZX devices in Hi BW Mode                 |      | 3    | 5   | ps<br>(rms) | 1,2,3,5,8 |

| CLK_IN, DIF[x:0]            | t <sub>DSSTE</sub>    | Random Differential Spread Spectrum Tracking error between two 9ZX devices in Hi BW Mode |      | 15   | 75  | ps          | 1,2,3,5,8 |

| DIF{x:0]                    | t <sub>SKEW_ALL</sub> | Output-to-Output Skew across all outputs<br>(Common to Bypass and PLL mode)              |      | 39   | 65  | ps          | 1,2,3,8   |

| PLL Jitter Peaking          | jpeak-hibw            | LOBW#_BYPASS_HIBW = 1                                                                    |      |      | 2.5 | dB          | 7,8       |

| PLL Jitter Peaking          | jpeak-lobw            | LOBW#_BYPASS_HIBW = 0                                                                    |      |      | 2   | dB          | 7,8       |

| PLL Bandwidth               | pll <sub>HIBW</sub>   | LOBW#_BYPASS_HIBW = 1                                                                    |      |      | 4   | MHz         | 8,9       |

| PLL Bandwidth               | pll <sub>LOBW</sub>   | LOBW#_BYPASS_HIBW = 0                                                                    |      |      | 1.4 | MHz         | 8,9       |

| Duty Cycle                  | t <sub>DC</sub>       | Measured differentially, PLL Mode                                                        | 45   | 50.1 | 55  | %           | 1         |

| Duty Cycle Distortion       | t <sub>DCD</sub>      | Measured differentially, Bypass Mode<br>@100MHz                                          |      | -1.7 | 2   | %           | 1,10      |

| Jitter, Cycle to cycle      | t <sub>jcyc-cyc</sub> | PLL mode                                                                                 |      | 14   | 50  | ps          | 1,11      |

| Notes for a second to eyele | gcy c-cy c            | Additive Jitter in Bypass Mode                                                           |      | 0    | 25  | ps          | 1,11      |

#### Notes for preceding table:

<sup>1</sup> C<sub>L</sub> = 2pF, Zo = 85Ω differential trace impedance. Input to output skew is measured at the first output edge following the corresponding input.

<sup>&</sup>lt;sup>2</sup> Measured from differential cross-point to differential cross-point. This parameter can be tuned with external feedback path, if present.

<sup>&</sup>lt;sup>3</sup> All Bypass Mode Input-to-Output specs refer to the timing between an input edge and the specific output edge created by it.

<sup>&</sup>lt;sup>4</sup> This parameter is deterministic for a given device

<sup>&</sup>lt;sup>5</sup> Measured with scope averaging on to find mean value.

<sup>&</sup>lt;sup>6</sup> t is the period of the input clock

<sup>&</sup>lt;sup>7</sup> Measured as maximum pass band gain. At frequencies within the loop BW, highest point of magnification is called PLL jitter peaking.

<sup>&</sup>lt;sup>8.</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>9</sup> Measured at 3 db down or half power point.

<sup>&</sup>lt;sup>10</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock when the device is operated in bypass mode.

<sup>&</sup>lt;sup>11</sup> Measured from differential waveform

## **Electrical Characteristics-Phase Jitter Parameters**

$T_A = T_{COM}$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V +/-5}\%$

| PARAMETER                             | SYMBOL                  | CONDITIONS                                                              | MIN | TYP  | MAX  | INDUSTRY<br>LIMIT | UNITS       | Notes   |

|---------------------------------------|-------------------------|-------------------------------------------------------------------------|-----|------|------|-------------------|-------------|---------|

|                                       | t <sub>jphPCleG1</sub>  | PCIe Gen 1                                                              |     | 43   | 46   | 86                | ps (p-p)    | 1,2,3   |

|                                       |                         | PCle Gen 2 Lo Band<br>10kHz < f < 1.5MHz                                |     | 1.4  | 1.5  | 3                 | ps<br>(rms) | 1,2     |

|                                       | t <sub>jphPCIeG2</sub>  | PCle Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)                    |     | 2.4  | 2.7  | 3.1               | ps<br>(rms) | 1,2     |

|                                       | t <sub>jphPCIeG3</sub>  | PCIe Gen 3<br>(PLL BW of 2-4MHz, 2-5MHz, CDR = 10MHz)                   |     | 0.56 | 0.61 | 1                 | ps<br>(rms) | 1,2,4   |

| Phase Jitter, PLL Mode                |                         | QPI & SMI<br>( PLL BW of 17.04MHz 100/133MHz, 4.8Gb/s,<br>6.4Gb/s 12UI) |     | 0.27 | 0.51 | 1                 | ps<br>(rms) | 1,5     |

|                                       | t <sub>jphQPI_SMI</sub> | QPI & SMI<br>( PLL BW of 7.8MHz 100/133MHz, 4.8Gb/s,<br>6.4Gb/s 12UI)   |     | 0.22 | 0.49 | 0.5               | ps<br>(rms) | 1,5     |

|                                       |                         | QPI & SMI<br>(100MHz, 8.0Gb/s, 12UI)                                    |     | 0.16 | 0.28 | 0.3               | ps<br>(rms) | 1,5     |

|                                       |                         | QPI & SMI<br>(100MHz, 9.6Gb/s, 12UI)                                    |     | 0.11 | 0.17 | 0.2               | ps<br>(rms) | 1,5     |

|                                       | t <sub>jphPCleG1</sub>  | PCle Gen 1                                                              |     | 1    | 5    | N/A               | ps (p-p)    | 1,2,3   |

|                                       | t <sub>iphPCIeG2</sub>  | PCle Gen 2 Lo Band<br>10kHz < f < 1.5MHz                                |     | 0.0  | 0.0  | N/A               | ps<br>(rms) | 1,2,6   |

|                                       | gpnPCTeG2               | PCle Gen 2 High Band<br>1.5MHz < f < Nyquist (50MHz)                    |     | 0.0  | 0.0  | N/A               | ps<br>(rms) | 1,2,6   |

|                                       | t <sub>jphPCIeG3</sub>  | PCle Gen 3<br>(PLL BW of 2-4MHz, 2-5MHz, CDR = 10MHz)                   |     | 0.0  | 0.0  | N/A               | ps<br>(rms) | 1,2,4,6 |

| Additive Phase Jitter,<br>Bypass mode |                         | QPI & SMI<br>( PLL BW of 17.04MHz 100/133MHz, 4.8Gb/s,<br>6.4Gb/s 12UI) |     | 0.25 | 0.3  | N/A               | ps<br>(rms) | 1,5,6   |

|                                       | t <sub>jphQPI_SMI</sub> | QPI & SMI<br>( PLL BW of 7.8MHz 100/133MHz, 4.8Gb/s,<br>6.4Gb/s 12UI)   |     | 0.10 | 0.15 | N/A               | ps<br>(rms) | 1,5,6   |

|                                       |                         | QPI & SMI<br>(100MHz, 8.0Gb/s, 12UI)                                    |     | 0.0  | 0.0  | N/A               | ps<br>(rms) | 1,5,6   |

|                                       |                         | QPI & SMI<br>(100MHz, 9.6Gb/s, 12UI)                                    |     | 0.0  | 0.0  | N/A               | ps<br>(rms) | 1,5,6   |

<sup>&</sup>lt;sup>1</sup> Applies to all outputs.

$<sup>^2\,\</sup>mbox{See}$  http://www.pcisig.com for complete specs.

<sup>&</sup>lt;sup>3</sup> Sample size of at least 100K cycles. This figure extrapolates to 108ps pk-pk at 1M cycles for a BER of 1<sup>-12</sup>.

<sup>&</sup>lt;sup>4</sup> Subject to final ratification by PCI SIG.

<sup>&</sup>lt;sup>5</sup> Calculated from Intel-supplied clock jitter tool.

<sup>&</sup>lt;sup>6</sup> For RMS figures, additive jitter is calculated by solving the following equation: (Additive jitter)<sup>2</sup> = (total jitter)<sup>2</sup> - (input jitter)<sup>2</sup>.

# Clock Periods-Differential Outputs with Spread Spectrum Disabled

|         |              |                              | Measurement Window                   |                                      |                            |                                      |                                      |                              |       |       |

|---------|--------------|------------------------------|--------------------------------------|--------------------------------------|----------------------------|--------------------------------------|--------------------------------------|------------------------------|-------|-------|

|         | Center       | 1 Clock                      | 1us                                  | 0.1s                                 | 0.1s                       | 0.1s                                 | 1us                                  | 1 Clock                      |       |       |

| SSC OFF | Freq.<br>MHz | -c2c jitter<br>AbsPer<br>Min | -SSC<br>Short-Term<br>Average<br>Min | - ppm<br>Long-Term<br>Average<br>Min | 0 ppm<br>Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Max | +SSC<br>Short-Term<br>Average<br>Max | +c2c jitter<br>AbsPer<br>Max | Units | Notes |

| DIF     | 100.00       | 9.94900                      |                                      | 9.99900                              | 10.00000                   | 10.00100                             |                                      | 10.05100                     | ns    | 1,2,3 |

# Clock Periods-Differential Outputs with Spread Spectrum Enabled

| Conto  |                        | Measurement Window           |                                      |                                      |                            |                                      |                                      |                              |       |       |

|--------|------------------------|------------------------------|--------------------------------------|--------------------------------------|----------------------------|--------------------------------------|--------------------------------------|------------------------------|-------|-------|

|        | Contor                 | 1 Clock                      | 1us                                  | 0.1s                                 | 0.1s                       | 0.1s                                 | 1us                                  | 1 Clock                      |       |       |

| SSC ON | Center<br>Freq.<br>MHz | -c2c jitter<br>AbsPer<br>Min | -SSC<br>Short-Term<br>Average<br>Min | - ppm<br>Long-Term<br>Average<br>Min | 0 ppm<br>Period<br>Nominal | + ppm<br>Long-Term<br>Average<br>Max | +SSC<br>Short-Term<br>Average<br>Max | +c2c jitter<br>AbsPer<br>Max | Units | Notes |

| DIF    | 99.75                  | 9.94906                      | 9.99906                              | 10.02406                             | 10.02506                   | 10.02607                             | 10.05107                             | 10.10107                     | ns    | 1,2,3 |

#### Notes

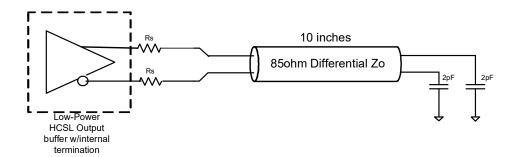

## **Test Loads**

## **Differential Output Terminations**

| DIF Zo (Ω) | Rs (Ω) |

|------------|--------|

| 100        | 7      |

| 85         | 0      |

Note: No resistors are required for connection to 85ohm transmission lines.

<sup>&</sup>lt;sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> All Long Term Accuracy specifications are guaranteed with the assumption that the input clock complies with CK420BQ/CK410B+ accuracy requirements (+/-100ppm). The 9ZXL0651 itself does not contribute to ppm error.

<sup>&</sup>lt;sup>3</sup> Driven by SRC output of main clock, 100 MHz PLL Mode or Bypass mode

## General SMBus Serial Interface Information for 9ZXL0651

#### **How to Write**

- · Controller (host) sends a start bit

- · Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- Controller (host) sends the byte count = X

- Renesas clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- Renesas clock will acknowledge each byte one at a time

- Controller (host) sends a Stop bit

|           | Index BI  | ock '  | Write Operation          |

|-----------|-----------|--------|--------------------------|

| Controll  | er (Host) |        | Renesas (Slave/Receiver) |

| Т         | starT bit |        |                          |

| Slave A   | Address   |        |                          |

| WR        | WRite     |        |                          |

|           |           |        | ACK                      |

| Beginning | Byte = N  |        |                          |

|           |           |        | ACK                      |

| Data Byte | Count = X |        |                          |

|           |           |        | ACK                      |

| Beginnin  | g Byte N  |        |                          |

|           |           |        | ACK                      |

| 0         |           | ×      |                          |

| 0         |           | X Byte | 0                        |

| 0         |           | (Đ     | 0                        |

|           |           |        | 0                        |

| Byte N    | + X - 1   |        |                          |

|           |           |        | ACK                      |

| Р         | stoP bit  |        |                          |

#### **How to Read**

- Controller (host) will send a start bit

- · Controller (host) sends the write address

- Renesas clock will acknowledge

- Controller (host) sends the beginning byte location = N

- Renesas clock will acknowledge

- · Controller (host) will send a separate start bit

- · Controller (host) sends the read address

- Renesas clock will acknowledge

- Renesas clock will send the data byte count = X

- Renesas clock sends Byte N+X-1

- Renesas clock sends Byte 0 through Byte X (if X<sub>(H)</sub> was written to Byte 8)

- · Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- · Controller (host) will send a stop bit

|      | Index Block F   | Read O | peration          |

|------|-----------------|--------|-------------------|

| Cor  | ntroller (Host) |        | Renesas           |

| Т    | starT bit       |        |                   |

| SI   | ave Address     |        |                   |

| WR   | WRite           |        |                   |

|      |                 |        | ACK               |

| Begi | nning Byte = N  |        |                   |

|      |                 |        | ACK               |

| RT   | Repeat starT    |        |                   |

| SI   | ave Address     |        |                   |

| RD   | ReaD            |        |                   |

|      |                 |        | ACK               |

|      |                 |        |                   |

|      |                 |        | Data Byte Count=X |

|      | ACK             |        |                   |

|      |                 |        | Beginning Byte N  |

|      | ACK             |        |                   |

|      |                 | த      | 0                 |

|      | 0               | X Byte | 0                 |

|      | 0               | ×      | 0                 |

|      | 0               |        |                   |

|      |                 |        | Byte N + X - 1    |

| N    | Not acknowledge |        |                   |

| Р    | stoP bit        |        |                   |

SMBusTable: PLL Mode, and Frequency Select Register

| Byte  | 0 Pin# | Name       | Control Function             | Type | 0          | 1                      | Default |  |

|-------|--------|------------|------------------------------|------|------------|------------------------|---------|--|

| Bit 7 | 2      | PLL Mode 1 | PLL Operating Mode Rd back 1 | R    | See PLL Op | See PLL Operating Mode |         |  |

| Bit 6 | 2      | PLL Mode 0 | PLL Operating Mode Rd back 0 | R    | Readba     | Latch                  |         |  |

| Bit 5 |        |            | Reserved                     |      |            |                        | 0       |  |

| Bit 4 |        |            | Reserved                     |      |            |                        |         |  |

| Bit 3 |        | PLL_SW_EN  | Enable S/W control of PLL BW | RW   | HW Latch   | SMBus Control          | 0       |  |

| Bit 2 |        | PLL Mode 1 | PLL Operating Mode 1         | RW   | See PLL Op | erating Mode           | 1       |  |

| Bit 1 |        | PLL Mode 0 | PLL Operating Mode 1         | RW   | Readba     | ck Table               | 1       |  |

| Bit 0 |        |            | Reserved                     |      |            |                        |         |  |

**Note:** Setting bit 3 to '1' allows the user to override the Latch value from pin 5 via use of bits 2 and 1. Use the values from the PLL Operating Mode Readback Table. Note that Bits 7 and 6 will keep the value originally latched on pin 5. A warm reset of the system will have to accomplished if the user changes these bits.

SMBusTable: Output Control Register

| Byte  | e 1 | Pin#  | Name     | Control Function                       | Туре | 0       | 1       | Default |  |

|-------|-----|-------|----------|----------------------------------------|------|---------|---------|---------|--|

| Bit 7 |     |       |          | Reserved                               |      |         |         | 1       |  |

| Bit 6 | 2   | 26/27 | DIF_3_En | Output Control - '0' overrides OE# pin | RW   | Low/Low | Enable  | 1       |  |

| Bit 5 | 2   | 23/24 | DIF_2_En | Output Control - '0' overrides OE# pin | RW   | LOW/LOW | Ellable | 1       |  |

| Bit 4 |     |       |          | Reserved                               |      |         |         |         |  |

| Bit 3 |     |       |          | Reserved                               |      |         |         | 1       |  |

| Bit 2 | 1   | 17/18 | DIF_1_En | Output Control - '0' overrides OE# pin | RW   | Low/Low | Enable  | 1       |  |

| Bit 1 | 1   | 14/15 | DIF_0_En | Output Control - '0' overrides OE# pin | RW   | LOW/LOW | Ellable | 1       |  |

| Bit 0 |     |       |          | Reserved                               |      |         |         | 1       |  |

SMBusTable: Output Control Register

| Byte  | e 2 | Pin# | Name     | Control Function                       | Type | 0       | 1      | Default |  |  |

|-------|-----|------|----------|----------------------------------------|------|---------|--------|---------|--|--|

| Bit 7 |     |      |          | Reserved                               |      |         |        | 0       |  |  |

| Bit 6 |     |      |          | Reserved                               |      |         |        |         |  |  |

| Bit 5 |     |      |          | Reserved                               |      |         |        |         |  |  |

| Bit 4 |     |      |          | Reserved                               |      |         |        |         |  |  |

| Bit 3 |     |      |          | Reserved                               |      |         |        | 1       |  |  |

| Bit 2 | 3   | 6/37 | DIF_5_En | Output Control - '0' overrides OE# pin | RW   | Low/Low | Enable | 1       |  |  |

| Bit 1 | 3   | 3/34 | DIF_4_En | Output Control - '0' overrides OE# pin | RW   | LOW/LOW | Enable | 1       |  |  |

| Bit 0 |     |      |          | Reserved                               |      |         |        |         |  |  |

SMBusTable: Reserved Register

| Byte  | e 3 | Pin# | Name     | Control Function | Type | 0 | 1 | Default |  |  |

|-------|-----|------|----------|------------------|------|---|---|---------|--|--|

| Bit 7 |     |      |          | Reserved         |      |   |   | 0       |  |  |

| Bit 6 |     |      |          | Reserved         |      |   |   |         |  |  |

| Bit 5 |     |      |          | Reserved         |      |   |   |         |  |  |

| Bit 4 |     |      | Reserved |                  |      |   |   |         |  |  |

| Bit 3 |     |      |          | Reserved         |      |   |   | 0       |  |  |

| Bit 2 |     |      |          | Reserved         |      |   |   | 0       |  |  |

| Bit 1 |     |      |          | Reserved         |      |   |   | 0       |  |  |

| Bit 0 |     |      |          | Reserved         |      |   |   | 0       |  |  |

SMBusTable: Reserved Register

| Byte 4 | Pin # | Name | Control Function | Туре | 0 | 1 | Default |

|--------|-------|------|------------------|------|---|---|---------|

| Bit 7  |       |      | Reserved         |      |   |   | 0       |

| Bit 6  |       |      | Reserved         |      |   |   | 0       |

| Bit 5  |       |      | Reserved         |      |   |   | 0       |

| Bit 4  |       |      | Reserved         |      |   |   | 0       |

| Bit 3  |       |      | Reserved         |      |   |   | 0       |

| Bit 2  |       |      | Reserved         |      |   |   | 0       |

| Bit 1  |       |      | Reserved         |      |   |   | 0       |

| Bit 0  |       |      | Reserved         |      |   |   | 0       |

SMBusTable: Vendor & Revision ID Register

| Byte ! | 5 Pin # | Name | Control Function | Type | 0     | 1 | Default |

|--------|---------|------|------------------|------|-------|---|---------|

| Bit 7  | -       | RID3 |                  | R    |       | Х |         |

| Bit 6  | -       | RID2 | REVISION ID      | R    | A rev | X |         |

| Bit 5  | -       | RID1 |                  | R    | A IEV | X |         |

| Bit 4  | -       | RID0 |                  | R    |       | X |         |

| Bit 3  | -       | VID3 |                  | R    | -     | - | 0       |

| Bit 2  | -       | VID2 | VENDOR ID        | R    | -     | - | 0       |

| Bit 1  | -       | VID1 | VENDOR ID        | R    | -     | - | 0       |

| Bit 0  | -       | VID0 |                  | R    | -     | - | 1       |

SMBusTable: DEVICE ID

| Byte 6 Pin # |   | Name Control Function |                  | Type | 0  | 1   | Default |

|--------------|---|-----------------------|------------------|------|----|-----|---------|

| Bit 7        |   | De                    | evice ID 7 (MSB) | R    | ₹  |     |         |

| Bit 6        |   |                       | Device ID 6      | R    |    | 1   |         |

| Bit 5        |   |                       | Device ID 5      | R    |    |     | 1       |

| Bit 4        |   |                       | Device ID 4      | R    | гв | Hex | 1       |

| Bit 3        |   |                       | Device ID 3      | R    | ГБ | пех | 1       |

| Bit 2        | - |                       | Device ID 2      | R    |    |     | 0       |

| Bit 1        |   |                       | Device ID 1      | R    |    | 1   |         |

| Bit 0        | - |                       | Device ID 0      | R    |    |     | 1       |

SMBusTable: Byte Count Register

| Byte 7 | Pin # | Name | Control Function                        | Type | 0                | 1 | Default |  |  |

|--------|-------|------|-----------------------------------------|------|------------------|---|---------|--|--|

| Bit 7  |       |      | Reserved                                |      |                  |   |         |  |  |

| Bit 6  |       |      | Reserved                                |      |                  |   |         |  |  |

| Bit 5  |       |      | Reserved                                |      |                  |   |         |  |  |

| Bit 4  | -     | BC4  |                                         | RW   |                  |   | 0       |  |  |

| Bit 3  | -     | BC3  | Writing to this register configures how | RW   | Default value    | 1 |         |  |  |

| Bit 2  | -     | BC2  |                                         | RW   | bytes (0 to 8) v | 0 |         |  |  |

| Bit 1  | -     | BC1  | many bytes will be read back.           | RW   | by de            | 0 |         |  |  |

| Bit 0  | -     | BC0  |                                         | RW   | ] '              |   | 0       |  |  |

SMBusTable: Reserved Register

| Byte 8 Pin # Name |  | Name     | Control Function | Type   | 0 | 1 | Default |  |

|-------------------|--|----------|------------------|--------|---|---|---------|--|

| Bit 7             |  |          | Reserved         |        |   |   | 0       |  |

| Bit 6             |  |          | Reserved         | served |   |   |         |  |

| Bit 5             |  | Reserved |                  |        |   |   | 0       |  |

| Bit 4             |  | Reserved |                  |        |   |   | 0       |  |

| Bit 3             |  | Reserved |                  |        |   |   | 0       |  |

| Bit 2             |  |          | Reserved         |        |   |   | 0       |  |

| Bit 1             |  | Reserved |                  |        |   |   | 0       |  |

| Bit 0             |  |          | Reserved         |        |   |   | 0       |  |

# **Marking Diagram**

- · Line 2: truncated part number; "L" denotes RoHS compliant package.

- Line 3: "YYWW" is the last two digits of the year and week that the part was assembled.

- Line 4: "COO": country of origin.

- Line 5: "LOT" denotes the lot number.

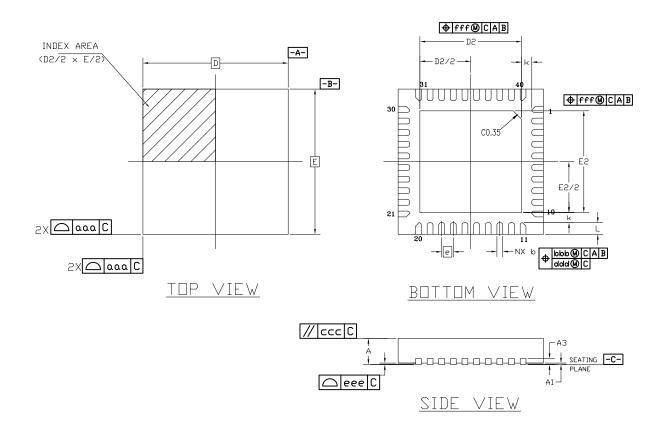

# **Package Outline Drawings**

The package outline drawings are appended at the end of this document. The package information is the most current data available.

# **Ordering Information**

| Part / Order Number |          | Shipping Package | Package       | Temperature |  |

|---------------------|----------|------------------|---------------|-------------|--|

| 9ZXL0651AKLF        |          | Trays            | 40-pin VFQFPN | 0 to +70°C  |  |

| 9ZXL0               | 551AKLFT | Tape and Reel    | 40-pin VFQFPN | 0 to +70°C  |  |

<sup>&</sup>quot;LF" suffix to the part number denotes Pb-Free configuration, RoHS compliant.

# **Revision History**

| Revision Date                                                                             | Description                                                                                 |  |  |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| October 31, 2013 Updated Electrical Tables with characterization data and moved to final. |                                                                                             |  |  |  |  |

| November 25, 2014                                                                         | 1. Updates to Byte 6, bits 7:4; default should be "1".                                      |  |  |  |  |

| November 25, 2014                                                                         | 2. Updated device ID in Byte 6 from "8B" to "FB".                                           |  |  |  |  |

| March 30, 2015                                                                            | 1. Corrected Test Loads to remove references to IREF and Rp. These are not present on parts |  |  |  |  |

| Walcii 30, 2013                                                                           | that have LP-HCSL outputs.                                                                  |  |  |  |  |

| November 20, 2015                                                                         | 1. Updated QPI references to QPI/UPI                                                        |  |  |  |  |

| November 20, 2013                                                                         | 2. Updated DIF_IN table to match PCI SIG specification, no silicon change                   |  |  |  |  |

|                                                                                           | 1. Updated input frequency minimum values from 33MHz to 25MHz.                              |  |  |  |  |

| January 28, 2021                                                                          | 2. Added "25MHz PFT clock delay management" bullet to Features section on cover page.       |  |  |  |  |

| January 20, 2021                                                                          | 3. Reformatted headers and footers to Renesas.                                              |  |  |  |  |

|                                                                                           | 4. Updated Marking Diagram and Package Outline Drawings sections.                           |  |  |  |  |

<sup>&</sup>quot;A" is the device revision designator (will not correlate with the datasheet revision).

|     | REVISIONS       |         |          |  |  |  |  |

|-----|-----------------|---------|----------|--|--|--|--|

| REV | DESCRIPTION     | DATE    | APPROVED |  |  |  |  |

| 00  | INITIAL RELEASE | 5/17/16 | JH       |  |  |  |  |

| SYMBOL | DIMENSION |         |        |  |  |  |

|--------|-----------|---------|--------|--|--|--|

| P      | MIN       | NOM     | MAX    |  |  |  |

| b      | 0.15      | 0.20    | 0.25   |  |  |  |

| D      | 5         | .00 BSC |        |  |  |  |

| Е      | 5         | .00 BSC |        |  |  |  |

| D2     | 3.40      | 3.50    | 3.60   |  |  |  |

| E2     | 3.40      | 3.50    | 3.60   |  |  |  |

| L      | 0.30      | 0.40    | 0.50   |  |  |  |

| е      | C         | .40 BSC |        |  |  |  |

| N      |           | 40      |        |  |  |  |

| ND     |           |         | ote 3) |  |  |  |

| NE     |           | 10 (n   | ote 3) |  |  |  |

| Α      | 0.80      | 0.90    | 1.00   |  |  |  |

| A1     | 0.00      | 0.02    | 0.05   |  |  |  |

| A3     |           | 0.2 REF |        |  |  |  |

| k      |           | 0.35 RE | F      |  |  |  |

| aaa    | 0.10      |         |        |  |  |  |

| bbb    |           | 0.07    |        |  |  |  |

| ccc    | 0.10      |         |        |  |  |  |

| ddd    | 0.05      |         |        |  |  |  |

| eee    |           | 0.08    |        |  |  |  |

| fff    |           | 0.10    |        |  |  |  |

#### NOTES:

- 1. ALL DIMENSIONING AND TOLERANCING CONFORM TO ANSI Y14.5M-1982

- 2 ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

| TOLERANCES<br>UNLESS SPEC<br>DECIMAL<br>X±.1<br>XX±.05<br>XXX± .030 | ANGULAR  | W.                   | TM VAL                        | 6024 SILVER CREEK<br>VALLEY ROAD. SAN JOSE,<br>CA 95138<br>PHONE: (408) 284-8200<br>FAX: (408) 284-3572 |         |       |  |

|---------------------------------------------------------------------|----------|----------------------|-------------------------------|---------------------------------------------------------------------------------------------------------|---------|-------|--|

| APPROVALS                                                           | DATE     |                      | TITLEND/NDG40 PACKAGE OUTLINE |                                                                                                         |         |       |  |

| DRAWN Mæ                                                            | 05/31/10 |                      | .0 x 5.0 mm BODY,E            |                                                                                                         | 3.50mr  | n SQ. |  |

| CHECKED                                                             |          | 0                    | .40 mm PITCH QFN              |                                                                                                         |         |       |  |

|                                                                     |          | SIZE                 | DRAWING No.                   |                                                                                                         |         | REV   |  |

|                                                                     |          | С                    | PSC-429.                      | 2-                                                                                                      | 02      | 00    |  |

|                                                                     |          | DO NOT SCALE DRAWING |                               |                                                                                                         | SHEET 1 | OF 2  |  |

|     | REVISIONS       |         |          |  |  |  |  |

|-----|-----------------|---------|----------|--|--|--|--|

| REV | DESCRIPTION     | DATE    | APPROVED |  |  |  |  |

| 00  | INITIAL RELEASE | 5/17/16 | JH       |  |  |  |  |

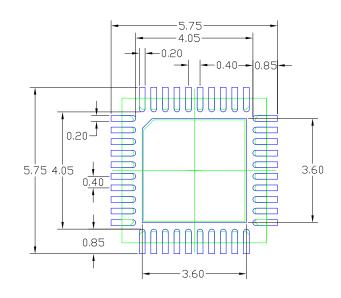

## RECOMMENDED LAND PATTERN

#### NOTES:

- 1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

- 2. TOP DOWN VIEW AS VIEWED ON PCB.

- 3. COMPONENT OUTLINE SHOWS FOR REFERENCE IN GREEN.

4. LAND PATTERN IN BLUE. NSMD PATTERN ASSUMED.

5. LAND PATTERN RECOMMENDATION PER IPC-7351B GENERIC REQUIREMENT FOR SURFACE MOUNT DESIGN AND LAND PATTERN.

| TOLERANCES<br>UNLESS SPECIFIED |          |       | 72                               |         | ÆR CREEK<br>OAD. SAN ( | JOSE, |  |

|--------------------------------|----------|-------|----------------------------------|---------|------------------------|-------|--|

| DECIMAL                        |          |       | TM VAI                           | 95138   |                        | ·     |  |

|                                | ±1°      | 4     |                                  | ONE: (4 | 108) 284-82            | 200   |  |

| XX±.05<br>XXX± .030            |          | W     | /ww.IDT.com FAX                  | X: (408 | ) 284-3572             | !     |  |

| APPROVALS                      | DATE     |       | D/NDG40 PACKAGE (                |         |                        |       |  |

| DRAWN Mæ                       | 05/31/10 | 5     | 5.0 x 5.0 mm BODY,EPAD 3.50mm SQ |         |                        |       |  |

| CHECKED                        |          | 0     | .40 mm PITCH QFN                 | 1       |                        |       |  |

|                                |          | SIZE  | DRAWING No.                      |         |                        | REV   |  |

|                                |          | C     | PSC-429                          | 2-      | 02                     | 00    |  |

|                                |          | DO NO | T SCALE DRAWING                  |         | SHEET 2                | OF 2  |  |