# A7986A

## 3 A step-down switching regulator for automotive applications

#### Datasheet - production data

### Features

- AEC-Q100 qualified

- 3 A DC output current

- 4.5 V to 38 V input voltage

- Output voltage adjustable from 0.6 V

- 250 kHz switching frequency, programmable up to 1 MHz

- Internal soft-start and enable

- Low dropout operation: 100% duty cycle

- Voltage feed-forward

- Zero load current operation

- Overcurrent and thermal protection

- HSOP8 package

## **Applications**

- · Dedicated to automotive applications

- Automotive LED driving

## Description

The A7986A is a step-down switching regulator with a 3.7 A (min.) current limited embedded power MOSFET, so it is able to deliver up to 3 A current to the load depending on the application conditions.

The input voltage can range from 4.5 V to 38 V, while the output voltage can be set starting from 0.6 V to VIN.

Requiring a minimum set of external components, the device includes an internal 250 kHz switching frequency oscillator that can be externally adjusted up to 1 MHz.

The HSOP8 package with exposed pad allows the reduction of  $R_{th(JA)}$  down to 40  $^\circ\text{C/W}.$

#### February 2017

DocID022801 Rev 8

This is information on a product in full production.

1/42

## Contents

| 1 | Pin settings |                                     |  |  |

|---|--------------|-------------------------------------|--|--|

|   | 1.1          | Pin connection                      |  |  |

|   | 1.2          | Pin description                     |  |  |

| 2 | Maxir        | num ratings                         |  |  |

| 3 | Thern        | nal data                            |  |  |

| 4 | Elect        | rical characteristics6              |  |  |

| 5 | Funct        | tional description                  |  |  |

|   | 5.1          | Oscillator and synchronization      |  |  |

|   | 5.2          | Soft-start                          |  |  |

|   | 5.3          | Error amplifier and compensation    |  |  |

|   | 5.4          | Overcurrent protection              |  |  |

|   | 5.5          | Enable function                     |  |  |

|   | 5.6          | Hysteretic thermal shutdown 14      |  |  |

| 6 | Appli        | cation information                  |  |  |

|   | 6.1          | Input capacitor selection           |  |  |

|   | 6.2          | Inductor selection                  |  |  |

|   | 6.3          | Output capacitor selection 17       |  |  |

|   | 6.4          | Compensation network                |  |  |

|   |              | 6.4.1 Type III compensation network |  |  |

|   |              | 6.4.2 Type II compensation network  |  |  |

|   | 6.5          | Thermal considerations              |  |  |

|   | 6.6          | Layout considerations               |  |  |

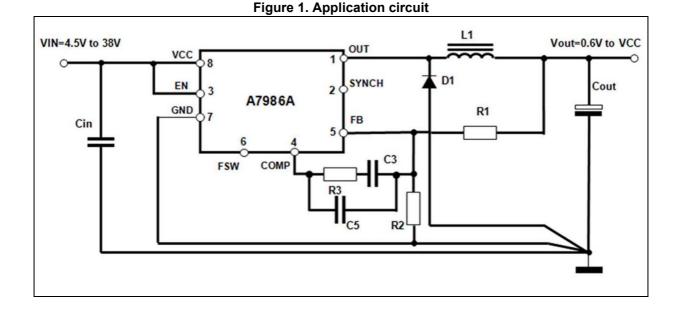

|   | 6.7          | Application circuit                 |  |  |

| 7 | Appli        | cation ideas                        |  |  |

|   | 7.1          | Positive buck-boost                 |  |  |

|   | 7.2          | Inverting buck-boost                |  |  |

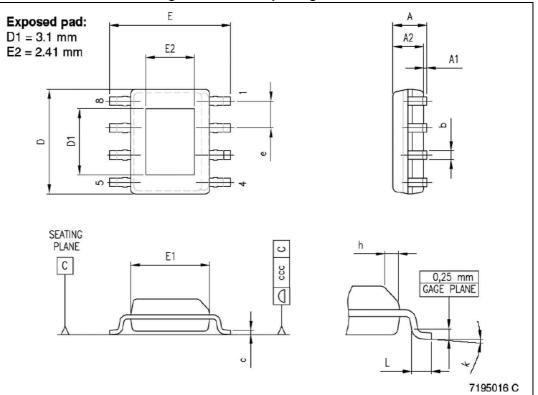

| 8  | Package information              |

|----|----------------------------------|

|    | 8.1 HSOP8 package information 38 |

| 9  | Ordering information             |

| 10 | Revision history                 |

## 1 Pin settings

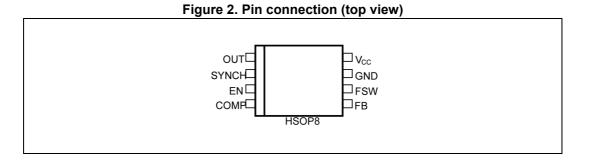

### **1.1 Pin connection**

## 1.2 Pin description

| No.     | Туре                                                                                                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | OUT                                                                                                                                                                                                                           | Regulator output.                                                                                                                                                                                                                                                                                                                   |

| 2 SYNCF |                                                                                                                                                                                                                               | Master/slave synchronization. When it is left floating, a signal with<br>a phase shift of half a period in respect to the power turn-on is present at<br>the pin. When connected to an external signal at a frequency higher than<br>the internal one, the device is synchronized by the external signal, with<br>zero phase shift. |

|         |                                                                                                                                                                                                                               | Connecting together the SYNCH pins of two devices, the one with the higher frequency works as master and the other as slave; so the two powers turn-ons have a phase shift of half a period.                                                                                                                                        |

| 3       | EN                                                                                                                                                                                                                            | A logical signal (active high) enables the device. With EN higher than 1.2 V the device is ON and with EN lower than 0.3 V the device is OFF.                                                                                                                                                                                       |

| 4       | COMP                                                                                                                                                                                                                          | Error amplifier output to be used for loop frequency compensation.                                                                                                                                                                                                                                                                  |

| 5       | 5 FB Feedback input. Connecting the output voltage directly to this pin the output voltage is regulated at 0.6 V. To have higher regulated voltage external resistor divider is required from V <sub>OUT</sub> to the FB pin. |                                                                                                                                                                                                                                                                                                                                     |

| 6       | F <sub>SW</sub>                                                                                                                                                                                                               | The switching frequency can be increased connecting an external resistor from the FSW pin and ground. If this pin is left floating the device works at its free-running frequency of 250 KHz.                                                                                                                                       |

| 7       | GND                                                                                                                                                                                                                           | Ground.                                                                                                                                                                                                                                                                                                                             |

| 8       | V <sub>CC</sub>                                                                                                                                                                                                               | Unregulated DC input voltage.                                                                                                                                                                                                                                                                                                       |

#### Table 1. Pin description

# 2 Maximum ratings

| Symbol Parameter              |                                                  |  | Value            | Unit |

|-------------------------------|--------------------------------------------------|--|------------------|------|

| V <sub>CC</sub>               | Input voltage                                    |  | 45               |      |

| OUT                           | Output DC voltage                                |  | -0.3 to $V_{CC}$ |      |

| F <sub>SW</sub> , COMP, SYNCH | Analog pin                                       |  | -0.3 to 4        | V    |

| EN                            | Enable pin                                       |  | -0.3 to $V_{CC}$ |      |

| FB                            | Feedback voltage                                 |  | -0.3 to 1.5      |      |

| P <sub>TOT</sub>              | Power dissipation at $T_A < 60 \text{ °C}$ HSOP8 |  | 2                | W    |

| Т <sub>Ј</sub>                | Junction temperature range                       |  | -40 to 150       | °C   |

| T <sub>stg</sub>              | Storage temperature range                        |  | -55 to 150       | °C   |

#### Table 2. Absolute maximum ratings

## 3 Thermal data

#### Table 3. Thermal data

| Symbol              | Parameter                                                  |       |    | Unit |

|---------------------|------------------------------------------------------------|-------|----|------|

| R <sub>th(JA)</sub> | Maximum thermal resistance junction ambient <sup>(1)</sup> | HSOP8 | 40 | °C/W |

1. Package mounted on demonstration board.

# 4 Electrical characteristics

$T_J$  = - 40 °C to 125 °C,  $V_{CC}$  = 12 V, unless otherwise specified.

| 0h.d                | Parameter                         | <b>T</b> . ( ) , ( ) ( ) ( )                     | Values     |       |            |      |  |

|---------------------|-----------------------------------|--------------------------------------------------|------------|-------|------------|------|--|

| Symbol              |                                   | Test conditions                                  | Min.       | Тур.  | Max.       | Unit |  |

| V <sub>CC</sub>     | Operating input voltage range     | -                                                | 4.5        | -     | 38         |      |  |

| V <sub>CCON</sub>   | Turn-on V <sub>CC</sub> threshold | -                                                | -          | -     | 4.5        | V    |  |

| V <sub>CCHYS</sub>  | V <sub>CC</sub> UVLO hysteresis   | -                                                | 0.1        | -     | 0.4        |      |  |

| R <sub>DS(on)</sub> | MOSFET on-resistance              | -                                                | -          | 200   | 400        | mΩ   |  |

| I <sub>LIM</sub>    | Maximum limiting current          | T <sub>J</sub> = 25 °C<br>-                      | 3.7<br>3.5 | -     | 5.2<br>5.2 | A    |  |

| Oscillator          |                                   | -                                                | 5.5        | _     | 0.2        |      |  |

| F <sub>SW</sub>     | Switching frequency               | -                                                | 210        | 250   | 275        | KHz  |  |

| V <sub>FSW</sub>    | FSW pin voltage                   | -                                                | -          | 1.254 | -          | V    |  |

| D                   | Duty cycle                        | -                                                | 0          | -     | 100        | %    |  |

| F <sub>ADJ</sub>    | Adjustable switching frequency    | R <sub>FSW</sub> = 33 kΩ                         | -          | 1000  | -          | KHz  |  |

| Dynamic cha         | aracteristics                     |                                                  | ·          |       |            |      |  |

| V <sub>FB</sub>     | Feedback voltage                  | 4.5 V< V <sub>CC</sub> < 38 V                    | 0.588      | 0.6   | 0.612      | V    |  |

| DC characte         | ristics                           |                                                  |            |       |            |      |  |

| Ι <sub>Q</sub>      | Quiescent current                 | Duty cycle = 0, V <sub>FB</sub> = 0.8 V          | -          | -     | 2.4        | mA   |  |

| I <sub>QST-BY</sub> | Total standby quiescent current   | -                                                | -          | 20    | 30         | μA   |  |

| Enable              | •                                 |                                                  |            |       |            |      |  |

| N/                  |                                   | Device OFF level                                 | -          | -     | 0.3        | V    |  |

| $V_{\sf EN}$        | EN threshold voltage              | Device ON level                                  | 1.2        | -     | -          | V    |  |

| I <sub>EN</sub>     | EN current                        | EN = V <sub>CC</sub>                             |            | 7.5   | 10         | μA   |  |

| Soft-start          | •                                 |                                                  |            |       |            |      |  |

| т                   | Coff start duration               | FSW pin floating                                 | 7.3        | 8.2   | 9.8        |      |  |

| T <sub>SS</sub>     | Soft-start duration               | $F_{SW}$ = 1 MHz, $R_{FSW}$ = 33 k $\Omega$      | -          | 2     | -          | – ms |  |

| Error amplif        | ier                               |                                                  |            |       |            |      |  |

| V <sub>CH</sub>     | High level output voltage         | V <sub>FB</sub> < 0.6 V                          | 3          | -     | -          |      |  |

| V <sub>CL</sub>     | Low level output voltage          | V <sub>FB</sub> > 0.6 V                          | -          | -     | 0.1        | V    |  |

| IO SOURCE           | Source COMP pin                   | V <sub>FB</sub> = 0.5 V, V <sub>COMP</sub> = 1 V | -          | 19    | -          | mA   |  |

#### Table 4. Electrical characteristics

| Symbol                | Parameter               | Test conditions                                        | Values |      |      | Unit |  |

|-----------------------|-------------------------|--------------------------------------------------------|--------|------|------|------|--|

| Symbol                | Farameter               | Test conditions                                        | Min.   | Тур. | Max. | Onit |  |

| I <sub>O SINK</sub>   | Sink COMP pin           | V <sub>FB</sub> = 0.7 V, V <sub>COMP</sub> = 0.75 V    | -      | 30   | -    | mA   |  |

| G <sub>V</sub>        | Open loop voltage gain  | (1)                                                    | -      | 100  | -    | dB   |  |

| Synchroniza           | tion function           |                                                        |        |      |      |      |  |

| V <sub>S_IN,HI</sub>  | High input voltage      | -                                                      | 2      | -    | 3.3  | v    |  |

| V <sub>S_IN,LO</sub>  | Low input voltage       | -                                                      | -      | -    | 1    | v    |  |

| t                     | Input pulse width       | V <sub>S_IN,HI</sub> = 3 V, V <sub>S_IN,LO</sub> = 0 V | 100    | -    | -    | ns   |  |

| t <sub>S_IN_PW</sub>  |                         | $V_{S_{IN,HI}}$ = 2 V, $V_{S_{IN,LO}}$ = 1 V           | 300    | -    | -    |      |  |

| I <sub>SYNCH,LO</sub> | Slave sink current      | V <sub>SYNCH</sub> = 2.9 V                             | -      | 0.7  | 1    | mA   |  |

| V <sub>S_OUT,HI</sub> | Master output amplitude | I <sub>SOURCE</sub> = 4.5 mA                           | 2      | -    | -    | V    |  |

| t <sub>S_OUT_PW</sub> | Output pulse width      | SYNCH floating                                         | -      | 110  | -    | ns   |  |

| Protection            |                         |                                                        |        |      |      |      |  |

| т                     | Thermal shutdown        | -                                                      | -      | 150  | -    | °C   |  |

| T <sub>SHDN</sub>     | Hysteresis              | -                                                      | -      | 30   | -    |      |  |

1. Guaranteed by design.

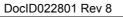

## 5 Functional description

The A7986A device is based on a "voltage mode", constant frequency control. The output voltage  $V_{OUT}$  is sensed by the feedback pin (FB) compared to an internal reference (0.6 V) providing an error signal that, compared to a fixed frequency sawtooth, controls the on and off time of the power switch.

The main internal blocks are shown in the block diagram in *Figure 3*. They are:

- A fully integrated oscillator that provides sawtooth to modulate the duty cycle and the synchronization signal. Its switching frequency can be adjusted by an external resistor. The voltage and frequency feed-forward are implemented

- The soft-start circuitry to limit inrush current during the startup phase

- The voltage mode error amplifier

- The pulse width modulator and the relative logic circuitry necessary to drive the internal power switch

- The high-side driver for embedded P-channel power MOSFET switch

- The peak current limit sensing block, to handle overload and short-circuit conditions

- A voltage regulator and internal reference. It supplies internal circuitry and provides a fixed internal reference

- A voltage monitor circuitry (UVLO) that checks the input and internal voltages

- A thermal shutdown block, to prevent thermal runaway.

#### Figure 3. Block diagram

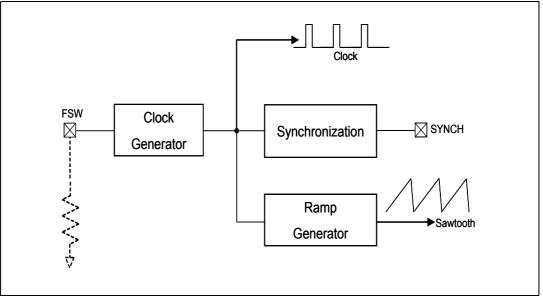

## 5.1 Oscillator and synchronization

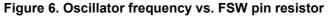

*Figure 4* shows the block diagram of the oscillator circuit. The internal oscillator provides a constant frequency clock. Its frequency depends on the resistor externally connected to the FSW pin. If the FSW pin is left floating, the frequency is 250 kHz; it can be increased as shown in *Figure 6* by an external resistor connected to ground.

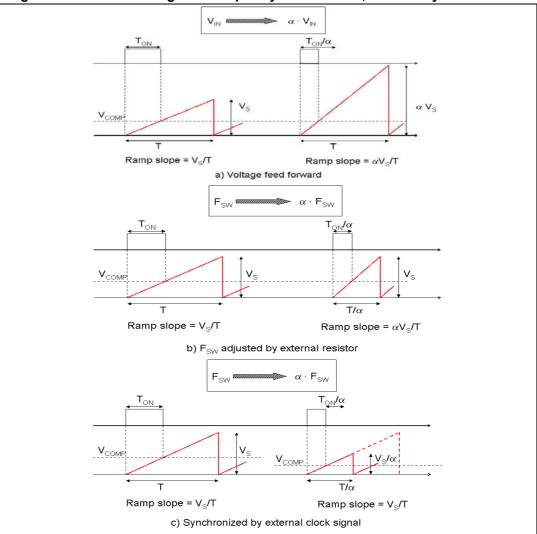

To improve the line transient performance, keeping the PWM gain constant versus the input voltage, the voltage feed-forward is implemented by changing the slope of the sawtooth according to the input voltage change (see *Figure 5.a*).

The slope of the sawtooth also changes if the oscillator frequency is increased by the external resistor. In this way a frequency feed-forward is implemented (*Figure 5.b*) in order to keep the PWM gain constant versus the switching frequency (see *Section 6.4 on page 18* for PWM gain expression).

The synchronization signal is generated on the SYNCH pin. This signal has a phase shift of 180 ° with respect to the clock. This delay is useful when two devices are synchronized connecting the SYNCH pins together. When the SYNCH pins are connected, the device with higher oscillator frequency works as master, so the slave device switches at the frequency of the master but with a delay of half a period. This minimizes the RMS current flowing through the input capacitor (see the L5988D datasheet).

Figure 4. Oscillator circuit block diagram

The device can be synchronized to work at higher frequency feeding an external clock signal. The synchronization changes the sawtooth amplitude, changing the PWM gain (*Figure 5.c*). This change must be taken into account when the loop stability is studied. To minimize the change of the PWM gain, the free-running frequency should be set (with a resistor on the FSW pin) only slightly lower than the external clock frequency. This pre-adjusting of the frequency changes the sawtooth slope in order to render the truncation of sawtooth negligible, due to the external synchronization.

Figure 5. Sawtooth: voltage and frequency feed-forward; external synchronization

DocID022801 Rev 8

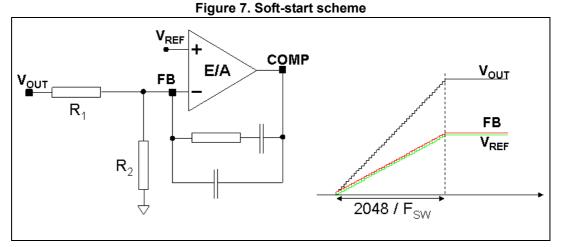

### 5.2 Soft-start

Soft-start is essential to assure a correct and safe startup of the step-down converter. It avoids inrush current surge and makes the output voltage increase monothonically.

Soft-start is performed by a staircase ramp on the non inverting input ( $V_{REF}$ ) of the error amplifier. So the output voltage slew rate is:

#### **Equation 1**

$$SR_{OUT} = SR_{VREF} \cdot \left(1 + \frac{R1}{R2}\right)$$

where  $SR_{VREF}$  is the slew rate of the non inverting input, while *R*1 and *R*2 is the resistor divider to regulate the output voltage (see *Figure* 7). The soft-start staircase consists of 64 steps of 9.5 mV each, from 0 V to 0.6 V. The time base of one step is of 32 clock cycles. So the soft-start time and then the output voltage slew rate depend on the switching frequency.

Soft-start time results:

#### **Equation 2**

$$SS_{TIME} = \frac{32 \cdot 64}{Fsw}$$

For example, with a switching frequency of 250 kHz, the SS<sub>TIME</sub> is 8 ms.

### 5.3 Error amplifier and compensation

The error amplifier (EA) provides the error signal to be compared with the sawtooth to perform the pulse width modulation. Its non inverting input is internally connected to a 0.6 V voltage reference, while its inverting input (FB) and output (COMP) are externally available for feedback and frequency compensation. In this device the error amplifier is a voltage mode operational amplifier so with high DC gain and low output impedance.

The uncompensated error amplifier characteristics are the following:

| Parameter                   | Value       |  |  |

|-----------------------------|-------------|--|--|

| Low frequency gain          | 100 dB      |  |  |

| GBWP                        | 4.5 MHz     |  |  |

| Slew rate                   | 7 V/μs      |  |  |

| Output voltage swing        | 0 to 3.3 V  |  |  |

| Maximum source/sink current | 17 mA/25 mA |  |  |

Table 5.Uncompensated error amplifier characteristics

In continuous conduction mode (CCM), the transfer function of the power section has two poles due to the LC filter and one zero due to the ESR of the output capacitor. Different kinds of compensation networks can be used depending on the ESR value of the output capacitor. If the zero introduced by the output capacitor helps to compensate the double pole of the LC filter, a Type II compensation network can be used. Otherwise, a Type III compensation network must be used (see *Section 6.4 on page 18* for details of the compensation network selection).

Anyway, the methodology to compensate the loop is to introduce zeros to obtain a safe phase margin.

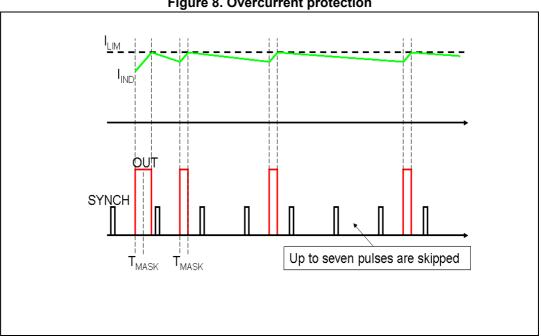

## 5.4 Overcurrent protection

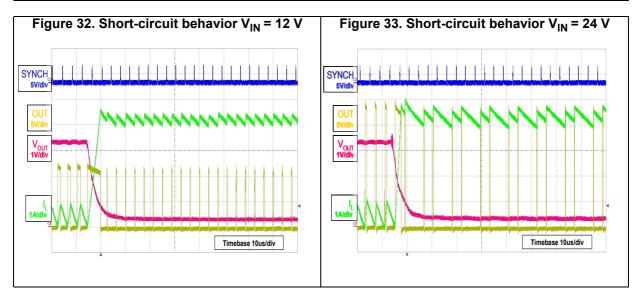

The A7986A implements the overcurrent protection sensing current flowing through the power MOSFET. Due to the noise created by the switching activity of the power MOSFET, the current sensing is disabled during the initial phase of the conduction time. This avoids an erroneous detection of a fault condition. This interval is generally known as "masking time" or "blanking time". The masking time is about 200 ns.

If the overcurrent limit is reached, the power MOSFET is turned off implementing the pulseby-pulse overcurrent protection. Under the overcurrent condition, the device can skip turnon pulses in order to keep the output current constant and equal to the current limit. If, at the end of the "masking time", the current is higher than the overcurrent threshold, the power MOSFET is turned off and one pulse is skipped. If, at the following switching on, when the "masking time" ends, the current is still higher than the overcurrent threshold, the device skips two pulses. This mechanism is repeated and the device can skip up to seven pulses. While, if at the end of the "masking time" the current is lower than the overcurrent threshold, the number of skipped cycles is decreased by one unit (see *Figure 8*).

So the overcurrent/short-circuit protection acts by switching off the power MOSFET and reducing the switching frequency down to one eighth of the default switching frequency, in order to keep constant the output current around the current limit.

DocID022801 Rev 8

This kind of overcurrent protection is effective if the output current is limited. To prevent the current from diverging, the current ripple in the inductor during the on-time must not be higher than the current ripple during the off-time. That is:

#### **Equation 3**

$$\frac{V_{\text{IN}} - V_{\text{OUT}} - R_{\text{DSON}} \cdot I_{\text{OUT}} - \text{DCR} \cdot I_{\text{OUT}}}{L \cdot F_{\text{SW}}} \cdot D = \frac{V_{\text{OUT}} + V_{\text{F}} + R_{\text{DSON}} \cdot I_{\text{OUT}} + \text{DCR} \cdot I_{\text{OUT}}}{L \cdot F_{\text{SW}}} \cdot (1 - D)$$

If the output voltage is shorted,  $V_{OUT} \cong 0$ ,  $I_{OUT} = I_{LIM}$ ,  $D/F_{SW} = T_{ON\_MIN}$ ,  $(1-D)/F_{SW} \cong 1/F_{SW}$ . So, from the above equation, the maximum switching frequency that guarantees to limit the current results:

#### **Equation 4**

$$F_{SW}^{\star} = \frac{(V_{F} + DCR \cdot I_{LIM})}{(V_{IN} - (R_{DSON} + DCR) \cdot I_{LIM})} \cdot \frac{1}{T_{ON MIN}}$$

With  $R_{DS(on)}$  = 300 m $\Omega$ , DRC = 0.08  $\Omega$ , the worst condition is with  $V_{IN}$  = 38 V,  $I_{LIM}$  = 3.7 A; the maximum frequency to keep the output current limited during the short-circuit results 88 kHz.

Based on the pulse-by-pulse mechanism, that reduces the switching frequency down to one eighth, the maximum  $F_{SW}$ , adjusted by the FSW pin, which assures that a full effective output current limitation is 88 kHz \* 8 = 706 kHz.

If, with  $V_{IN}$ = 38 V, the switching frequency is set higher than 706 kHz, during short-circuit condition the system finds a different equilibrium with higher current. For example, with  $F_{SW}$  = 800 kHz and the output shorted to ground, the output current is limited around:

#### **Equation 5**

$$I_{OUT} = \frac{V_{IN} \cdot F_{SW}^* - V_F / T_{ON\_MIN}}{(DRC / T_{ON\_MIN}) + (R_{DSON} + DCR) \cdot F_{SW}^*} = 4.2A$$

where  $F_{SW}^*$  is 800 kHz divided by eight.

Figure 8. Overcurrent protection

#### 5.5 **Enable function**

The enable feature allows the device to be put into standby mode. With the EN pin is lower than 0.3 V the device is disabled and the power consumption is reduced to less than 30  $\mu$ A. With the EN pin is lower than 1.2 V, the device is enabled. If the EN pin is left floating, an internal pull-down ensures that the voltage at the pin reaches the inhibit threshold and the device is disabled. The pin is also  $V_{CC}$  compatible.

#### 5.6 Hysteretic thermal shutdown

The thermal shutdown block generates a signal that turns off the power stage if the junction temperature goes above 150 °C. Once the junction temperature goes back to about 120 °C, the device restarts in normal operation. The sensing element is very close to the PDMOS area, so ensuring an accurate and fast temperature detection.

## 6 Application information

### 6.1 Input capacitor selection

The capacitor connected to the input must be capable of supporting the maximum input operating voltage and the maximum RMS input current required by the device. The input capacitor is subject to a pulsed current, the RMS value of which is dissipated over its ESR, affecting the overall system efficiency.

So the input capacitor must have an RMS current rating higher than the maximum RMS input current and an ESR value compliant with the expected efficiency.

The maximum RMS input current flowing through the capacitor can be calculated as:

#### **Equation 6**

$$I_{RMS} = I_{O} \cdot \sqrt{D - \frac{2 \cdot D^2}{\eta} + \frac{D^2}{\eta^2}}$$

where  $I_o$  is the maximum DC output current, *D* is the duty cycle, and  $\eta$  is the efficiency. Considering  $\eta = 1$ , this function has a maximum at D = 0.5 and is equal to Io/2.

In a specific application the range of possible duty cycles must be considered in order to find out the maximum RMS input current. The maximum and minimum duty cycles can be calculated as:

#### **Equation 7**

$$\mathsf{D}_{\mathsf{MAX}} = \frac{\mathsf{V}_{\mathsf{OUT}} + \mathsf{V}_{\mathsf{F}}}{\mathsf{V}_{\mathsf{INMIN}} - \mathsf{V}_{\mathsf{SW}}}$$

and:

#### **Equation 8**

$$\mathsf{D}_{\mathsf{MIN}} = \frac{\mathsf{V}_{\mathsf{OUT}} + \mathsf{V}_{\mathsf{F}}}{\mathsf{V}_{\mathsf{INMAX}} - \mathsf{V}_{\mathsf{SW}}}$$

where  $V_F$  is the forward voltage on the freewheeling diode and  $V_{SW}$  is voltage drop across the internal PDMOS.

The peak-to-peak voltage across the input capacitor can be calculated as:

#### **Equation 9**

$$V_{PP} = \frac{I_{O}}{C_{IN} \cdot F_{SW}} \cdot \left[ \left( 1 - \frac{D}{\eta} \right) \cdot D + \frac{D}{\eta} \cdot (1 - D) \right] + ESR \cdot I_{O}$$

where ESR is the equivalent series resistance of the capacitor.

Given the physical dimension, ceramic capacitors can well meet the requirements of the input filter sustaining a higher input RMS current than electrolytic/tantalum types. In this case the equation of  $C_{IN}$  as a function of the target  $V_{PP}$  can be written as follows:

#### **Equation 10**

$$C_{IN} = \frac{I_{O}}{V_{PP} \cdot F_{SW}} \cdot \left[ \left( 1 - \frac{D}{\eta} \right) \cdot D + \frac{D}{\eta} \cdot (1 - D) \right]$$

neglecting the small ESR of ceramic capacitors.

Considering  $\eta$  = 1, this function has its maximum in D = 0.5, therefore, given the maximum peak-to-peak input voltage (V<sub>PP MAX</sub>), the minimum input capacitor (C<sub>IN MIN</sub>) value is:

#### **Equation 11**

$$C_{IN\_MIN} = \frac{I_{O}}{2 \cdot V_{PP\_MAX} \cdot F_{SW}}$$

Typically,  $C_{\text{IN}}$  is dimensioned to keep the maximum peak-to-peak voltage in the order of 1% of  $V_{\text{INMAX}}$

In Table 6 some multi-layer ceramic capacitors suitable for this device are reported:

| Manufacture | Series          | Cap value (μF) | Rated voltage (V) |

|-------------|-----------------|----------------|-------------------|

| Taiyo Yuden | UMK325BJ106MM-T | 10             | 50                |

|             | GMK325BJ106MN-T | 10             | 35                |

| Murata      | GRM32ER71H475K  | 4.7            | 50                |

Table 6. Input MLCC capacitors

A ceramic bypass capacitor, as close to the VCC and GND pins as possible, so that additional parasitic ESR and ESL are minimized, is recommended in order to prevent instability on the output voltage due to noise. The value of the bypass capacitor can go from 100 nF to 1  $\mu$ F.

### 6.2 Inductor selection

The inductance value fixes the current ripple flowing through the output capacitor. So the minimum inductance value, in order to have the expected current ripple, must be selected. The rule to fix the current ripple value is to have a ripple at 20% - 40% of the output current.

In continuous current mode (CCM), the inductance value can be calculated by the following equation:

#### Equation 12

$$\Delta I_{L} = \frac{V_{IN} - V_{OUT}}{L} \cdot T_{ON} = \frac{V_{OUT} + V_{F}}{L} \cdot T_{OFF}$$

where  $T_{ON}$  is the conduction time of the internal high-side switch and  $T_{OFF}$  is the conduction time of the external diode [in CCM,  $F_{SW} = 1/(T_{ON} + T_{OFF})$ ]. The maximum current ripple, at fixed V<sub>OUT</sub>, is obtained at maximum  $T_{OFF}$ , that is at minimum duty cycle (see Section 6.1 to calculate minimum duty). So, fixing  $\Delta I_L = 20\%$  to 30% of the maximum output current, the minimum inductance value can be calculated as:

#### **Equation 13**

$$L_{MIN} = \frac{V_{OUT} + V_F}{\Delta I_{MAX}} \cdot \frac{1 - D_{MIN}}{F_{SW}}$$

where  $F_{SW}$  is the switching frequency,  $1/(T_{ON} + T_{OFF})$ .

For example, for V<sub>OUT</sub> = 5 V, V<sub>IN</sub> = 24 V, I<sub>O</sub> = 3 A and F<sub>SW</sub> = 250 kHz, the minimum inductance value to have  $\Delta I_L$  = 30% of I<sub>O</sub> is about 18  $\mu$ H.

The peak current through the inductor is given by:

#### Equation 14

$$I_{L, PK} = I_{O} + \frac{\Delta I_{L}}{2}$$

Therefore, if the inductor value decreases, then the peak current (that must be lower than the minimum current limit of the device) increases. According to the maximum DC output current for this product family (3 A), the higher the inductor value, the higher the average output current that can be delivered, without triggering the overcurrent protection.

In *Table 7* some inductor part numbers are listed.

| Manufacturer | Series       | Inductor value ( $\mu$ H) | Saturation current (A) |  |  |

|--------------|--------------|---------------------------|------------------------|--|--|

| Coilcraft    | MSS1038      | 3.8 to 10                 | 3.9 to 6.5             |  |  |

| Colicran     | MSS1048      | 12 to 22                  | 3.84 to 5.34           |  |  |

| Wurth        | PD Type L    | 8.2 to 15                 | 3.75 to 6.25           |  |  |

| warth        | PD Type M    | 2.2 to 4.7                | 4 to 6                 |  |  |

| SUMIDA       | CDRH6D226/HP | 1.5 to 3.3                | 3.6 to 5.2             |  |  |

| SUMIDA       | CDR10D48MN   | 6.6 to 12                 | 4.1 to 5.7             |  |  |

Table 7. Inductors

## 6.3 Output capacitor selection

The current in the capacitor has a triangular waveform which generates a voltage ripple across it. This ripple is due to the capacitive component (charge or discharge of the output capacitor) and the resistive component (due to the voltage drop across its ESR). So the output capacitor must be selected in order to have a voltage ripple compliant with the application requirements.

The amount of the voltage ripple can be calculated starting from the current ripple obtained by the inductor selection.

#### **Equation 15**

$$\Delta V_{OUT} = ESR \cdot \Delta I_{MAX} + \frac{\Delta I_{MAX}}{8 \cdot C_{OUT} \cdot f_{SW}}$$

Usually the resistive component of the ripple is much higher than the capacitive one, if the output capacitor adopted is not a multi-layer ceramic capacitor (MLCC) with very low ESR value.

DocID022801 Rev 8

The output capacitor is important also for loop stability: it fixes the double LC filter pole and the zero due to its ESR. *Section 6.4* illustrates how to consider its effect in the system stability.

For example, with  $V_{OUT} = 5 \text{ V}$ ,  $V_{IN} = 24 \text{ V}$ ,  $\Delta I_L = 0.9 \text{ A}$  (resulting by the inductor value), in order to have a  $\Delta V_{OUT} = 0.01 \cdot V_{OUT}$ , if the multi-layer ceramic capacitor is adopted, 10 µF are needed and the ESR effect on the output voltage ripple can be neglected. In the case of not negligible ESR (electrolytic or tantalum capacitors), the capacitor is chosen taking into account its ESR value. So, in the case of 330 µF with ESR = 730 m $\Omega$ , the resistive component of the drop dominates and the voltage ripple is 28 mV.

The output capacitor is also important to sustain the output voltage when a load transient with high slew rate is required by the load. When the load transient slew rate exceeds the system bandwidth, the output capacitor provides the current to the load. So, if the high slew rate load transient is required by the application, the output capacitor and system bandwidth must be chosen in order to sustain the load transient.

| Manufacturer | Series  | Cap value (μF) | Rated voltage (V) | ESR (m $\Omega$ ) |  |  |

|--------------|---------|----------------|-------------------|-------------------|--|--|

| MURATA       | GRM32   | 22 to 100      | 6.3 to 25         | < 5               |  |  |

| MOICAIA      | GRM31   | 10 to 47       | 6.3 to 25         | < 5               |  |  |

| PANASONIC    | ECJ     | 10 to 22       | 6.3               | < 5               |  |  |

| FANASONIC    | EEFCD   | 10 to 68       | 6.3               | 15 to 55          |  |  |

| SANYO        | TPA/B/C | 100 to 470     | 4 to 16           | 40 to 80          |  |  |

| TDK          | C3225   | 22 to 100      | 6.3               | < 5               |  |  |

In Table 8 some capacitor series are listed.

Table 8. Output capacitors

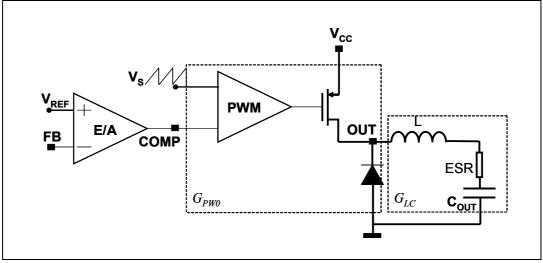

### 6.4 Compensation network

The compensation network must assure stability and good dynamic performance. The loop of the A7986A is based on the voltage mode control. The error amplifier is a voltage operational amplifier with high bandwidth. So by selecting the compensation network, the EA is considered as ideal, that is, its bandwidth is much larger than the system one.

The transfer function of the PWM modulator, from the error amplifier output (COMP pin) to the OUT pin (see *Figure 10*) results:

#### **Equation 16**

$$G_{PW0} = \frac{V_{IN}}{V_s}$$

where  $V_S$  is the sawtooth amplitude. As seen in Section 5.1 on page 9, the voltage feed-forward generates a sawtooth amplitude directly proportional to the input voltage, that is:

**Equation 17**

$$V_{S} = K \cdot V_{IN}$$

In this way the PWM modulator gain results constant and equal to:

#### **Equation 18**

$$G_{PW0} = \frac{V_{IN}}{V_s} = \frac{1}{K} = 18$$

The synchronization of the device with an external clock provided trough the SYNCH pin can modify the PWM modulator gain (see *Section 5.1 on page 9* to understand how this gain changes and how to keep it constant in spite of the external synchronization).

Figure 9. The error amplifier, the PWM modulation and the LC output filter

The transfer function on the LC filter is given by:

#### **Equation 19**

$$G_{LC}(s) = \frac{1 + \frac{s}{2\pi \cdot f_{zESR}}}{1 + \frac{s}{2\pi \cdot Q \cdot f_{LC}} + \left(\frac{s}{2\pi \cdot f_{LC}}\right)^2}$$

where:

**Equation 20**

$$f_{LC} = \frac{1}{2\pi \cdot \sqrt{L \cdot C_{OUT}} \cdot \sqrt{1 + \frac{ESR}{R_{OUT}}}}, \qquad f_{zESR} = \frac{1}{2\pi \cdot ESR \cdot C_{OUT}}$$

#### **Equation 21**

$$Q = \frac{\sqrt{R_{OUT} \cdot L \cdot C_{OUT} \cdot (R_{OUT} + ESR)}}{L + C_{OUT} \cdot R_{OUT} \cdot ESR}, \qquad R_{OUT} = \frac{V_{OUT}}{I_{OUT}}$$

As seen in Section 5.3 on page 12, two different kinds of network can compensate the loop. In the two following paragraphs, the guidelines to select the Type II and Type III compensation network are illustrated.

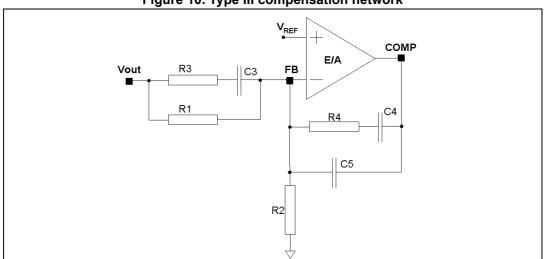

#### 6.4.1 Type III compensation network

The methodology to stabilize the loop consists of placing two zeros to compensate the effect of the LC double pole, therefore increasing phase margin; then to place one pole in the origin to minimize the DC error on regulated output voltage; finally, to place other poles far from the zero dB frequency.

If the equivalent series resistance (ESR) of the output capacitor introduces a zero with a frequency higher than the desired bandwidth (that is:  $2\pi * ESR * C_{OUT} < 1 / BW$ ), the Type III compensation network is needed. Multi-layer ceramic capacitors (MLCC) have very low ESR (< 1 m $\Omega$ ), with very high frequency zero, so a Type III network is adopted to compensate the loop.

In *Figure 10*, the Type III compensation network is shown. This network introduces two zeros ( $f_{Z1}$ ,  $f_{Z2}$ ) and three poles ( $f_{P0}$ ,  $f_{P1}$ ,  $f_{P2}$ ). They are expressed as:

#### **Equation 22**

$$f_{Z1} = \frac{1}{2\pi \cdot C_3 \cdot (R_1 + R_3)}, \qquad f_{Z2} = \frac{1}{2\pi \cdot R_4 \cdot C_4}$$

**Equation 23**

$$f_{P0} = 0, \qquad f_{P1} = \frac{1}{2\pi \cdot R_3 \cdot C_3}, \qquad f_{P2} = \frac{1}{2\pi \cdot R_4 \cdot \frac{C_4 \cdot C_5}{C_4 + C_5}}$$

Figure 10. Type III compensation network

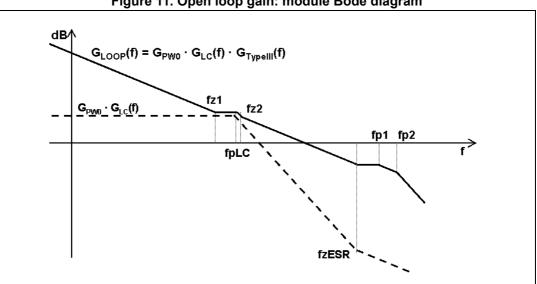

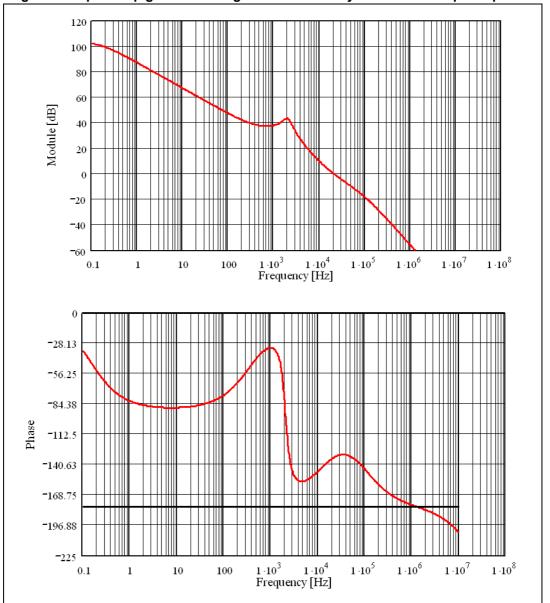

In Figure 11, the Bode diagram of the PWM and LC filter transfer function (G\_{PW0}  $\cdot$  G<sub>LC</sub>(f)) and the open loop gain (G<sub>LOOP</sub>(f) = G<sub>PW0</sub>  $\cdot$  G<sub>LC</sub>(f)  $\cdot$  G<sub>TYPEIII</sub>(f)) are drawn.

Figure 11. Open loop gain: module Bode diagram

The guidelines for positioning the poles and the zeroes and for calculating the component values can be summarized as follows:

- Choose a value for  $R_1$ , usually between 1 k $\Omega$  and 5 k $\Omega$ . 1.

- 2. Choose a gain  $(R_4/R_1)$  in order to have the required bandwidth (BW), that means:

#### **Equation 24**

$$\mathsf{R}_4 = \frac{\mathsf{BW}}{\mathsf{f}_{\mathsf{LC}}} \cdot \mathsf{K} \cdot \mathsf{R}_1$$

where K is the feed-forward constant and 1/K is equal to 18.

3. Calculate  $C_4$  by placing the zero at 50% of the output filter double pole frequency ( $f_{LC}$ ):

#### **Equation 25**

$$C_4 = \frac{1}{\pi \cdot R_4 \cdot f_{LC}}$$

4. Calculate C<sub>5</sub> by placing the second pole at four times the system bandwidth (BW):

#### **Equation 26**

$$C_5 = \frac{C_4}{2\pi \cdot R_4 \cdot C_4 \cdot 4 \cdot BW - 1}$$

5. Set also the first pole at four times the system bandwidth and also the second zero at the output filter double pole:

#### **Equation 27**

$$R_3 = \frac{R_1}{\frac{4 \cdot BW}{f_{LC}} - 1}, \qquad C_3 = \frac{1}{2\pi \cdot R_3 \cdot 4 \cdot BW}$$

The suggested maximum system bandwidth is equal to the switching frequency divided by 3.5 ( $F_{SW}$ /3.5), anyway lower than 100 kHz if the  $F_{SW}$  is set higher than 500 kHz.

For example, with V<sub>OUT</sub> = 5 V, V<sub>IN</sub> = 24 V, I<sub>O</sub> = 3 A, L = 18  $\mu$ H, C<sub>OUT</sub> = 22  $\mu$ F, and ESR<1 m $\Omega$ , the Type III compensation network is:

#### **Equation 28**

$\mathsf{R}_1 = 4.99 \mathsf{k} \Omega, \quad \mathsf{R}_2 = 680 \Omega, \quad \mathsf{R}_3 = 200 \Omega, \quad \mathsf{R}_4 = 2 \mathsf{k} \Omega, \quad \mathsf{C}_3 = 3.3 \mathsf{nF}, \quad \mathsf{C}_4 = 22 \mathsf{nF}, \quad \mathsf{C}_5 = 220 \mathsf{pF}$

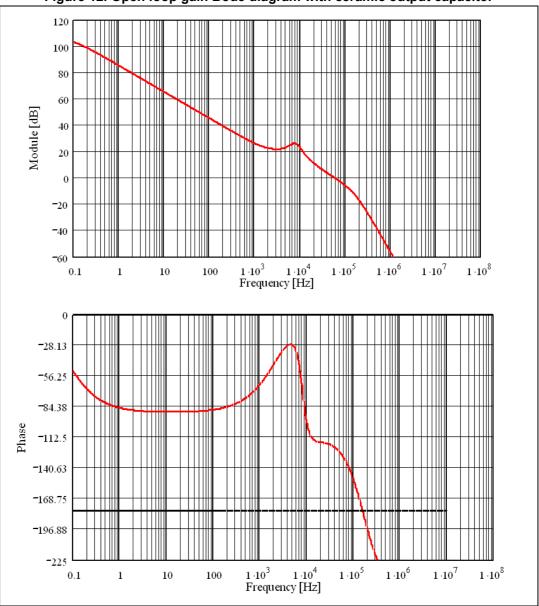

In *Figure 12*, the module and phase of the open loop gain is shown. The bandwidth is about 32 kHz and the phase margin is  $51^{\circ}$ .

Figure 12. Open loop gain Bode diagram with ceramic output capacitor

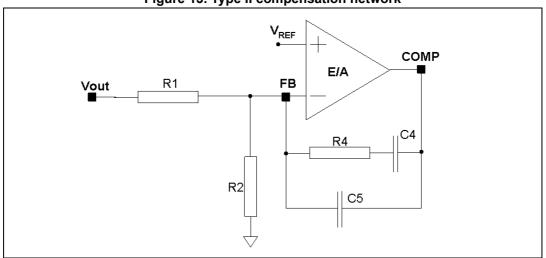

### 6.4.2 Type II compensation network

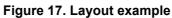

If the equivalent series resistance (ESR) of the output capacitor introduces a zero with a frequency lower than the desired bandwidth (that is:  $2\pi * \text{ESR} * C_{\text{OUT}} > 1 / \text{BW}$ ), this zero helps stabilize the loop. Electrolytic capacitors show not negligible ESR (> 30 m $\Omega$ ), so with this kind of output capacitor the Type II network combined with the zero of the ESR allows the stabilization of the loop.

Figure 13. Type II compensation network

The singularities of the network are:

#### **Equation 29**

$$f_{Z1} = \frac{1}{2\pi \cdot R_4 \cdot C_4}, \quad f_{P0} = 0, \quad f_{P1} = \frac{1}{2\pi \cdot R_4 \cdot \frac{C_4 \cdot C_5}{C_4 + C_5}}$$

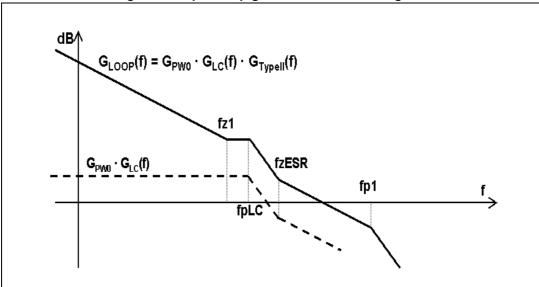

In *Figure 14*, the Bode diagram of the PWM and LC filter transfer function  $(G_{PW0} \cdot G_{LC}(f))$  and the open loop gain  $(G_{LOOP}(f) = G_{PW0} \cdot G_{LC}(f) \cdot G_{TYPEII}(f))$  are drawn.

#### Figure 14. Open loop gain: module Bode diagram

The guidelines for positioning the poles and the zeroes and for calculating the component values can be summarized as follows:

- 1. Choose a value for  $R_1$ , usually between 1 k $\Omega$  and 5 k $\Omega$ , in order to have values of C4 and C5 not comparable with parasitic capacitance of the board.

- 2. Choose a gain  $(R_4/R_1)$  in order to have the required bandwidth (BW), that means:

#### **Equation 30**

$$\mathsf{R_4} = \left(\frac{\mathsf{f}_{\mathsf{ESR}}}{\mathsf{f}_{\mathsf{LC}}}\right)^2 \cdot \frac{\mathsf{BW}}{\mathsf{f}_{\mathsf{ESR}}} \cdot \frac{\mathsf{V}_{\mathsf{S}}}{\mathsf{V}_{\mathsf{IN}}} \cdot \mathsf{R}_{\mathsf{1}}$$

where  $f_{ESR}$  is the ESR zero:

#### **Equation 31**

$$f_{ESR} = \frac{1}{2\pi \cdot ESR \cdot C_{OUT}}$$

and Vs is the sawtooth amplitude. The voltage feed-forward keeps the ratio Vs/Vin constant.

3. Calculate C<sub>4</sub> by placing the zero one decade below the output filter double pole:

#### Equation 32

$$C_4 = \frac{10}{2\pi \cdot R_4 \cdot f_{LC}}$$

4. Then calculate C<sub>3</sub> in order to place the second pole at four times the system bandwidth (BW):

#### **Equation 33**

$$C_5 = \frac{C_4}{2\pi \cdot R_4 \cdot C_4 \cdot 4 \cdot BW - 1}$$

For example with V<sub>OUT</sub> = 5 V, V<sub>IN</sub> = 24 V, I<sub>O</sub> = 3 A, L = 18  $\mu$ H, C<sub>OUT</sub> = 330  $\mu$ F, and ESR = 35 m $\Omega$ , the Type II compensation network is:

$$R_1 = 1.1 k\Omega$$

,  $R_2 = 150 \Omega$ ,  $R_4 = 4.99 k\Omega$ ,  $C_4 = 82 nF$ ,  $C_5 = 68 pF$

In *Figure 15*, the module and phase of the open loop gain is shown. The bandwidth is about 21 kHz and the phase margin is 45°.

Figure 15. Open loop gain Bode diagram with electrolytic/tantalum output capacitor

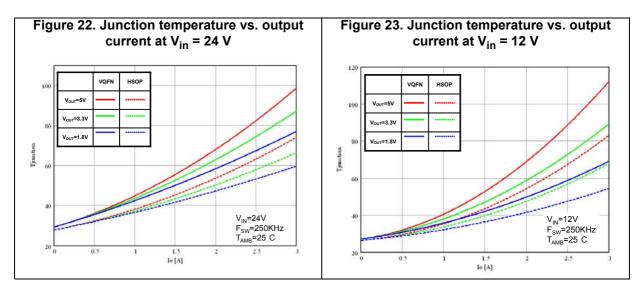

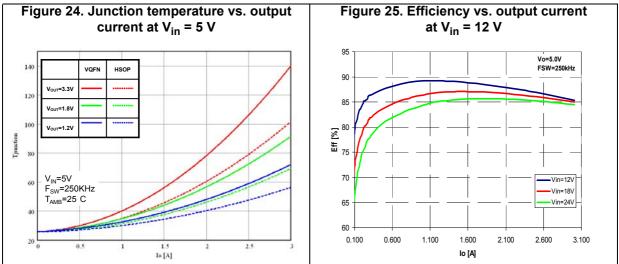

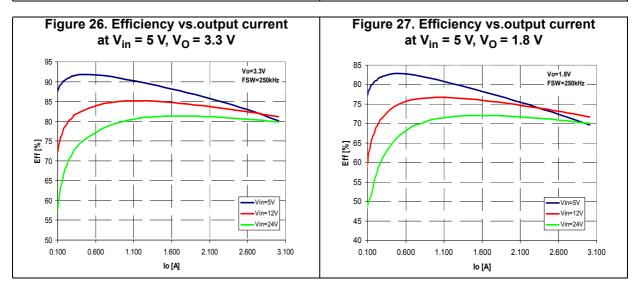

### 6.5 Thermal considerations

The thermal design is important to prevent the thermal shutdown of the device if junction temperature goes above 150 °C. The three different sources of losses within the device are:

a) conduction losses due to the not negligible R<sub>DS(on)</sub> of the power switch; these are equal to:

#### **Equation 34**

$$P_{ON} = R_{DS(on)} \cdot (I_{OUT})^2 \cdot D$$

where *D* is the duty cycle of the application and the maximum  $R_{DS(on)}$  overtemperature is 220 m $\Omega$ . Note that the duty cycle is theoretically given by the ratio between V<sub>OUT</sub> and V<sub>IN</sub>, but actually it is quite higher to compensate the losses of the regulator. So the conduction losses increase compared with the ideal case.

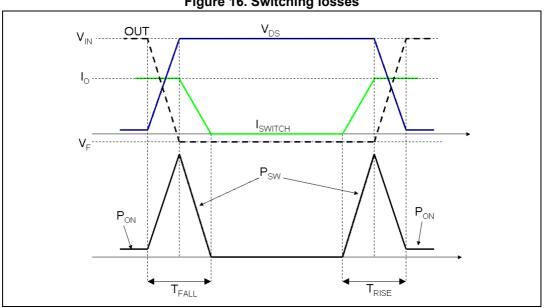

b) switching losses due to power MOSFET turn ON and OFF; these can be calculated as:

#### Equation 35

$$\mathsf{P}_{\mathsf{SW}} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \frac{(\mathsf{T}_{\mathsf{RISE}} + \mathsf{T}_{\mathsf{FALL}})}{2} \cdot \mathsf{Fsw} = \mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{OUT}} \cdot \mathsf{T}_{\mathsf{SW}} \cdot \mathsf{F}_{\mathsf{SW}}$$

where  $T_{R/SE}$  and  $T_{FALL}$  are the overlap times of the voltage across the power switch ( $V_{DS}$ ) and the current flowing into it during turn ON and turn OFF phases, as shown in *Figure 16*.  $T_{SW}$  is the equivalent switching time. For this device the typical value for the equivalent switching time is 40 ns.

c) Quiescent current losses, calculated as:

#### **Equation 36**

$P_Q = V_{IN} \cdot I_Q$

where  $I_Q$  is the quiescent current ( $I_Q$ = 2.4 mA).

The junction temperature  $T_J$  can be calculated as:

#### **Equation 37**

$$T_J = T_A + Rth_{JA} \cdot P_{TOT}$$

where  $T_A$  is the ambient temperature and  $P_{TOT}$  is the sum of the power losses just seen.

$R_{th(JA)}$  is the equivalent thermal resistance junction to ambient of the device; it can be calculated as the parallel of many paths of heat conduction from the junction to the ambient. For this device the path through the exposed pad is the one conducting the largest amount of heat. The  $R_{th(JA)}$  measured on the demonstration board described in the following paragraph is about 40 °C/W for the HSOP8 package.

Figure 16. Switching losses

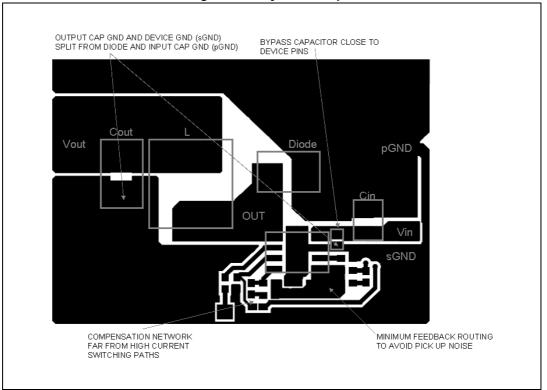

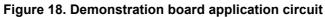

#### 6.6 Layout considerations

The PC board layout of switching DC-DC regulator is very important to minimize the noise injected in high impedance nodes and interference generated by the high switching current loops.

In a step-down converter the input loop (including the input capacitor, the power MOSFET and the freewheeling diode) is the most critical one. This is due to the fact that the high value pulsed current is flowing through it. In order to minimize the EMI, this loop must be as short as possible.

The feedback pin (FB) connection to the external resistor divider is a high impedance node, so the interference can be minimized by placing the routing of the feedback node as far as possible from the high current paths. To reduce the pick-up noise, the resistor divider must be placed very close to the device.

To filter the high frequency noise, a small bypass capacitor (220 nF - 1 µF) can be added as close as possible to the input voltage pin of the device.

Thanks to the exposed pad of the device, the ground plane helps to reduce the thermal resistance junction to ambient; so a large ground plane enhances the thermal performance of the converter allowing high power conversion.

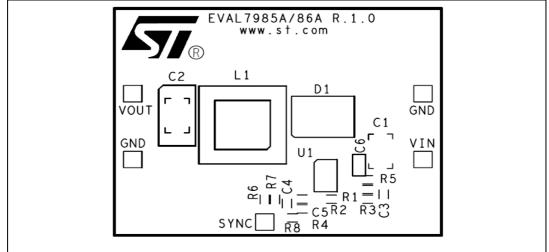

In *Figure 17*, a layout example is shown.

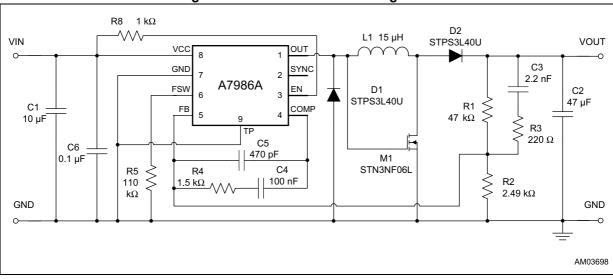

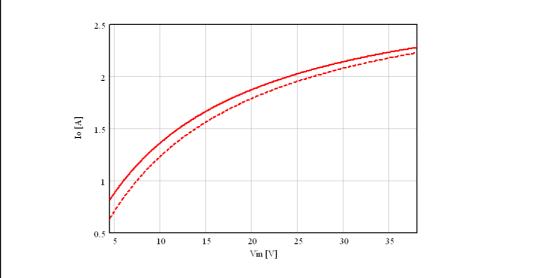

## 6.7 Application circuit

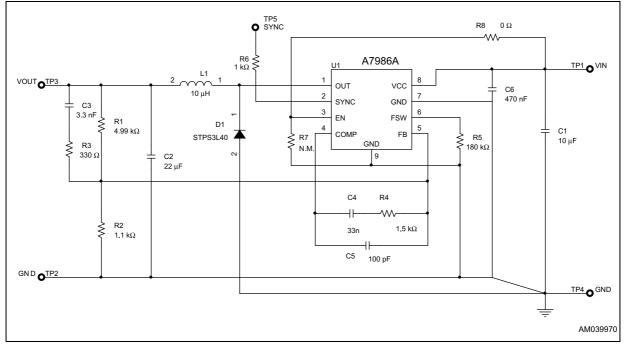

In *Figure 18* the demonstration board application circuit is shown.

| Table | 9.  | Component list   |

|-------|-----|------------------|

|       | ••• | •••••••••••••••• |

| Reference | Part number       | Description                                  | Manufacturer      |  |  |

|-----------|-------------------|----------------------------------------------|-------------------|--|--|

| C1        | UMK325BJ106MM-T   | 10 μF, 50 V                                  | Taiyo Yuden       |  |  |

| C2        | GRM32ER61E226KE15 | 22 μF, 25 V                                  | Murata            |  |  |

| C3        | -                 | 3.3 nF, 50 V                                 | -                 |  |  |

| C4        | -                 | 33 nF, 50 V                                  | -                 |  |  |

| C5        | -                 | 100 pF, 50 V                                 | -                 |  |  |

| C6        | -                 | 470 nF, 50 V                                 | -                 |  |  |

| R1        | -                 | 4.99 kΩ, 1%, 0.1 W 0603                      | -                 |  |  |

| R2        | -                 | 1.1 kΩ, 1%, 0.1 W 0603                       | -                 |  |  |

| R3        | -                 | 330 Ω, 1%, 0.1 W 0603                        | -                 |  |  |

| R4        | -                 | 1.5 kΩ, 1%, 0.1 W 0603                       | -                 |  |  |

| R5        | -                 | 180 kΩ, 1%, 0.1 W 0603                       | -                 |  |  |

| D1        | STPS3L40          | 3 A DC, 40 V                                 | STMicroelectronic |  |  |

| L1        | MSS1038-103NL     | 10 μH, 30%, 3.9 A, DCR <sub>MAX</sub> =35 mΩ | Coilcraft         |  |  |

| L1        | MSS1038-103NL     | 10 μH, 30%, 3.9 A, DCR <sub>MAX</sub> =35 mΩ | Coilcraft         |  |  |

Figure 20. PCB layout: A7986A (bottom side)

#### Figure 21. PCB layout: A7986A (front side)

DocID022801 Rev 8

## 7 Application ideas

## 7.1 Positive buck-boost

The A7986A device can implement the step-up/down converter with a positive output voltage.

*Figure 34* shows the schematic: one power MOSFET and one Schottky diode are added to the standard buck topology to provide 12 V output voltage with input voltage from 4.5 V to 38 V.

Figure 34. Positive buck-boost regulator

The relationship between input and output voltage is:

**Equation 38**

$$V_{OUT} = V_{IN} \cdot \frac{D}{1 - D}$$

so the duty cycle is:

**Equation 39**

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{OUT}} + \mathsf{V}_{\mathsf{IN}}}$$

The output voltage isn't limited by the maximum operating voltage of the device (38 V), because the output voltage is sensed only through the resistor divider. The external power MOSFET maximum drain to source voltage must be higher than the output voltage; the maximum gate to source voltage must be higher than the input voltage (in *Figure 34*, if V<sub>IN</sub> is higher than 16 V, the gate must be protected through a Zener diode and resistor).

The current flowing through the internal power MOSFET is transferred to the load only during the OFF time, so according to the maximum DC switch current (3.0 A), the maximum output current for the buck-boost topology can be calculated from *Equation 40*.

DocID022801 Rev 8

#### **Equation 40**

$$I_{SW} = \frac{I_{OUT}}{1-D} < 3 \text{ A}$$

where  $I_{SW}$  is the average current in the embedded power MOSFET in the ON time.

To chose the right value of the inductor and to manage transient output current, which for a short time can exceed the maximum output current calculated by *Equation 40*, also the peak current in the power MOSFET must be calculated. The peak current, shown in *Equation 41*, must be lower than the minimum current limit (3.7 A).

#### **Equation 41**

$$I_{SW,PK} = \frac{I_{OUT}}{1 - D} \cdot \left[1 + \frac{r}{2}\right] < 3.7A$$

$$r = \frac{V_{OUT}}{I_{OUT} \cdot L \cdot F_{SW}} \cdot (1 - D)^{2}$$

where *r* is defined as the ratio between the inductor current ripple and the inductor DC current:

So, in the buck-boost topology the maximum output current depends on the application conditions (firstly input and output voltage, secondly switching frequency and inductor value).

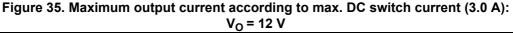

In *Figure 35*, the maximum output current for the above configuration is depicted varying the input voltage from 4.5 V to 38 V.

The dashed line considers a more accurate estimation of the duty cycles given by *Equation* 42, where power losses across diodes, external power MOSFET, and internal power MOSFET are taken into account.

$$D = \frac{V_{OUT} + 2 \cdot V_D}{V_{IN} - V_{SW} - V_{SWE} + V_{OUT} + 2 \cdot V_D}$$

where  $V_D$  is the voltage drop across the diodes,  $V_{SW}$  and  $V_{SWE}$  across the internal and external power MOSFET.

### 7.2 Inverting buck-boost

The A7986A device can implement the step-up/down converter with a negative output voltage.

*Figure 34* shows the schematic to regulate -5 V: no further external components are added to the standard buck topology.

The relationship between input and output voltage is:

#### **Equation 43**

$$V_{OUT} = -V_{IN} \cdot \frac{D}{1-D}$$

so the duty cycle is:

#### **Equation 44**

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{IN}}}$$

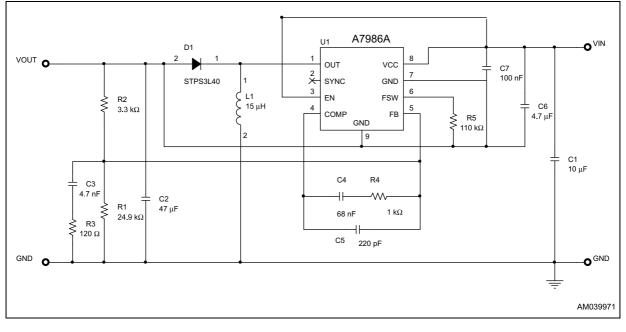

As in the positive one, in the inverting buck-boost the current flowing through the power MOSFET is transferred to the load only during the OFF time. So according to the maximum DC switch current (3.0 A), the maximum output current can be calculated from *Equation 40*, where the duty cycle is given by *Equation 44*.

#### Figure 36. Inverting buck-boost regulator

DocID022801 Rev 8

The GND pin of the device is connected to the output voltage so, given the output voltage, the input voltage range is limited by the maximum voltage the device can withstand across VCC and GND (38 V). Therefore, if the output is -5 V, the input voltage can range from 4.5 V to 33 V.

As in the positive buck-boost, the maximum output current according to application conditions is shown in *Figure 37*. The dashed line considers a more accurate estimation of the duty cycles given by *Equation 45*, where power losses across diodes and the internal power MOSFET are taken into account.

#### **Equation 45**

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{D}}}{-\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{SW}} + \mathsf{V}_{\mathsf{OUT}} - \mathsf{V}_{\mathsf{D}}}$$

Figure 37. Maximum output current according to switch max. peak current (3.0 A):  $V_0 = -5 V$

## 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

## 8.1 HSOP8 package information

#### Figure 38. HSOP8 package outline

|        | Dimensions |      |           |           |        |        |

|--------|------------|------|-----------|-----------|--------|--------|

| Symbol | mm         |      |           | inch      |        |        |

|        | Min.       | Тур. | Max.      | Min.      | Тур.   | Max.   |

| А      | -          | -    | 1.70      | -         | -      | 0.0669 |

| A1     | 0.00       | -    | 0.10      | -         | 0.00   | 0.0039 |

| A2     | 1.25       | -    | -         | 0.0492    | -      | -      |

| b      | 0.31       | -    | 0.51      | 0.0122    | -      | 0.0201 |

| С      | 0.17       | -    | 0.25      | 0.0067    | -      | 0.0098 |

| D      | 4.80       | 4.90 | 5.00      | 0.1890    | 0.1929 | 0.1969 |

| D1     | 3          | 3.1  | 3.2       | 0.118     | 0.122  | 0.126  |

| E      | 5.80       | 6.00 | 6.20      | 0.2283    | -      | 0.2441 |

| E1     | 3.80       | 3.90 | 4.00      | 0.1496    | -      | 0.1575 |

| E2     | 2.31       | 2.41 | 2.51      | 0.091     | 0.095  | 0.099  |

| е      | -          | 1.27 | -         | -         | -      | -      |

| h      | 0.25       | -    | 0.50      | 0.0098    | -      | 0.0197 |

| L      | 0.40       | -    | 1.27      | 0.0157    | -      | 0.0500 |

| k      |            |      | 0° (min), | 8° (max.) |        | •      |

| CCC    | -          | -    | 0.10      | -         | -      | 0.0039 |

Table 10. HSOP8 package mechanical data

# 9 Ordering information

| Table 11. | Ordering | information |

|-----------|----------|-------------|

|-----------|----------|-------------|

| Order code | Package | Packaging     |

|------------|---------|---------------|

| A7986A     | HSOP8   | Tube          |

| A7986ATR   | HSOP8   | Tape and reel |

# 10 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                          |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13-Feb-2012 | 1        | Initial release.                                                                                                                                                                                                                                                                                                 |  |

| 20-Mar-2012 | 2        | Section 8: Package information has been updated.                                                                                                                                                                                                                                                                 |  |

| 16-Oct-2012 | 3        | In Section 5.6 changed temperature value from 130 to 120 °C.                                                                                                                                                                                                                                                     |  |

| 04-Jul-2013 | 4        | Updated values for V <sub>FB</sub> parameter in <i>Table 4: Electrical characteristics</i> .                                                                                                                                                                                                                     |  |

| 12-Aug-2013 | 5        | Changed V <sub>FB</sub> parameter in <i>Table 4</i> from 0.594 to 0.588.                                                                                                                                                                                                                                         |  |

| 17-Mar-2014 | 6        | Updated Figure 34: Positive buck-boost regulator on page 34<br>(replaced by a new figure).<br>Updated Section 8: Package information on page 38 (reversed order<br>of Figure 38 and Table 10, minor modifications).<br>Updated cross-references throughout document.<br>Minor modifications throughout document. |  |

| 15-Sep-2016 | 7        | Updated Figure 18 on page 30, Figure 36 on page 36 and Figure 38<br>on page 38 (replaced by a new figures).<br>Updated Equation 40 on page 35 (replaced 2 A by 3 A).<br>Updated Table 10 on page 39 (replaced by new table).<br>Minor modifications throughout document.                                         |  |

| 14-Feb-2017 | 8        | Updated <i>Section : Features on page 1</i> (replaced "Qualified following AEC-Q100 requirements" by "AEC-Q100 qualified").<br>Minor modifications throughout document.                                                                                                                                          |  |

#### Table 12. Document revision history