### ACT81460

#### Low Power PMIC With Integrated Linear Charger

#### **BENEFITS and FEATURES**

#### Wide Input Voltage Range

- 4V to 5.5V Input with 20V Protection

- 2.7V to 4.5V Battery Range

#### Complete Integrated Power Solution

- Two 0.4A DC/DC Step-Down (Buck) Regulators

- One 0.4A Buck-Boost Regulator

- Three 100mA LDOs

- Three 100mA Load Switches

- One High Voltage Boost 20V

- 38mA Constant Current Sink LED Drive

- 0.8A Linear Charger

#### • Optimized Power for Portable Applications

- Active Power-Path Linear Charger (APLC)

- Multiple Sleep Modes

- Active-COT for Very Low Quiescent Current

- 6µA Quiescent Current with 6 regulators and 3 load switches running

#### • Space Savings

- Fully Integrated

- Maximum Fsw = 3MHz for small size

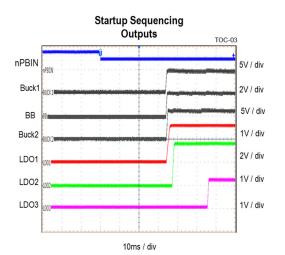

- Integrated Sequencing

#### • Easy System Level Design

- Configurable Sequencing

- Seamless Sequencing with External Supplies

- Programmable Reset and Power Good GPIOs

#### • Easy System Interface and Monitoring

- Four General Purpose I/O (4 X GPIOs)

- I2C Serial Interface

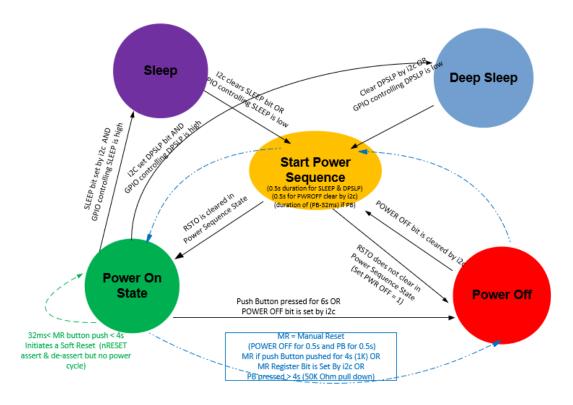

- Reset and Power Sequencing Control

- Interrupt Controller and fault monitoring

- Two configurable low power modes SLEEP & DPSLP mode.

- Watchdog Supervision

- Hard/Soft Reset Functions

- Multi-function Push button (PB) interface.

- Highly Configurable

- uP interface for status and report and controllability

- Flexible Sequencing and Fault Thresholds

- Programmable GPIO Functions

- GPIO/LED Current Sinks

- Push Button Functionality (PB)

- Contact Active Semi for PWREN Mode Startup

#### **APPLICATIONS**

- Consumer or medical wearables.

- Battery operated personal devices.

- IOT Modules.

- Cameras & DVRs

#### **GENERAL DESCRIPTION**

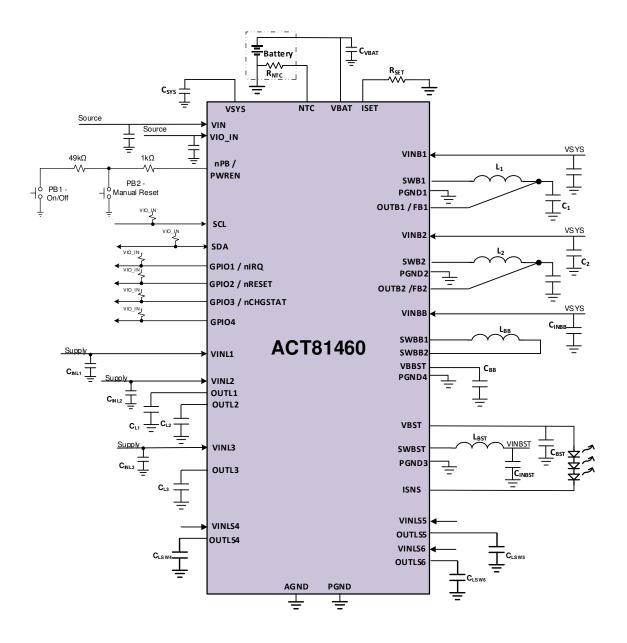

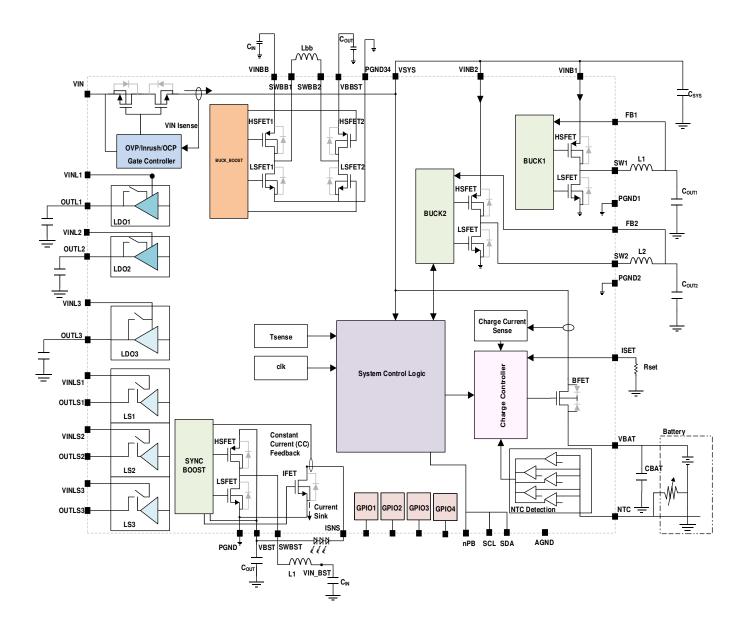

The ACT81460 is a low power PMIC (power management integrated circuit) that is specifically designed for battery operated systems and is suitable for a variety of processor applications. It features very low standby current that prolongs battery life between charges, especially in applications requiring long stand by or low power mode durations. It is a highly efficient PMIC that also enhances battery run time during normal operating modes. The number of regulators that can be turned OFF or left ON during low power modes is configurable and offers users flexibility to optimize system efficiency.

The IC includes four DC/DC converters with integrated power FETs, three low-dropout regulators (LDOs), and three load switches. Two of the DC/DC converters are step down buck regulators, one is a step up/down buckboost regulator and the fourth is a high voltage step-up boost regulator capable of providing up to 20V. Each regulator can be configured for a wide range of output voltages through the I<sup>2</sup>C interface.

The ACT81460 is highly configurable. It offers configurable power sequencing combinations, startup timing, output voltage settings, fault monitoring, interrupt control, programmable GPIO options, and many more features. The device is pre-configured at the factory with default configuration settings that can be further adjusted though firmware via the standard I<sup>2</sup>C interface to suit individual system requirements. The IC also features the ability to sequence external power supply rails as part of the power up sequence by using GPIOs.

#### **TYPICAL APPLICATION CIRCUIT**

#### FUNCTIONAL BLOCK DIAGRAM

#### ACT81460 Low Power PMIC With Integrated Linear Charger

#### **ORDERING INFORMATION**

| PART NUMBER     | V <sub>BUCK1</sub> | V <sub>BUCK2</sub> | V <sub>BUCK_BST</sub>             | V <sub>BOOST</sub> | V <sub>LDO1</sub> | $V_{LDO2}$ | V <sub>LDO3</sub> | Buck_Bst Mode |

|-----------------|--------------------|--------------------|-----------------------------------|--------------------|-------------------|------------|-------------------|---------------|

| ACT81460VM101-T | 1.8V               | 1.2V               | 5.0V                              | 12V (off)          | 3.2V              | 1.8V       | 1.2V              | Boost         |

|                 |                    |                    | Number –<br>ackage Co<br>Pin<br>C |                    |                   | (x-T       |                   |               |

Note 1: Standard product options are identified in this table. Contact factory for custom options, minimum order quantity required.

Note 2: All Active-Semi components are RoHS Compliant and with Pb-free plating unless specified differently. The term Pb-free means semiconductor products that are in compliance with current RoHS (Restriction of Hazardous Substances) standards.

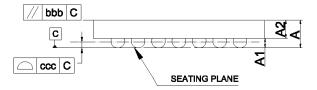

Note 3: Package Code designator "V" represents CSP

Note 4: Pin Count designator "I" represents 49 pins

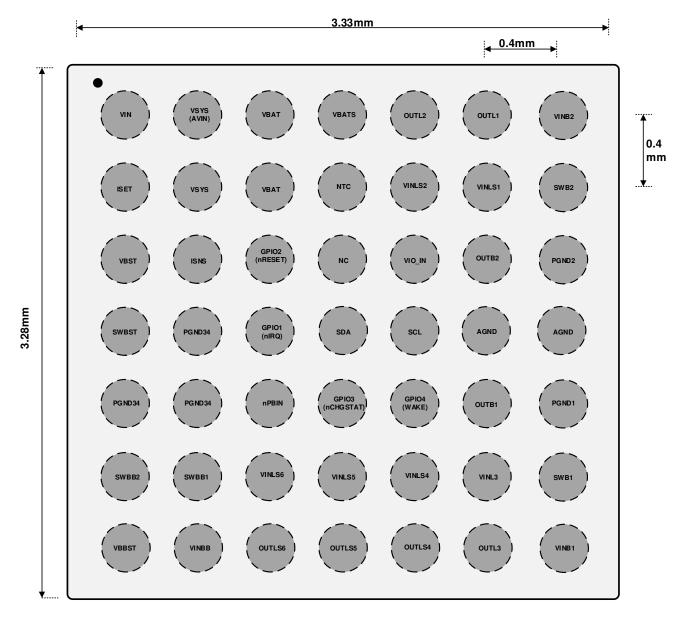

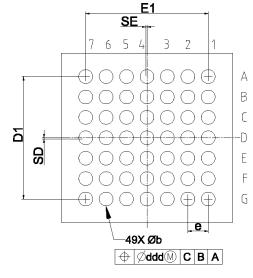

#### **PIN CONFIGURATION**

Pin Configuration - Top View (bumps down): 49 Pin CSP

Figure 1: Pin Configuration – Top View – 49 Pin CSP (0.4mm pitch) 3.32mm x 3.27mm

#### **PIN DESCRIPTIONS**

| PIN   | NAME   | DESCRIPTION                                                                                                                                                                                                                                |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1    | VIN    | VIN power input                                                                                                                                                                                                                            |

| A2/B2 | VSYS   | System Voltage (system output of smart switch / linear charger). Input voltage to buck converters                                                                                                                                          |

| A3/B3 | VBAT   | Charging Power Output pin. Positive side of battery connects to VBAT.                                                                                                                                                                      |

| A4    | VBATS  | Sense Pin for Battery Voltage. Kelvin connect VBATS close the battery to sense the battery voltage.                                                                                                                                        |

| A5    | OUTL2  | LDO2 output pin. This is also the LDO2 feedback pin.                                                                                                                                                                                       |

| A6    | OUTL1  | LDO1 output pin. This is also the LDO1 feedback pin.                                                                                                                                                                                       |

| A7    | VINB2  | Dedicated input pin for BUCK2                                                                                                                                                                                                              |

| B1    | ISET   | Charge current setting pin. Connect a resistor from ISET to AGND to program the maximum charge current.                                                                                                                                    |

| A2/B2 | VSYS   | System Voltage (system output of smart switch / linear charger). Input voltage to buck converters                                                                                                                                          |

| A3/B3 | VBAT   | Charging Power Output pin. Positive side of battery connects to VBAT.                                                                                                                                                                      |

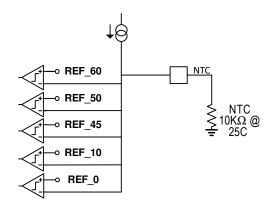

| B4    | NTC    | Battery temperature sensing input. Connect a negative temperature coefficient thermistor from TH to AGND. This pin provides a constant current output and the voltage at this pin is used for temperature calculation.                     |

| B5    | VINL2  | Dedicated power input pin for LDO2                                                                                                                                                                                                         |

| B6    | VINL1  | Dedicated power input pin for LDO1                                                                                                                                                                                                         |

| B7    | SW2    | Switch pin for BUCK2                                                                                                                                                                                                                       |

| C1    | VBST   | Boost output pin                                                                                                                                                                                                                           |

| C2    | ISNS   | Back light LED current sense pin for Boost regulator                                                                                                                                                                                       |

| C3    | GPIO2  | GPIO2. Typically defined as nRESET, but can be configured for other functionality.                                                                                                                                                         |

| C4    | NC     | No Connection, this is floating so it can be tied to the adjacent VIO_IN or left floating                                                                                                                                                  |

| C5    | VIO_IN | Digital Input Reference Voltage Input. Connect a 0.1uF ceramic capacitor between VIN_IN and AGND. Used for CMOS output reference voltage.                                                                                                  |

| C6    | FB_B2  | Feedback pin for Buck2. Kelvin connect to the Buck2 output capacitors.                                                                                                                                                                     |

| C7    | PGND2  | Power Ground pin for Buck2. The Buck2 input capacitor must be connected directly to PGND2.                                                                                                                                                 |

| D1    | SWBST  | Switch pin for Boost Regulator                                                                                                                                                                                                             |

| D2    | PGND34 | Power Ground pin for the Buck-Boost and Boost. The Buck-Boost input and output capacitors must be connected directly to PGND34. The Boost output capacitors must be directly connected PGND34. All PGND34 pins must be connected together. |

| D3    | GPIO1  | GPIO1. Typically defined as nIRQ, but can be configured for other functionality                                                                                                                                                            |

| D4    | SDA    | I <sup>2</sup> C Data Input and Output. Needs an external pull up resistor.                                                                                                                                                                |

| D5    | SCL    | I <sup>2</sup> C Clock Input. Needs an external pull up resistor.                                                                                                                                                                          |

| D6    | AGND   | Analog Ground                                                                                                                                                                                                                              |

| D7    | AGND   | Analog Ground                                                                                                                                                                                                                              |

| E1    | PGND34 | Power Ground pin for the Buck-Boost and Boost. The Buck-Boost input and output capacitors must be connected directly to PGND34. The Boost output capacitors must be directly connected PGND34. All PGND34 pins must be connected together. |

| E2    | PGND34 | Power Ground pin for the Buck-Boost and Boost. The Buck-Boost input and output capacitors must be connected directly to PGND34. The Boost output capacitors must be directly connected PGND34. All PGND34 pins must be connected together. |

| E3    | nPBIN  | Push-Button Input Pin                                                                                                                                                                                                                      |

| E4 | GPIO3  | GPIO3. Typically configured as a charge status indicator, nCHGSTAT, but can be configured for other functionality |

|----|--------|-------------------------------------------------------------------------------------------------------------------|

| E5 | GPIO4  | GPIO4. Typically configured as a general input or output, but can be configured for other functionality.          |

| E6 | FB_B1  | Feedback pin for Buck1. Kelvin connect to the Buck1 output capacitors.                                            |

| E7 | PGND1  | Power Ground pin for Buck1. Buck1 input capacitors must be connected directly to PGND1.                           |

| F1 | SWBB2  | Switch pin 2 for Buck Boost                                                                                       |

| F2 | SWBB1  | Switch pin 1 for Buck Boost                                                                                       |

| F3 | VINLS6 | Input to Load Switch 6                                                                                            |

| F4 | VINLS5 | Input to Load Switch 5                                                                                            |

| F5 | VINLS4 | Input to Load Switch 4                                                                                            |

| F6 | VINL3  | Dedicated input power pin to LDO3.                                                                                |

| F7 | SW1    | Switch pin for Buck 1                                                                                             |

| G1 | VBBST  | Output and feedback pin for Buck Boost (BBST) regulator                                                           |

| G2 | VINBB  | Dedicated input power pin to the Buck Boost regulator                                                             |

| G3 | OUTLS6 | Output of Load Switch 6                                                                                           |

| G4 | OUTLS5 | Output of Load Switch 5                                                                                           |

| G5 | OUTLS4 | Output of Load Switch 4                                                                                           |

| G6 | OUTL3  | Output and feedback pin for LDO3                                                                                  |

| G7 | VINB1  | Dedicated input power to pin to BUCK1                                                                             |

#### ABSOLUTE MAXIMUM RATINGS (NOTE 1)

| PARAMETER                                                   | VALUE                | UNIT |

|-------------------------------------------------------------|----------------------|------|

| All Pins to GND unless stated otherwise below               | -0.3 to 6.0          | V    |

| nPBIN/PWREN, GPIO 1,2,3 (nIRQ, nRESET, nCHGSTAT), ISET, NTC | -0.3 to 6.0          | V    |

| VIN to PGNDx                                                | -0.3 to 22.0         | V    |

| VSYS(AVIN), VBAT, VINLx, VINLSx, VINBx, VINBB to PGNDx      | -0.3 to 6.0          | V    |

| OUTLS1,2,3 & OUTL1,2,3                                      | -0.3 to VSYS voltage | V    |

| VBBST                                                       | -0.3 to 6.0          | V    |

| SWBBx to PGNDx                                              | -1.0 to VBBST + 1.0  | V    |

| VBST                                                        | -0.3 to 21           | V    |

| SWBST to PGNDx                                              | -1.0 to VBST + 1.0   | V    |

| VIN_IO                                                      | -0.3 to 6.0          | V    |

| ISNS to PGNDx                                               | -0.3 to VBST         | V    |

| FBx to PGNDx                                                | -0.3 to VINBx        | V    |

| SWx to PGNDx                                                | -1.0 to VINBx + 1    | V    |

| AGND, PGNDx                                                 | -0.3 to + 0.3        | V    |

| Junction to Ambient Thermal Resistance (Note 2)             | 40                   | °C/W |

| Operating Ambient Temperature Range                         | -40 to 85            | °C   |

| Operating Junction Temperature                              | -40 to 150           | °C   |

| Storage Temperature                                         | -55 to 150           | °C   |

Note1: Do not exceed these limits to prevent damage to the IC. Exposure to absolute maximum rating conditions for long periods may affect IC reliability.

Note2: Measured on Active-Semi Evaluation Kit

#### **ESD RATINGS**

| PARAMETER            | TEST CONDITIONS                       | VALUE    | UNIT |

|----------------------|---------------------------------------|----------|------|

| V_ESD_HMB (All pins) | Human body model per JEDEC JS-001     | +/- 2000 | V    |

| V_ESD_CDM (All pins) | Charged device model per JEDEC JS-002 | +/- 1000 | V    |

#### SYSTEM CHARACTERISTICS

(VIN = 5V, VSYS = 3.6V,  $T_{\text{A}}$  = 25°C, unless otherwise specified)

| PARAMETER                                        | TEST CONDITIONS                                                                                                                                                   | MIN  | ТҮР     | MAX  | UNIT |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|------|

| VIN Input Voltage                                | Charger Input                                                                                                                                                     | 4.0  |         | 20   | V    |

| VIN Input UV Threshold, rising                   | Charger Input UV                                                                                                                                                  |      | 3.8     | 4.0  | V    |

| VIN Input UV Threshold, hysteresis               |                                                                                                                                                                   | 0.1  | 0.2     | 0.3  | V    |

| VIN Input UV detection deglitch time             |                                                                                                                                                                   | 75   | 100     | 125  | μs   |

| VIN Input OV Threshold, rising                   | Charger Input OV                                                                                                                                                  |      | 5.8     |      | V    |

| VIN Input OV Threshold, hysteresis               |                                                                                                                                                                   | 0.2  | 0.3     | 0.4  | V    |

| VIN Input OV detection deglitch time             |                                                                                                                                                                   | 150  | 200     | 250  | μs   |

| VIN OCP threshold level                          | Over current threshold (Configurable: 0.5/1/1.5/2A)                                                                                                               | 0.5  | 1       | 2.0  | А    |

| VSYS Voltage Ramp time                           | Soft Start time, V <sub>SYS</sub> , C <sub>SYS</sub> < 100 μF.                                                                                                    | 400  | 500     | 700  | μs   |

| System Voltage Range                             |                                                                                                                                                                   | 2.7  |         | 5.7  | V    |

| VINL1,2 referenced to AGND                       |                                                                                                                                                                   | 1.5  |         | VSYS | V    |

| VINL3 referenced to AGND                         |                                                                                                                                                                   | 1.2  |         | VSYS | V    |

| VINLS4,5,6 referenced to AGND                    |                                                                                                                                                                   | 0.8  |         | VSYS | V    |

| VSYS POR Level, Rising                           | IC Powers up at this voltage                                                                                                                                      |      | 1.4     |      | V    |

| VSYS POR Level, Rising                           | IC Powers down at this voltage                                                                                                                                    |      | 1.2     |      | V    |

| VSYS UVLO Threshold Falling                      |                                                                                                                                                                   | 2.34 | 2.5     | 2.66 | V    |

| VSYS UVLO Hysteresis                             | Voltage above the UVLO Falling Threshold, above which all regulators turn on (device powers up)                                                                   | 75   | 100     | 150  | mV   |

| VSYS UV Warning Interrupt Thresh-<br>old Falling | Configurable in 100mV steps from 1.85V to 3.35V<br>Must be set above the VSYS UVLO Falling<br>Threshold plus the Hysteresis                                       | -0.2 | Nominal | +0.2 | V    |

| VSYS UV Warning Interrupt Hyste-<br>resis        | Voltage Rising                                                                                                                                                    | 0.1  | 0.2     | 0.3  | V    |

| VSYS OV Threshold Rising                         | Overvoltage Set Point                                                                                                                                             | 5.5  | 5.7     | 5.9  | V    |

| VSYS OV Hysteresis                               | Voltage Falling                                                                                                                                                   | 100  | 200     | 300  | mV   |

| VSYS UV Deglitch Time                            |                                                                                                                                                                   | 80   | 100     | 120  | μs   |

| VSYS OV Deglitch Time                            |                                                                                                                                                                   | 160  | 200     | 240  | μs   |

| Operating Supply Current                         | All regulators enabled but no load, boost regulator<br>is disabled. Charger off, power supplied from<br>VSYS.                                                     |      | 6       | 8    | μA   |

| Operating Supply Current                         | LDO1 enabled but no load. BUCK1/2, Buck-boost,<br>Boost, and Charger disabled. Battery FET enabled<br>and supplied from VBAT. References and<br>monitors enabled. |      | 2.1     | 2.6  | μA   |

| Operating Supply Current                         | LDO1 and one BUCK regulator enabled with no<br>load. Charger disabled. Power supplied from<br>VSYS. References and monitors enabled.                              |      | 2.7     | 3.2  | μA   |

| Thermal Low Power Threshold                      |                                                                                                                                                                   |      | 70      |      | °C   |

| Thermal Warning Temperature                      | Temperature rising.                                                                                                                                               | 115  | 125     | 135  | °C   |

| Thermal Shutdown Temperature                     | Temperature rising.                                                                                                                                               | 140  | 155     | 170  | °C   |

| Thermal Shutdown Hysteresis                      |                                                                                                                                                                   |      | 25      |      | °C   |

| Power Up Delay after initial VSYS                                       | Time from VSYS > UVLO threshold to Internal<br>Power-On Clear (POR)                                                           |    |                                           | 5   | ms |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------|-----|----|

| Startup Delay after initial VSYS                                        | Time from VSYS > UVLO threshold to start of first regulator turning On.                                                       |    |                                           | 10  | ms |

| Transition time from Sleep State<br>(SLEEP) to Active State             | Time from I2C command to clear sleep mode to time when the first regulator turns ON with minimum turn on delay configuration. |    | 90                                        |     | μs |

| Turn Off Delay                                                          | Time from turn off event to when the first power rail turns off with minimum turn off delay configuration.                    |    | 56                                        |     | μs |

| Regulator Startup Delay Program-<br>mable Range between turn on events. | ONDLY=000<br>ONDLY=001<br>ONDLY=010<br>ONDLY=011<br>ONDLY=100<br>ONDLY=101<br>ONDLY=110<br>ONDLY=111                          |    | 0<br>0.5<br>1<br>2<br>5<br>10<br>15<br>20 |     | ms |

| Regulator Turn Off Delay Program-<br>mable Range                        | Configurable in 4ms steps                                                                                                     | 0  |                                           | 60  | ms |

| nRESET, Delay Timing                                                    | Configurable to 20, 40, 60 or 100ms.                                                                                          | 20 |                                           | 100 | ms |

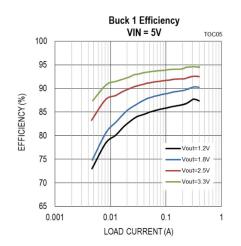

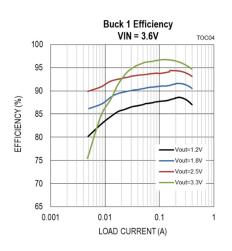

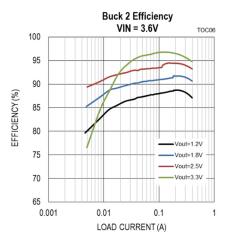

#### **BUCK1 AND BUCK2 ELECRICAL CHARACTERISTICS**

(VSYS = 3.6V,  $T_A$  = 25°C, unless otherwise specified)

| PARAMETER                                         | TEST CONDITIONS                                                                              | MIN | ТҮР              | MAX | UNIT              |

|---------------------------------------------------|----------------------------------------------------------------------------------------------|-----|------------------|-----|-------------------|

| Input Operating Voltage Range                     |                                                                                              | 2.7 |                  | 5.5 | V                 |

| Output Operating Voltage Range                    | Configurable in 50mV steps (Note 1)                                                          | 0.6 |                  | 3.6 | V                 |

| Maximum Output Current                            | (Note 1)                                                                                     | 0.4 |                  |     | Α                 |

| Standby Supply Current, Low<br>Power Mode Enabled | $V_{OUTBx} >= 103\%$ of setpoint, Regulator Enabled,<br>$V_{OUTBx} = 1.2V$ , No Load         |     | 0.6              | 0.8 | μΑ                |

| Shutdown Current                                  | Regulator Disabled                                                                           |     |                  | 0.1 | μA                |

|                                                   | $V_{OUTBx} > 1.2V$ , $I_{OUT} = 0.4A$ (PWM mode)                                             | -3  | V <sub>NOM</sub> | 3   | %                 |

|                                                   | V <sub>OUTBx</sub> =< 1.2V, I <sub>OUT</sub> = 0.4A (PWM mode)                               | -36 | V <sub>NOM</sub> | 36  | mV                |

|                                                   | $V_{OUTBx} > 1.2V, I_{OUT} = 1mA (PFM mode)$                                                 | -4  | V <sub>NOM</sub> | 4   | %                 |

| Output Voltage Accuracy                           | V <sub>OUTBx</sub> =< 1.2V, I <sub>OUT</sub> = 1mA (PFM mode)                                | -48 | V <sub>NOM</sub> | 48  | mV                |

|                                                   | $V_{OUTBx} > 1.2V$ , $I_{OUT} < 0.01mA$ (LPM on)                                             | -5  | V <sub>NOM</sub> | 5   | %                 |

|                                                   | $V_{OUTBx} = < 1.2V, I_{OUT} < 0.01mA (LPM on)$                                              | -60 | V <sub>NOM</sub> | 60  | mV                |

| Line Regulation                                   | $V_{IN\_B1}$ = 3.0V to 5.0V, 200mA, PWM Regulation.<br>(Note 2)                              |     | 0.08             |     | %/V               |

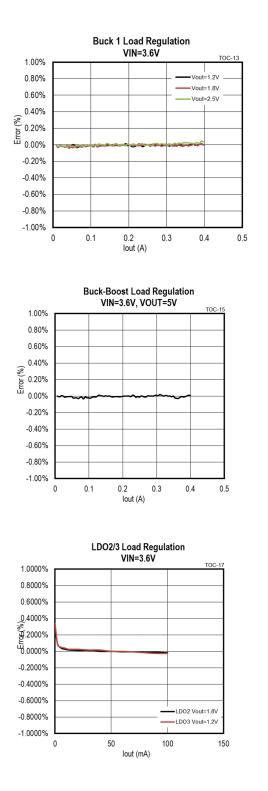

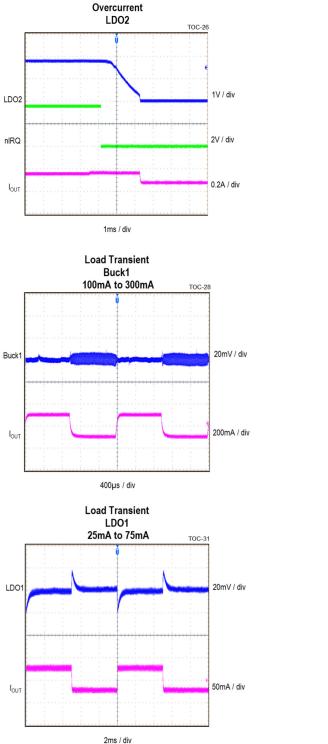

| Load Regulation                                   | PWM mode, 0.1A to 0.4A. (Note 2)                                                             |     | 0.1              |     | %/A               |

| Power Good Threshold                              | $V_{\text{OUTBx}}$ Rising, relative to regulation point                                      | 88  | 92               | 96  | %V <sub>NOM</sub> |

| Power Good Hysteresis                             | $V_{\text{OUTBx}}$ Falling, relative to regulation point                                     |     | 3                |     | %V <sub>NOM</sub> |

|                                                   | Freq = 00, VIN = 3.6V, V <sub>OUTB1</sub> = 1.8V. V <sub>OUTB2</sub> = 1.2V, Note $^{1}$     |     | 1.5              |     | MHz               |

| Switching Frequency, PWM Mode                     | Freq = 01, VIN = 3.6V, V <sub>OUTB1</sub> = 1.8V. V <sub>OUTB2</sub> = 1.2V, Note $^{1}$     |     | 2.0              |     | MHz               |

| Switching Frequency, FWM Mode                     | Freq = 10, VIN = 3.6V, $V_{OUTB1}$ = 1.8V. $V_{OUTB2}$ = 1.2V, Note <sup>1,2</sup>           |     | 2.5              |     | MHz               |

|                                                   | Freq = 11, VIN = 3.6V, V <sub>OUTB1</sub> = 1.8V<br>V <sub>OUTB2</sub> = 1.2V, Note $^{1,2}$ |     | 3.3              |     | MHz               |

| Soft-Start Ramp                                   | 10% to 90% V <sub>NOM</sub>                                                                  |     | 2.5              |     | V/ms              |

| T <sub>start</sub> , Time from EN to POK          | Time from enable to POK (92% VNOM)<br>Buck1 = 1.8V<br>Buck2 = 1.2V                           |     | 3100<br>3500     |     | μs                |

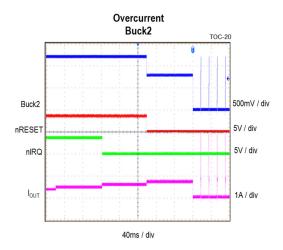

| Current Limit, Cycle-by-Cycle (ac-                | ILIM_SET = 0                                                                                 |     | 0.6              |     | А                 |

| curacy is valid at a CMI's default setting)       | ILIM_SET = 1                                                                                 |     | 1.2              |     | Α                 |

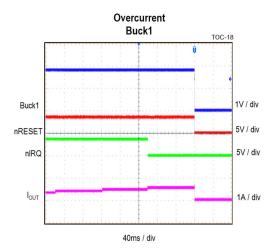

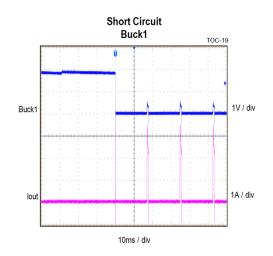

| Current Limit, Warning                            | 2 consecutive switching cycles of 125% of cycle-by-<br>cycle current limit.                  |     | 125              |     | %                 |

| Current Limit, Shutdown                           | 8 consecutive switching cycles of 125% of cycle-by-<br>cycle current limit.                  |     | 125              |     | %                 |

| PMOS On-Resistance                                | $I_{SW} = -0.2A, V_{IN} = 5.0V$                                                              |     | 250              |     | mΩ                |

| NMOS On-Resistance                                | I <sub>SW</sub> = 0.2A, V <sub>IN</sub> = 5.0V                                               |     | 200              |     | mΩ                |

| SW Leakage Current           | $V_{\text{IN}} = 5.5V,  V_{\text{SW}} = 0 \text{ or } 5.5V,  T_j < 60^{\circ}C$ |    |    | 0.1 | μA    |

|------------------------------|---------------------------------------------------------------------------------|----|----|-----|-------|

| Dynamic Voltage Scaling Rate |                                                                                 |    | 5  |     | mV/us |

| Output Pull Down Resistance  | Pull Down Enabled when the regulator is turned off. $V_{OUTBX} = 0.1$ .         | 32 |    | 50  | Ohms  |

| Recommended Max Duty Cycle   |                                                                                 |    | 85 |     | %     |

Note1: L = 1uH, DCR = 80 m $\Omega$ , C<sub>OUT\_effective</sub> =10uF. If the user desires different VOUT configurations, from the default CMI, they should consult with active-semi Applications staff for proper setup of the device. Default CMI is what sets the output voltages of the regulators on POR event. Parts can be ordered with different CMI settings, to fit the specific customer output voltages in the application.

Note2: For heavy loads and high frequency settings, may need to use different VFFResSelect [2:0] setting for a stable switching frequency. Load may be limited when above 200mA, in order to keep the switch pin at a stable frequency Please consult with Applications for proper setup of different frequencies, and different output voltage settings.

#### **BUCK-BOOST ELECTRICAL CHARACTERISTICS**

(VSYS = 3.6V, Fsw = 2MHz,  $T_A$  = 25°C, unless otherwise specified)

| PARAMETER                               | TEST CONDITIONS                                                              | MIN | ТҮР                      | MAX  | UNIT  |

|-----------------------------------------|------------------------------------------------------------------------------|-----|--------------------------|------|-------|

| VINBB, Operating Voltage Range          |                                                                              | 2.7 |                          | 5.5  | V     |

| VBBST, Output Voltage Range             | Configurable in 50mV steps                                                   | 3.2 |                          | 5.0  | V     |

|                                         | VBBST >= 4.2V                                                                | 250 |                          |      | mA    |

| IBBST, Maximum Output Current           | VBBST < 4.2V, (Note 1)                                                       | 400 |                          |      | mA    |

| No Load Input Current                   | VBBST = 5V, No Load                                                          |     | 0.9                      | 1.2  | μA    |

| Shutdown Current                        | Regulator Disabled                                                           |     |                          | 0.1  | μA    |

|                                         | I <sub>OUT</sub> = 100mA (PWM), BB Mode                                      | -3  | V <sub>NOM</sub>         | 3    | %     |

| Output Voltage Accuracy                 | Iout = 1mA, BB Mode                                                          | -5  | V <sub>NOM</sub>         | 5    | %     |

| Line Regulation                         | $V_{BBST} = 5V$ , $V_{INBB} = 3.0V$ to 5.0V, 100mA, PWM Regulation. (Note 2) |     | 0.03                     |      | %/V   |

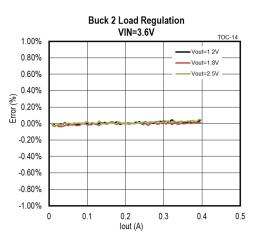

| Load Regulation                         | V <sub>BBST</sub> = 5V, PWM Regulation, (Note 1)                             |     | 0.4                      |      | %/A   |

| Power Good Threshold                    | VBBST Rising                                                                 | 88  | 92                       | 96   | %VNOM |

| Power Good Hysteresis                   | VBBST Falling                                                                |     | 3                        |      | %VNOM |

| Overvoltage Fault Threshold             | VBBST Rising                                                                 | 105 | 110                      | 115  | %VNOM |

| Overvoltage Fault Hysteresis            | VBBST Falling                                                                |     | 3                        |      | %VNOM |

| Switching Frequency, PWM Mode           |                                                                              |     | 3.3<br>2.5<br>2.0<br>1.5 |      | MHz   |

| Soft-Start Period T <sub>SS</sub>       | 10% to 90% VBBST ramp time (Note 1)                                          |     | 800                      | 1200 | μs    |

| T <sub>start</sub> , Time from EN to PG | Time from enable to PGOOD / POK.                                             |     | 1500                     |      | μs    |

|                                         | VBBST > 4.2V                                                                 |     | 0.85                     |      | А     |

| Current Limit, Cycle-by-Cycle           | VBBST <= 4.2V, (Note 2)                                                      |     | 1.2                      |      | А     |

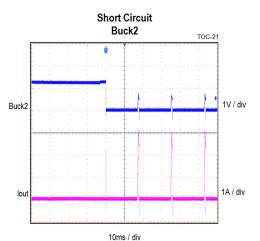

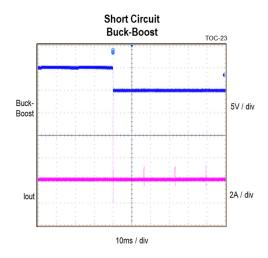

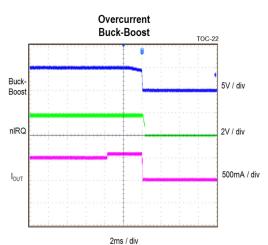

| Current Limit, Warning                  | 2 consecutive switching cycles at 125% of cycle-by-cycle current limit.      |     | 125                      |      | %     |

| Current Limit, Shutdown                 | 8 consecutive switching cycles of 125% of cycle-by-cycle current limit.      |     | 125                      |      | %     |

| VINBB to SWBB1 (HSFET1) Resistance      | $I_{SW}=-0.2A,\ V_{BBST}=5.0V,\ T_{j}=25^{\circ}C$                           |     | 210                      |      | mΩ    |

| SWBB1 to PGND (LSFET1) Resistance       | $I_{SW} = 0.2A, V_{BBST} = 5.0V, T_j = 25^{\circ}C$                          |     | 185                      |      | mΩ    |

| VBBST to SWBB2 (HSFET2) Resistance      | $I_{SW} = -0.2A, V_{BBTS} = 5.0V, T_j = 25^{\circ}C$                         |     | 170                      |      | mΩ    |

| SWBB2 to PGND (LSFET2) Resistance       | $I_{SW} = 0.2A, V_{BBST} = 5.0V, T_j = 25^{\circ}C$                          |     | 170                      |      | mΩ    |

| SWBB1 and SWBB2 Leakage Current         | V <sub>SYS</sub> = 5.5V, SWBB1 = SWBB2 = 0 or 5.5V                           |     |                          | 0.1  | μA    |

Data Sheet Rev. B, November 2019 | Subject to change without notice

| Output Pull Down Resistance | Pull Down Enabled when the regulator is turned off. VBBST = 0.1V. | 32 |  | 50 | Ohms |  |

|-----------------------------|-------------------------------------------------------------------|----|--|----|------|--|

|-----------------------------|-------------------------------------------------------------------|----|--|----|------|--|

Note 1: L = 2.2uH, DCR 80 m $\Omega$ , C<sub>OUT\_effective</sub> = 10uF. If the user desires different VOUT configurations from the default CMI, contact active-semi. Default CMI is what sets the output voltages of the regulators on POR event. Parts can be ordered with different CMI settings, to fit the specific customer output voltages in the application.

Note 2: Depends on ordering options (vout, ilim, etc), and external inductor selection.

Note 3: Device needs to be tuned for these frequencies. Contact active-semi for a different default operating frequencies or voltage.

#### **BOOST ELECTRICAL CHARACTERISTICS**

(VSYS = 3.6V, VBOOST = 12V,  $T_A = 25^{\circ}C$ , unless otherwise specified)

| PARAMETER                                         | TEST CONDITIONS                                                                                                                | MIN   | ТҮР              | MAX     | UNIT   |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|------------------|---------|--------|

| VINBOOST, Operating Voltage<br>Range              |                                                                                                                                | 3.0   |                  | Vsys_ov | V      |

| VBST Programmable Output<br>Voltage Range         | Configurable in 250mV steps, VSET [5:0]                                                                                        | 5.0   |                  | 20.75   | V      |

| ISNS Programmable Boost<br>Current Range          | Constant current mode; 0.625mA per step across entire range                                                                    | 0.625 |                  | 39.375  | mA     |

| ISNS Boost Current Accuracy                       | At default CMI setting.                                                                                                        | -2    |                  | 2       | %      |

| ISNS Voltage                                      | Constant Current sense voltage                                                                                                 |       | 0.25             |         | V      |

| ISNS Programmable LED<br>Current Sink Range       | DISCC = 1, Disable CC mode and ISNS pin<br>configured as a constant current sink. 0.625mA<br>per step across the entire range. | 0.625 |                  | 39.375  | mA     |

| IVBST, Maximum Output                             | Continuous boost output current, VBST=12V                                                                                      |       |                  | 39.375  | mA     |

| Current                                           | Continuous boost output current, VBST=20V                                                                                      |       |                  | 32      | mA     |

| Standby Supply Current, Low<br>Power Mode Enabled | VBST >= 103% of Nominal Voltage, Regulator<br>Enabled, VBST = 12.0V, No Load                                                   |       | 373              |         | μΑ     |

| Shutdown Current                                  | Regulator Disabled                                                                                                             |       | 0.12             |         | μA     |

| Output Voltage Accuracy                           | VBST =12.0V, I <sub>OUT</sub> = 0.02A                                                                                          | -3    | V <sub>NOM</sub> | 3       | %      |

| Line Regulation                                   | VBST = 12.0V, VSYS = 3.0V to 5.0V. 20mA (Note 1)                                                                               |       | 0.01             |         | %/V    |

| Load Regulation                                   | VBST = 12.0V, I <sub>Boost</sub> 2.0mA to 20mA. (Note 1)                                                                       |       | 0.005            |         | %/mA   |

| Power Good Threshold                              | VBST Rising                                                                                                                    | 65    | 70               | 75      | %VNOM  |

| Power Good Hysteresis                             | VBST Falling                                                                                                                   |       | 3                |         | %VNOM  |

| Overvoltage Fault Threshold                       | VBST Rising                                                                                                                    | 105   | 110              | 115     | %VNOM  |

| Overvoltage Fault Hysteresis                      | VBST Falling                                                                                                                   |       | 3                |         | %VNOM  |

| Switching Frequency, PWM<br>Mode                  | VBST = 12.0V, I <sub>Boost</sub> = 20mA, (Note 1)                                                                              |       | 1.125            |         | MHz    |

| Soft-Start Period Tss                             | 10% to 90% of setpoint. (Note 1)                                                                                               |       | 80               |         | ms     |

| T <sub>start</sub> , Time from EN to POK          | 70% of setpoint. (Note 1)                                                                                                      |       | 80               |         | ms     |

| Current Limit, Cycle-by-Cycle                     | LSILIM = 0<br>LSILIM = 1                                                                                                       |       | 1.0<br>1.35      |         | A<br>A |

| Current Limit, Warning                            | % compared to Current Limit, cycle-by-cycle                                                                                    | 70    | 80               | 90      | %      |

| VBST to SWBST (HSFET)<br>Resistance               | $I_{SWBST} = -0.2A, V_{SYS} = 5.0V, VBST = 5.0V, T_j < 85^{\circ}C$                                                            |       | 400              |         | mΩ     |

| SWBST to PGND (LSFET)<br>Resistance               | $I_{SWBST} = 0.2A, V_{SYS} = 5.0V, VBST = 5.0V, T_j < 85^{\circ}C$                                                             |       | 250              |         | mΩ     |

| SWBST Leakage Current                             | V <sub>SWBST</sub> = 20V, V <sub>SYS</sub> = 3.6V                                                                              |       |                  | 1       | μA     |

#### Note1: L = 2.2uH, DCR = 10mΩ, C = 10uF LDO1 AND LDO2 ELECTRICAL CHARACTERISTICS

(VINL1 =VINL2 = 3.6V,  $T_A = 25^{\circ}C$ , unless otherwise specified)

### ACT81460

Low Power PMIC With Integrated Linear Charger

| PARAMETER                                | TEST CONDITIONS                                                                                        | MIN | ТҮР              | МАХ  | UNIT               |

|------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|------------------|------|--------------------|

| Input Operating Voltage<br>Range         | VINL1,2 (Input Voltage) to LDO1,2                                                                      | 1.5 |                  | VSYS | V                  |

| Output Voltage Programmable<br>Range     | Configurable in 50mV steps                                                                             | 0.6 |                  | 3.6  | V                  |

| Output Current                           | V <sub>OUTL1,2</sub> < VINL1,2 - 0.25V                                                                 | 100 |                  |      | mA                 |

| Output Voltage Accuracy                  | 1.2V < V <sub>OUTL1,2</sub> < VINL1,2 - 0.25V                                                          | -3  | V <sub>NOM</sub> | 3    | %                  |

|                                          | 0.6V < V <sub>OUTL1,2</sub> < 1.2V                                                                     | -36 | V <sub>NOM</sub> | 36   | mV                 |

| Line Regulation                          | VINL1,2 - V <sub>OUTL1,2</sub> > 0.25V, VINL1,2= 2.7V to VSYS.<br>I <sub>LD01,2</sub> = 10mA. (Note 2) |     | 0.02             |      | %/V                |

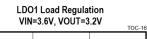

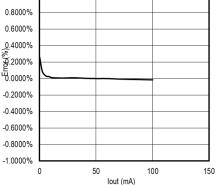

| Load Regulation                          | I <sub>LDO1</sub> = 1mA to 100mA                                                                       |     | 2.0              |      | %/A                |

|                                          | f = 1kHz, I <sub>LDO1</sub> = 10mA                                                                     |     | 59.6             |      | dB                 |

| Power Supply Rejection Ratio             | f = 10kHz, I <sub>LDO1</sub> = 10mA                                                                    |     | 55.5             |      | dB                 |

|                                          | f = 2.25MHz, I <sub>LDO1</sub> = 10mA                                                                  |     | 10.6             |      | dB                 |

| Iq1, Supply Current                      | Regulator Enabled, no load, UV/OV and Current Limit Monitors are OFF.                                  |     | 0.4              | 0.5  | μA                 |

| Iq2, Supply Current                      | Regulator Enabled, no load, UV/OV and Current Limit Monitors are ON.                                   |     | 0.5              | 0.6  | μA                 |

| Soft-Start Ramp Rate                     |                                                                                                        |     | 1.7              |      | V/ms               |

| Power Good Threshold                     | V <sub>OUTL1,2</sub> Rising                                                                            | 88  | 92               | 96   | % V <sub>NOM</sub> |

| Power Good Hysteresis                    | VOUTL1,2 Falling                                                                                       |     | 3                |      | % V <sub>NOM</sub> |

| Overvoltage Fault Threshold              | V <sub>OUTL1,2</sub> Rising                                                                            | 105 | 110              | 115  | % V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis             | VOUTL1,2 Falling                                                                                       |     | 3                |      | % V <sub>NOM</sub> |

| Discharge Resistance                     | V <sub>OUTL1,2</sub> = 0.1V                                                                            |     |                  | 80   | Ω                  |

| Dropout Voltage                          | I <sub>LDOL1,2</sub> = 50mA,                                                                           |     |                  | 100  | mV                 |

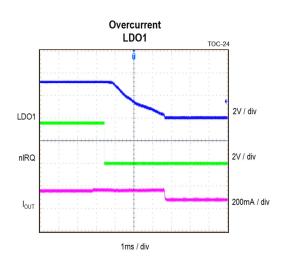

| Output Current Limit                     | V <sub>INL1,2</sub> = 1.5V to VSYS                                                                     | 120 |                  |      | mA                 |

| T <sub>start</sub> , Time from EN to POK | 70% of setpoint.<br>$V_{OUTL1} = 3.2V$<br>$V_{OUTL2} = 1.8V$                                           |     | 2300<br>1500     |      | μs                 |

#### LDO3 ELECTRICAL CHARACTERISTICS

(VINL3 = 3.6V,  $T_A$  = 25°C, unless otherwise specified)

| PARAMETER                                | TEST CONDITIONS                                                                                                           | MIN       | ТҮР                                  | MAX     | UNIT               |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------|---------|--------------------|

| Input Operating Voltage<br>Range         | VINL3 (Input Voltage) to LDO3                                                                                             | 1.2       |                                      | VSYS    | V                  |

| Output Voltage Programmable<br>Range     | Configurable in 50mV steps                                                                                                | 0.6       |                                      | 3.6     | V                  |

| Output Current                           | $V_{OUTL3} < V_{INL3} - 0.25V, V_{INL3} > 1.5V$                                                                           | 100       |                                      |         | mA                 |

| Output Current                           | $V_{OUTL3} < V_{INL3} - 0.25V, 1.5V > V_{INL3} > 1.2V$                                                                    | 40        |                                      |         | mA                 |

| Output Voltage Accuracy                  | 1.2V < V <sub>OUTL3</sub> < V <sub>INL3</sub> - 0.25V<br>0.65V < V <sub>OUTL3</sub> < 1.2V                                | -3<br>-36 | V <sub>NOM</sub><br>V <sub>NOM</sub> | 3<br>36 | %<br>mV            |

| Line Regulation                          | $V_{\text{OUTL3}} < V_{\text{INL3}} - 0.25V, V_{\text{INL3}} = 1.5V$ to $V_{\text{SYS}}, I_{\text{LDO3}} = 10 \text{mA}.$ |           | 0.02                                 |         | %/V                |

| Load Regulation                          | I <sub>LDO3</sub> = 1mA to 100mA.                                                                                         |           | 3.0                                  |         | %/A                |

|                                          | $f = 1 \text{ kHz}, I_{\text{LDO3}} = 10 \text{ mA},$                                                                     |           | 64                                   |         | dB                 |

| Power Supply Rejection Ratio             | f = 10kHz, I <sub>LDO3</sub> = 10mA                                                                                       |           | 56.9                                 |         | dB                 |

|                                          | f = 2.25MHz, ILDO3 = 10mA                                                                                                 |           | 13.9                                 |         | dB                 |

| Supply Current per Output                | Regulator Disabled                                                                                                        |           |                                      | 0.1     | μA                 |

| Iq1, Supply Current                      | Regulator Enabled, no load, UV/OV and Current Limit Monitors are OFF.                                                     |           | 0.4                                  | 0.5     | μΑ                 |

| Iq2, Supply Current                      | Regulator Enabled, no load, UV/OV and Current Limit Monitors are ON.                                                      |           | 0.5                                  | 0.6     | μA                 |

| Soft-Start Period                        | Time from soft start "ON" to PGOOD                                                                                        |           | 1000                                 |         | μs                 |

| Power Good Threshold                     | V <sub>OUTL3</sub> Rising                                                                                                 | 88        | 92                                   | 96      | % V <sub>NOM</sub> |

| Power Good Hysteresis                    | VOUTL3 Falling                                                                                                            |           | 3                                    |         | % V <sub>NOM</sub> |

| Overvoltage Fault Threshold              | V <sub>OUTL3</sub> Rising                                                                                                 | 105       | 110                                  | 115     | % V <sub>NOM</sub> |

| Overvoltage Fault Hysteresis             | Voutl3 Falling                                                                                                            |           | 3                                    |         | % V <sub>NOM</sub> |

| Discharge Resistance                     | V <sub>OUTL3</sub> = 0.1V                                                                                                 |           |                                      | 80      | Ω                  |

| Dropout Voltage                          | Iout3 = 50mA, Vout3 = 1.2V                                                                                                |           |                                      | 140     | mV                 |

| Output Current Limit                     | V <sub>INL3</sub> = 1.5V to VSYS                                                                                          | 120       |                                      |         | mA                 |

| T <sub>start</sub> , Time from EN to POK | 70% of setpoint.                                                                                                          |           | 1100                                 |         | μs                 |

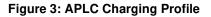

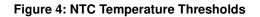

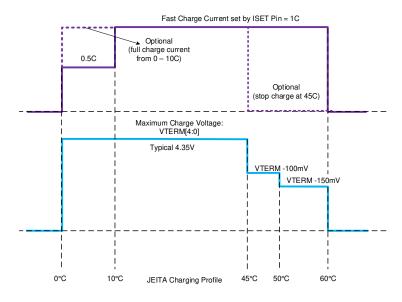

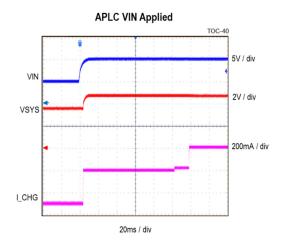

#### ACTIVE PATH LINEAR CHARGER (APLC) ELECTRICAL CHARACTERISTICS

(VIN = 5V,  $T_A = 25^{\circ}C$ , unless otherwise specified.)

| PARAMETER                                         | TEST CONDITIONS                                                                                                 | MIN                        | ТҮР                       | MAX                        | UNIT |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|----------------------------|------|

| VIN Input Voltage                                 |                                                                                                                 | 4.0                        |                           | 20                         | V    |

| VIN Input UV Threshold, rising                    |                                                                                                                 |                            | 3.8                       | 4.0                        | V    |

| VIN Input UV Threshold, hysteresis                |                                                                                                                 | 0.1                        | 0.2                       | 0.3                        | V    |

| VIN Input UV detection deglitch time              |                                                                                                                 | 75                         | 100                       | 125                        | μs   |

| VIN Input OV Threshold, rising                    |                                                                                                                 | 5.5                        | 5.7                       | 5.9                        | V    |

| VIN Input OV Threshold, hysteresis                |                                                                                                                 | 0.2                        | 0.3                       | 0.4                        | V    |

| VIN Input OV detection deglitch time              |                                                                                                                 | 75                         | 100                       | 125                        | μs   |

| VIN OCP threshold level (current limit threshold) | IINSET [1:0] = 00<br>IINSET [1:0] = 01<br>IINSET [1:0] = 10<br>IINSET [1:0] = 11                                | 0.45<br>0.9<br>1.35<br>1.7 | 0.55<br>1.0<br>1.5<br>1.9 | 0.55<br>1.1<br>1.65<br>2.1 | A    |

| VSYS Voltage Ramp time                            | Soft Start time, VSYS, $C_{SYS}$ < 100 $\mu$ F                                                                  | 400                        | 500                       | 700                        | μs   |

| System Voltage Range: VSYS referenced to AGND     |                                                                                                                 | 2.7                        |                           | 5.7                        | v    |

| VSYS regulation voltage                           |                                                                                                                 |                            | 4.8                       |                            | V    |

| VIN to VSYS Resistance                            | I <sub>VSYS</sub> = 0.2A                                                                                        |                            | 160                       | 200                        | mΩ   |

| VSYS to VBAT (BFET) Resistance                    | VBAT = 3.6V, I <sub>SYS</sub> = 0.2A                                                                            |                            | 100                       | 125                        | mΩ   |

| VIN supply current                                | Charge disabled, I <sub>VSYS</sub> = 0mA<br>CHG_EN bit = 0                                                      |                            | 0.75                      | 0.9                        | mA   |

| VIN supply current                                | Charge enabled, $I_{VSYS} = 0mA$ , $I_{CHG} = 0$<br>CHG_EN bit = 1                                              |                            | 0.95                      | 1.1                        | mA   |

| VBAT supply current                               | VIN = 0V, $I_{VSYS}$ = 0mA, BFET enabled. ILIM Disabled. VSYS powered from VBAT.                                |                            | 0.3                       | 0.5                        | μΑ   |

| VBAT supply current                               | VIN = 0V, Regulators disabled, References<br>and VSYS monitors are On, BFET enabled.<br>VSYS powered from VBAT. |                            | 1.4                       | 1.7                        | μΑ   |

| ISET pin voltage                                  | VIN = 5.0V, VSYS – VBAT > 100mV<br>ISET voltage is proportional to ICHRG, ISET<br>max in CC.                    |                            |                           | 1.2                        | v    |

| RSET, Allowable external resistor range           | RSET sets the ISET pin current                                                                                  | 1.2                        |                           | 15                         | kΩ   |

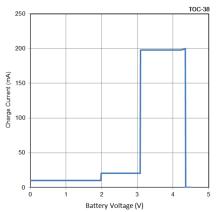

| Charge Programmable Current<br>Range              | RSET resistor sets the ISET pin current and the charge current.                                                 | 10                         |                           | 800                        | mA   |

| ISET current ratio                                | VBAT = 3.8V, ICHG/ISET Ratio. ICHG < 200mA                                                                      |                            | 10000                     |                            |      |

| Charge current accuracy                           | VBAT = 3.8V, ICHG at default charge current setting.                                                            | -10                        |                           | +10                        | %    |

### ACT81460

#### Low Power PMIC With Integrated Linear Charger

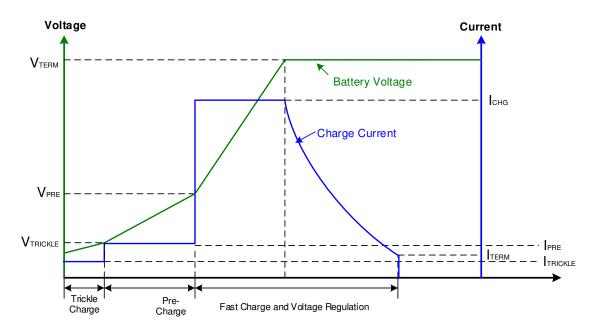

| IPRE, Precondition Charge Current                                       | IPRE is a percentage of ICHG (fast charge)<br>IPRESET $[1:0] = 00$<br>IPRESET $[1:0] = 01$<br>IPRESET $[1:0] = 10$<br>IPRESET $[1:0] = 11$ |     | 20<br>15<br>10<br>5     |      | %<br>%<br>%          |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------|------|----------------------|

| Precondition Voltage Threshold,<br>VPRE, Programmable Range             | Configure by VPRESET [3:0], 50mV step size                                                                                                 | 2.7 |                         | 3.45 | V                    |

| Precondition Voltage Threshold<br>Hysteresis                            |                                                                                                                                            |     | 0.1                     |      | V                    |

| Termination Voltage Threshold,<br>VTERM, Programmable Range<br>(Note 1) | Configure by VTERM [4:0], 20mV step size                                                                                                   | 3.9 | 4.4                     | 4.5  | V                    |

| Termination Voltage Threshold,<br>VTERM, accuracy (Note 1)              | Configure by VTERM [4:0], 20mV step size                                                                                                   | -1  | VTERM                   | 1    | %                    |

| Termination Current Threshold,<br>ITERM (Note 1)                        | Percentage of IFCHG<br>ITERM [1:0] = 00<br>ITERM [1:0] = 01<br>ITERM [1:0] = 10<br>ITERM [1:0] = 11                                        |     | 20<br>15<br>10<br>5     |      | %<br>%<br>%          |

| Charge Restart Threshold                                                | BAT_RECHG_THRESHOLD = 00<br>BAT_RECHG_THRESHOLD = 01<br>BAT_RECHG_THRESHOLD = 10<br>BAT_RECHG_THRESHOLD = 11                               |     | 80<br>120<br>160<br>200 |      | mV<br>mV<br>mV<br>mV |

| Fast charge safety timer                                                |                                                                                                                                            |     | 12000                   |      | s                    |

| Precondition charge safety timer                                        |                                                                                                                                            |     | 4000                    |      | S                    |

| Thermal regulation threshold                                            | Temperature range were charge current is proportionally reduced.                                                                           | 95  | 115                     | 150  | °C                   |

| NTC pin pull up current                                                 | VBAT = 3.8V, NTC = $10k\Omega$ resistor to AGND.                                                                                           |     | 100                     |      | μA                   |

| NTC 60°C Detection Voltage, V <sub>NTC</sub>                            |                                                                                                                                            |     | 0.300                   |      | V                    |

| NTC 60°C Hysteresis                                                     |                                                                                                                                            |     | 30                      |      | mV                   |

| NTC 50°C Voltage Detection                                              |                                                                                                                                            |     | 0.416                   |      | V                    |

| NTC 50°C Hysteresis                                                     |                                                                                                                                            |     | 40                      |      | mV                   |

| NTC 45°C Voltage Detection                                              |                                                                                                                                            |     | 0.492                   |      | V                    |

| NTC 45°C Hysteresis                                                     |                                                                                                                                            |     | 50                      |      | mV                   |

| NTC 10 <sup>o</sup> C Voltage Detection                                 |                                                                                                                                            |     | 1.792                   |      | V                    |

| NTC 10 <sup>0</sup> C Hysteresis                                        |                                                                                                                                            |     | 200                     |      | mV                   |

| NTC 0°C Voltage Detection                                               |                                                                                                                                            |     | 2.720                   |      | V                    |

| NTC 0°C Hysteresis                                                      |                                                                                                                                            |     | 300                     |      | mV                   |

Note1: For end of charge accuracy, (Bat\_ESR\*EOC Current) should be greater than 1mV

#### LOAD SWITCH 4,5,6 ELECTRICAL CHARACTERISTICS

(VSYS = 3.6V, VINLSx = 1.2V,  $T_{\text{A}}$  = 25°C, unless otherwise specified.)

| PARAMETER                                                              | TEST CONDITIONS                                                                                                                                      | MIN                    | ТҮР                     | MAX                     | UNIT                 |

|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|-------------------------|----------------------|

| Operating Input Voltage Range                                          | V <sub>INLS456</sub> (Input Voltage) to the LS4,5,6<br>EN_LSW_ILIM_COMPS=0                                                                           | 0.6                    |                         | VSYS                    | V                    |

| Output Voltage Range                                                   | V <sub>INLS456</sub> (Input Voltage) to the LS4,5,6<br>EN_LSW_ILIM_COMPS=0                                                                           | 0.6                    |                         | VSYS                    | V                    |

| Operating Input Voltage Range Cur-<br>rent limit enabled normal range  | V <sub>INLS456</sub> (Input Voltage) to the LS4,5,6<br>EN_LSW_ILIM_COMPS =1<br>EN_LOWVIN_ILIM_MODE = 0                                               | 0.8                    |                         | VSYS                    | V                    |

| Operating Input Voltage Range Cur-<br>rent limit enabled low vin range | V <sub>INLS456</sub> (Input Voltage) to the LS4,5,6<br>EN_LSW_ILIM_COMPS =1<br>EN_LOWVIN_ILIM_MODE = 1                                               | 0.6                    |                         | VSYS-0.7                | V                    |

| Maximum Output Current                                                 |                                                                                                                                                      | 100                    |                         |                         | mA                   |

| Current Limit voltage detection<br>threshold (VINLS456 – VOUTL456)     | $V_{OUTLS456} > 1.2V$<br>ILIM SET56[1:0] = 00<br>ILIM SET56[1:0] = 01<br>ILIM SET56[1:0] = 10<br>ILIM SET56[1:0] = 11                                | 35<br>75<br>125<br>175 | 50<br>100<br>150<br>200 | 65<br>125<br>175<br>225 | mV<br>mV<br>mV<br>mV |

| Load Switch Resistance<br>LSW4, LSW5 and LSW6                          | VINLS456 = 1.2V, I <sub>VINLS456</sub> = 50mA<br>VSYS=3.6V                                                                                           |                        | 250                     | 320                     | mΩ                   |

| Load Switch Resistance<br>Load Switch Mode for LDO3                    | VINL3 = 1.2V, I <sub>OUTL3</sub> = 50mA<br>VSYS=3.6V                                                                                                 |                        | 300                     | 380                     | mΩ                   |

| Soft-start slew rate                                                   | Output start from 0 to 1.2V<br>VSYS=3.6V, 10 – 90% measurement.                                                                                      |                        | 100                     |                         | μs                   |

| Current limit deglitch time                                            | Minimum time for current limit signal to be valid. (Note 1)                                                                                          | 10                     |                         |                         | μs                   |

| Output Discharge Resistance                                            | $VSYS = 3.6V, V_{OUTLS456} = 0.1V.$                                                                                                                  |                        |                         | 90                      | Ω                    |

| Startup Delay                                                          | Time from Enable to PG                                                                                                                               |                        |                         | 1000                    | μs                   |

| Iq1, Total Current Condition 1                                         | VSYS=3.6V, VIN=1.2V<br>I <sub>SYS</sub> +I <sub>VINLS456</sub> with no load current<br>EN_LSW_ILIM_COMPS =0<br>EN_LOWVIN_ILIM_MODE = x               |                        | 40                      |                         | nA                   |

| lq2, Total Current Condition 2                                         | VSYS=3.6V, VIN=1.2V<br>I <sub>SYS</sub> +I <sub>VINLS456</sub> with no load current<br>EN_LSW_ILIM_COMPS =1<br>EN_LOWVIN_ILIM_MODE = 0               |                        | 225                     |                         | nA                   |

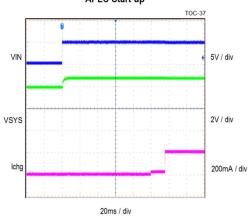

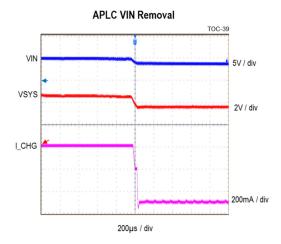

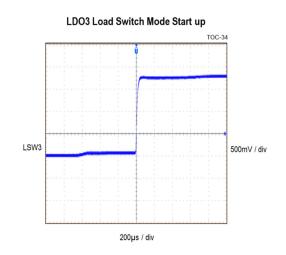

| lq3, Total Current Condition 3                                         | VSYS=3.6V, VIN=1.2V<br>I <sub>SYS</sub> +I <sub>VINLS456</sub> with no load current<br>EN_LSW_ILIM_COMPS =1<br>EN_LOWVIN_ILIM_MODE = 1               |                        | 225                     |                         | nA                   |