### ACT88321EVK1-101 User's Guide

### Description

This document describes the characteristic and operation of the Qorvo ACT88321EVK1-101 evaluation kit (EVK). It provides setup and operation instructions, schematic, layout, BOM, and test data. This EVK demonstrates the ACT88321VU101 Qorvo PMU power management IC. Other ACT88321VUxxx options can be evaluated on this EVK by replacing the IC and any other necessary components.

### Features

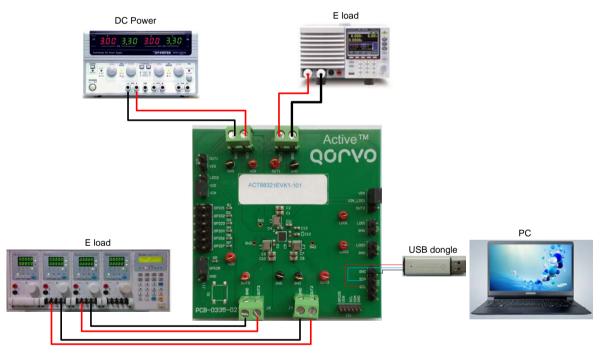

The EVK can be used as a standalone board if desired. However, to access the internal registers and to take full advantage of the IC's capability, the user must connect the EVK kit to a PC with Qorvo's USB-TO-I2C interface dongle and use the GUI software. The EVK provides full access to each converter's input and output voltage, as well as all the digital control signals. This gives the user the flexibility to configure the EVK to match their real-world system.

Note that the ACT88321EVK1-101 is specifically configured for the ACT88321VU101. This CMI does not use Push-Button.

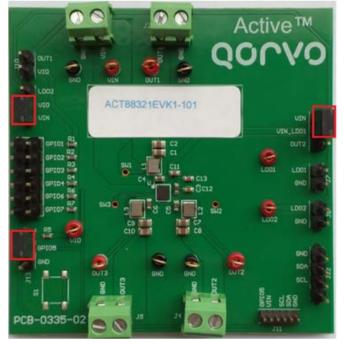

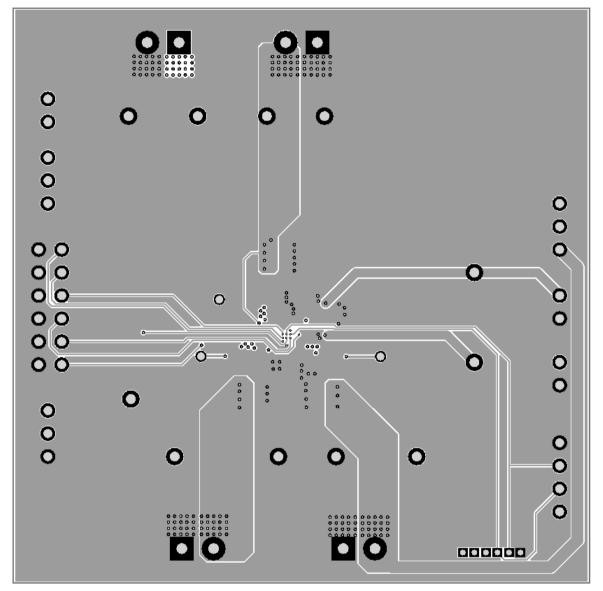

Figure 1 – EVK Picture

#### Setup

#### **Required Equipment**

ACT88321 EVK

USB-TO-I2C Dongle

Power supply – 3.3V @ 4A for full power operation

Oscilloscope - >100MHz, >2 channels

Loads - Electronic or resistive. 3A minimum current capability.

Digital Multi-meters (DMM)

Windows compatible computer with spare USB port.

### **EVK Setup**

Figure 2 – EVK Setup

### Hardware Setup

- 1. Decide which voltage will power VIO\_IN. Qorvo recommends powering VIO\_IN from the VIN input. Connect a shorting jumper between J9-2 and J9-3 header to power VIO\_IN from the VIN input voltage.

- 2. Connect a jumper between J3-1 and J3-2 header to power VIN\_LDO1 from VIN input voltage.

- 3. Connect a jumper between J13-1 and J13-2 to power GPIO5.

- 4. Connect DC source between J1-1 and J1-2 with 3.3V.

- 5. Connect an appropriate load to each power supply output.

- 6. Note that the typical setup is to apply the same 3.3V input voltage to all inputs. Using different input voltage sources requires careful consideration of startup sequencing.

# QOUND

Figure 3 – Shorting Jumper Settings

### **GUI Setup (optional)**

- 1. Refer to the end of this document for detailed instructions to install the ACT88321 GUI.

- 2. Connect the USB-TO-I2C dongle to the computer via a USB cable.

- 3. Connect the USB-TO-I2C dongle to the EVK J12 connector. Refer to Figure 4 to ensure the correct polarity of the connection. As a guide, use the "Active-Semi" logo on the top of the dongle so the black wire is connected toward the lower left corner of the Dongle.

Dongle Cable Connector (Black Wire Connected to GND of the J12 I2C Jumper on the ACT88321 EVK Board)

Figure 4 – USB-TO-I2C Dongle Connection

### **Recommended Operating Conditions**

The ACT88321EVK1-101 is designed for a 3.3V input voltage. The maximum operating voltage is determined by the IC's maximum input voltage rating. The minimum operating voltages are determined by the buck converters' minimum input voltage and by the LDOs' dropout voltages. Maximum currents are determined by the IC's CMI settings, which can be changed via I2C after startup.

#### **Table 1. Recommended Operating Conditions**

| PARAMETER                                               | VALUE                 | UNIT |

|---------------------------------------------------------|-----------------------|------|

| All I/O and Power pins except PGND1, PGND2, PGND3, AGND | -0.3 to 6             | V    |

| Grounds: Any PGND referenced to AGND                    | -0.3 to +0.3          | V    |

| SW_Bx to PGNDx                                          | -1 to VIN_Bx + 1      | V    |

| FB_Bx to PGNDx                                          | -0.3 to AVIN + 0.3    | V    |

| LDO2 to AGND                                            | -0.3 to AVINx + 0.3   | V    |

| LDO1 to AGND                                            | -0.3 to VIN_LDO + 0.3 | V    |

| Junction to Ambient Thermal Resistance, CSP             | 37                    | °C/W |

| Operating Junction Temperature                          | -40 to 150            | °C   |

| Storage Temperature                                     | -55 to 150            | °C   |

### **EVK Operation**

#### Turn-on

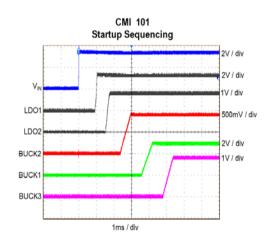

Apply the 3.3V input voltage. All outputs automatically turn on with the programmed startup sequence.

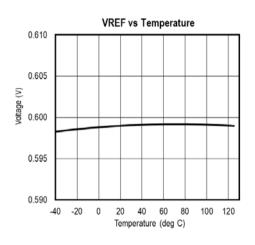

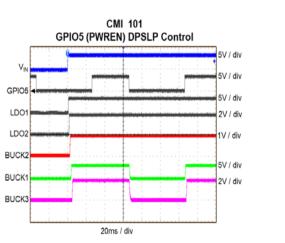

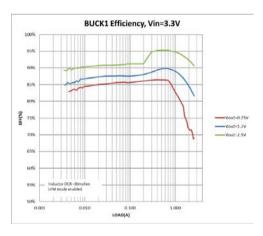

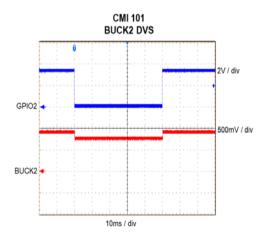

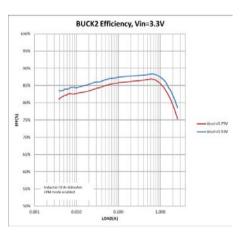

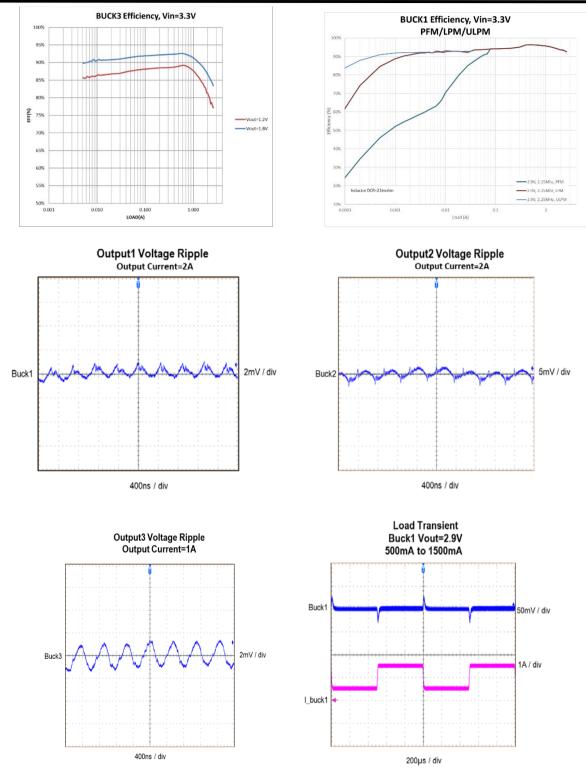

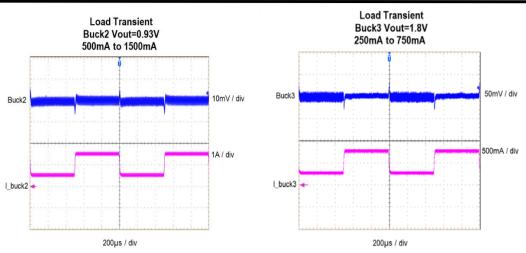

#### **Test Results**

### **UG142** Rev. 1.0, 24-Nov-2020

# QOUND

**UG142** Rev. 1.0, 24-Nov-2020

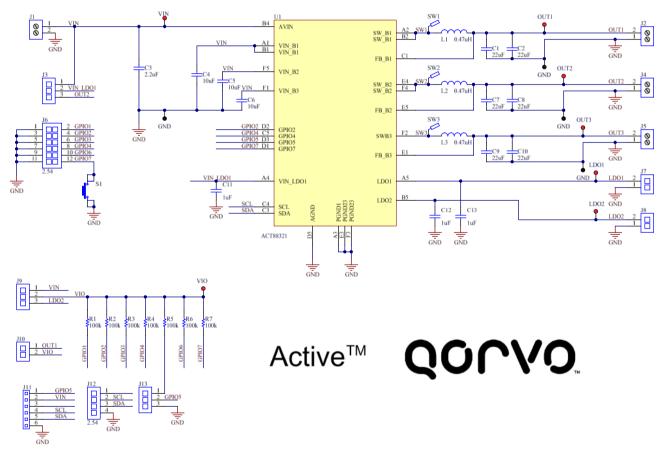

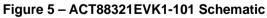

### Schematic

### **Bill of Materials**

Table 2 - BOM

| Item | Designator                                   | Quantity | Description                             | Package | Manufac-<br>turer   | PartNumber         |

|------|----------------------------------------------|----------|-----------------------------------------|---------|---------------------|--------------------|

| 1    | C1, C2, C7,<br>C8, C9, C10                   | 6        | Cap, Ceramic, 22uF, 16V, 20%,<br>X5R    | 0805    | std                 | std                |

| 2    | C3                                           | 1        | Cap, Ceramic,2.2uF, 16V, 20%,<br>X5R    | 0603    | std                 | std                |

| 3    | C4, C5, C6                                   | 3        | Cap, Ceramic, 10uF, 16V, 20%,<br>X5R    | 0603    | std                 | std                |

| 4    | C11, C12, C13                                | 3        | Cap, Ceramic, 1uF, 16V, 20%,<br>X5R     | 0603    | std                 | std                |

| 5    | J1, J2, J4, J5                               | 4        | CON, Screw Terminal, 3.50, 2P,<br>KF350 |         | Wurth<br>Elektronik | 691214110002       |

| 6    | J3, J9                                       | 2        | Header, Unshrouded, 2.54, Male, 3P      | CON3    | Wurth<br>Elektronik | 61300211121        |

| 7    | J6                                           | 1        | Header, Unshrouded, 2.54, Male, 7x2P    | CON7x2  | Wurth<br>Elektronik | 61301421121        |

| 8    | J7, J8, J10                                  | 3        | Header, Unshrouded, 2.54, Male, 2P      | CON2    | Wurth<br>Elektronik | 61300211121        |

| 9    | J11                                          | 1        | Header, Unshrouded, 1.27, Male, 6P      | CON6    | Digekey             | GRPB061VWVN-<br>RC |

| 10   | J12                                          | 1        | Header, Unshrouded, 2.54, Male, 4P      | CON4    | Wurth<br>Elektronik | 61300211121        |

| 11   | L1, L2, L3                                   | 3        | Inductor, 0.47uH                        | 2512    | Wurth<br>Elektronik | 744383240047       |

| 12   | R1, R2, R3,<br>R4, R5, R6,<br>R7             | 7        | Res, 100kΩ, 5%                          | 0603    | std                 | std                |

| 13   | S1                                           | 0        | Switch, TSW, TE-1437565-0               |         | N/A                 | std                |

| 14   | TP1, TP2,<br>TP3, TP5,<br>TP8, TP10,<br>TP11 | 7        | TEST POINT PC MINI .040"D<br>RED        |         | KeyStone            | 5000               |

| 15   | TP4, TP6,<br>TP7, TP9                        | 4        | TEST POINT PC MINI .040"D<br>BLK        |         | KeyStone            | 5001               |

| 16   | U1                                           | 1        | IC, ACT88321                            | CSP     | Qorvo               | ACT88321VU101      |

**UG142** Rev. 1.0, 24-Nov-2020

### Layout

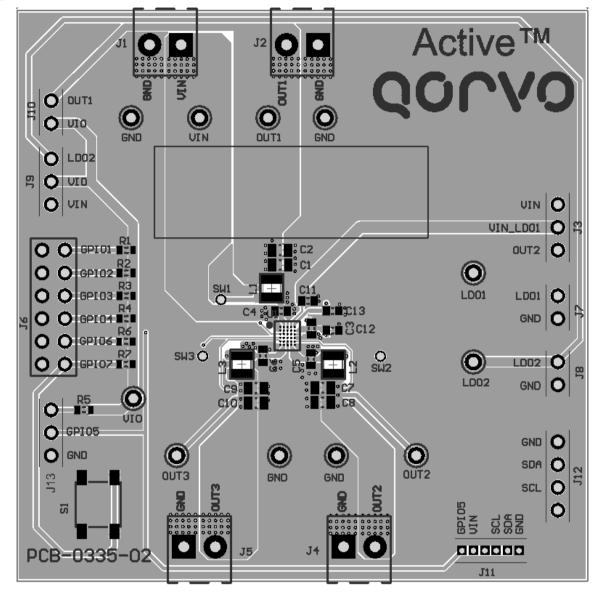

Figure 6 – Layout Top Assembly

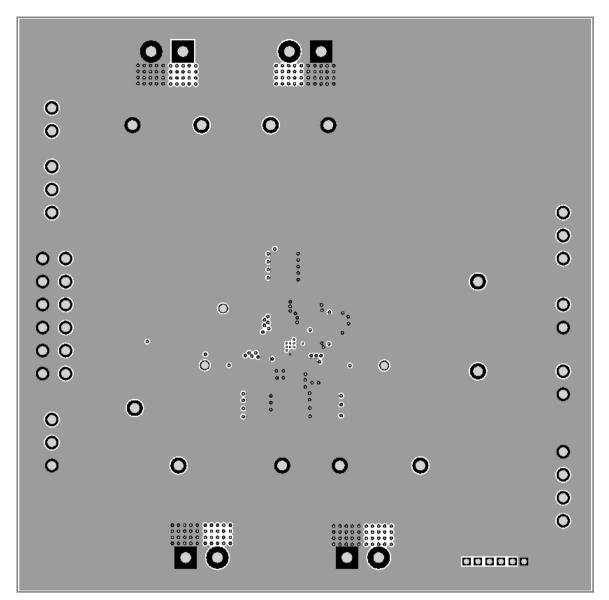

Figure 7 – Layout Layer 2

0

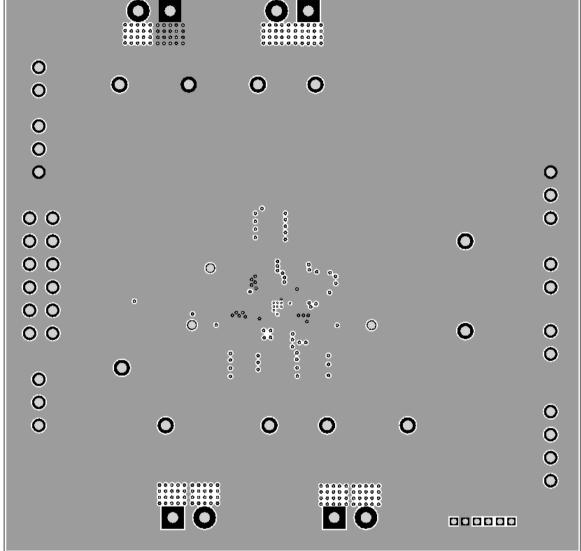

Figure 8 – Layout Layer 3

# QONO

# QOUVO

Figure 9 – Layout Bottom Layer

# QOUVO

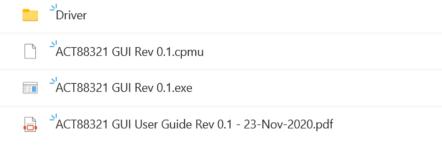

#### **GUI Installation**

- 1. Download the GUI files from Qorvo's website and save them on your computer.

- 2. Plug the USB-TO-I2C dongle into a free USB port.

- 3. Double click on the ACT88321 GUI.exe to start the ACT88321 GUI.

Figure 10 – Dongle Driver

#### **GUI Overview**

The GUI has 2 basic function buttons allocated in top-left of the Tool Bar which are Read and Write I2C. The GUI contains 2 setting modes: Basic Mode and Advanced Mode. In Basic Mode screen it displays basic user programmable configuration options are programmed using the drop-down boxes or check boxes. Advanced Mode contains the button text for changing setting for every single bit.

#### **Basic Mode**

The following figure shows the GUI in basic mode. This mode allows the user to easily change one or more IC settings.

| ACT88321 GUI REV | ? 础                       |                |           | ACT               | 88321         |       |          |      |       |      |      | -      |      | •    |   |

|------------------|---------------------------|----------------|-----------|-------------------|---------------|-------|----------|------|-------|------|------|--------|------|------|---|

| Basic Mode       | SYSTEM CONTROL            |                |           | REGULATORS        |               |       |          |      |       |      |      |        |      |      |   |

| Advanced Mode    | 12C Address               | 0x2            | h         |                   | BU            | CK1   | BUCK2    |      | BUCK3 |      | LDO1 | 1      | LDO2 |      |   |

|                  | Tile Trigger Interrupt    | MST            | B         | ON BR             |               |       |          |      |       |      |      |        |      |      |   |

|                  |                           |                |           | SLEEP_EN Bt       |               |       |          |      |       |      |      |        |      |      |   |

|                  |                           | VIN_POK_OV (V) | V (V) 3.5 | ~                 | DPSLP_EN Bit  |       |          |      |       |      |      |        |      |      |   |

|                  | VSYSMON (V)               | VSYSMON (V)    | 2.7       | ~                 | VSET0 (V)     | 0.60  | 0 ~ 0    | 0.50 | ~     | 0.50 | ~    | 0.60   | ×    | 0.60 | ~ |

|                  | VSYSWARN (V)              | 2.7            | ~         | VSET1 (V)         | 0.60          |       | 0.50     | _    | 0.50  | _    |      |        |      |      |   |

|                  | nRESET Time (ms)          | 0.5            | ~         |                   |               |       |          | ~    |       | ~    |      |        |      |      |   |

|                  |                           |                |           | Current Limit (A) | 3.7           | 5 ~   | 3.75     | ~    | 2.0   | ~    | 0.35 | ~      | 0.35 | ~    |   |

|                  | LDO1 Operation Mode       | Dead           | der.      | Soft Start Time ( | (us) 500      | ) v   | 50       | ~    | 50    | ×    | 160  | $\sim$ | 160  |      |   |

|                  |                           |                |           | Regulator         | DVS Rate (mV/ | us)   |          | 22.5 | i i   |      |      |        |      |      |   |

|                  | LDO2 Operation Mode       | Regul          | ator      | Startup Delay (m  | ns) 0         | ×     | 0        | ~    | 0     | ~    | 0    | ~      | 0    | ~    |   |

|                  |                           |                |           | Tum-off Delay (r  | ns) 0         | ~     | 0        | -    | 0     | ~    | 0    | ~      | 0    | ~    |   |

|                  |                           |                |           |                   | _             | _     | 1.5      | _    |       | _    | 0    |        |      | ~    |   |

|                  |                           |                |           | Frequency (Minz   | ) 2           | 2.25  |          | 9    | 1.5   |      |      |        |      |      |   |

|                  |                           |                |           |                   |               |       |          |      |       |      |      |        |      |      |   |

|                  | GPIO <sub>S</sub> SETTING | PIO2           | G         | PIO4 GPI          | 05            | GPIO  | 7        |      |       |      |      |        |      |      |   |

|                  | Operation Mode            | NA             |           | NA                | NA            | PB Ac | tive Low |      |       |      |      |        |      |      |   |

|                  | Delay Time (ms)           | 0              | 7         |                   | 0 ~           | 0     |          |      |       |      |      |        |      |      |   |

|                  |                           |                |           |                   |               | _     |          |      |       |      |      |        |      |      |   |

| OLAO             | Degitch Time (ms)         | 0              | ¥ 1       | 0 4               | 0 ~           | 0     | ~        |      |       |      |      |        |      |      |   |

Figure 11 – GUI Basic Mode

# QOUVO

#### **Advanced Mode**

Click the "Advanced Mode" button in the left of the GUI screen to see all available user programmable options. With Advanced Mode, additional user programmable features can be selected using the button text. In the left side of the Advanced Mode Screen, click on the Tiles Selector to display the register to view or change. Then change a register one bit at a time by clicking on the desired bit. The value of the bit is display right next to the bit-name button.

Note that the right side of the screen contains a scroll down button to scroll down to additional registers since the Tile Screen can only display up to 8 bytes at once.

| / 🗌 🐗 🕯       | iq= ((            | ? 🖆            |   | AC T8832        | 21           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |              |   |

|---------------|-------------------|----------------|---|-----------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|---|

| Basic Mode    | Bits              | Address 0x00   |   | Address 0x01    |              | Address 0x02                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | Address 0x03 |   |

| Advanced Mode | 7                 | ROM STAT       | 0 | ROM INT MASK    | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | RFU          | 0 |

| System        | 6                 | WD TIMER ALERT | 0 | WD_ALERT_MASK   | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | GPIO7_STAT   | 0 |

| Buck1         | 5                 | TWARN          | 0 | TMASK           | 0            | VSYSWARN_RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 | REU          | 0 |

| Buck2         | 4                 |                |   |                 |              | And the second state of th |   | 1162218341   |   |

| Buck3         | -                 | VSYS_STAT      | 0 | VSYS_MASK       | 0            | VSYSDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 | GPIO5_STAT   | 0 |

| LDO12         | 3                 | VIN_POK_OV     | 0 | VIN_POK_OV_MASK | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | GPIO4_STAT   | 0 |

|               | 2                 | RFU            | 0 | RFU             | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | RFU          | 0 |

|               | 1                 | VSYSWARN       | 0 | VSYSWARN_MASK   | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | GPIO2_STAT   | 0 |

|               | 0                 | RFU            | 0 | RFU             | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | RFU          | ( |

|               | Bits Address 0x04 |                |   | Address 0x05    | Address 0x06 | Address 0x07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |              |   |

|               | 7 [               | RFU            | 0 | RFU             | 0            | INTADR[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | MR           | 0 |

|               | 6                 | GPIO7_Toggled  | 0 | GPIO7_MASK      | 0            | INTADR[6]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | SLEEP        | ( |

|               | 5                 | RFU            | 0 | RFU             | 0            | INTADR[5]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | RFU          | ( |

|               | 4                 | GPIO5_Toggled  | 0 | GPIO5_MASK      | 0            | INTADR[4]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | DPSLP        |   |

|               | 3                 | GPIO4_Toggled  | 0 | GPIO4_MASK      | 0            | INTADR[3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | RFU          |   |

|               | 2                 | RFU            | 0 | RFU             | 0            | INTADR[2]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | POWER_OFF    |   |

|               | 1                 | GPIO2_Toggled  | 0 | GPIO2_MASK      | 0            | INTADR[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | WDPCEN       | ( |

|               | 0                 | RFU            | 0 | RFU             | 0            | INTADR[0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | WDSREN       |   |

|               | Bits              | Address 0x09   |   | Address 0x0A    |              | Address 0x0B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | Address 0x0C |   |

| 0010          | 7                 | TRST_DLY[2]    | 0 | RFU             | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | 105_DLY[1]   | 0 |

| 01.40         | 6                 | TRST_DLY[1]    | 0 | RFU             | 0            | RFU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | 105_DLY[0]   | 0 |

Figure 12 – GUI Advanced Mode

#### **Button Descriptions**

**Read:** Clicking on this button reads the ACT88321 registers and displays them in the GUI. Note that this reads all registers. Qorvo recommend spreading registers each time the ACT88321 powers-up to acquire the initial register settings. Qorvo also recommends reading registers after making changes to them. Immediately reading the registers after a write confirms the changes were properly stored.

| / 🗂 🔜 🔌         | ▶ ? 础                                    |                        | ACT88                | 321   |   |        |        |      |        |      | •4     |  |

|-----------------|------------------------------------------|------------------------|----------------------|-------|---|--------|--------|------|--------|------|--------|--|

| Basic Mode Read | SYSTEM CONTROL                           |                        | REGULATORS S         |       |   |        | -      | 1001 |        |      |        |  |

| Advanced Mode   | 12C Address                              | 0x25h                  | 0110                 | BUCK1 |   | BUCK2  | BUCK3  | LDO1 |        | LDO2 |        |  |

|                 | Tile Trigger Interrupt<br>VIN_POK_OV (V) | Tile Trigger Interrupt | MSTR                 | ON Br |   |        |        |      |        |      |        |  |

|                 |                                          | 3.5 ~                  | SLEEP_EN BR          |       |   |        |        |      |        |      |        |  |

|                 |                                          |                        | DPSLP_EN BE          |       |   |        |        |      |        |      |        |  |

|                 | VSYSMON (V)                              | 2.7 🗸                  | VSET0 (V)            | 0.600 | ~ | 0.50 ~ | 0.50 ~ | 0.60 | ~      | 0.60 | V      |  |

|                 | VSYSWARN (V)                             | 2.7 v                  |                      |       | - |        |        | 1    |        |      |        |  |

|                 | nRESET Time (ms)                         | 0.5 ~                  | VSET1 (V)            | 0.600 | ~ | 0.50 ~ | 0.50 ~ | 1    |        |      |        |  |

|                 |                                          |                        | Current Limit (A)    | 3.75  | × | 3.75 ~ | 2.0 ~  | 0.35 | ~      | 0.35 | ~      |  |

|                 |                                          |                        | Soft Start Time (us) | 500   | ~ | 50 v   | 50 v   | 160  | ~      | 160  |        |  |

|                 | LDO1 Operation Mode                      | Regulator              | DVS Rate (mV/us)     |       |   | 22.5   |        |      | _      |      |        |  |

|                 | LDO2 Operation Mode                      | Regulator              | DV3 Hate (mV/Us)     |       |   | 22.5   |        |      |        |      |        |  |

|                 |                                          |                        | Startup Delay (ms)   | 0     | ¥ | 0 ~    | 0 ~    | 0    | $\sim$ | 0    | $\sim$ |  |

|                 |                                          |                        | Tum-off Delay (ms)   | 0     | ~ | 0 ~    | 0 ~    | 0    | ~      | 0    | ~      |  |

|                 |                                          |                        | Frequency (Mhz)      | 2.25  | 1 | 1.5    | 1.5    | 1    |        |      |        |  |

Figure 13 – Read Button