# Quad-Channel, Software Configurable Input/Output

Data Sheet AD74412R

#### **FEATURES**

Quad-channel software configurable input/output circuit Screw terminals protected to  $\pm 40\,\text{V}$

Line protectors to block power from the screw terminals to supplies

Six configurable modes

Voltage input

**Current input**

Voltage output

**Current output**

**Digital input**

**RTD** measurement

Internal 16-bit,  $\Sigma$ - $\Delta$  ADC with optional 50 Hz and 60 Hz rejection

13-bit monotonic DACs

Charge pump for true zero voltage output

Internal temperature sensor, 5°C accuracy

On-chip diagnostics including open circuit and short-circuit detection

**Robust architecture**

SP

Temperature range: -40°C to +85°C

64-lead LFCSP

#### **APPLICATIONS**

**Building control systems**

**Process control**

**Industrial automation**

#### **GENERAL DESCRIPTION**

The AD74412R is a quad-channel software configurable input/output solution for building and process control applications. The AD74412R contains functionality for analog output, analog input, digital input, and resistance temperature detector (RTD) measurements integrated into a single chip solution with an interface compatible with the serial port interface (SPI).

The device features a 16-bit,  $\Sigma$ - $\Delta$  analog-to-digital converter (ADC) and four configurable, 13-bit digital-to-analog converters (DACs) to provide four configurable input/output channels and a suite of diagnostic functions.

There are several modes related to the AD74412R. These modes are voltage output, current output, voltage input, externally powered current input, loop powered current input, external RTD measurement, digital input logic, and loop powered digital input.

The AD74412R contains a high accuracy 2.5 V internal reference to drive the DACs and the ADC.

#### COMPANION PRODUCTS

**External Reference: ADR4525**

Power: ADP1720

#### **PRODUCT HIGHLIGHTS**

- 1. Quad-Channel, Software Configurable Channels.

- 2. Built In Diagnostics and Alert Features.

- 3. Robust Architecture. Surge tested to ±1 kV, per the IEC61000-4-5 standard, on the input/output terminals with unshielded cables.

## **AD74412R**

## **TABLE OF CONTENTS**

| Features                                    | 1    | ADC Functionality                                   | 40 |

|---------------------------------------------|------|-----------------------------------------------------|----|

| Applications                                | 1    | Diagnostics                                         | 44 |

| General Description                         | 1    | DACs                                                | 45 |

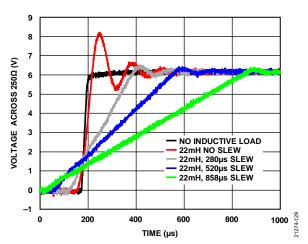

| Companion Products                          | 1    | Driving Inductive Loads                             | 46 |

| Product Highlights                          | 1    | Reset Function                                      | 46 |

| Revision History                            | 3    | Thermal Alert and Thermal Reset                     | 46 |

| Functional Block Diagram                    | 4    | Faults and Alerts                                   | 46 |

| Specifications                              | 5    | Power Supply Monitors                               | 46 |

| Voltage Output                              | 5    | GPO_x Pins                                          | 47 |

| Current Output                              | 6    | SPI Interface and Diagnostics                       | 47 |

| Voltage Input                               | 7    | Board Design and Layout Considerations              | 50 |

| Current Input Externally Powered            | 8    | Applications Information                            | 51 |

| Current Input Loop Powered                  | 9    | Register Map                                        | 52 |

| RTD Measurement                             | 9    | NOP Register                                        | 53 |

| Digital Input Logic                         | . 10 | Function Setup Register per Channel                 | 53 |

| Digital Input Loop Powered                  | . 10 | ADC Configuration Register per Channel              | 53 |

| ADC Specifications                          | . 11 | Digital Input Configuration Register per Channel    | 54 |

| General Specifications                      | . 12 | GPO Parallel Data Register                          | 55 |

| Timing Characteristics                      | . 14 | GPO Configuration Register per Channel              | 55 |

| Absolute Maximum Ratings                    | . 16 | Output Configuration Register per Channel           | 56 |

| Thermal Resistance                          | . 16 | DAC Code Register per Channel                       | 56 |

| ESD Caution                                 | 16   | DAC Clear Code Register per Channel                 | 56 |

| Pin Configuration and Function Descriptions | . 17 | DAC Active Code Register per Channel                | 57 |

| Typical Performance Characteristics         | . 20 | Digital Input Threshold Register                    | 57 |

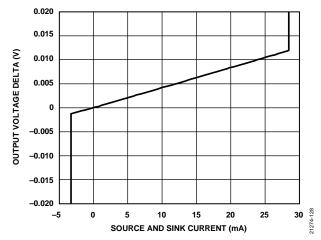

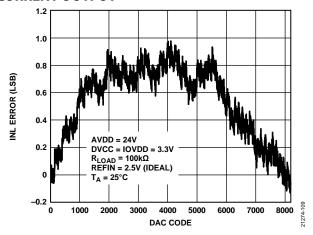

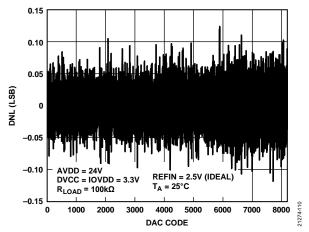

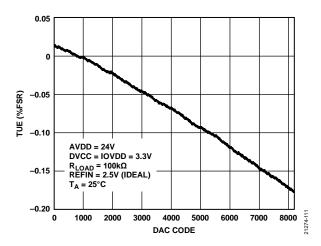

| Voltage Output                              | 20   | ADC Conversion Control Register                     | 57 |

| Current Output                              | . 22 | Diagnostics Select Register                         | 58 |

| Reference                                   | 24   | Digital Output Level Register                       | 59 |

| ADC                                         | 25   | ADC Conversion Results Register per Channel         | 60 |

| Supplies                                    | 26   | Diagnostic Results Registers per Diagnostic Channel | 60 |

| Theory of Operation                         | 27   | Alert Status Register                               | 60 |

| Robust Architecture                         | 27   | Live Status Register                                | 62 |

| Serial Interface                            | 27   | Alert Mask Register                                 | 63 |

| DAC Architecture                            | 27   | Readback Select Register                            | 63 |

| ADC Overview                                | 28   | 80 SPS ADC Conversion Control Register              | 64 |

| Reference                                   | 28   | Thermal Reset Enable Register                       | 64 |

| Power-On State of the AD74412R              | 28   | Command Register                                    | 65 |

| Device Functions                            | 28   | Scratch or Spare Register                           | 65 |

| Digital Input, Loop Powered Mode            | 38   | Silicon Revision Register                           | 65 |

| Getting Started                             | 39   | Outline Dimensions                                  | 66 |

| Using Channel Functions                     | . 39 | Ordering Guide                                      | 66 |

## **REVISION HISTORY**

| 9/2019—Rev. 0 to Rev. A          |    |

|----------------------------------|----|

| Change to Figure 6 and Figure 8  | 20 |

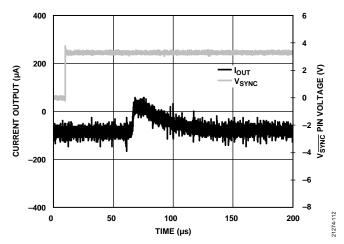

| Changes to Figure 18             | 22 |

| Changes to Table 19 and Table 20 | 43 |

9/2019—Revision 0: Initial Version

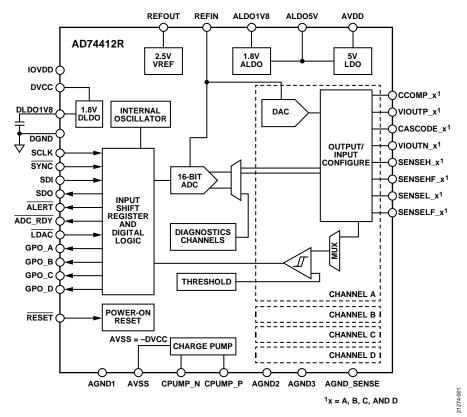

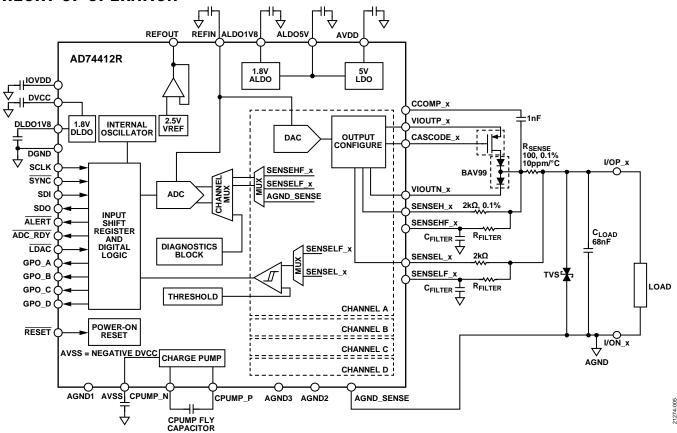

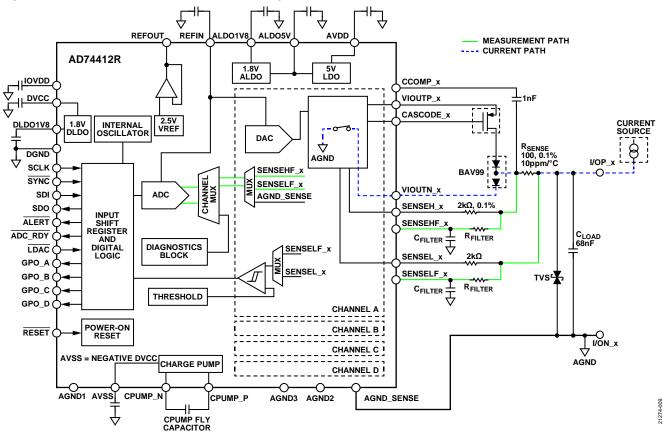

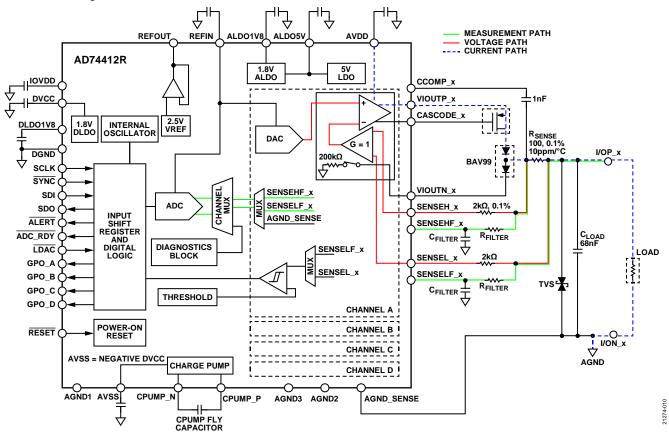

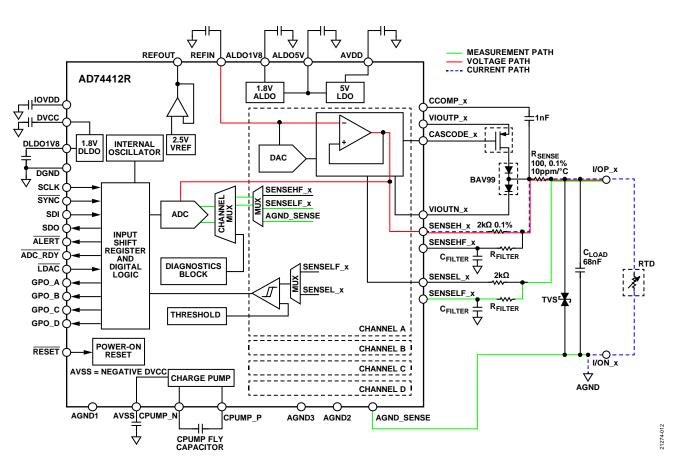

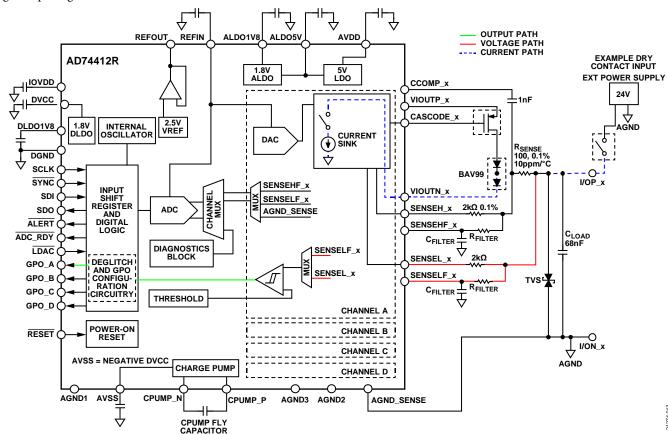

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **SPECIFICATIONS**

#### **VOLTAGE OUTPUT**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ , unless otherwise noted. Resistor load ( $R_{LOAD}$ ) = 100 k $\Omega$  and capacitor load ( $R_{LOAD}$ ) = 68 nF per recommended configuration.

Table 1.

| Parameter                              | Min   | Тур  | Max   | Unit    | Test Conditions/Comments                                                                                                                                                        |

|----------------------------------------|-------|------|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOLTAGE OUTPUT                         |       |      |       |         |                                                                                                                                                                                 |

| Resolution                             | 13    |      |       | Bits    |                                                                                                                                                                                 |

| Output Range                           | 0     |      | 11    | V       |                                                                                                                                                                                 |

| ACCURACY                               |       |      |       |         |                                                                                                                                                                                 |

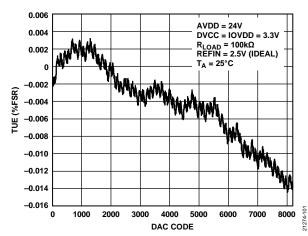

| Total Unadjusted Error (TUE)           | -0.4  |      | +0.4  | %FSR    | Internal reference                                                                                                                                                              |

|                                        | -0.35 |      | +0.35 | %FSR    | External reference                                                                                                                                                              |

| TUE at 25°C                            | -0.2  |      | +0.2  | %FSR    | Internal reference                                                                                                                                                              |

|                                        | -15   |      | +0.15 | %FSR    | External reference                                                                                                                                                              |

| TUE Drift vs. Time <sup>1</sup>        |       | ±400 |       | ppm FSR | Internal reference, drift after 1000 hours at T <sub>A</sub> = 85°C                                                                                                             |

|                                        |       | ±100 |       | ppm FSR | External reference, drift after 1000 hours at $T_A = 85^{\circ}$ C                                                                                                              |

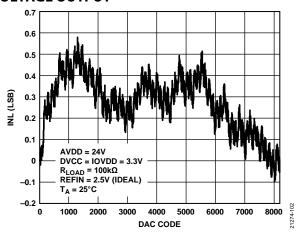

| Integral Nonlinearity (INL)            | -4    |      | +4    | LSB     |                                                                                                                                                                                 |

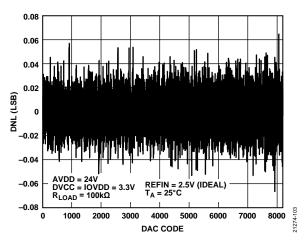

| Differential Nonlinearity (DNL)        | -1    |      | +1    | LSB     | Guaranteed monotonic                                                                                                                                                            |

| Offset Error                           | -8    |      | +8    | mV      |                                                                                                                                                                                 |

| Gain Error                             | -0.4  |      | +0.4  | %FSR    | Internal reference                                                                                                                                                              |

|                                        | -0.25 |      | +0.25 | %FSR    | External reference                                                                                                                                                              |

| OUTPUT CHARACTERISTICS                 |       |      |       |         |                                                                                                                                                                                 |

| Load                                   | 500   | 100k |       | Ω       |                                                                                                                                                                                 |

| Headroom (500 $\Omega$ Load)           | 4     |      |       | V       | Minimum voltage difference required between AVDD and the input/output positive (I/OP_x where x is the channel number) screw terminal to provide 11 V across a 500 $\Omega$ load |

| Short-Circuit Current (Sourcing)       | 25    | 29   | 32    | mA      | Per channel, lower limit bit = 0 (default)                                                                                                                                      |

| -                                      | 5.5   | 7    | 9     | mA      | Per channel, lower limit bit = 1                                                                                                                                                |

| Short-Circuit Current (Sinking)        | 3.0   | 3.8  | 4.5   | mA      |                                                                                                                                                                                 |

| Maximum Capacitive Load                |       |      | 2     | μF      |                                                                                                                                                                                 |

| DC Output Impedance                    |       | 0.12 |       | Ω       |                                                                                                                                                                                 |

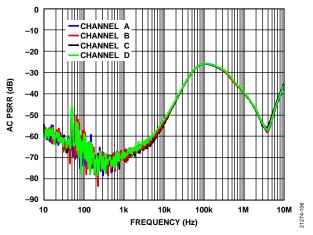

| DC Power Supply Rejection Ratio (PSRR) |       | 80   |       | dB      |                                                                                                                                                                                 |

| DYNAMIC PERFORMANCE <sup>1</sup>       |       |      |       |         |                                                                                                                                                                                 |

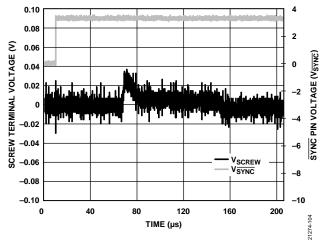

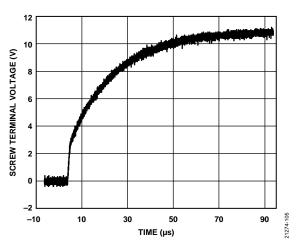

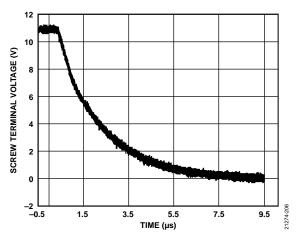

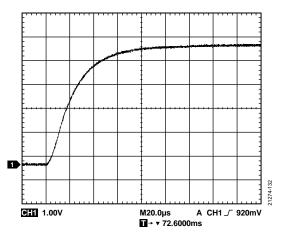

| Output Voltage Settling Time           |       | 90   |       | μs      | 10 V step (0.5 V to 10.5 V or 10.5 V to 0.5 V) to ±0.05%FSR                                                                                                                     |

| Noise (Internal Reference)             |       |      |       |         | Measured at the I/OP_x screw terminal, 2.5 V output                                                                                                                             |

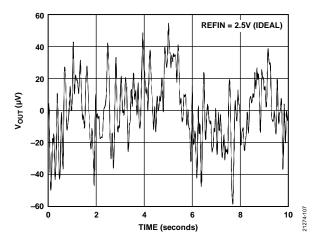

| Output Noise                           |       | 0.1  |       | LSB p-p | 0.1 Hz to 10 Hz bandwidth                                                                                                                                                       |

| Output Noise Spectral Density          |       | 2    |       | μV/√Hz  | Measured at 1 kHz                                                                                                                                                               |

| Noise (External Reference)             |       |      |       |         | Measured at the I/OP_x screw terminal, 2.5 V output                                                                                                                             |

| Output Noise                           |       | 0.07 |       | LSB p-p | 0.1 Hz to 10 Hz bandwidth                                                                                                                                                       |

| Output Noise Spectral Density          |       | 320  |       | nV/√Hz  | Measured at 1 kHz                                                                                                                                                               |

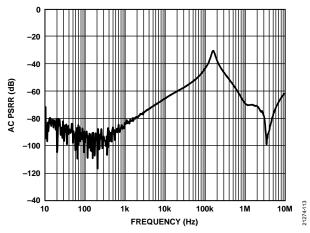

| AC PSRR                                |       | 65   |       | dB      | 200 mV at 1 kHz sine wave superimposed on the AVDD supply                                                                                                                       |

$<sup>^{\</sup>rm 1}\,\mbox{Guaranteed}$  by design and characterization.

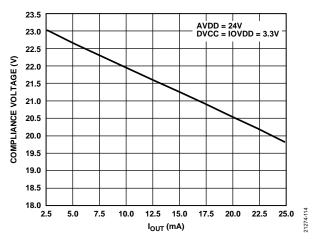

#### **CURRENT OUTPUT**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD= 1.7 V to 5.5 V, and all specifications at  $T_A$ =-40°C to +85°C, unless otherwise noted.  $R_{LOAD}$  = 250  $\Omega$ ,  $C_{LOAD}$  = 68 nF per recommended configuration, and the sense resistor ( $R_{SENSE}$ ) = 100  $\Omega$ , 0.1%, 10 ppm/°C.

Table 2.

| Parameter                        | Min   | Тур  | Max   | Unit    | Test Conditions/Comments                                                                       |

|----------------------------------|-------|------|-------|---------|------------------------------------------------------------------------------------------------|

| CURRENT OUTPUT                   |       |      |       |         |                                                                                                |

| Resolution                       | 13    |      |       | Bits    |                                                                                                |

| Output Range                     | 0     |      | 25    | mA      |                                                                                                |

| ACCURACY                         |       |      |       |         |                                                                                                |

| TUE <sup>1</sup>                 | -0.55 |      | +0.55 | %FSR    | Internal reference                                                                             |

|                                  | -0.45 |      | +0.45 | %FSR    | External reference                                                                             |

| TUE at 25°C                      | -0.35 |      | +0.35 | %FSR    | Internal reference                                                                             |

|                                  | -0.2  |      | +0.2  | %FSR    | External reference                                                                             |

| TUE Drift vs. Time <sup>2</sup>  |       | 500  |       | ppm FSR | Internal reference, drift after 1000 hours at $T_A = 85^{\circ}C$                              |

|                                  |       | 300  |       | ppm FSR | External reference, drift after 1000 hours at $T_A = 85^{\circ}C$                              |

| INL                              | -4    |      | +4    | LSB     | From zero-scale to full-scale                                                                  |

| DNL                              | -1    |      | +1    | LSB     | Guaranteed monotonic                                                                           |

| Offset Error                     | -37.5 | +5.0 | +37.5 | μΑ      |                                                                                                |

| Gain Error <sup>1</sup>          | -0.4  |      | +0.4  | %FSR    | Internal reference                                                                             |

|                                  | -0.3  |      | +0.3  | %FSR    | External reference                                                                             |

| OUTPUT CHARACTERISTICS           |       |      |       |         |                                                                                                |

| Headroom                         | 5     |      |       | V       | Minimum voltage difference required between AVDD and the I/OP_x screw terminal to source 25 mA |

| Open Circuit Voltage             |       | AVDD |       | V       |                                                                                                |

| Output Impedance                 | 1.5   | 4    |       | ΜΩ      |                                                                                                |

| DC PSRR                          |       | 200  |       | nA/V    | PSRR measured with a change in AVDD                                                            |

| DYNAMIC PERFORMANCE <sup>2</sup> |       |      |       |         |                                                                                                |

| Output Current Settling Time     |       | 230  |       | μs      | 25 mA step up or down, time to settle within a window of ±100 μA of final current              |

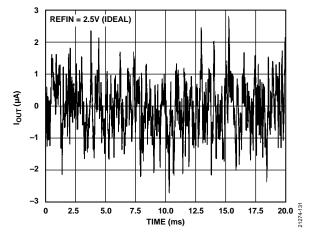

| Noise (Internal Reference)       |       |      |       |         | Measured at the I/OP_x screw terminal with 250 $\Omega$ load, 12.5 mA output                   |

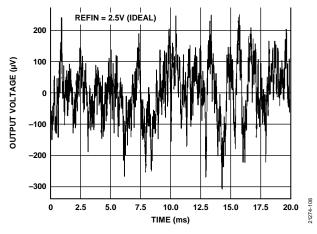

| Output Noise                     |       | 0.2  |       | LSB p-p | 0.1 Hz to 10 Hz bandwidth                                                                      |

| Output Noise Spectral Density    |       | 12   |       | nA/√Hz  | Measured at 1 kHz                                                                              |

| Noise (External Reference)       |       |      |       |         | Measured at the I/OP_x screw terminal with 250 $\Omega$ load, 12.5 mA output                   |

| Output Noise                     |       | 0.15 |       | LSB p-p | 0.1 Hz to 10 Hz bandwidth                                                                      |

| Output Noise Spectral Density    |       | 2    |       | nA/√Hz  | Measured at 1 kHz, 12.5 mA output                                                              |

| AC PSRR                          |       | 80   |       | dB      | Voltage on the supply at 1 kHz to the voltage across the 250 $\Omega$ .                        |

$<sup>^{\</sup>rm 1}\,R_{\text{SENSE}}$  accuracy directly impacts the TUE and gain error.

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and characterization.

#### **VOLTAGE INPUT**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.  $C_{LOAD} = 68$  nF per recommended configuration.

Table 3.

| Parameter                          | Min  | Тур  | Max  | Unit    | Test Conditions/Comments                                                                                                                                                                          |

|------------------------------------|------|------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOLTAGE INPUT                      |      |      |      |         |                                                                                                                                                                                                   |

| Input Resolution                   | 16   |      |      | Bits    |                                                                                                                                                                                                   |

| Input Range                        | 0    |      | 10   | V       |                                                                                                                                                                                                   |

| ACCURACY                           |      |      |      |         |                                                                                                                                                                                                   |

| TUE                                | -0.4 |      | +0.4 | %FSR    | Internal reference                                                                                                                                                                                |

|                                    | -0.2 |      | +0.2 | %FSR    | External reference                                                                                                                                                                                |

| TUE at 25°C                        | -0.3 |      | +0.3 | %FSR    | Internal reference                                                                                                                                                                                |

|                                    | -0.1 |      | +0.1 | %FSR    | External reference                                                                                                                                                                                |

| TUE Drift vs. Time <sup>1</sup>    |      | 500  |      | ppm FSR | Internal reference, drift after 1000 hours, T <sub>A</sub> = 85°C                                                                                                                                 |

|                                    |      | 500  |      | ppm FSR | External reference, drift after 1000 hours, T <sub>A</sub> = 85°C                                                                                                                                 |

| INL                                | -5   | ±2   | +5   | LSB     |                                                                                                                                                                                                   |

| Gain Error                         |      | 2000 |      | ppm FSR | Internal reference                                                                                                                                                                                |

| Offset Error                       |      | ±2   |      | LSB     |                                                                                                                                                                                                   |

| OTHER INPUT SPECIFICATIONS         |      |      |      |         |                                                                                                                                                                                                   |

| DC PSRR <sup>1</sup>               |      | 10   |      | μV/V    |                                                                                                                                                                                                   |

| Normal Mode Rejection <sup>1</sup> |      | 75   |      | dB      | 50 Hz ± 1 Hz and 60 Hz ± 1 Hz                                                                                                                                                                     |

| Input Bias Current at 25°C         | -100 |      | +100 | nA      | As seen from the I/OP_x screw terminal, ADC is either idle or converting; 200 k $\Omega$ to GND is disabled (CH_200K_TO_GND bit = 0), does not include transient voltage suppressor (TVS) leakage |

| Input Resistance                   | 175  | 195  | 215  | kΩ      | 200 kΩ to GND enabled                                                                                                                                                                             |

$<sup>^{\</sup>mbox{\tiny 1}}$  Guaranteed by design and characterization.

#### **CURRENT INPUT EXTERNALLY POWERED**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A = -40$  °C to +85 °C, unless otherwise noted.  $C_{LOAD} = 68$  nF per recommended configuration. AGND –  $0.5~V < I/OP_x$  screw terminal voltage < AVDD - 0.2~V, and  $R_{SENSE} = 100~\Omega$ , 0.1%,  $10~ppm/^{\circ}C$ .

Table 4.

| Parameter                          | Min   | Тур  | Max   | Unit    | Test Conditions/Comments                                            |

|------------------------------------|-------|------|-------|---------|---------------------------------------------------------------------|

| CURRENT INPUT                      |       |      |       |         |                                                                     |

| Input Resolution                   | 16    |      |       | Bits    |                                                                     |

| Input Range                        | 0     |      | 25    | mA      | Sensed across the external 100 $\Omega$ resistor                    |

| Short-Circuit Current Limit        | 25    |      | 35    | mA      | Nonprogrammable                                                     |

| ACCURACY                           |       |      |       |         |                                                                     |

| TUE <sup>1</sup>                   | -0.5  |      | +0.5  | %FSR    | Internal reference, 0.16% contribution from R <sub>SENSE</sub>      |

|                                    | -0.36 |      | +0.36 | %FSR    | External reference, 0.16% contribution from R <sub>SENSE</sub>      |

| TUE at 25°C                        | -0.34 |      | +0.34 | %FSR    | Internal reference                                                  |

|                                    | -0.2  |      | +0.2  | %FSR    | External reference                                                  |

| TUE Drift vs. Time <sup>1, 2</sup> |       | 700  |       | ppm FSR | Internal reference, drift after 1000 hours, T <sub>A</sub> = 85°C   |

|                                    |       | 600  |       | ppm FSR | External reference, drift after 1000 hours, T <sub>A</sub> = 85°C   |

| INL                                | -5    | +2   | +5    | LSB     |                                                                     |

| Gain Error                         |       | 2000 |       | ppm FSR |                                                                     |

| Offset Error                       |       | ±2   |       | LSB     |                                                                     |

| OTHER INPUT SPECIFICATIONS         |       |      |       |         |                                                                     |

| DC PSRR <sup>2</sup>               |       | 150  |       | nA/V    |                                                                     |

| Input Impedance                    |       | 200  |       | Ω       | Including 100 Ω R <sub>SENSE</sub>                                  |

| Compliance                         | 6.3   |      |       | V       | Minimum voltage required at the I/OP_x screw terminal to sink 25 mA |

$<sup>^1</sup>$  R\_{SENSE} accuracy directly impacts the TUE and gain error.  $^2$  Guaranteed by design and characterization; not production tested.

#### **CURRENT INPUT LOOP POWERED**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A$ =-40°C to +85°C, unless otherwise noted.  $C_{LOAD}$  = 68 nF per recommended configuration, AGND - 0.5 V < I/OP\_x screw terminals voltage < AVDD - 0.2 V, and  $R_{SENSE}$  = 100  $\Omega$ , 0.1%, 10 ppm/°C.

Table 5.

| Parameter                          | Min   | Тур  | Max   | Unit    | Test Conditions/Comments                                                                       |

|------------------------------------|-------|------|-------|---------|------------------------------------------------------------------------------------------------|

| CURRENT INPUTS                     |       |      |       |         |                                                                                                |

| Input Resolution                   | 16    |      |       | Bits    |                                                                                                |

| Input Range                        | 0     |      | 25    | mA      | Sensed across external $100 \Omega$ resistor                                                   |

| Programmable Current Limit         | 0.5   |      | 24.5  | mA      | Typical programmable current limit, current input loop powered enabled, 13-bit resolution      |

| ACCURACY                           |       |      |       |         |                                                                                                |

| TUE <sup>1</sup>                   | -0.5  |      | +0.5  | %FSR    | Internal reference, 0.16% contribution from R <sub>SENSE</sub>                                 |

|                                    | -0.36 |      | +0.36 | %FSR    | External reference, 0.16% contribution from R <sub>SENSE</sub>                                 |

| TUE at 25°C                        | -0.34 |      | +0.34 | %FSR    | Internal reference                                                                             |

|                                    | -0.2  |      | +0.2  | %FSR    | External reference                                                                             |

| TUE Drift vs. Time <sup>1, 2</sup> |       | 700  |       | ppm FSR | Internal reference, drift after 1000 hours, T <sub>A</sub> = 85°C                              |

|                                    |       | 600  |       | ppm FSR | External reference, drift after 1000 hours, T <sub>A</sub> = 85°C                              |

| INL                                | -5    | +2   | +5    | LSB     | Linearity specified in 0.1 mA – 25 mA range                                                    |

| Gain Error                         |       | 2000 |       | ppm FSR |                                                                                                |

| Offset Error                       |       | ±2   |       | LSB     |                                                                                                |

| OTHER INPUT SPECIFICATIONS         |       |      |       |         |                                                                                                |

| DC PSRR <sup>2</sup>               |       | 150  |       | nA/V    |                                                                                                |

| Input Impedance                    |       | 175  |       | Ω       | Including 100 Ω R <sub>SENSE</sub>                                                             |

| Headroom                           | 5.0   |      |       | V       | Minimum required difference between AVDD and the I/OP_x screw terminal voltage to source 25 mA |

<sup>&</sup>lt;sup>1</sup> R<sub>SENSE</sub> accuracy directly impacts the TUE and gain error.

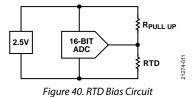

#### **RTD MEASUREMENT**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT pin tied to REFIN pin), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A$ = -40°C to +85°C, unless otherwise noted. External current limiting resistor of 2 k $\Omega$ , 0.1% accuracy, and 10 ppm/°C connected to the SENSEH\_x pin.  $R_{SENSE}$  = 100  $\Omega$ , 0.1%, 10 ppm/°C.

Table 6.

| Parameter                                     | Min | Тур             | Max | Unit | Test Conditions/Comments                                                                                                                                     |

|-----------------------------------------------|-----|-----------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESISTANCE MEASUREMENT                        |     |                 |     |      |                                                                                                                                                              |

| Input Range                                   | 0   |                 | 1   | ΜΩ   | 2-wire RTD measurements supported                                                                                                                            |

| Bias Voltage                                  |     | 2.5             |     | V    |                                                                                                                                                              |

| Pull-Up Resistor (R <sub>PULL-UP</sub> )      |     | 2.1             |     | kΩ   | $R_{\text{PULL-UP}}$ is comprised of the external 2 k $\Omega$ resistor and the external 100 $\Omega$ $R_{\text{SENSE}}$ with an accuracy of 0.1%, 10 ppm/°C |

| ACCURACY                                      |     |                 |     |      |                                                                                                                                                              |

| Measurement Range                             |     |                 |     |      |                                                                                                                                                              |

| $0\Omega$ to $80\Omega$                       |     | $0.5\% \pm 0.5$ |     | Ω    | $\pm\%$ of measured value $\pm\Omega$ offset                                                                                                                 |

| $80\Omega$ to $200\Omega$                     |     | 0.3             |     | %    | ±% of measured value                                                                                                                                         |

| $200\Omega$ to $1k\Omega$                     |     | 0.2             |     | %    | ±% of measured value                                                                                                                                         |

| 1 k $\Omega$ to 10 k $\Omega$                 |     | 0.2             |     | %    | ±% of measured value                                                                                                                                         |

| 10 k $\Omega$ to 20 k $\Omega$                |     | 0.3             |     | %    | ±% of measured value                                                                                                                                         |

| $20 \text{ k}\Omega$ to $100 \text{ k}\Omega$ |     | 0.8             |     | %    | ±% of measured value                                                                                                                                         |

| 100 k $\Omega$ to 200 k $\Omega$              |     | 1.0             |     | %    | ±% of measured value                                                                                                                                         |

| $200~k\Omega$ to $1~M\Omega$                  |     | 8               |     | %    | ±% of measured value                                                                                                                                         |

<sup>&</sup>lt;sup>2</sup> Guaranteed by design and characterization.

#### **DIGITAL INPUT LOGIC**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT pin tied to REFIN pin), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A = -40^{\circ}\text{C}$  to +85°C, unless otherwise noted.

Table 7.

| Parameter                          | Min     | Тур     | Max                 | Unit | Test Conditions/Comments                                                                             |

|------------------------------------|---------|---------|---------------------|------|------------------------------------------------------------------------------------------------------|

| DIGITAL INPUTS                     |         |         |                     |      |                                                                                                      |

| Input Data Rate <sup>1</sup>       |         |         | 5                   | kHz  | Unfiltered input, SENSEL pin driven by a low impedance source, 0 V to 10 V signal, duty cycle: 60:40 |

| Maximum Input Voltage <sup>1</sup> |         |         | 40                  | V    | Limited by the TVS clamping voltage                                                                  |

| Minimum Input Voltage <sup>1</sup> | -40     |         |                     |      |                                                                                                      |

| CURRENT SINK                       |         |         |                     |      |                                                                                                      |

| Series Resistor Value              |         | 2.3     |                     | kΩ   |                                                                                                      |

| Current Sink Range                 | 0       |         | 1.8                 | mA   | Typical programmable current sink to AGND                                                            |

| <b>Current Sink Resolution</b>     |         | 120     |                     | μΑ   |                                                                                                      |

| Current Sink Accuracy              |         | 2       |                     | %FSR |                                                                                                      |

| VOLTAGE THRESHOLDS MODES           |         |         |                     |      |                                                                                                      |

| AVDD Threshold Mode                |         |         |                     |      |                                                                                                      |

| Threshold Range                    | AVDD/60 |         | AVDD $\times$ 59/60 | V    | Programmable trip level shared between all channels                                                  |

| Threshold Resolution               |         | AVDD/30 |                     | V    |                                                                                                      |

| Hysteresis                         |         | AVDD/60 |                     | V    |                                                                                                      |

| Fixed Threshold Mode               |         |         |                     |      |                                                                                                      |

| Threshold Range                    | 0.5     |         | 16                  | V    | Programmable trip level shared between all channels                                                  |

| Threshold Resolution               |         | 0.5     |                     | V    |                                                                                                      |

| Hysteresis                         |         | 0.5     |                     | V    |                                                                                                      |

| Threshold Accuracy                 |         | 2       |                     | %FSR |                                                                                                      |

$<sup>^{\</sup>rm 1}$  Guaranteed by design and characterization.

#### **DIGITAL INPUT LOOP POWERED**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT pin tied to REFIN pin), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A = -40 \text{°C}$  to +85 °C, unless otherwise noted.

Table 8.

| Parameter                            | Min     | Тур     | Max                 | Unit | Test Conditions/Comments                                                                          |

|--------------------------------------|---------|---------|---------------------|------|---------------------------------------------------------------------------------------------------|

| DIGITAL INPUTS                       |         |         |                     |      |                                                                                                   |

| Input Data Rate <sup>1</sup>         |         | 15      | 5                   | kHz  | Unfiltered input, typically dominated by wetting current, load capacitance, and threshold voltage |

| Dry Contact Wetting Current<br>Range | 0.5     |         | 24.5                | mA   | Loop powered—typical programmable current per channel                                             |

| Headroom                             | 5.0     |         |                     | V    | Minimum required voltage difference between AVDD and the I/OP_x screw terminal to source 25 mA    |

| THRESHOLD MODES                      |         |         |                     |      |                                                                                                   |

| AVDD Threshold Mode                  |         |         |                     |      |                                                                                                   |

| Threshold Range                      | AVDD/60 |         | AVDD $\times$ 59/60 | V    | Programmable trip level shared between all channels                                               |

| Threshold Resolution                 |         | AVDD/30 |                     | V    |                                                                                                   |

| Hysteresis                           |         | AVDD/60 |                     | V    |                                                                                                   |

| Fixed Threshold Mode                 |         |         |                     |      |                                                                                                   |

| Threshold Range                      | 0.5     |         | 16                  | V    | Programmable trip level shared between all channels                                               |

| Threshold Resolution                 |         | 0.5     |                     | V    |                                                                                                   |

| Hysteresis                           |         | 0.5     |                     | V    |                                                                                                   |

| Threshold Accuracy                   |         | 2       |                     | %FSR |                                                                                                   |

$<sup>^{\</sup>rm 1}\,\mbox{Guaranteed}$  by design and characterization.

#### **ADC SPECIFICATIONS**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A$ =-40°C to +85°C, unless otherwise noted. AGND – 0.5 V < I/OP\_x screw terminal voltage < AVDD – 0.2 V when measuring current by sensing voltage across  $R_{SENSE}$ .

Table 9.

| Parameter                     | Min  | Тур   | Max  | Unit    | Test Conditions/Comments                                                                                                                                                |

|-------------------------------|------|-------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC SPECIFICATIONS            |      |       |      |         |                                                                                                                                                                         |

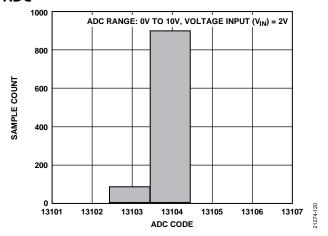

| Resolution                    | 16   |       |      | Bits    |                                                                                                                                                                         |

| No Missing Codes <sup>1</sup> | 16   |       |      | Bits    |                                                                                                                                                                         |

| Conversion Rates <sup>1</sup> |      |       |      |         | Sample rates vary depending on the number of channels selected                                                                                                          |

|                               |      |       |      |         | and the use of single or continuous conversion modes.                                                                                                                   |

| 20 SPS                        |      | 20    |      | SPS     | 50 Hz and 60 Hz rejection enabled.                                                                                                                                      |

| 80 SPS                        |      | 80    |      | SPS     | 50 Hz and 60 Hz rejection enabled.                                                                                                                                      |

| 4.8 kSPS                      |      | 4.8   |      | kSPS    | 50 Hz and 60 Hz rejection disabled.                                                                                                                                     |

| Noise <sup>1</sup>            |      |       |      |         | Refer to Table 19.                                                                                                                                                      |

| ADC INPUT RANGES              |      |       |      |         |                                                                                                                                                                         |

| 0 V to 10 V                   |      |       |      |         | Typically used to measure voltage across I/OP_x to I/ON_x screw terminals (I/ON_x is the input/output negative, where x is the channel number).                         |

| Range                         | 0    |       | 10   | V       |                                                                                                                                                                         |

| TUE                           |      | ±0.4  |      | %FSR    |                                                                                                                                                                         |

| INL                           |      | ±2    |      | LSB     |                                                                                                                                                                         |

| Gain Error                    |      | 2000  |      | ppm FSR |                                                                                                                                                                         |

| Offset Error                  |      | ±2    |      | LSB     |                                                                                                                                                                         |

| 0 V to 2.5 V                  |      |       |      |         | Typically used to measure the current flowing out of the AD74412R through the 100 $\Omega$ R <sub>SENSE</sub> or RTD voltage measurements at the I/OP_x screw terminal. |

| Range                         | 0    |       | 2.5  | V       | _                                                                                                                                                                       |

| TUE                           |      | ±0.25 |      | %FSR    | TUE does not include R <sub>SENSE</sub> .                                                                                                                               |

| INL                           |      | ±2    |      | LSB     |                                                                                                                                                                         |

| Gain Error                    |      | 2000  |      | ppm FSR |                                                                                                                                                                         |

| Offset Error                  |      | ±2    |      | LSB     |                                                                                                                                                                         |

| –2.5 V to 0 V                 |      |       |      |         | Typically used to measure the current flowing into the AD74412R across the 100 $\Omega$ Rsense.                                                                         |

| Range                         | -2.5 |       | 0    | V       |                                                                                                                                                                         |

| TUE                           |      | ±0.2  |      | %FSR    |                                                                                                                                                                         |

| INL                           |      | ±2    |      | LSB     |                                                                                                                                                                         |

| Gain Error                    |      | 2000  |      | ppm FSR |                                                                                                                                                                         |

| Offset Error                  |      | ±2    |      | LSB     |                                                                                                                                                                         |

| –2.5 V to +2.5 V              |      |       |      |         | Typically used to measure bidirectional current across 100 $\Omega$ sense resistor in voltage output mode.                                                              |

| Range                         | -2.5 |       | +2.5 | V       |                                                                                                                                                                         |

| TUE                           |      | ±0.2  |      | %FSR    |                                                                                                                                                                         |

| INL                           |      | ±2    |      | LSB     |                                                                                                                                                                         |

| Gain Error                    |      | 2000  |      | ppm FSR |                                                                                                                                                                         |

| Offset Error                  |      | ±2    |      | ppm FSR | Measured at the 0 V input voltage.                                                                                                                                      |

| DIAGNOSTICS SPECIFICATIONS    |      |       |      |         |                                                                                                                                                                         |

| Accuracy                      |      | 2     |      | %       | % of measured value.                                                                                                                                                    |

| Parameter                                | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                                 |

|------------------------------------------|-----|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERNAL TEMPERATURE SENSOR <sup>1</sup> |     |     |      |      |                                                                                                                                                          |

| Junction Operating<br>Temperature Range  | -40 |     | +125 | °C   | The 85°C maximum specified in the Ordering Guide is the ambient temperature. However, the temperature sensor is specified to a die temperature of 125°C. |

| Accuracy                                 |     | 5   |      | °C   |                                                                                                                                                          |

| Resolution                               |     | 0.2 |      | °C   |                                                                                                                                                          |

$<sup>^{\</sup>rm 1}\,\mbox{Guaranteed}$  by design and characterization; not production tested.

#### **GENERAL SPECIFICATIONS**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V (REFOUT tied to REFIN), DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C, unless otherwise noted.

Table 10.

| Parameter                                      | Min      | Тур      | Max      | Unit    | Test Conditions/Comments                                                                            |

|------------------------------------------------|----------|----------|----------|---------|-----------------------------------------------------------------------------------------------------|

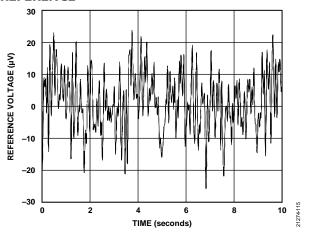

| REFERENCE SPECIFICATIONS                       |          |          |          |         |                                                                                                     |

| Reference Input                                |          |          |          |         |                                                                                                     |

| Reference Input Voltage                        | 2.495    | 2.5      | 2.505    | ٧       |                                                                                                     |

| DC Input Current                               | -1       |          | +1       | μΑ      |                                                                                                     |

| Reference Output                               |          |          |          |         |                                                                                                     |

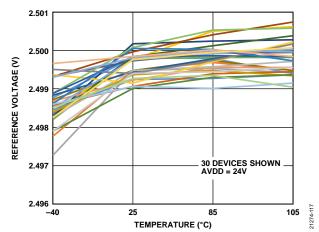

| Output Voltage                                 | 2.495    | 2.5      | 2.505    | ٧       | T <sub>A</sub> = 25°C                                                                               |

| Reference Temperature Coefficient <sup>1</sup> |          |          | 20       | ppm/°C  |                                                                                                     |

| Output Voltage Drift vs. Time <sup>1</sup>     |          | 400      |          | ppm FSR | Drift after 1000 hours, T <sub>A</sub> = 85°C                                                       |

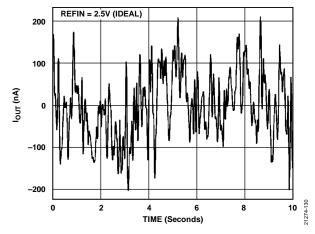

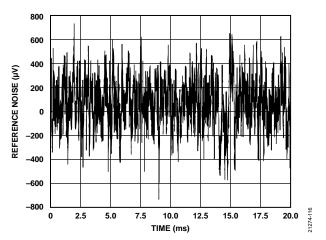

| Output Noise <sup>1</sup>                      |          | 59       |          | μV р-р  | 0.1 Hz to 10 Hz bandwidth.                                                                          |

| Output Noise Spectral Density                  |          | 2.3      |          | μV/√Hz  | Frequency = 1 kHz                                                                                   |

| Capacitive Load                                |          |          | 100      | nF      | On REFOUT pin                                                                                       |

| Output Impedance                               |          | 0.6      |          | Ω       | Sourcing or sinking up to 5 mA                                                                      |

| Short Circuit                                  |          | 25       |          | mA      |                                                                                                     |

| CHARGE PUMP                                    |          |          |          |         |                                                                                                     |

| Voltage                                        |          | -DVCC    |          | V       | The charge pump generates a voltage that is equal to the negative of DVCC                           |

| Accuracy                                       |          | ±10      |          | %       | _                                                                                                   |

| Output Impedance                               |          | 12.5     |          | Ω       |                                                                                                     |

| CASCODE PINS                                   |          |          |          |         |                                                                                                     |

| Cascode Voltage                                | AVDD – 8 | AVDD – 7 | AVDD – 6 | V       | Channel output stage enabled, with decimal Code 0x000 loaded to the DAC                             |

| TEMPERATURE ALERT AND RESET <sup>1</sup>       |          |          |          |         | Junction temperature                                                                                |

| Temperature Alert                              |          | 115      |          | °C      | Junction temperature, high temperature event flags the alert status and the ALERT pin (if unmasked) |

| Temperature Alert Accuracy                     |          | 5        |          | °C      |                                                                                                     |

| Temperature Reset                              |          | 140      |          | °C      | Junction temperature, resets the device if over temperature event when EN_THERM_RST =1              |

| Temperature Reset Accuracy                     |          | 5        |          | °C      |                                                                                                     |

| Parameter                      | Min            | Тур  | Max            | Unit | Test Conditions/Comments                                     |

|--------------------------------|----------------|------|----------------|------|--------------------------------------------------------------|

| LOGIC INPUTS                   |                |      |                |      | SCLK, SDI, RESET, SYNC, LDAC                                 |

| Input Voltage                  |                |      |                |      |                                                              |

| High (V <sub>I</sub> )         | 0.8 ×<br>IOVDD |      |                | V    | IOVDD ≤ 2.7 V                                                |

|                                | 0.7 ×<br>IOVDD |      |                | V    | IOVDD > 2.7 V                                                |

| Low (V <sub>IL</sub> )         |                |      | 0.2 ×<br>IOVDD | V    | IOVDD ≤ 2.7 V                                                |

|                                |                |      | 0.3 ×<br>IOVDD | V    | IOVDD > 2.7 V                                                |

| Input Current                  | -1             |      | +1             | μΑ   | Per pin                                                      |

| Input Capacitance <sup>1</sup> |                | 3    |                | рF   | Per pin                                                      |

| LOGIC OUTPUTS                  |                |      |                |      |                                                              |

| SDO Pin                        |                |      |                |      |                                                              |

| Output Voltage                 |                |      |                |      |                                                              |

| Low (V <sub>OL</sub> )         |                |      | 0.4            | V    | Sink current (I <sub>SINK</sub> ) = 200 μA                   |

| High (V <sub>он</sub> )        | IOVDD –<br>0.4 |      |                | V    | Source current (I <sub>SOURCE</sub> ) = 200 μA               |

| High Impedance Leakage Current | -1             |      | +1             | μΑ   |                                                              |

| GPO_x Pin                      |                |      |                |      |                                                              |

| Output Voltage                 |                |      |                |      |                                                              |

| Low V <sub>OL</sub>            |                |      | 0.4            | V    | $I_{SINK} = 200  \mu A$                                      |

|                                |                | 0.15 | 0.4            | V    | $I_{SINK} = 3 \text{ mA for IOVDD} > 2.7 \text{ V}$          |

| High V <sub>OH</sub>           | IOVDD –<br>0.4 |      |                | V    | I <sub>SINK</sub> = 200 μA                                   |

|                                | IOVDD –<br>0.4 |      |                | V    | $I_{SINK} = 3 \text{ mA for IOVDD} > 2.7 \text{ V}$          |

| Pull-Down Resistance           |                | 101  |                | kΩ   |                                                              |

| High Impedance Leakage Current | -1             |      | +1             | μΑ   |                                                              |

| OPEN-DRAIN LOGIC OUTPUTS       |                |      |                |      | ADC_RDY, ALERT                                               |

| $V_{OL}$                       |                |      | 0.4            | V    | 10 kΩ pull-up resistor to IOVDD                              |

|                                |                |      | 0.4            | V    | At 2.5 mA                                                    |

| High Impedance Leakage Current | -1             |      | +1             | V    |                                                              |

| POWER SUPPLY MONITORS          |                |      |                |      |                                                              |

| AVDD Threshold                 |                | 9.5  |                | V    |                                                              |

| ALDO5V Threshold               |                | 4.1  |                | V    |                                                              |

| DVCC Threshold                 |                | 2.0  |                | V    |                                                              |

| ALDO1V8 Threshold              |                | 1.4  |                | V    |                                                              |

| AVSS Threshold                 |                | -1.9 |                | V    |                                                              |

| POWER REQUIREMENTS             |                |      |                |      |                                                              |

| Supply Voltages <sup>1</sup>   |                |      |                |      |                                                              |

| AVDD                           | 14             | 24   | 26.4           | V    |                                                              |

| DVCC                           | 2.7            | 3.3  | 5.5            | V    |                                                              |

| IOVDD                          | 1.7            | DVCC | 5.5            | V    |                                                              |

| Supply Quiescent Currents      |                |      |                |      |                                                              |

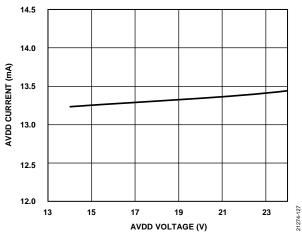

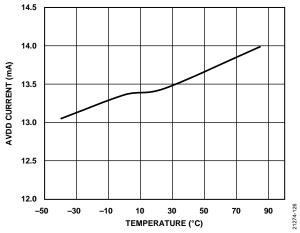

| AVDD Current                   | 10             | 13.5 | 18             | mA   | AD74412R powered up and in high-Z mode                       |

|                                | 10             | 12.5 | 14             | mA   | Four channels configured in any output mode, no load current |

|                                | 10             | 15   | 18.5           | mA   | Four channels configured in any input mode, no load current  |

| Parameter                                                 | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                                                                   |

|-----------------------------------------------------------|-----|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVCC Current                                              | 5.5 | 9.0  | 13.5 | mA   | AD74412R powered up and in high-Z mode                                                                                                                                                     |

|                                                           | 8.5 | 10.5 | 12.5 | mA   | Four channels configured in any output mode, no load current                                                                                                                               |

| IOVDD Current                                             |     | 15   | 100  | μΑ   | AD74412R powered up and in high-Z mode                                                                                                                                                     |

| CONFIGURATION TIMING                                      |     |      |      |      |                                                                                                                                                                                            |

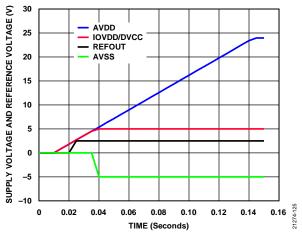

| Device Power-Up Time <sup>1</sup>                         |     | 10   |      | ms   | After AVDD and DVCC power up                                                                                                                                                               |

| Device Reset Time <sup>1</sup>                            |     | 1    |      | ms   | Time taken for device reset and calibration memory upload to complete hardware or software reset events after the device is powered up (see Table 11 for RESET pulse width specifications) |

| Use Case Switch Time <sup>1</sup>                         |     | 130  |      | μs   | Time in use case before changing to another use case                                                                                                                                       |

| Time in Use Case Before Loading DAC<br>Codes <sup>1</sup> |     | 150  |      | μs   |                                                                                                                                                                                            |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization.

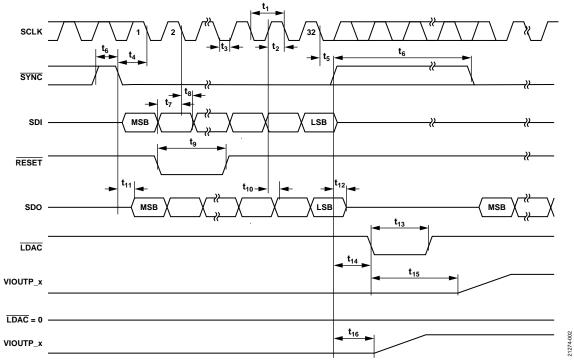

#### **TIMING CHARACTERISTICS**

#### **SPI Timing Specifications**

AVDD = 14 V to 26.4 V, AGND = DGND = 0 V, REFIN = 2.5 V internal or external, DVCC = 2.7 V to 5.5 V, IOVDD = 1.7 V to 5.5 V, and all specifications at T<sub>A</sub>=-40°C to +85°C, unless otherwise noted.

Table 11.

| Parameter <sup>1, 2</sup> | Description                                                     | IOVDD = 1.7 V to 2.7 V | IOVDD = 2.7 V to 5.5 V | Unit   |

|---------------------------|-----------------------------------------------------------------|------------------------|------------------------|--------|

| t <sub>1</sub>            | SCLK pin cycle time                                             | 50                     | 42                     | ns min |

| $t_2$                     | SCLK high time                                                  | 20                     | 17                     | ns min |

| t <sub>3</sub>            | SCLK low time                                                   | 20                     | 17                     | ns min |

| $t_4$                     | SYNC falling edge to SCLK falling edge setup time               | 25                     | 21                     | ns min |

| <b>t</b> <sub>5</sub>     | Last SCLK falling edge to SYNC rising edge                      | 25                     | 21                     | ns min |

| t <sub>6</sub>            | SYNC high time                                                  | 650                    | 650                    | ns min |

| t <sub>7</sub>            | Data setup time                                                 | 5                      | 5                      | ns min |

| t <sub>8</sub>            | Data hold time                                                  | 5                      | 5                      | ns min |

| t <sub>9</sub>            | RESET pulse width                                               | 50                     | 50                     | μs min |

|                           |                                                                 | 1                      | 1                      | ms max |

| t <sub>10</sub>           | SCLK rising edge to SDO valid                                   | 39.5                   | 23                     | ns max |

| t <sub>11</sub>           | SYNC falling edge to SDO valid (for readback MSB only)          | 34                     | 15                     | ns max |

| t <sub>12</sub>           | SYNC rising edge to SDO tristate                                | 15                     | 14                     | ns min |

| t <sub>13</sub>           | LDAC pulse width                                                | 350                    | 350                    | ns min |

|                           | (LDAC must not be pulsed low until after SYNC is returned high) |                        |                        |        |

| t <sub>14</sub>           | SYNC rising edge to LDAC falling edge                           | 1                      | 1                      | μs min |

| t <sub>15</sub>           | LDAC falling edge to DAC output response time                   | 3                      | 3                      | μs typ |

| t <sub>16</sub>           | SYNC rising edge to DAC output response time (when LDAC is 0)   | 3.5                    | 3                      | μs typ |

| $t_{17}^{3}$              | ADC_RDY pulse                                                   | 30                     | 30                     | μs typ |

$<sup>^1</sup>$  All input signals are specified with rise time ( $t_R$ ) = fall time ( $t_R$ ) = 5 ns (10% to 90% of the voltage on the IOVDD pin ( $V_{\text{IOVDD}}$ )) and timed from a voltage level of  $V_{\text{IOVDD}}/2$ .  $^2$  Guaranteed by design and characterization; not production tested.

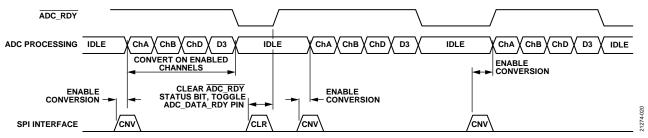

$<sup>^3</sup>$  t<sub>17</sub> is not shown in Figure 2 because it is not an SPI timing specification. See Figure 47 for a diagram with the t<sub>17</sub>.

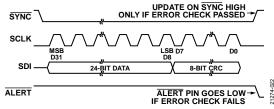

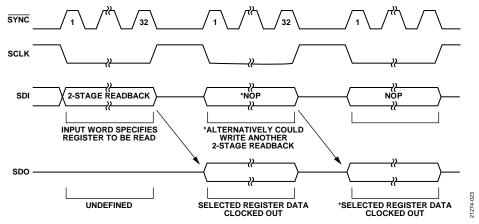

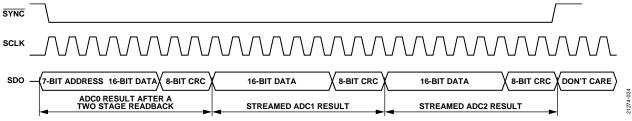

## **Timing Diagrams**

Figure 2. SPI Timing Diagram

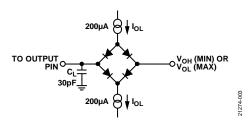

Figure 3. Load Circuit for Digital Output (SDO) Timing Specifications

#### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C unless otherwise noted.

With the recommended configuration, the I/OP\_x screw terminal tolerates overvoltages to dc  $\pm$  40 V (limited by external TVS).

Table 12.

| 1 4010 121                                                                                |                                           |

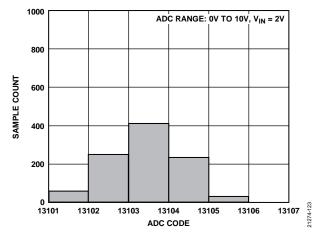

|-------------------------------------------------------------------------------------------|-------------------------------------------|