# 16-Bit, 1600 MSPS, TxDAC+ Digital-to-Analog Converter

Data Sheet AD9139

#### **FEATURES**

Selectable 1× or 2× interpolation filter

Support input signal bandwidth up to 575 MHz

Very small inherent latency variation: <2 DAC clock cycles

Proprietary low spurious and distortion design

6-carrier GSM ACLR = 79 dBc at 200 MHz IF

SFDR >85 dBc (bandwidth = 300 MHz) at zero IF

Flexible 16-bit LVDS interface

Supports word and byte load

Multiple chip synchronization

Fixed latency and data generator latency compensation

FIFO eases system timing and includes error detection

High performance, low noise PLL clock multiplier

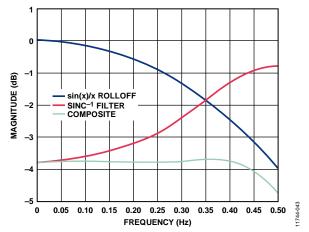

Digital inverse sinc filter

Low power: 700 mW at 1230 MSPS

72-lead LFCSP

#### **APPLICATIONS**

Wireless communications: 3G/4G and MC-GSM base stations, wideband repeaters, software defined radios Wideband communications: point-to-point, LMDS/MMDS Transmit diversity/MIMO Instrumentation

Automated test equipment

#### **GENERAL DESCRIPTION**

The AD9139 is an 16-bit, high dynamic range digital-to-analog converter (DAC) that provides a sample rate of 1600 MSPS, permitting a multicarrier generation up to the Nyquist frequency. The AD9139 TxDAC+\* includes features optimized for wideband communication applications, including 1× and 2× interpolation, a delay locked loop (DLL) powered high speed interface, sample error detection, and parity detection. A 3-wire serial port interface provides for the programming/readback of many internal parameters. A full-scale output current can be programmed over a range of 9 mA up to 33 mA. The AD9139 is available in a 72-lead LFCSP.

#### **PRODUCT HIGHLIGHTS**

- 1. 575 MHz achievable input signal bandwidth.

- Advanced low spurious and distortion design techniques provide high quality synthesis of wideband signals from baseband to high intermediate frequencies.

- Very small inherent latency variation simplifies both software and hardware design in the system. It allows easy multichip synchronization for most applications.

- 4. Low power architecture improves power efficiency.

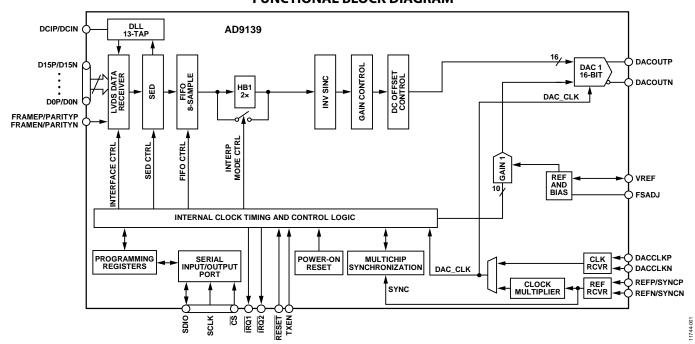

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

**Data Sheet**

## AD9139

## **TABLE OF CONTENTS**

| Features 1                                   | Multidevice Synchronization and Fixed Latency     | 29 |

|----------------------------------------------|---------------------------------------------------|----|

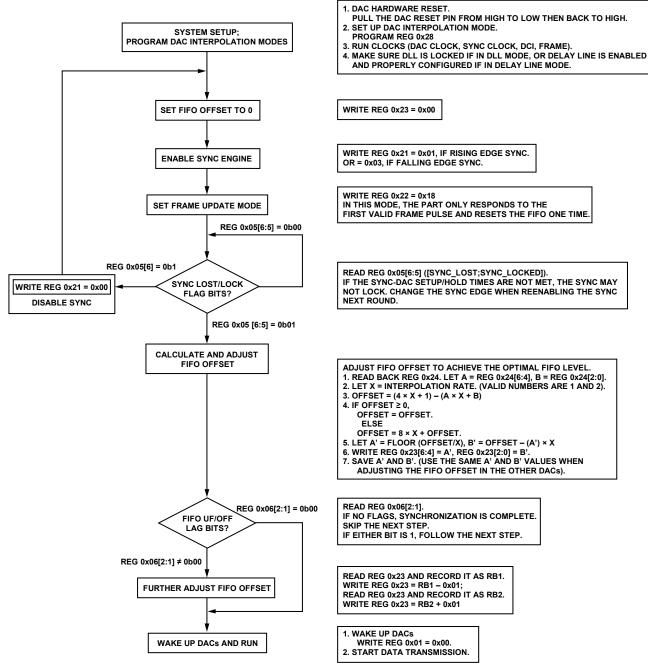

| Applications1                                | Very Small Inherent Latency Variation             | 29 |

| General Description1                         | Further Reducing the Latency Variation            | 29 |

| Product Highlights1                          | Synchronization Implementation                    | 29 |

| Functional Block Diagram1                    | Synchronization Procedures                        | 30 |

| Revision History3                            | Interrupt Request Operation                       | 32 |

| Specifications4                              | Interrupt Working Mechanism                       | 32 |

| DC Specifications                            | Interrupt Service Routine                         | 32 |

| Digital Specifications5                      | Temperature Sensor                                | 33 |

| Latency Variation Specifications             | DAC Input Clock Configurations                    | 34 |

| AC Specifications6                           | Driving the DACCLK and REFCLK Inputs              | 34 |

| Operating Speed Specifications6              | Direct Clocking                                   | 34 |

| Absolute Maximum Ratings7                    | Clock Multiplication                              | 34 |

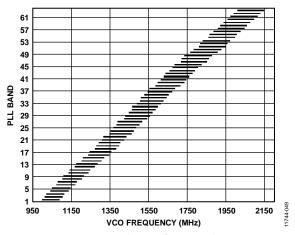

| Thermal Resistance                           | PLL Settings                                      | 35 |

| ESD Caution                                  | Configuring the VCO Tuning Band                   | 35 |

| Pin Configuration and Function Descriptions8 | Automatic VCO Band Select                         | 35 |

| Typical Performance Characteristics11        | Manual VCO Band Select                            | 35 |

| Terminology                                  | PLL Enable Sequence                               | 35 |

| Serial Port Operation16                      | Analog Outputs                                    | 36 |

| Data Format                                  | Transmit DAC Operation                            | 36 |

| Serial Port Pin Descriptions16               | Interfacing to Modulators                         | 37 |

| Serial Port Options                          | Reducing LO Leakage and Unwanted Sidebands        | 38 |

| Data Interface18                             | Start-Up Routine                                  | 39 |

| LVDS Input Data Ports                        | Device Configuration Register Map and Description | 40 |

| Word Interface Mode                          | SPI Configure Register                            | 42 |

| Byte Interface Mode                          | Power-Down Control Register                       | 42 |

| Data Interface Configuration Options         | Interrupt Enable 0 Register                       | 42 |

| DLL Interface Mode                           | Interrupt Enable 1 Register                       | 42 |

| Parity                                       | Interrupt Flag 0 Register                         | 43 |

| SED Operation21                              | Interrupt Flag 1 Register                         | 43 |

| SED Example                                  | Interrupt Select 0 Register                       | 43 |

| Delay Line Interface Mode22                  | Interrupt Select 1 Register                       | 44 |

| FIFO Operation24                             | Frame Mode Register                               | 44 |

| Resetting the FIFO                           | Data Control 0 Register                           | 44 |

| Serial Port Initiated FIFO Reset25           | Data Control 1 Register                           | 44 |

| Frame Initiated FIFO Reset                   | Data Control 2 Register                           | 45 |

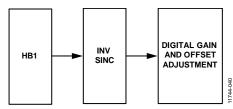

| Digital Datapath27                           | Data Control 3 Register                           | 45 |

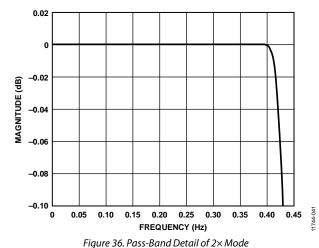

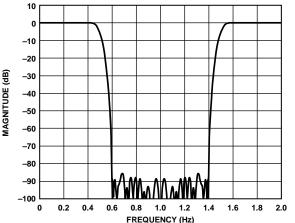

| Interpolation Filters                        | Data Status 0 Register                            | 45 |

| Inverse Sinc Filter                          | DAC Clock Receiver Control Register               | 46 |

| Digital Function Configuration               | Reference Clock Receiver Control Register         | 46 |

| PLL Control Register                                    | 46 |

|---------------------------------------------------------|----|

| PLL Control Register                                    | 47 |

| PLL Control Register                                    | 47 |

| PLL Status Register                                     | 47 |

| PLL Status Register                                     | 48 |

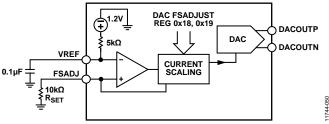

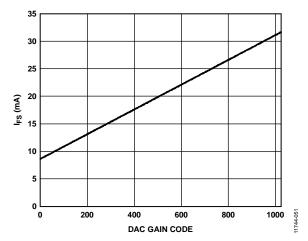

| DAC FS Adjust LSB Register                              | 48 |

| DAC FS Adjust MSB Register                              | 48 |

| Die Temperature Sensor Control Register                 | 48 |

| Die Temperature LSB Register                            | 48 |

| Die Temperature MSB Register                            | 49 |

| Chip ID Register                                        | 49 |

| Interrupt Configuration Register                        | 49 |

| Sync CTRL Register                                      | 49 |

| Frame Reset CTRL Register                               | 49 |

| FIFO Level Configuration Register                       | 50 |

| FIFO Level Readback Register                            | 50 |

| FIFO CTRL Register                                      | 50 |

| Data Format Select Register                             | 51 |

| Datapath Control Register                               | 51 |

| Interpolation Control Register                          | 51 |

| Power-Down Data Input 0 Register                        | 51 |

| DAC_DC_OFFSET0 Register                                 | 51 |

| DAC_DC_OFFSET1 Register                                 | 51 |

| DAC_GAIN_ADJ Register                                   | 52 |

|                                                         |    |

| REVISION HISTORY                                        |    |

| /14—Rev. 0 to Rev. A                                    |    |

| Change to Register 0x7F, Table 21<br>Change to Table 80 |    |

|                                                         |    |

|   | Gain Step Control0 Register        | .52 |

|---|------------------------------------|-----|

|   | Gain Step Control1 Register        | .52 |

|   | TX Enable Control Register         | .52 |

|   | DAC Output Control Register        | .53 |

|   | DLL Cell Enable 0 Register         | .53 |

|   | DLL Cell Enable 1 Register         | .53 |

|   | SED Control Register               | .53 |

|   | SED Pattern S0 Low Bits Register   | .54 |

|   | SED Pattern S0 High Bits Register  | .54 |

|   | SED Pattern S1 Low Bits Register   | .54 |

|   | SED Pattern S1 High Bits Register  | .54 |

|   | SED Pattern S2 Low Bits Register   | .54 |

|   | SED Pattern S2 High Bits Register  | .54 |

|   | SED Pattern S3 Low Bits Register   | .54 |

|   | SED Pattern S3 High Bits Register  | .55 |

|   | Parity Control Register            | .55 |

|   | Parity Error Rising Edge Register  | .55 |

|   | Parity Error Falling Edge Register | .55 |

|   | Version Register                   | .55 |

| P | ackaging and Ordering Information  | .56 |

|   | Outline Dimensions                 | .56 |

|   | Ordering Guide                     | .56 |

## R

| Change to | Register 0x7F, Table 21 | 4  | l |

|-----------|-------------------------|----|---|

| Change to | Table 80                | 55 | 5 |

10/13—Revision 0: Initial Version

# **SPECIFICATIONS** DC SPECIFICATIONS

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{OUTFS}}$  = 20 mA, maximum sample rate, unless otherwise noted.

Table 1.

| Parameter                        | Test Conditions/Comments                       | Min    | Тур       | Max    | Unit   |

|----------------------------------|------------------------------------------------|--------|-----------|--------|--------|

| RESOLUTION                       |                                                |        | 16        |        | Bits   |

| ACCURACY                         |                                                |        |           |        |        |

| Differential Nonlinearity (DNL)  |                                                |        | ±2.1      |        | LSB    |

| Integral Nonlinearity (INL)      |                                                |        | ±3.7      |        | LSB    |

| MAIN DAC OUTPUT                  |                                                |        |           |        |        |

| Offset Error                     |                                                | -0.001 | 0         | +0.001 | % FSR  |

| Gain Error                       | With internal reference                        | -3.2   | +2        | +4.7   | % FSR  |

| Full-Scale Output Current        | 10 kΩ external resistor between FSADJ and AVSS | 19.06  | 19.8      | 20.6   | mA     |

| Output Compliance Range          |                                                | -1.0   |           | +1.0   | V      |

| Output Resistance                |                                                |        | 10        |        | ΜΩ     |

| Gain DAC Monotonicity            |                                                |        | Guarantee | ed     |        |

| Settling Time to Within ±0.5 LSB |                                                |        | 20        |        | ns     |

| MAIN DAC TEMPERATURE DRIFT       |                                                |        |           |        |        |

| Offset                           |                                                |        | 0.04      |        | ppm/°0 |

| Gain                             |                                                |        | 100       |        | ppm/°0 |

| Reference Voltage                |                                                |        | 30        |        | ppm/°0 |

| REFERENCE                        |                                                |        |           |        | 1      |

| Internal Reference Voltage       |                                                | 1.17   |           | 1.19   | V      |

| Output Resistance                |                                                |        | 5         |        | kΩ     |

| ANALOG SUPPLY VOLTAGES           |                                                |        |           |        |        |

| AVDD33                           |                                                | 3.13   | 3.3       | 3.47   | V      |

| CVDD18                           |                                                | 1.7    | 1.8       | 1.9    | V      |

| DIGITAL SUPPLY VOLTAGES          |                                                |        |           |        |        |

| DVDD18                           |                                                | 1.7    | 1.8       | 1.9    | V      |

| DVDD18 Variation over Operating  |                                                | -2.5%  |           | +2.5%  | V      |

| Conditions <sup>1</sup>          |                                                |        |           |        |        |

| POWER CONSUMPTION                |                                                |        |           |        |        |

| 1× Mode                          | $f_{DAC} = 614 \text{ MSPS}$                   |        | 440       |        | mW     |

|                                  | $f_{DAC} = 1230 \text{ MSPS}$                  |        | 700       |        | mW     |

| 2× Mode                          | $f_{DAC} = 800 \text{ MSPS}$                   |        | 670       |        | mW     |

|                                  | $f_{DAC} = 1600 \text{ MSPS}$                  |        | 1150      |        | mW     |

| Phase-Locked Loop                |                                                |        | 70        |        | mW     |

| Inverse Sinc                     | $f_{DAC} = 1230 \text{ MSPS}$                  |        | 60        |        | mW     |

| Reduced Power Mode (Power-Down)  |                                                |        |           | 57.3   | mW     |

| AVDD33 Current                   |                                                |        |           | 0.4    | mA     |

| CVDD18 Current                   |                                                |        |           | 26.6   | mA     |

| DVDD18 Current                   |                                                |        |           | 4.5    | mA     |

| OPERATING RANGE                  |                                                | -40    | +25       | +85    | °C     |

<sup>&</sup>lt;sup>1</sup> This parameter specifies the maximum allowable variation of DVDD18 over operating conditions compared with the DVDD18 presented to the device at the time the data interface DLL is enabled.

#### **DIGITAL SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{OUTFS}}$  = 20 mA, maximum sample rate, unless otherwise noted.

Table 2.

| Parameter                                        | Symbol                             | Test Conditions/Comments                            | Min  | Тур  | Max  | Unit |

|--------------------------------------------------|------------------------------------|-----------------------------------------------------|------|------|------|------|

| CMOS INPUT LOGIC LEVEL                           |                                    |                                                     |      |      |      |      |

| Input                                            |                                    |                                                     |      |      |      |      |

| Logic High                                       |                                    | DVDD18 = 1.8 V                                      | 1.2  |      |      | V    |

| Logic Low                                        |                                    | DVDD18 = 1.8 V                                      |      |      | 0.6  | V    |

| CMOS OUTPUT LOGIC LEVEL                          |                                    |                                                     |      |      |      |      |

| Output                                           |                                    |                                                     |      |      |      |      |

| Logic High                                       |                                    | DVDD18 = 1.8 V                                      | 1.4  |      |      | V    |

| Logic Low                                        |                                    | DVDD18 = 1.8 V                                      |      |      | 0.4  | V    |

| LVDS RECEIVER INPUTS                             |                                    | Data and frame inputs                               |      |      |      |      |

| Input Voltage Range                              | V <sub>IA</sub> or V <sub>IB</sub> |                                                     | 825  |      | 1675 | mV   |

| Input Differential Threshold                     | V <sub>IDTH</sub>                  |                                                     | -175 |      | +175 | mV   |

| Input Differential Hysteresis                    | VIDTHH to VIDTHL                   |                                                     |      | 20   |      | mV   |

| Receiver Differential Input Impedance            | R <sub>IN</sub>                    |                                                     |      | 100  |      | Ω    |

| DLL SPEED RANGE                                  |                                    |                                                     | 250  |      | 575  | MHz  |

| DAC UPDATE RATE                                  |                                    |                                                     |      |      | 1600 | MSPS |

| DAC Adjusted Update Rate                         |                                    | 1× interpolation                                    |      |      | 1150 | MSPS |

|                                                  |                                    | 2× interpolation                                    |      |      | 800  | MSPS |

| DAC CLOCK INPUT (DACCLKP, DACCLKN)               |                                    |                                                     |      |      |      |      |

| Differential Peak-to-Peak Voltage                |                                    |                                                     | 100  | 500  | 2000 | mV   |

| Common-Mode Voltage                              |                                    | Self biased input, ac-coupled                       |      | 1.25 |      | V    |

| REFCLK/SYNCCLK INPUT (REFP/SYNCP,<br>REFN/SYNCN) |                                    |                                                     |      |      |      |      |

| Differential Peak-to-Peak Voltage                |                                    |                                                     | 100  | 500  | 2000 | mV   |

| Common-Mode Voltage                              |                                    |                                                     |      | 1.25 |      | V    |

| Input Clock Frequency                            |                                    | $1.03 \text{ GHz} \le f_{VCO} \le 2.07 \text{ GHz}$ |      |      | 450  | MHz  |

| SERIAL PORT INTERFACE                            |                                    |                                                     |      |      |      |      |

| Maximum Clock Rate                               | SCLK                               |                                                     | 40   |      |      | MHz  |

| Minimum Pulse Width                              |                                    |                                                     |      |      |      |      |

| High                                             | t <sub>РWH</sub>                   |                                                     |      |      | 12.5 | ns   |

| Low                                              | t <sub>PWL</sub>                   |                                                     |      |      | 12.5 | ns   |

| SDIO to SCLK Setup Time                          | t <sub>DS</sub>                    |                                                     | 1.5  |      |      | ns   |

| SDIO to SCLK Hold Time                           | t <sub>DH</sub>                    |                                                     | 0.68 |      |      | ns   |

| CS to SCLK Setup Time                            | t <sub>DCSB</sub>                  |                                                     | 2.38 | 1.4  |      | ns   |

| CS to SCLK Hold Time                             | t <sub>DCSB</sub>                  |                                                     | 9.6  |      |      | ns   |

| SDIO to SCLK Delay                               | t <sub>DV</sub>                    | Wait time for valid output from SDIO                | 11   |      |      | ns   |

| SDIO High-Z to $\overline{\text{CS}}$            |                                    | Time for SDIO to relinquish the output bus          | 8.5  |      |      | ns   |

| SDIO LOGIC LEVEL                                 |                                    |                                                     |      |      |      |      |

| Voltage Input High                               | V <sub>IH</sub>                    |                                                     | 1.2  | 1.8  |      | V    |

| Voltage Input Low                                | V <sub>IL</sub>                    |                                                     |      | 0    | 0.5  | V    |

| Voltage Output High                              | Іін                                | With 2 mA loading                                   | 1.36 |      | 2    | V    |

| Voltage Output Low                               | I <sub>IL</sub>                    | With 2 mA loading                                   | 0    |      | 0.45 | V    |

#### **LATENCY VARIATION SPECIFICATIONS**

Table 3.

| Parameter                          | Min | Тур | Max | Unit             |

|------------------------------------|-----|-----|-----|------------------|

| DAC LATENCY <sup>1</sup> VARIATION |     |     |     |                  |

| SYNC Off                           |     | 1   | 2   | DAC clock cycles |

| SYNC On                            |     | 0   | 1   | DAC clock cycles |

<sup>&</sup>lt;sup>1</sup> DAC latency is defined as the elapsed time from a data sample clocked at the input to the device until the analog output begins to change.

#### **AC SPECIFICATIONS**

$T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , AVDD33 = 3.3 V, DVDD18 = 1.8 V, CVDD18 = 1.8 V,  $I_{\text{OUTFS}}$  = 20 mA, maximum sample rate, unless otherwise noted.

#### Table 4.

| Parameter                                    | Test Conditions/Comments         | Min | Тур    | Max | Unit   |

|----------------------------------------------|----------------------------------|-----|--------|-----|--------|

| SPURIOUS-FREE DYNAMIC RANGE (SFDR)           | –14 dBFS single tone             |     |        |     |        |

| $f_{DAC} = 737.28 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     |        |     |        |

| Bandwidth (BW) = 125 MHz                     |                                  |     | 85     |     | dBc    |

| BW = 270 MHz                                 |                                  |     | 80     |     | dBc    |

| $f_{DAC} = 983.04 \text{ MSPS}$              | $f_{OUT} = 200 \text{ MHz}$      |     |        |     |        |

| BW = 360 MHz                                 |                                  |     | 85     |     | dBc    |

| $f_{DAC} = 1228.8 \text{ MSPS}$              | f <sub>OUT</sub> = 280 MHz       |     |        |     |        |

| BW = 200 MHz                                 |                                  |     | 85     |     | dBc    |

| BW = 500 MHz                                 |                                  |     | 75     |     | dBc    |

| TWO-TONE INTERMODULATION DISTORTION (IMD)    | -12 dBFS each tone               |     |        |     |        |

| $f_{DAC} = 737.28 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     | 80     |     | dBc    |

| $f_{DAC} = 983.04 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     | 82     |     | dBc    |

| $f_{DAC} = 1228.8 \text{ MSPS}$              | f <sub>OUT</sub> = 280 MHz       |     | 80     |     | dBc    |

| NOISE SPECTRAL DENSITY (NSD)                 | Eight-tone, 500 kHz tone spacing |     |        |     |        |

| $f_{DAC} = 737.28 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     | -160   |     | dBm/Hz |

| $f_{DAC} = 983.04 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     | -161.5 |     | dBm/Hz |

| $f_{DAC} = 1228.8 \text{ MSPS}$              | f <sub>OUT</sub> = 280 MHz       |     | -164.5 |     | dBm/Hz |

| W-CDMA ADJACENT CHANNEL LEAKAGE RATIO (ACLR) | Single carrier                   |     |        |     |        |

| $f_{DAC} = 983.04 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     | 81     |     | dBc    |

| $f_{DAC} = 1228.8 \text{ MSPS}$              | $f_{OUT} = 20 \text{ MHz}$       |     | 83     |     | dBc    |

|                                              | f <sub>OUT</sub> = 280 MHz       |     | 80     |     | dBc    |

| W-CDMA SECOND (ACLR)                         | Single carrier                   |     |        |     |        |

| $f_{DAC} = 983.04 \text{ MSPS}$              | f <sub>OUT</sub> = 200 MHz       |     | 85     |     | dBc    |

| $f_{DAC} = 1228.8 \text{ MSPS}$              | f <sub>OUT</sub> = 20 MHz        |     | 86     |     | dBc    |

|                                              | f <sub>OUT</sub> = 280 MHz       |     | 86     |     | dBc    |

### **OPERATING SPEED SPECIFICATIONS**

Table 5.

| Interpolation | Interpolation DVDD18, CVDD18 = 1.8 V ± 5% |                             |                             | 9 V ± 5% or 1.8 V ± 2%      | DVDD18, CVDD18 = 1.9 V ± 2% |                             |  |

|---------------|-------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|--|

| Factor        | f <sub>DCI</sub> (MSPS) Max               | f <sub>DAC</sub> (MSPS) Max | f <sub>DCI</sub> (MSPS) Max | f <sub>DAC</sub> (MSPS) Max | f <sub>DCI</sub> (MSPS) Max | f <sub>DAC</sub> (MSPS) Max |  |

| 1×            | 575                                       | 1150                        | 575                         | 1150                        | 575                         | 1150                        |  |

| 2×            | 350                                       | 1400                        | 375                         | 1500                        | 400                         | 1600                        |  |

#### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                                                      | Rating                   |

|----------------------------------------------------------------|--------------------------|

| AVDD33 to GND                                                  | −0.3 V to +3.6 V         |

| DVDD18, CVDD18 to GND                                          | −0.3 V to +2.1 V         |

| FSADJ, VREF, DACOUTP/DACOUTN, to GND                           | -0.3 V to AVDD33 + 0.3 V |

| D15P to D0P/D15N to D0N,<br>FRAMEP/FRAMEN, DCIP/DCIN to<br>GND | -0.3 V to DVDD18 + 0.3 V |

| DACCLKP/DACCLKN,<br>REFP/SYNCP/REFN/SYNCN to GND               | -0.3 V to CVDD18 + 0.3 V |

| RESET, IRQ1, IRQ2, CS, SCLK, SDIO to GND                       | -0.3 V to DVDD18 + 0.3 V |

| Junction Temperature                                           | 125°C                    |

| Storage Temperature Range                                      | −65°C to +150°C          |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

The exposed pad (EPAD) must be soldered to the ground plane (AVSS) for the 72-lead LFCSP. The EPAD provides an electrical, thermal, and mechanical connection to the board.

Typical  $\theta_{JA}$ ,  $\theta_{JB}$ , and  $\theta_{JC}$  values are specified for a 4-layer board in still air. Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$  and  $\theta_{JB}$ .

**Table 7. Thermal Resistance**

| Package       | θ <sub>JA</sub> | <b>Ө</b> ЈВ | θ <sub>JC</sub> | Unit | Conditions      |

|---------------|-----------------|-------------|-----------------|------|-----------------|

| 72-Lead LFCSP | 20.7            | 10.9        | 1.1             | °C/W | EPAD soldered   |

|               |                 |             |                 |      | to ground plane |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

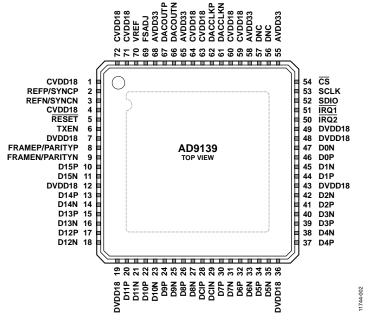

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

- NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT TO THIS PIN.

2. THE EXPOSED PAD MUST BE SOLDERED TO THE GROUND PLANE (AVSS, DVSS, CVSS). THE EPAD PROVIDES AN ELECTRICAL, THERMAL, AND MECHANICAL CONNECTION TO THE BOARD.

Figure 2. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No. | Mnemonic       | Description                                                                                                                                                                          |

|---------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CVDD18         | 1.8 V PLL Supply. CVDD18 supplies the power to the clock receivers, clock multiplier, and clock distribution.                                                                        |

| 2       | REFP/SYNCP     | PLL Reference Clock/Synchronization Clock Input, Positive.                                                                                                                           |

| 3       | REFN/SYNCN     | PLL Reference Clock/Synchronization Clock Input, Negative.                                                                                                                           |

| 4       | CVDD18         | 1.8 V PLL Supply. CVDD18 supplies the power to the clock receivers, clock multiplier, and clock distribution.                                                                        |

| 5       | RESET          | Reset, Active Low. CMOS levels with respect to DVDD18. Recommended reset pulse length is 1 µs.                                                                                       |

| 6       | TXEN           | Active High Transmit Path Enable. CMOS levels with respect to DVDD18. A low level on this pin triggers two selectable actions in the DAC. See Register 0x43 in Table 64 for details. |

| 7       | DVDD18         | 1.8 V <u>Digital Supply. Pin 7 supplies power to the digital core, digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2.</u>                                     |

| 8       | FRAMEP/PARITYP | Frame/Parity Input, Positive.                                                                                                                                                        |

| 9       | FRAMEN/PARITYN | Frame/Parity Input, Negative.                                                                                                                                                        |

| 10      | D15P           | Data Bit 15 (MSB), Positive.                                                                                                                                                         |

| 11      | D15N           | Data Bit 15 (MSB), Negative.                                                                                                                                                         |

| 12      | DVDD18         | 1.8 V Digital Supply. Pin 12 supplies the power to the digital core and digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2.                                    |

| 13      | D14P           | Data Bit 14, Positive.                                                                                                                                                               |

| 14      | D14N           | Data Bit 14, Negative.                                                                                                                                                               |

| 15      | D13P           | Data Bit 13, Positive.                                                                                                                                                               |

| 16      | D13N           | Data Bit 13, Negative.                                                                                                                                                               |

| 17      | D12P           | Data Bit 12, Positive.                                                                                                                                                               |

| 18      | D12N           | Data Bit 12, Negative.                                                                                                                                                               |

| 19      | DVDD18         | 1.8 V <u>Digital Supp</u> ly. Pin 19 supplies power to the digital core, digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2.                                   |

| 20      | D11P           | Data Bit 11, Positive.                                                                                                                                                               |

| 21      | D11N           | Data Bit 11, Negative.                                                                                                                                                               |

| 22      | D10P           | Data Bit 10, Positive.                                                                                                                                                               |

| 23      | D10N           | Data Bit 10, Negative.                                                                                                                                                               |

| Pin No. | Mnemonic  | Description                                                                                                                                                     |  |  |  |  |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 24      | D9P       | Data Bit 9, Positive.                                                                                                                                           |  |  |  |  |

| 25      | D9N       | Data Bit 9, Negative.                                                                                                                                           |  |  |  |  |

| 26      | D8P       | Data Bit 8, Positive.                                                                                                                                           |  |  |  |  |

| 27      | D8N       | Data Bit 8, Negative.                                                                                                                                           |  |  |  |  |

| 28      | DCIP      | Data Clock Input, Positive.                                                                                                                                     |  |  |  |  |

| 29      | DCIN      | Data Clock Input, Negative.                                                                                                                                     |  |  |  |  |

| 30      | D7P       | Data Bit 7, Positive.                                                                                                                                           |  |  |  |  |

| 31      | D7N       | Data Bit 7, Negative.                                                                                                                                           |  |  |  |  |

| 32      | D6P       | Data Bit 6, Positive.                                                                                                                                           |  |  |  |  |

| 33      | D6N       | Data Bit 6, Negative.                                                                                                                                           |  |  |  |  |

| 34      | D5P       | Data Bit 5, Positive.                                                                                                                                           |  |  |  |  |

| 35      | D5N       | Data Bit 5, Negative.                                                                                                                                           |  |  |  |  |

| 36      | DVDD18    | 1.8 V <u>Digital Supply. Pin 36 supplies</u> the power to the digital core, digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2.           |  |  |  |  |

| 37      | D4P       | Data Bit 4, Positive.                                                                                                                                           |  |  |  |  |

| 38      | D4N       | Data Bit 4, Negative.                                                                                                                                           |  |  |  |  |

| 39      | D3P       | Data Bit 3, Positive.                                                                                                                                           |  |  |  |  |

| 40      | D3N       | Data Bit 3, Negative.                                                                                                                                           |  |  |  |  |

| 41      | D2P       | Data Bit 2, Positive.                                                                                                                                           |  |  |  |  |

| 42      | D2N       | Data Bit 2, Negative.                                                                                                                                           |  |  |  |  |

| 43      | DVDD18    | 1.8 V <u>Digital Supply</u> . Pin 43 supplies the power to the digital core, digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2.          |  |  |  |  |

| 44      | D1P       | Data Bit 1, Positive.                                                                                                                                           |  |  |  |  |

| 45      | D1N       | Data Bit 1, Negative.                                                                                                                                           |  |  |  |  |

| 46      | D0P       | Data Bit 0, Positive.                                                                                                                                           |  |  |  |  |

| 47      | D0N       | Data Bit 0, Negative.                                                                                                                                           |  |  |  |  |

| 48      | DVDD18    | 1.8 V <u>Digital Supp</u> ly. Pi <u>n 48 s</u> upplies the power to the digital core, digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2. |  |  |  |  |

| 49      | DVDD18    | 1.8 V <u>Digital Supply. Pin 49 supplies the power to the digital core, digital data ports, serial port input/output pins, RESET, IRQ1, and IRQ2.</u>           |  |  |  |  |

| 50      | ĪRQ2      | Second Interrupt Request. Open-drain, active low output. Connect an external pull-up to DVDD18 through a 10 k $\Omega$ resistor.                                |  |  |  |  |

| 51      | ĪRQ1      | First Interrupt Request. Open-drain, active low output. Connect an external pull-up to DVDD18 through a 10 k $\Omega$ resistor.                                 |  |  |  |  |

| 52      | SDIO      | Serial Port Data Input/Output. CMOS levels with respect to DVDD18.                                                                                              |  |  |  |  |

| 53      | SCLK      | Serial Port Clock Input. CMOS levels with respect to DVDD18.                                                                                                    |  |  |  |  |

| 54      | <u>cs</u> | Serial Port Chip Select. Active low (CMOS levels with respect to DVDD18).                                                                                       |  |  |  |  |

| 55      | AVDD33    | 3.3 V Analog Supply.                                                                                                                                            |  |  |  |  |

| 56      | DNC       | Do No Connect. Leave this pin floating.                                                                                                                         |  |  |  |  |

| 57      | DNC       | Do No Connect. Leave this pin floating.                                                                                                                         |  |  |  |  |

| 58      | AVDD33    | 3.3 V Analog Supply.                                                                                                                                            |  |  |  |  |

| 59      | CVDD18    | 1.8 V Clock Supply. CVDD18 supplies the power to the clock receivers and clock distribution.                                                                    |  |  |  |  |

| 60      | CVDD18    | 1.8 V Clock Supply. CVDD18 supplies the power to the clock receivers and clock distribution.                                                                    |  |  |  |  |

| 61      | DACCLKN   | DAC Clock Input, Negative.                                                                                                                                      |  |  |  |  |

| 62      | DACCLKP   | DAC Clock Input, Positive.                                                                                                                                      |  |  |  |  |

| 63      | CVDD18    | 1.8 V Clock Supply. CVDD18 supplies the power to the clock receivers and clock distribution.                                                                    |  |  |  |  |

| 64      | CVDD18    | 1.8 V Clock Supply. CVDD18 supplies the power to the clock receivers and clock distribution.                                                                    |  |  |  |  |

| 65      | AVDD33    | 3.3 V Analog Supply.                                                                                                                                            |  |  |  |  |

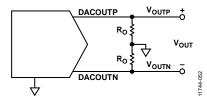

| 66      | DACOUTN   | DAC Current Output, Negative.                                                                                                                                   |  |  |  |  |

| 67      | DACOUTP   | DAC Current Output, Positive.                                                                                                                                   |  |  |  |  |

| 68      | AVDD33    | 3.3 V Analog Supply.                                                                                                                                            |  |  |  |  |

| 69      | FSADJ     | Full-Scale Current Output Adjust. Place a 10 $k\Omega$ resistor from this pin to AVSS.                                                                          |  |  |  |  |

| 70      | VREF      | Voltage Reference. Nominally 1.2 V output. Decouple VREF to AVSS.                                                                                               |  |  |  |  |

| 71      | CVDD18    | 1.8 V Clock Supply. Pin 71 supplies power to the clock receivers, clock multiplier, and clock distribution.                                                     |  |  |  |  |

| Pin No.                                                                  | Mnemonic | Description                                                                                              |  |  |  |

|--------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------|--|--|--|

| 72                                                                       | CVDD18   | BV Clock Supply. Pin 72 supplies power to the clock receivers, clock multiplier, and clock distribution. |  |  |  |

|                                                                          | EPAD     | Exposed Pad. The exposed pad (EPAD) must be soldered to the ground plane (AVSS, DVSS, CVSS). The EPAD    |  |  |  |

| provides an electrical, thermal, and mechanical connection to the board. |          | provides an electrical, thermal, and mechanical connection to the board.                                 |  |  |  |

## TYPICAL PERFORMANCE CHARACTERISTICS

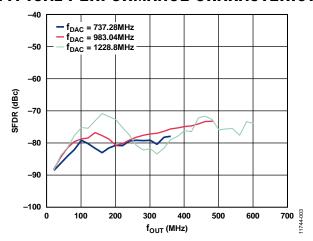

Figure 3. Single-Tone (0 dBFS) SFDR vs.  $f_{OUT}$  in the First Nyquist Zone over  $f_{DAC}$

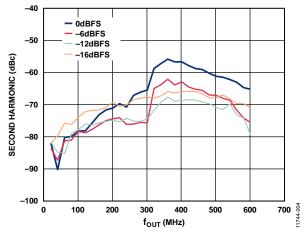

Figure 4. Single-Tone Second Harmonic vs.  $f_{OUT}$  in the First Nyquist Zone over Digital Back Off,  $f_{DAC} = 1228.8 \, \text{MHz}$

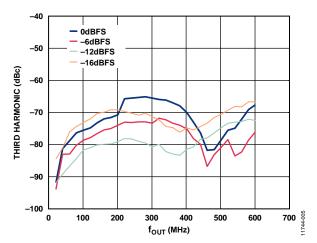

Figure 5. Single-Tone Third Harmonic vs.  $f_{OUT}$  in the First Nyquist Zone over Digital Back Off,  $f_{DAC} = 1228.8$  MHz

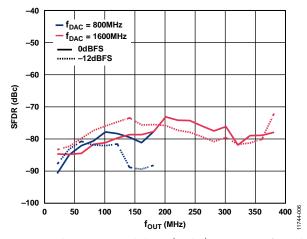

Figure 6. Single-Tone SFDR Excluding 2<sup>nd</sup> and 3<sup>rd</sup> Harmonics vs. f<sub>OUT</sub> in the First Nyquist Zone over f<sub>DAC</sub> and Digital Back Off

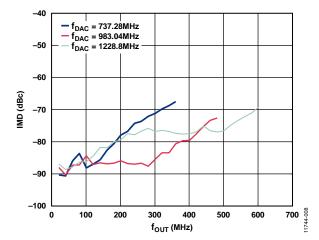

Figure 7. Two-Tone Third IMD vs. fout over fdac

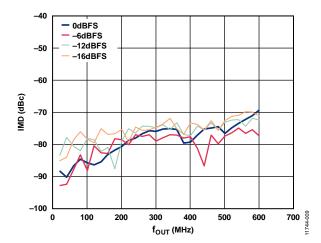

Figure 8. Two-Tone Third IMD vs.  $f_{OUT}$  over Digital Back Off,  $f_{DAC} = 1228.8 \text{ MHz}$

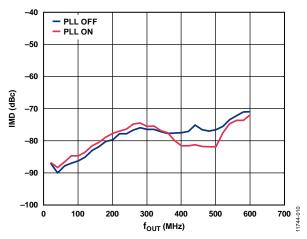

Figure 9. Two-Tone Third IMD vs.  $f_{OUT}$  over PLL on and off,  $f_{DAC} = 1228.8 \, \text{MHz}$

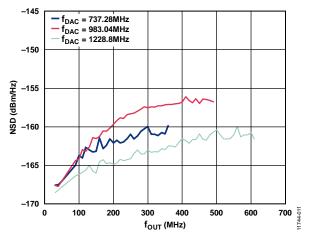

Figure 10. Single-Tone (0 dBFS) NSD vs.  $f_{OUT}$  over  $f_{DAC}$

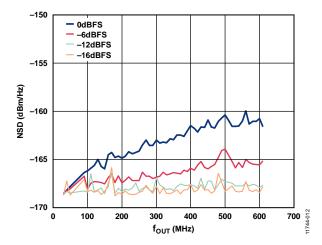

Figure 11. Single-Tone NSD vs.  $f_{OUT}$ , over Digital Back Off,  $f_{DAC} = 1228.8$  MHz

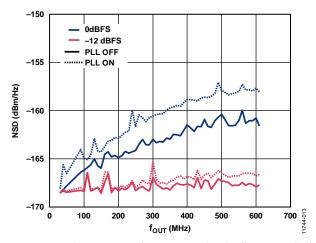

Figure 12. Single-Tone NSD vs.  $f_{\text{OUT}},$  over Digital Back Off, PLL on and off

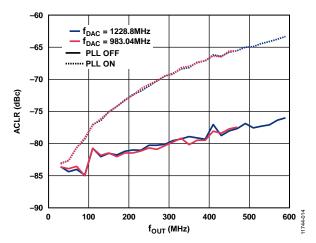

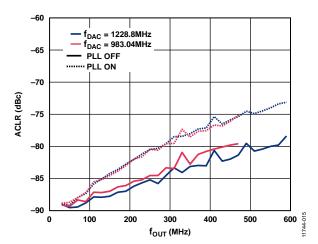

Figure 13. 1-Carrier WCDMA  $1^{\rm st}$  Adjacent ACLR vs.  $f_{\rm OUT}$  over  $f_{\rm DAC}$  PLL on and off

Figure 14. 1-Carrier WCDMA  $2^{nd}$  Adjacent ACLR vs.  $f_{OUT}$  over  $f_{DAC}$  PLL on and off

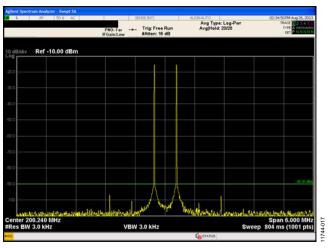

Figure 15. Two-Tone Third IMD Performance, IF = 200 MHz,  $f_{DAC}$  = 1228.8 MHz, -9 dBFS

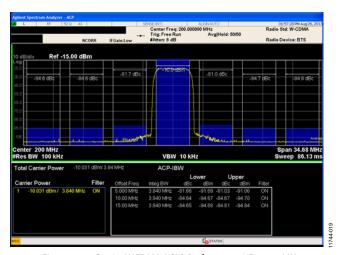

Figure 16. 1-Carrier WCDMA ACLR Performance, IF = 200 MHz,  $f_{\rm DAC}$  = 1228.8 MHz

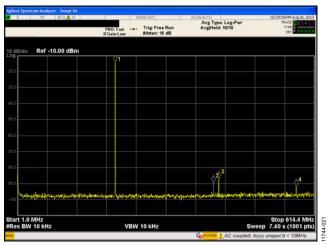

Figure 17. Single-Tone Performance, IF = 200 MH,  $f_{DAC}$  = 1228.8 MHz

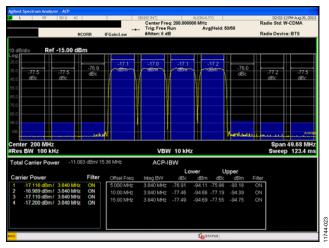

Figure 18. 4-Carrier WCDMA ACLR Performance, IF = 200 MHz,  $f_{\rm DAC}$  = 1228.8 MHz

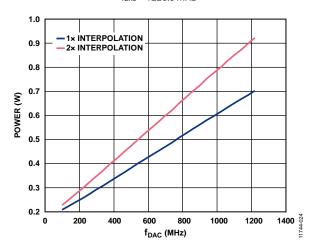

Figure 19. Total Power Consumption vs. f<sub>DAC</sub> over Interpolation

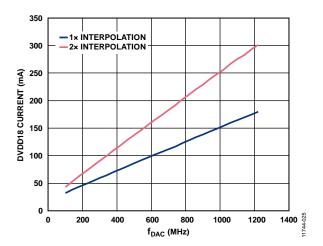

Figure 20. DVDD18 Current vs.  $f_{DAC}$  over Interpolation

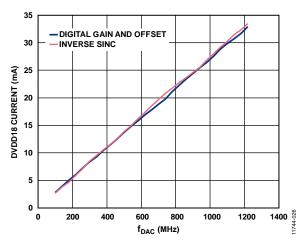

Figure 21. DVDD18 Current vs.  $f_{DAC}$  over Digital Functions

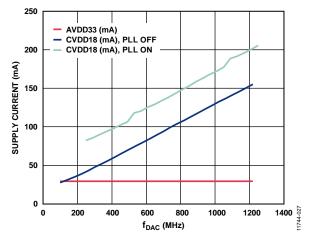

Figure 22. CVDD18 and AVDD18 Current vs. f<sub>DAC</sub>

## **TERMINOLOGY**

#### Integral Nonlinearity (INL)

INL is the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero scale to full scale.

#### Differential Nonlinearity (DNL)

DNL is the measure of the variation in analog value, normalized to full scale, associated with a 1 LSB change in digital input code.

#### **Offset Error**

Offset error is the deviation of the output current from the ideal of 0 mA. For DACOUTP, 0 mA output is expected when all inputs are set to 0. For DACOUTN, 0 mA output is expected when all inputs are set to 1.

#### **Gain Error**

Gain error is the difference between the actual and ideal output span. The actual span is determined by the difference between the output when all inputs are set to 1 and the output when all inputs are set to 0.

#### **Output Compliance Range**

The output compliance range is the range of allowable voltage at the output of a current output DAC. Operation beyond the maximum compliance limits can cause either output stage saturation or breakdown, resulting in nonlinear performance.

#### **Temperature Drift**

Temperature drift is specified as the maximum change from the ambient (25°C) value to the value at either  $T_{\text{MIN}}$  or  $T_{\text{MAX}}$ . For offset and gain drift, the drift is reported in ppm of full-scale range (FSR) per degree Celsius. For reference drift, the drift is reported in ppm per degree Celsius.

#### Power Supply Rejection (PSR)

PSR is the maximum change in the full-scale output as the supplies are varied from minimum to maximum specified voltages.

#### **Settling Time**

Settling time is the time required for the output to reach and remain within a specified error band around its final value, measured from the start of the output transition.

#### Spurious Free Dynamic Range (SFDR)

SFDR is the difference, in decibels, between the peak amplitude of the output signal and the peak spurious signal within the dc to Nyquist frequency of the DAC. Typically, the interpolation filters reject energy in this band. This specification, therefore, defines how well the interpolation filters work and the effect of other parasitic coupling paths on the DAC output.

#### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the measured output signal to the rms sum of all other spectral components below the Nyquist frequency, excluding the first six harmonics and dc. The value for SNR is expressed in decibels.

#### **Interpolation Filter**

If the digital inputs to the DAC are sampled at a multiple rate of  $f_{DATA}$  (interpolation rate), a digital filter can be constructed that has a sharp transition band near  $f_{DATA}/2$ . Images that typically appear around  $f_{DAC}$  (output data rate) can be greatly suppressed.

#### Adjacent Channel Leakage Ratio (ACLR)

ACLR is the ratio in decibels relative to the carrier (dBc) between the measured power within a channel relative to its adjacent channel.

#### **Complex Image Rejection**

In a traditional two-part upconversion, two images are created around the second IF frequency. These images have the effect of wasting transmitter power and system bandwidth. By placing the real part of a second complex modulator in series with the first complex modulator, either the upper or lower frequency image near the second IF can be rejected.

## SERIAL PORT OPERATION

The serial port is a flexible, synchronous serial communications port that allows easy interfacing to many industry standard microcontrollers and microprocessors. The serial I/O is compatible with most synchronous transfer formats, including both the Motorola SPI and Intel® SSR protocols. The interface allows read/write access to all registers that configure the AD9139. MSB first or LSB first transfer formats are supported. The serial port interface is a 3-wire only interface. The input and output share a single input/output (SDIO) pin.

Figure 23. Serial Port Interface Pins

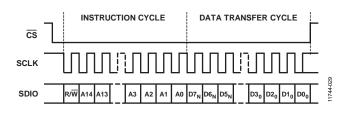

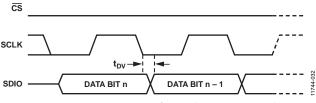

There are two phases to a communication cycle with the AD9139. Phase 1 is the instruction cycle (the writing of an instruction byte into the device), coincident with the first 16 SCLK rising edges. The instruction word provides the serial port controller with information regarding the data transfer cycle, Phase 2, of the communication cycle. The Phase 1 instruction word defines whether the upcoming data transfer is a read or write, together with the starting register address for the following data transfer.

A logic high on the  $\overline{\text{CS}}$  pin, followed by a logic low, resets the serial port timing to the initial state of the instruction cycle. From this state, the next 16 rising SCLK edges represent the instruction bits of the current I/O operation.

The remaining SCLK edges are for Phase 2 of the communication cycle. Phase 2 is the actual data transfer between the device and the system controller. Phase 2 of the communication cycle is a transfer of one data byte. Registers change immediately upon writing to the last bit of each transfer byte.

#### **DATA FORMAT**

The instruction byte contains the information shown in Table 9.

**Table 9. Serial Port Instruction Word**

| I15 (MSB)        | I[14:0] |

|------------------|---------|

| $R/\overline{W}$ | A[14:0] |

$R/\overline{W}$  (Bit 15 of the instruction word) determines whether a read or a write data transfer occurs after the instruction word write. Logic 1 indicates a read operation, and Logic 0 indicates a write operation.

A14 to A0 (Bit 14 to Bit 0 of the instruction word) determine the register that is accessed during the data transfer portion of the communication cycle. For multibyte transfers, A14 is the starting address; the device generates the remaining register addresses based on the SPI\_LSB\_FIRST bit.

#### **SERIAL PORT PIN DESCRIPTIONS**

#### Serial Clock (SCLK)

The serial clock pin, SCLK, synchronizes data to and from the device and runs the internal state machines. The maximum frequency of SCLK is 40 MHz. All data input is read on the rising edge of SCLK. All data is driven out on the falling edge of SCLK.

### Chip Select (CS)

$\overline{\text{CS}}$  is an active low input that starts and gates a communication cycle. It allows the use of multiple devices on the same serial communications line. The SDIO pin enters a high impedance state when the  $\overline{\text{CS}}$  input is high. During the communication cycle,  $\overline{\text{CS}}$  remains low.

#### Serial Data I/O (SDIO)

The SDIO pin is a bidirectional data line.

#### **SERIAL PORT OPTIONS**

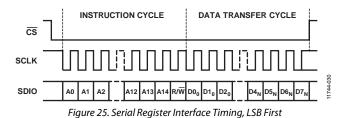

The serial port supports both MSB first and LSB first data formats; the SPI\_LSB\_FIRST bit (Register 0x00, Bit 6) controls this functionality. The default is MSB first (SPI\_LSB\_FIRST = 0).

When SPI\_LSB\_FIRST = 0 (MSB first), the instruction and data bits must be written from MSB to LSB. Multibyte data transfers in MSB first format start with an instruction word that includes the register address of the most significant data byte. Subsequent data bytes must follow from high address to low address. In MSB first mode, the serial port internal word address generator decrements for each data byte of the multibyte communication cycle.

When SPI\_LSB\_FIRST = 1 (LSB first), the instruction and data bits must be written from LSB to MSB. Multibyte data transfers in LSB first format start with an instruction word that includes the register address of the least significant data byte. Subsequent data bytes must follow from low address to high address. In LSB first mode, the serial port internal word address generator increments for each data byte of the multibyte communication cycle.

When the MSB first mode is active, the serial port controller data address decrements from the data address written toward 0x00 for multibyte I/O operations. If the LSB first mode is active, the serial port controller data address increments from the data address written toward 0xFF for multibyte I/O operations.

Figure 24. Serial Register Interface Timing, MSB First

cs -t<sub>PWH</sub>-▶ SDIO **INSTRUCTION BIT 15** INSTRUCTION BIT 14

Figure 26. Timing Diagram for Serial Port Register Write

Figure 27. Timing Diagram for Serial Port Register Read

## DATA INTERFACE

#### LVDS INPUT DATA PORTS

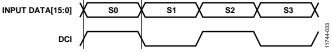

The AD9139 has a 16-bit LVDS bus that accepts 16-bit data either in word wide (16-bit) or byte wide (8-bit) formats. In the word wide interface mode, the data is sent over the entire 16-bit data bus. In the byte wide interface mode, the data is sent over the lower 8-bit (D7 to D0) LVDS bus. Table 10 lists the pin assignment of the bus and the SPI register configuration for each mode.

**Table 10. LVDS Input Data Modes**

| Interface Mode | Input Data<br>Width | SPI Register Configuration    |

|----------------|---------------------|-------------------------------|

| Word           | D15 to D0           | Register $0x26$ , Bit $0 = 0$ |

| Byte           | D7 to D0            | Register $0x26$ , Bit $0 = 1$ |

#### **WORD INTERFACE MODE**

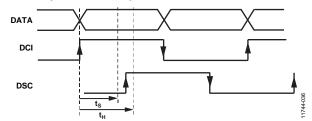

In word mode, the digital clock input (DCI) signal is a reference bit that generates a double data rate (DDR) data sampling clock. Time align the DCI signal with the data.

AD9139 WORD MODE

Figure 28. AD9139 Timing Diagram for Word Mode

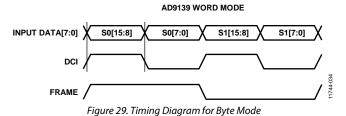

#### BYTE INTERFACE MODE

In byte mode, the required sequence of the input data stream is S0[15:8], S0[7:0], S1[15:8], S1[7:0], and so forth. A frame signal is required to align the order of input data bytes properly. Time align both the DCI signal and frame signal with the data. The rising edge of the frame indicates the start of the sequence. The frame can be either a one shot or periodical signal as long as its first rising edge is correctly captured by the device. For a one shot frame, the frame pulse must be held at high for at least one DCI cycle. For a periodical frame, the frequency must be

$$f_{DCI}/(2 \times n)$$

where n is a positive integer, that is, 1, 2, 3, ...

Figure 29 is an example of signal timing in byte mode.

#### **DATA INTERFACE CONFIGURATION OPTIONS**

To provide more flexibility for the data interface, additional options are listed in Table 11.

**Table 11. Data Interface Configuration Options**

|                      | 8                                                  |  |  |  |  |  |  |

|----------------------|----------------------------------------------------|--|--|--|--|--|--|

| Register 0x26, Bit 7 | Description                                        |  |  |  |  |  |  |

| DATA_FORMAT          | Select between binary and twos complement formats. |  |  |  |  |  |  |

#### **DLL INTERFACE MODE**

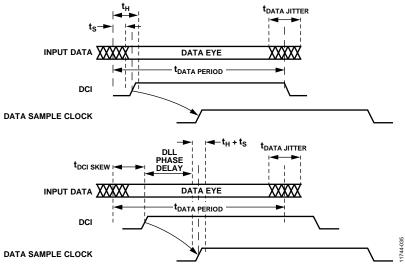

A source synchronous LVDS interface is used between the data host and the AD9139 to achieve high data rates while simplifying the interface. The FPGA or ASIC feeds the AD9139 with 16-bit input data. Together with the input data, the FPGA or ASIC provides a DDR DCI.

A delay locked loop (DLL) circuit, designed to operate with DCI clock rates between 250 MHz and 575 MHz, generates a phase shifted version of the DCI signal, called a data sampling clock (DSC), to register the input data on both the rising and falling edges.

As shown in Figure 31, the DCI clock edges must be coincident with the data bit transitions with minimum skew and jitter. The nominal sampling point of the input data occurs in the middle of the DCI clock edges because this point corresponds to the center of the data eye. This is also equivalent to a nominal phase shift of 90° of the DCI clock.

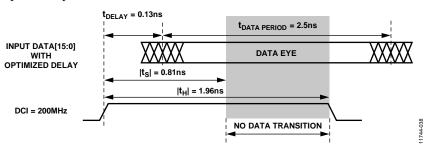

The data timing requirements are defined by a data valid window (DVW) that is dependent on the data clock input skew, input data jitter, and the variations of the DLL delay line across delay settings. The DVW is defined as

$$DVW = t_{DATA\ PERIOD} - t_{DATA\ SKEW} - t_{DATA\ JITTER}$$

The available margin for data interface timing is given by

$$t_{MARGIN} = DVW - (t_S + t_H)$$

The difference of the setup and hold times, which is also called the keep out window, or KOW, is the area where data transitions are prohibited. The timing margin allows the user to set the DLL delay, as shown in Figure 30.

Figure 30. LVDS Data Port Timing Requirements

Figure 30 shows that the ideal location for the DSC signal is 90° out of phase from the DCI input; however, due to skew of the DCI relative to the data, it may be necessary to change the DSC phase offset to sample the data at the center of its eye diagram. Vary the sampling instance in discrete increments by offsetting the nominal DLL phase shift value of 90° via Register 0x0A, Bits[3:0]. This register is a signed value. The MSB is the sign and the LSBs are the magnitude. The following equation defines the phase offset relationship:

*Phase Offset* =

$$90^{\circ} + n \times 11.25^{\circ}$$

,  $|n| < 7$

where n is the DLL phase offset setting.

Figure 31 shows the DSC setup and hold times with respect to the DCI signal and data signals.

Figure 31. LVDS Data Port Setup and Hold Times

Table 12 lists the guaranteed values across the operating conditions. These values were obtained using a 50% duty cycle and a DCI swing of 450 mV p-p. For best performance, maintain a duty cycle variation below  $\pm 5\%$  and set the DCI input as high as possible, up to 1200 mV p-p.

Table 12. DLL Phase Setup and Hold Times (Guaranteed)

| Frequency,             |                | Data Port S | Port Setup and Hold Times (ps)<br>at DLL Phase |      |  |  |

|------------------------|----------------|-------------|------------------------------------------------|------|--|--|

| f <sub>DCI</sub> (MHz) | Time (ps)      | -3          | 0                                              | +3   |  |  |

| 307                    | <b>t</b> s     | -125        | -385                                           | -695 |  |  |

|                        | t <sub>H</sub> | 834         | 1120                                           | 1417 |  |  |

| 368                    | <b>t</b> s     | -70         | -305                                           | -534 |  |  |

|                        | t <sub>H</sub> | 753         | 967                                            | 1207 |  |  |

| 491                    | t <sub>s</sub> | -81         | -245                                           | -402 |  |  |

|                        | t <sub>H</sub> | 601         | 762                                            | 928  |  |  |

| 614                    | ts             | -54.0       | -167                                           | -277 |  |  |

|                        | t <sub>H</sub> | 497         | 603                                            | 721  |  |  |

Table 13. DLL Phase Setup and Hold Times (Typical)

| Frequency,                 |                |     |      |      | Da   | ata Port | Setup ar | nd Hold | Times (p | s) at DLL | Phase |       |       |       |

|----------------------------|----------------|-----|------|------|------|----------|----------|---------|----------|-----------|-------|-------|-------|-------|

| fDCI <sup>1</sup><br>(MHz) | Time<br>(ps)   | -6  | -5   | -4   | -3   | -2       | -1       | 0       | +1       | +2        | +3    | +4    | +5    | +6    |

| 250                        | ts             | -93 | -196 | -312 | -416 | -530     | -658     | -770    | -878     | -983      | -1093 | -1193 | -1289 | -1412 |

|                            | t <sub>H</sub> | 468 | 579  | 707  | 825  | 947      | 1067     | 1188    | 1315     | 1442      | 1570  | 1697  | 1777  | 1876  |

| 275                        | ts             | -87 | -172 | -264 | -364 | -464     | -556     | -653    | -756     | -859      | -956  | -1053 | -1151 | -1251 |

|                            | t <sub>H</sub> | 451 | 537  | 646  | 757  | 878      | 977      | 1092    | 1218     | 1311      | 1423  | 1537  | 1653  | 1728  |

| 300                        | ts             | -82 | -166 | -256 | -341 | -426     | -515     | -622    | -715     | -809      | -900  | -1001 | -1097 | -1184 |

|                            | t <sub>H</sub> | 422 | 500  | 598  | 703  | 803      | 897      | 1000    | 1105     | 1203      | 1303  | 1411  | 1522  | 1612  |

| 325                        | t <sub>s</sub> | -46 | -114 | -190 | -271 | -358     | -447     | -538    | -612     | -706      | -806  | -891  | -966  | -1044 |

|                            | t <sub>H</sub> | 405 | 483  | 563  | 647  | 740      | 832      | 914     | 1000     | 1100      | 1200  | 1292  | 1380  | 1476  |

| 350                        | ts             | -23 | -92  | -180 | -252 | -328     | -409     | -491    | -574     | -654      | -731  | -819  | -889  | -959  |

|                            | t <sub>H</sub> | 383 | 451  | 524  | 607  | 682      | 762      | 844     | 930      | 1011      | 1097  | 1186  | 1277  | 1358  |

| 375                        | ts             | -7  | -82  | -150 | -225 | -315     | -391     | -461    | -526     | -595      | -661  | -726  | -786  | -853  |

|                            | t <sub>H</sub> | 401 | 466  | 504  | 569  | 641      | 718      | 783     | 863      | 941       | 1025  | 1106  | 1187  | 1264  |

| 400                        | ts             | -46 | -98  | -161 | -243 | -303     | -384     | -448    | -513     | -578      | -643  | -713  | -771  | -833  |

|                            | t <sub>H</sub> | 385 | 445  | 503  | 546  | 604      | 674      | 748     | 826      | 890       | 965   | 1039  | 1110  | 1178  |

| 425                        | ts             | 4   | -52  | -110 | -170 | -229     | -297     | -394    | -449     | -517      | -579  | -641  | -704  | -752  |

|                            | t <sub>H</sub> | 358 | 408  | 465  | 524  | 595      | 625      | 692     | 762      | 829       | 900   | 966   | 1032  | 1097  |

| 450                        | ts             | 11  | -34  | -92  | -147 | -209     | -269     | -324    | -386     | -446      | -509  | -564  | -622  | -672  |

|                            | t <sub>H</sub> | 354 | 406  | 457  | 516  | 573      | 637      | 693     | 731      | 792       | 852   | 917   | 983   | 1042  |

| 475                        | ts             | -15 | -51  | -95  | -147 | -198     | -255     | -313    | -366     | -425      | -480  | -530  | -585  | -640  |

|                            | t <sub>H</sub> | 355 | 399  | 451  | 499  | 556      | 613      | 675     | 727      | 779       | 815   | 873   | 930   | 988   |

| 500                        | ts             | 9   | -28  | -77  | -128 | -183     | -233     | -288    | -333     | -390      | -438  | -495  | -545  | -594  |

|                            | t <sub>H</sub> | 313 | 354  | 399  | 445  | 500      | 555      | 615     | 668      | 726       | 783   | 825   | 881   | 934   |

| 525                        | ts             | -7  | -52  | -100 | -147 | -187     | -237     | -285    | -335     | -387      | -436  | -483  | -530  | -581  |

|                            | t <sub>H</sub> | 311 | 356  | 395  | 438  | 489      | 537      | 592     | 645      | 692       | 746   | 799   | 850   | 909   |

| 550                        | ts             | -5  | -39  | -74  | -107 | -147     | -192     | -249    | -302     | -352      | -397  | -440  | -486  | -529  |

|                            | t <sub>H</sub> | 300 | 340  | 378  | 423  | 468      | 510      | 560     | 610      | 659       | 710   | 756   | 810   | 865   |

| 575                        | ts             | 8   | -28  | -66  | -102 | -143     | -181     | -245    | -280     | -336      | -366  | -406  | -443  | -488  |

|                            | t <sub>H</sub> | 312 | 348  | 379  | 414  | 453      | 496      | 544     | 599      | 654       | 708   | 759   | 806   | 847   |

<sup>&</sup>lt;sup>1</sup> Table 13 shows characterization data for selected  $f_{DG}$  frequencies. Other frequencies are possible; use Table 13 to estimate performance.

Table 13 shows the typical times for various DCI clock frequencies that are required to calculate the data valid margin. Use Table 13 to determine the amount of margin that is available for tuning of the DSC sampling point.

Maximizing the opening of the eye in both the DCI and data signals improves the reliability of the data port interface. Use differential controlled impedance traces of equal length (that is, delay) between the host processor and the AD9139 input. To ensure coincident transitions with the data bits, implement the DCI signal as an additional data line with an alternating (010101...) bit sequence from the same output drivers that are used for the data.

The DCI signal is ac-coupled by default; thus, removing the DCI signal may cause DAC output chatter due to randomness on the DCI input. To avoid this, disable the DAC output whenever the DCI signal is not present by setting the DAC output current power-down bit in Register 0x01[7] to 1. When the DCI signal is again present, enable the DAC output by programming Register 0x01[7] to 0.

Register 0x0D optimizes the DLL stability over the operating frequency range. Table 14 shows the recommended settings.

**Table 14. DLL Configuration Options**

| DCI Speed | Register 0x0D |

|-----------|---------------|

| ≥350 MHz  | 0x06          |

| <350 MHz  | 0x86          |

Poll the status of the DLL by reading the data status register at Address 0x0E. Bit 0 indicates that the DLL is running and attempting lock; Bit 7 is 1 when the DLL has locked. Bit 2 is 1 when a valid data clock input (DCI) is detected. The warning bits in [6:4] in Register 0x0E can be used as indicators that the DAC may be operating in a nonideal location in the delay line. Note that these bits are read at the SPI port speed, which is much slower than the actual speed of the DLL. This means they can only show a snapshot of what is happening as opposed to giving real-time feedback.

#### **DLL Configuration Example 1**

In the following DLL configuration example,  $f_{DCI} = 600$  MHz, DLL is enabled, and DLL phase offset = 0.

- 1.  $0x5E \rightarrow 0xFE /* Turn off LSB delay cell*/$

- 0x0D → 0x06 /\* Select DLL configure options \*/

- 3.  $0x0A \rightarrow 0xC0$  /\* Enable DLL and duty cycle correction. Set DLL phase offset to 0 \*/

- 4. Read 0x0E[7:4] /\* Expect 1000b if the DLL is locked \*/

#### **DLL Configuration Example 2**

In the following DLL configuration example,  $f_{\rm DCI} = 300$  MHz, DLL is enable, and DLL phase offset = 0.

- 1.  $0x5E \rightarrow 0xFE$  /\* Turn off LSB delay cell\*/

- 2.  $0x0D \rightarrow 0x86$  /\* Select DLL configure options \*/

- 3.  $0x0A \rightarrow 0xC0$  /\* Enable DLL and duty cycle correction. Set DLL phase offset to 0 \*/

- 4. Read 0x0E[7:4] /\* Expect 1000b if the DLL

is locked \*/

#### **PARITY**

The data interface can be continuously monitored by enabling the parity bit feature in Register 0x6A[7] and configuring the frame/parity bit as parity by setting Register 0x09 = 0x21. In this case, the host sends a parity bit with each data sample. This bit is set according to the following formulas, where n is the data sample that is being checked:

For even parity,

XOR[FRM(n), D0(n), D1(n), D2(n), ..., D15(n)] = 0For odd parity,

XOR[FRM(n), D0(n), D1(n), D2(n), ..., D15(n)] = 1

The parity bit is calculated over 17 bits (including the frame/parity bit).

If a parity error occurs, the parity error counter (Register 0x6B or Register 0x6C) increments. Parity errors on the bits sampled by the rising edge of the DCI signal increment the rising edge parity counter (Register 0x6B) and set the PARERRRIS bit (Register 0x6A[0]). Parity errors on the bits sampled by the falling edge of DCI increment the falling edge parity counter (Register 0x6C) and set the PARERRFAL bit (Register 0x6A[1]). The parity counter continues to accumulate until it clears or until it reaches a maximum value of 255. To clear the count, write a 1 to Register 0x6A[5].

To trigger an IRQ when a parity error occurs, write 1 to Bit 7 in Register 0x04. This IRQ triggers when there is either a rising edge or falling edge parity error. Observe the status of the IRQ pin via Register 0x06[7] or by using the selected  $\overline{\text{IRQx}}$  pin. Clear the IRQ by writing a 1 to Register 0x06[7].

Use the parity bit feature to validate the interface timing. As described previously, the host provides a parity bit with the data

samples, as well as configures the AD9139 to generate an IRQ. The user can then sweep the sampling instance of the input registers of the AD9139 to determine at what point sampling errors occur. The sampling instance can be varied in discrete increments by offsetting the nominal DLL phase shift value of 90° via SPI Register 0x0A[3:0].

#### **SED OPERATION**

The AD9139 provides on-chip sample error detection (SED) circuitry that simplifies verification of the input data interface. The SED compares the input data samples captured at the digital input pins with a set of comparison values. The comparison values are loaded into registers through the SPI port. Differences between the captured values and the comparison values are detected. Options are available for customizing SED test sequencing and error handling.

The SED circuitry allows the application to test a short user defined pattern to confirm that the high speed source synchronous data bus is correctly implemented and meets the timing requirement. Unlike the parity bit, the SED circuitry is expected to be used during initial system calibration, before the AD9139 is in use in the application. The SED circuitry operates on a data set made up of user defined input words, denoted as S0, S1, S2, and S3. The user defined pattern consists of sequential data-word samples (S0 is sampled on the rising edge of DCI, S1 is sampled on the following falling edge of DCI, S2 is sampled on the following DCI rising edge, and S3 is sampled on the following DCI falling edge). The user loads this data pattern in the byte format into Register 0x61 through Register 0x68.

The depth of the user defined pattern is selectable via Bit 4 of the SED\_CTRL register (0x60). A default of 0, means a depth of two (using S0 and S1), and a 1 means a depth of four (using S0, S1, S2, and S3, and requiring the use of frame signal input to define S0 to the SED state machine). To properly align the input samples using a depth of 4, S0 is indicated by asserting the frame signal for a minimum of two complete input samples as shown in. The frame signal can be issued once at the start of the data transmission, or it can be asserted repeatedly at intervals coinciding with the S0 word.

Figure 32. Timing Diagram of Extended FRAMEx Signal Required to Align Input Data for SED

The SED has three flag bits (Register 0x60, Bit 0, Bit 1, and Bit 2) that indicate the results of the input sample comparisons. The sample error detected bit (Register 0x60, Bit 0) is set when an error is detected and remains set until cleared.

The autosample error detection (AED) mode is an autoclear mode that has two effects: it activates the compare fail bit and the compare pass bit (Register 0x60, Bit 1 and Bit 2). The compare pass bit sets if the last comparison indicated the sample was error free. The compare fail bit sets if an error is

detected. The compare fail bit is automatically cleared by the reception of eight consecutive error free comparisons when autoclear mode is enabled.

The sample error flag can be configured to trigger an  $\overline{IRQ}$  when active, if desired, by enabling the appropriate bit in the event flag register (Register 0x04, Bit 6).

#### **SED EXAMPLE**

#### **Normal Operation**

The following example illustrates the AD9139 SED configuration for continuously monitoring the input data and assertion of an  $\overline{IRQ}$  when a single error is detected.

- Write to the following registers to enable the SED and load the comparison values with a four-deep user pattern.

Comparison values can be chosen arbitrarily; however, choosing values that require frequent bit toggling provides the most robust test.

- a. Register  $0x61[7:0] \rightarrow S0[7:0]$

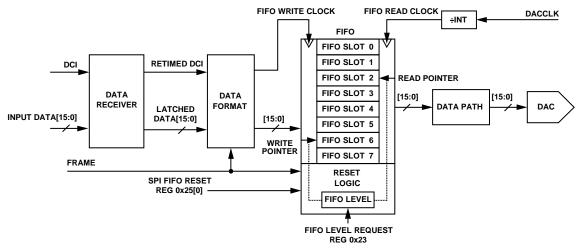

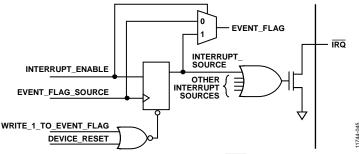

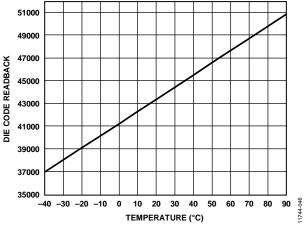

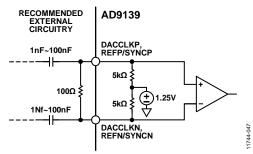

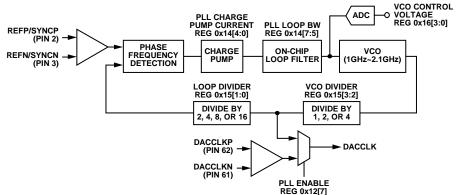

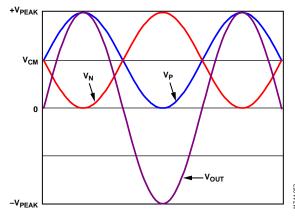

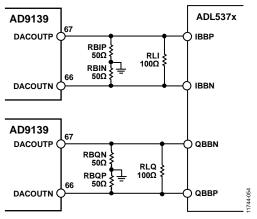

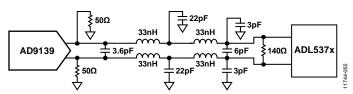

- b. Register  $0x62[7:0] \rightarrow S0[15:8]$