# Quad Input, 10-Output, Dual DPLL/IEEE 1588, 1 pps Synchronizer and Jitter Cleaner

Data Sheet AD9545

#### **FEATURES**

Dual DPLL synchronizes 1 Hz to 750 MHz physical layer clocks, providing frequency translation with jitter cleaning of noisy references

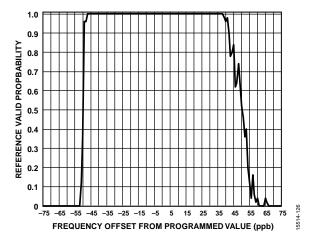

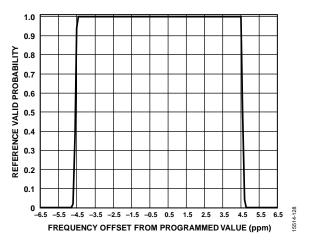

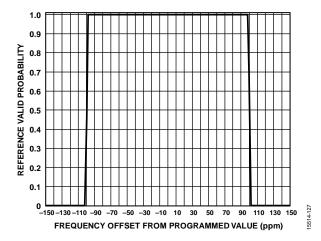

Complies with ITU-T G.8262 and Telcordia GR-253 Supports Telcordia GR-1244, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2 Continuous frequency monitoring and reference validation for frequency deviation as low as 50 ppb ( $5 \times 10^{-8}$ ) Both DPLLs feature a 24-bit fractional divider with 24-bit programmable modulus

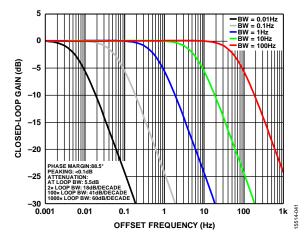

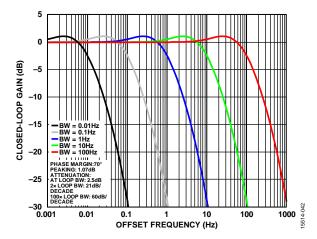

Programmable digital loop filter bandwidth:  $10^{-4}$  Hz to 1850 Hz 2 independent, programmable auxiliary NCOs (1 Hz to 65,535 Hz, resolution < 1.37  $\times$   $10^{-12}$  Hz), suitable for IEEE 1588 Version 2 servo feedback in PTP applications

Automatic and manual holdover and reference switchover, providing zero delay, hitless, or phase buildout operation Programmable priority-based reference switching with

manual, automatic revertive, and automatic nonrevertive modes supported

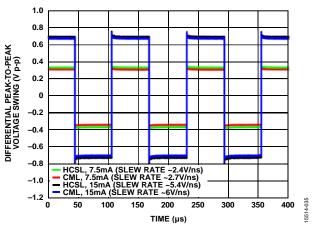

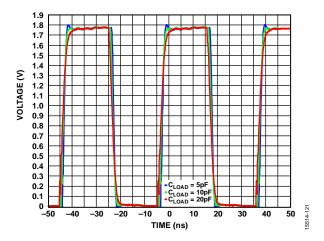

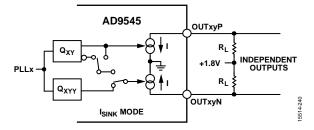

5 pairs of clock output pins with each pair useable as differential LVDS/HCSL/CML or as 2 single-ended outputs (1 Hz to 500 MHz)

2 differential or 4 single-ended input references Crosspoint mux interconnects reference inputs to PLLs Supports embedded (modulated) input/output clock signals Fast DPLL locking modes

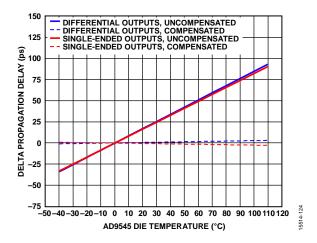

Provides internal capability to combine the low phase noise of a crystal resonator or crystal oscillator with the frequency stability and accuracy of a TCXO or OCXO External EEPROM support for autonomous initialization Single 1.8 V power supply operation with internal regulation Built in temperature monitor and alarm and temperature compensation for enhanced zero delay performance

#### **APPLICATIONS**

Global positioning system (GPS), PTP (IEEE 1588), and synchronous Ethernet (SyncE) jitter cleanup and synchronization

Optical transport networks (OTN), synchronous digital hierarchy (SDH), and macro and small cell base stations Small base station clocking, including baseband and radio Stratum 2, Stratum 3e, and Stratum 3 holdover, jitter cleanup, and phase transient control

JESD204B support for analog-to-digital converter (ADC) and digital-to-analog converter (DAC) clocking

**Cable infrastructures**

**Carrier Ethernet**

#### **GENERAL DESCRIPTION**

The AD9545 supports existing and emerging International Telecommunications Union (ITU) standards for the delivery of frequency, phase, and time of day over service provider packet networks, including ITU-G.8262, ITU-T G.812, ITU-T G.813, ITU-T G.823, ITU-T G.824, ITU-T G.825, and ITU-T G.8273.2.

The 10 clock outputs of the AD9545 are synchronized to any one of up to four input references. The digital phase-locked loops (DPLLs) reduce timing jitter associated with the external references. The digitally controlled loop and holdover circuitry continuously generate a low jitter output signal, even when all reference inputs fail.

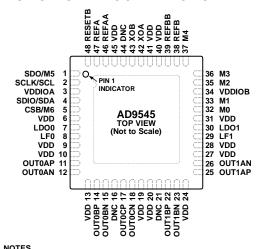

The AD9545 is available in a 48-lead LFCSP (7 mm  $\times$  7 mm) package and operates over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

Note that throughout this data sheet, multifunction pins, such as SDO/M5, are referred to either by the entire pin name or by a single function of the pin, for example, M5, when only that function is relevant.

# **TABLE OF CONTENTS**

| Features                                              | Pin Configuration and Function Descriptions | 37 |

|-------------------------------------------------------|---------------------------------------------|----|

| Applications1                                         | Typical Performance Characteristics         | 39 |

| General Description1                                  | Terminology                                 | 44 |

| Revision History 5                                    | Theory of Operation                         | 45 |

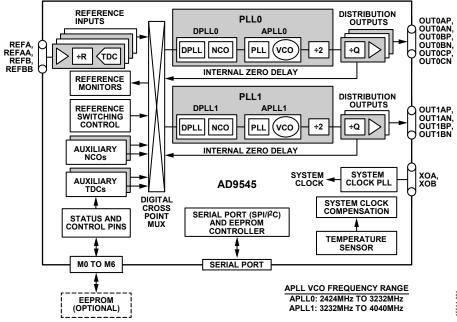

| Functional Block Diagram8                             | Input/Output Termination Recommendations    | 46 |

| Specifications9                                       | System Clock Inputs                         | 46 |

| Operating Temperature9                                | Reference Clock Inputs                      | 46 |

| Supply Voltage9                                       | Clock Outputs                               | 47 |

| Supply Current9                                       | System Clock PLL                            | 49 |

| Power Dissipation                                     | System Clock PLL Overview                   | 49 |

| System Clock Inputs, XOA and XOB11                    | System Clock Input Frequency Declaration    | 49 |

| Reference Inputs                                      | System Clock Source                         | 49 |

| Reference to Reference Coupling14                     | Prescale Divider                            | 50 |

| Reference to Mx Pin Input Timing Skew                 | Feedback Divider                            | 50 |

| Reference Monitors                                    | System Clock PLL Output Frequency           | 50 |

| Distribution Clock Outputs                            | System Clock PLL Lock Detector              | 50 |

| Output to Output Timing Skew21                        | System Clock Stability Timer                | 50 |

| Output Timing Skew Between Mx Pins and OUTxyP and/or  | System Clock Calibration                    | 50 |

| OUTxyN Pins22                                         | System Clock Stability Compensation         | 51 |

| Time Duration of Digital Functions                    | Reference Clock Input Receivers             | 52 |

| DPLL0 and DPLL1 Specifications23                      | Reference Clock Receivers Overview          | 52 |

| DPLL Lock Detection Specifications23                  | Single-Ended Mode                           | 52 |

| DPLL Phase Characteristics24                          | Differential Mode                           | 52 |

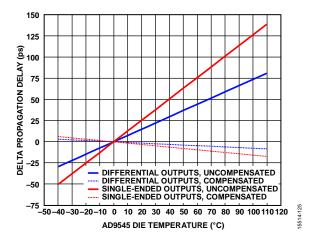

| DPLL Propagation Delay25                              | Reference Dividers (R-Dividers)             | 54 |

| DPLL Propagation Delay Variation25                    | Reference Monitor                           | 55 |

| Holdover Specifications                               | Reference Monitor Overview                  | 55 |

| Analog PLL (APLL0 and APLL1) Specifications26         | Reference Monitor State Machine             | 56 |

| Output Channel Divider Specifications26               | Reference Monitor Controls                  | 56 |

| Auxiliary Circuit Specifications                      | Monitor Time Base                           | 58 |

| Mx to Mx Pin Output Timing Skew27                     | Reference Period Jitter Estimation          | 58 |

| System Clock Compensation Specifications28            | Reference Monitor Decision Time             | 58 |

| Temperature Sensor Specifications                     | Reference Validation                        | 58 |

| Logic Input Specifications (RESETB, M0 to M6 Pins) 28 | Reference Monitor Reset                     | 59 |

| Logic Output Specifications (M0 to M6 Pins)29         | Reference Demodulator                       | 60 |

| Serial Port Specifications30                          | Reference Demodulator Overview              | 60 |

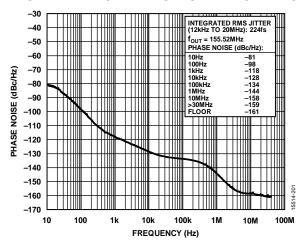

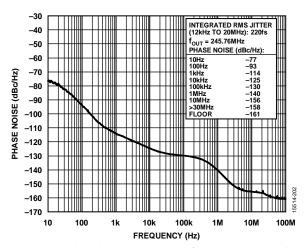

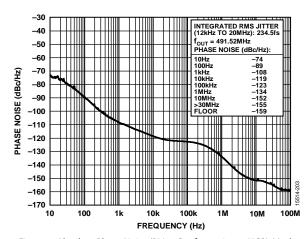

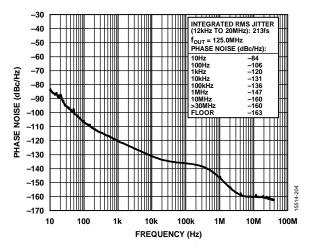

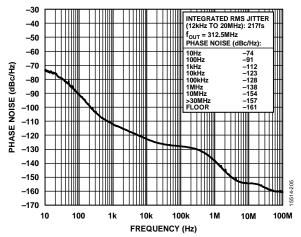

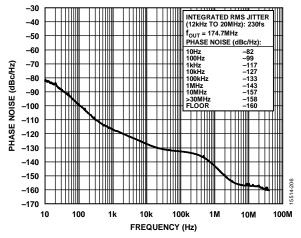

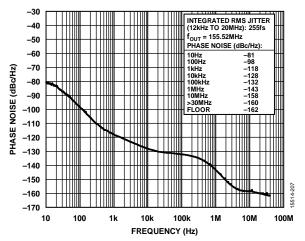

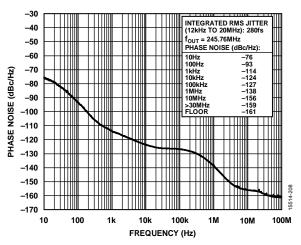

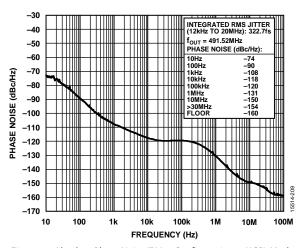

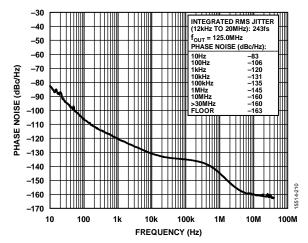

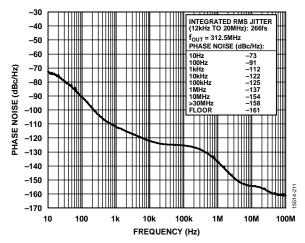

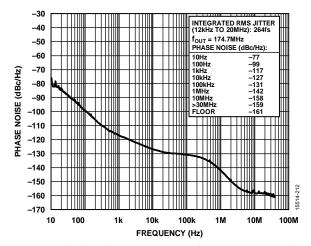

| Jitter Generation (Random Jitter)32                   | Demodulator Enable                          | 60 |

| Phase Noise                                           | Demodulator Delay                           | 61 |

| Absolute Maximum Ratings                              | Demodulator Polarity                        |    |

| Thermal Resistance                                    | Automatic Polarity Detection                |    |

| ESD Caution                                           | Demodulator Sensitivity                     | 61 |

|                                                       |                                             |    |

| Demodulator Persistence62                       | Profile Enable                        | 85  |

|-------------------------------------------------|---------------------------------------|-----|

| Demodulator Bandwidth62                         | Profile Priority                      | 85  |

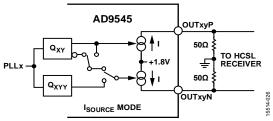

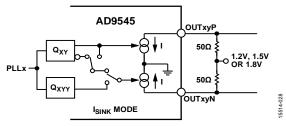

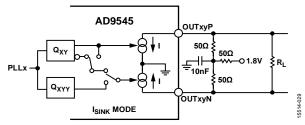

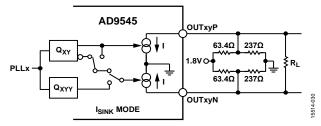

| Distribution Clock Output Drivers63             | Input Reference Source Selection      | 85  |

| Distribution Clock Output Drivers Overview63    | Active Reference Indication           | 85  |

| Output Current Control63                        | Translation Modes                     | 85  |

| Output Mode Control63                           | Phase Buildout Mode                   | 87  |

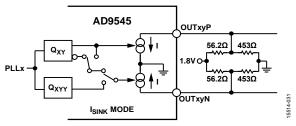

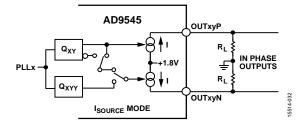

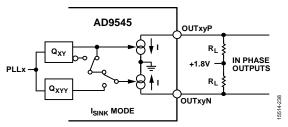

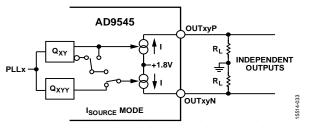

| Output Driver Configurations63                  | Internal Zero Delay (Hitless) Mode    | 88  |

| Output Driver Reset65                           | External Zero Delay (Hitless) Mode    | 89  |

| Output Muting65                                 | Source Profiles                       | 91  |

| Distribution Dividers (Q-Dividers)66            | Source Profiles Overview              | 91  |

| Distribution Dividers Overview66                | DPLL Phase/Frequency Lock Detector    | 91  |

| Q-Divider Clock Source Selection66              | Phase Step Limit                      | 91  |

| Integer Division67                              | Skew Adjustment                       | 92  |

| Half Integer Division67                         | Initial Phase Skew Refinement Steps   | 92  |

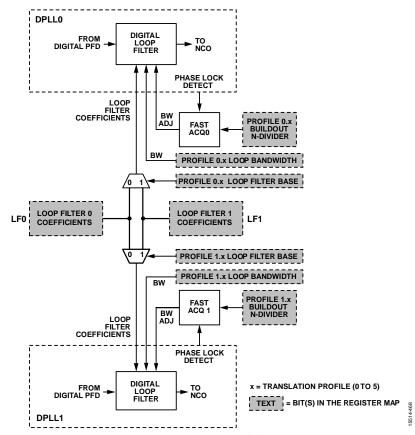

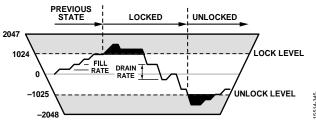

| Q-Divider Reset67                               | Digital PLL (DPLL)                    | 94  |

| Q-Divider Constraints68                         | DPLL Overview                         | 94  |

| Hitless/Zero Delay Feedback68                   | DPLL Loop Controller                  | 94  |

| Distribution Phase Offset Control69             | DPLL Feedback Divider (N-Divider)     | 95  |

| Output Phase Offset Overview69                  | DPLL Loop Filter                      | 96  |

| Initial Phase Offset69                          | DPLL NCO                              | 97  |

| Subsequent Phase Offsets69                      | NCO Gain Tuning Word Filter Bandwidth | 99  |

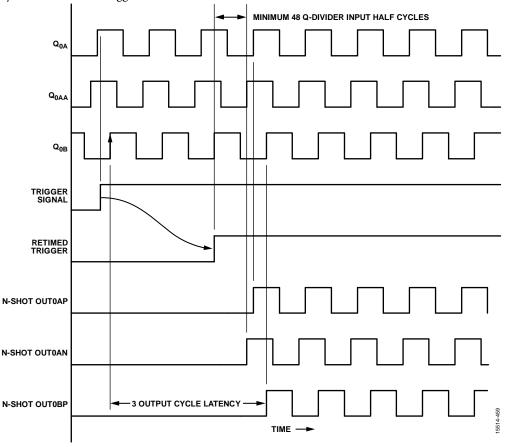

| Distribution N-Shot/PRBS Output Clocking72      | DPLL Lock Detectors                   | 99  |

| N-Shot/PRBS Clocking Overview72                 | Freerun Tuning Word                   | 101 |

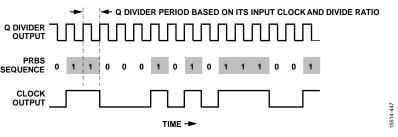

| Randomized Clock (PRBS)73                       | DPLL Fast Acquisition (FACQ) Options  | 101 |

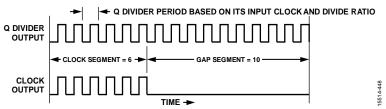

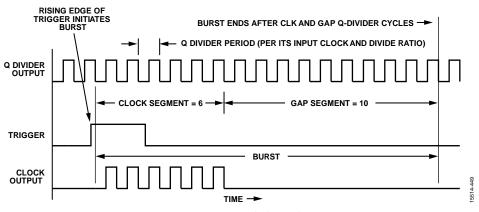

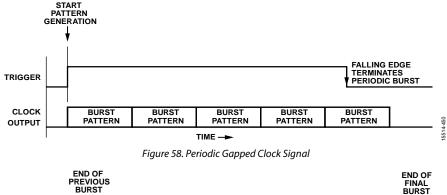

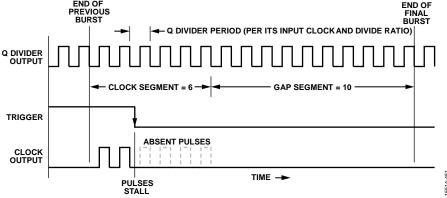

| N-Shot (JESD204B and Gapped Clocking)73         | DPLL Phase Offset Control             | 103 |

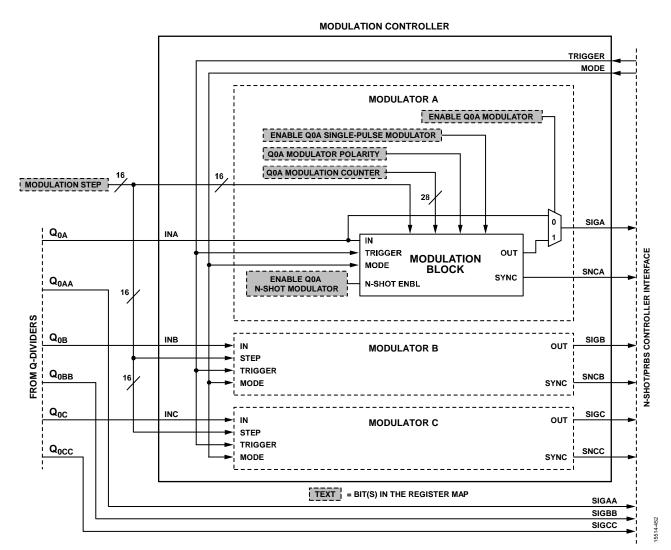

| Distribution Embedded Output Clock Modulation77 | Tuning Word Offset Clamp              | 104 |

| Modulation Controller Overview77                | Phase Slew Rate Limit                 | 105 |

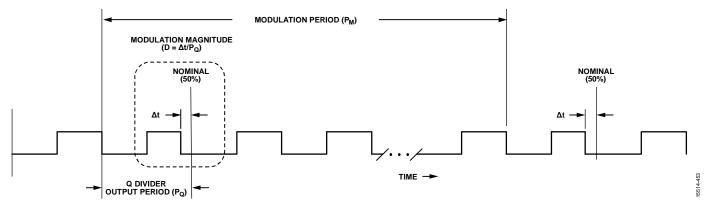

| Modulation Magnitude78                          | Tuning Word History                   | 106 |

| Modulation Period78                             | Delay Compensation                    | 109 |

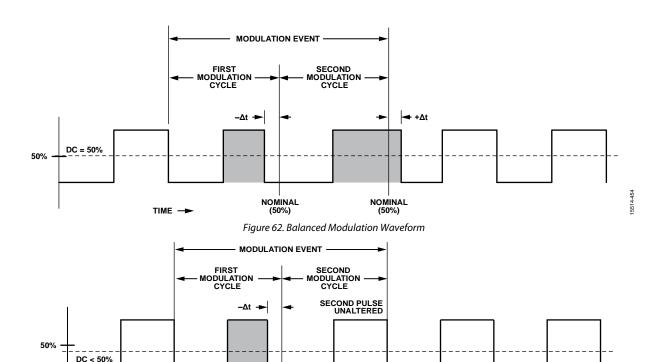

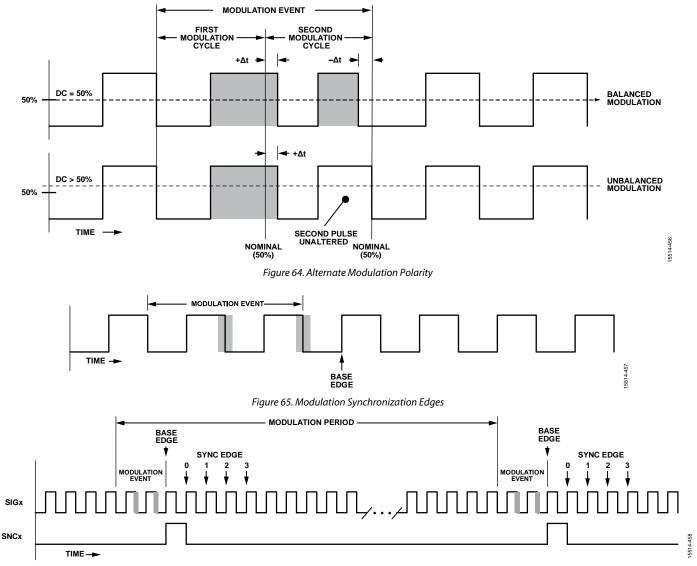

| Balanced and Unbalanced Modulation79            | Time Stamp Tagging Options            | 110 |

| Modulation Sync80                               | Cascaded DPLL Configuration           | 112 |

| Modulation Trigger81                            | Caveats of Cascaded DPLL Operation    | 114 |

| Distribution Output Clock Synchronization82     | Analog PLL (APLL)                     | 115 |

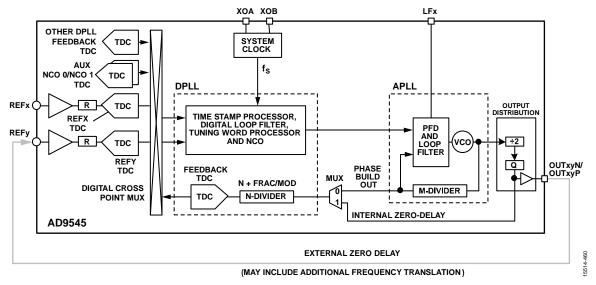

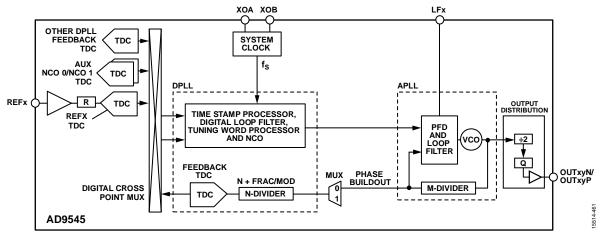

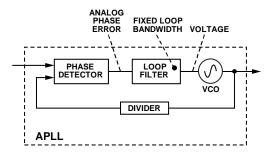

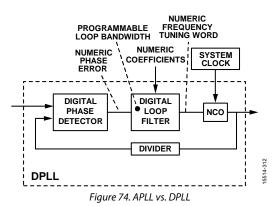

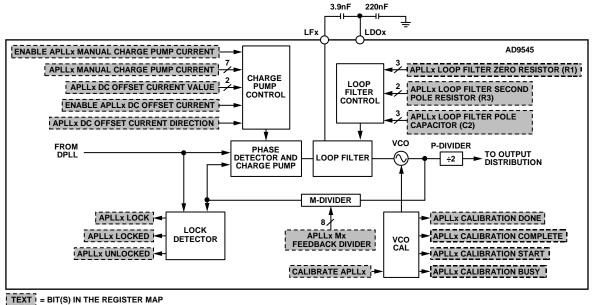

| Synchronization Overview82                      | APLL Overview                         | 115 |

| Manual Sync Trigger82                           | Voltage Controlled Oscillator (VCO)   | 115 |

| Autoreconfiguration Sync Trigger82              | APLL Feedback Divider (M-Divider)     | 116 |

| Autosync Trigger83                              | Phase/Frequency Detector (PFD)        | 116 |

| Reference Synchronization83                     | Charge Pump                           | 116 |

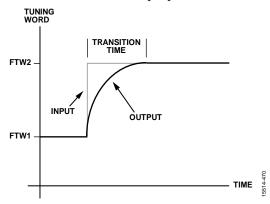

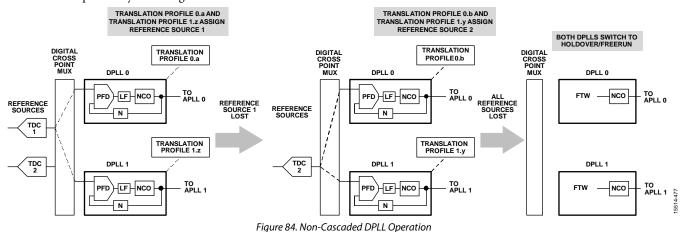

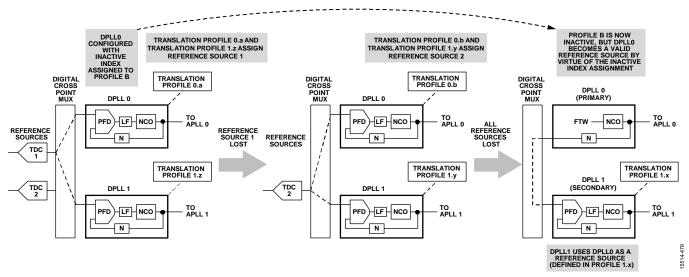

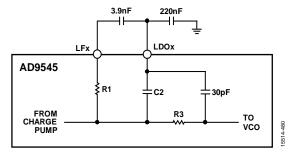

| Frequency Translation Loops84                   | APLL Loop Filter                      |     |

| Frequency Translation Loops Overview84          | Reference Switching                   | 118 |

| Translation Profiles84                          | Reference Switching Overview          |     |

|                                                 |                                       |     |

| Forced Freerun Mode                                       | 119                             |

|-----------------------------------------------------------|---------------------------------|

| Forced Holdover Mode                                      | 119                             |

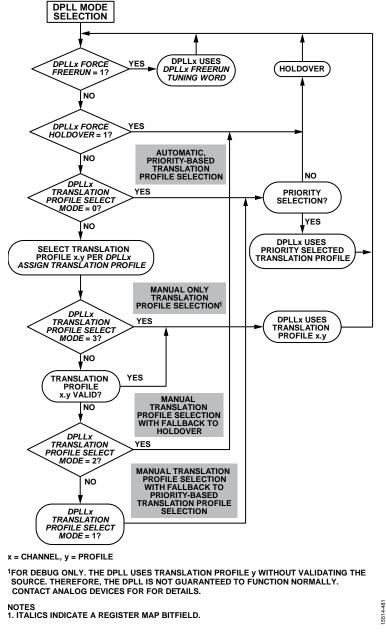

| Manual or Automatic Translation Profile Selection         | 120                             |

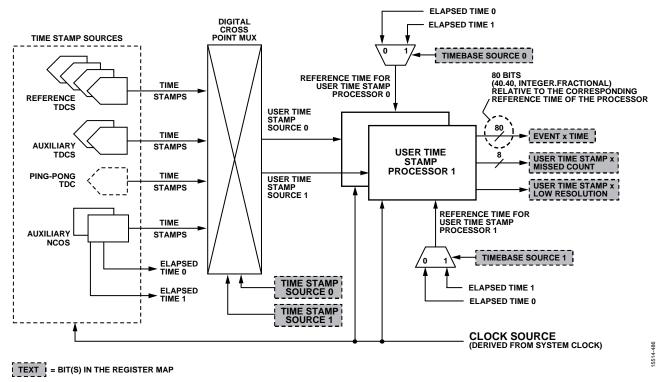

| Time to Digital Converter (TDC)                           | 124                             |

| Time Stamps                                               | 125                             |

| Time Stamps Overview                                      | 125                             |

| Digital Crosspoint Mux                                    | 125                             |

| Tagged Time Stamps                                        | 126                             |

| User Access to Time Stamps                                | 127                             |

| User Access to Time Stamps Overview                       | 127                             |

| Reading User Time Stamps                                  | 127                             |

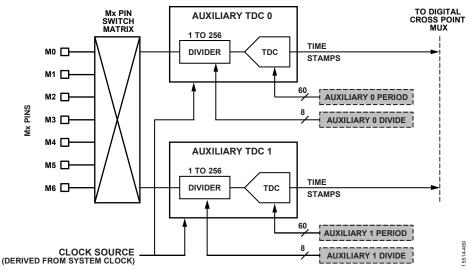

| Interpreting User Time Stamps                             | 128                             |

| Tagged User Time Stamps                                   | 129                             |

| User Time Stamp System Clock Compensation                 | 129                             |

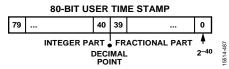

| Timing Skew Measurements Using Two TDCs                   | 130                             |

| Tagged Skew Measurement Time Stamps                       | 131                             |

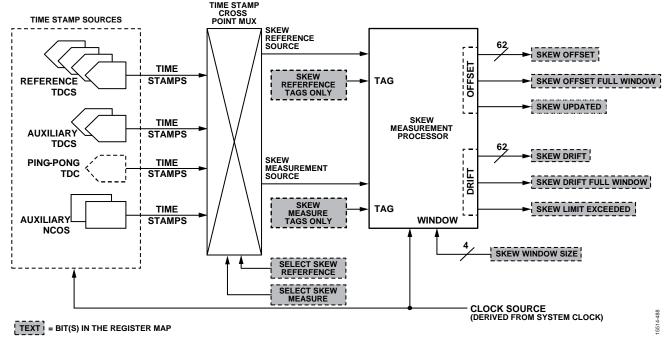

| Auxiliary TDCs                                            | 132                             |

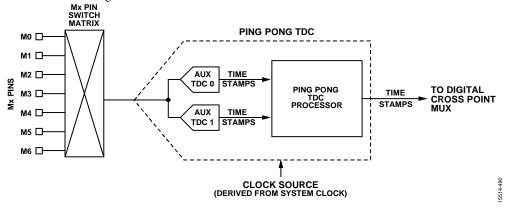

| Ping Pong TDC                                             | 132                             |

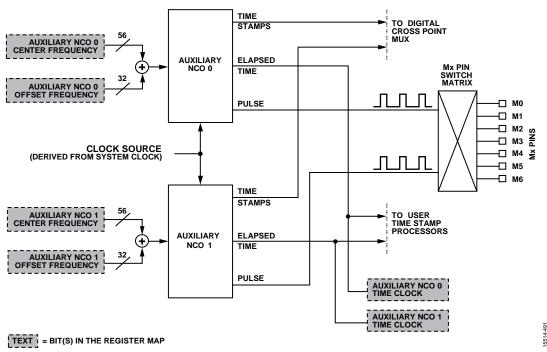

| Auxiliary NCOs                                            | 134                             |

| Auxiliary NCO Overview                                    | 134                             |

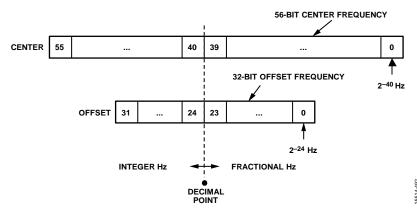

| Auxiliary NCO Frequency                                   | 134                             |

| Auxiliary NCO Phase Offset                                | 135                             |

| Auxiliary NCO Phase Slew Limit                            | 135                             |

| Manual Cycle Adjustment                                   | 136                             |

| Auxiliary NCO Time Stamps                                 | 136                             |

| Auxiliary NCO Pulse Output                                | 136                             |

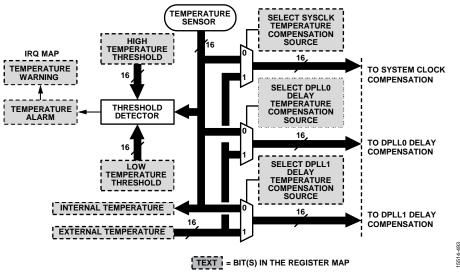

| Temperature Sensor                                        | 138                             |

|                                                           |                                 |

| Temperature Sensor Overview                               |                                 |

| Temperature Sensor Overview  Temperature Source Selection | 138                             |

|                                                           | 138<br>138                      |

| Temperature Source Selection                              | 138<br>138<br>138               |

| Temperature Source Selection                              | 138<br>138<br>138<br>139        |

| Temperature Source Selection                              | 138<br>138<br>138<br>139<br>140 |

|    | Compensation Method 2                           | 145 |

|----|-------------------------------------------------|-----|

|    | Compensation Method 3                           | 145 |

|    | Integrated Compensation Subsystem               | 147 |

|    | System Clock Compensation Programming Registers | 148 |

| St | tatus and Control Pins                          | 150 |

|    | Status and Control Pins Overview                | 150 |

|    | Multifunction Pins at Reset/Power-Up            | 150 |

|    | Status Functionality                            | 151 |

|    | Control Functionality                           | 151 |

| Iı | nterrupt Request (IRQ)                          | 153 |

|    | IRQ Overview                                    | 153 |

|    | IRQ Monitor                                     | 153 |

|    | IRQ Mask                                        | 153 |

|    | IRQ Clear                                       | 153 |

| V  | Vatchdog Timer                                  | 155 |

| E  | EPROM Usage                                     | 156 |

|    | EEPROM Overview                                 | 156 |

|    | EEPROM Controller General Operation             | 156 |

|    | EEPROM Instruction Set                          | 157 |

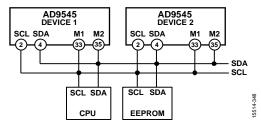

|    | Multidevice Support                             | 159 |

| A  | applications Information                        | 161 |

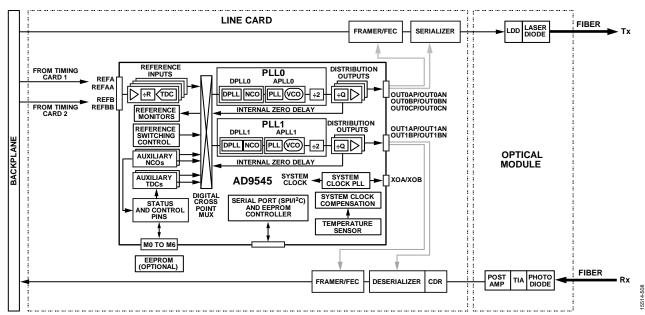

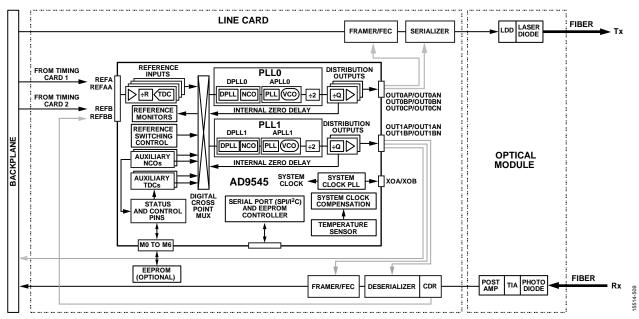

|    | Optical Networking Line Card                    | 161 |

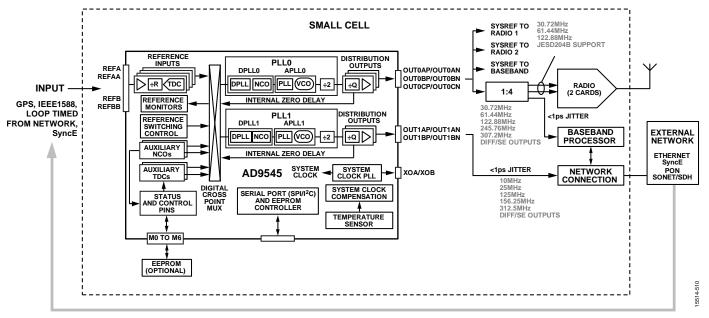

|    | Small Cell Base Station                         | 162 |

|    | IEEE 1588 Servo                                 | 163 |

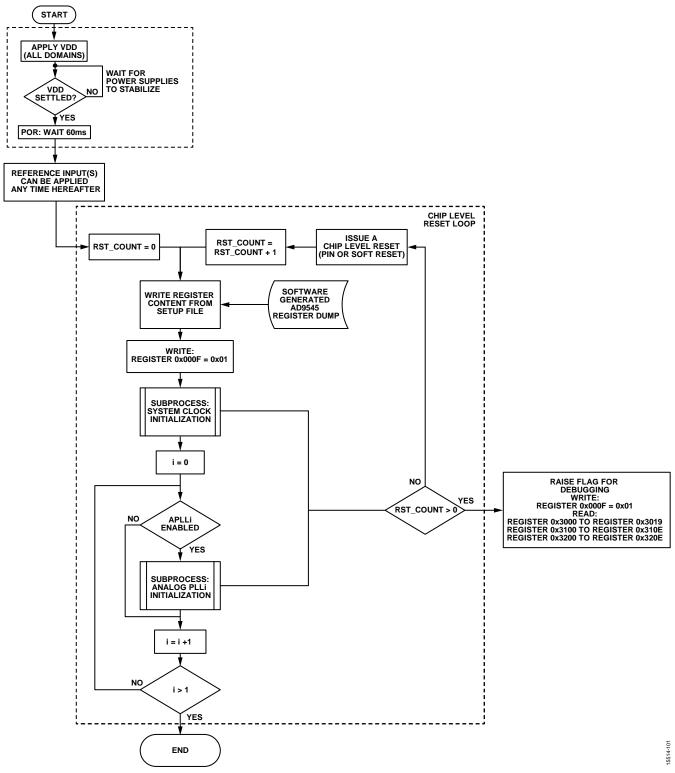

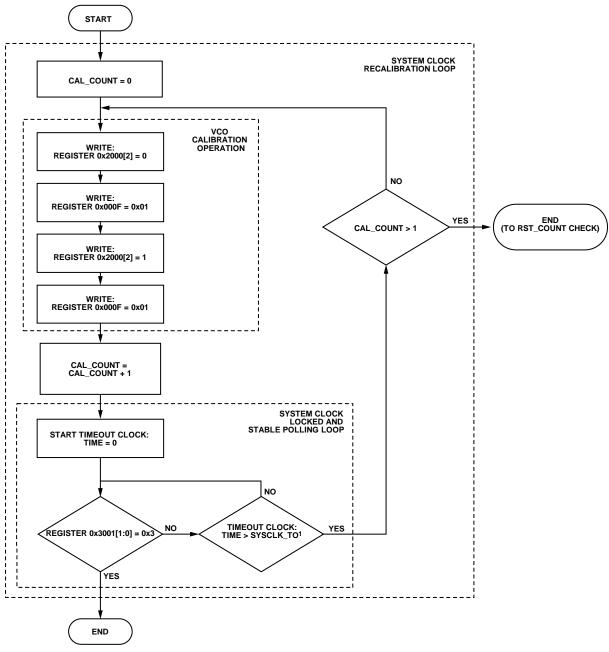

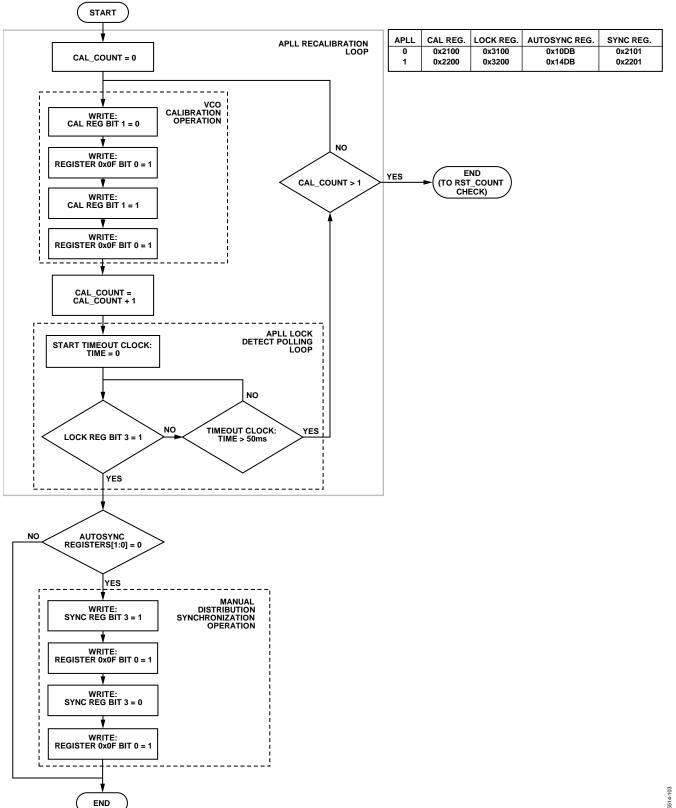

| Iı | nitialization Sequence                          | 164 |

| S  | erial Control Port                              | 167 |

|    | Serial Control Port Overview                    | 167 |

|    | SPI/I <sup>2</sup> C Port Selection             | 167 |

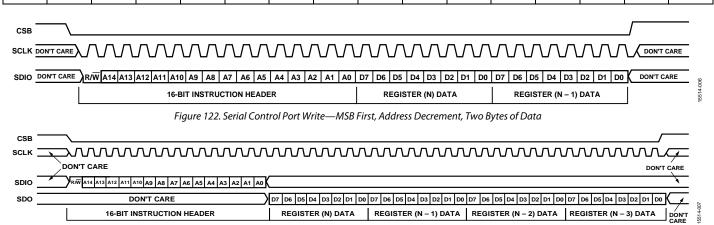

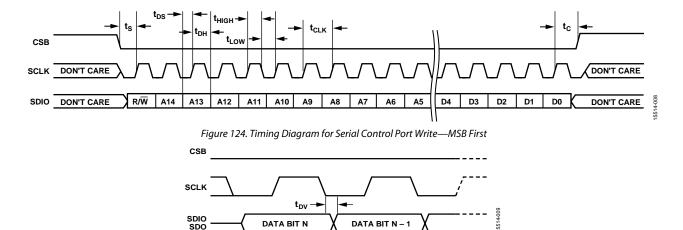

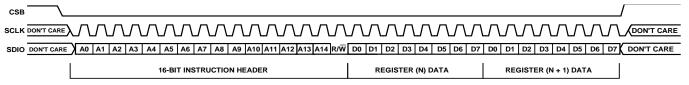

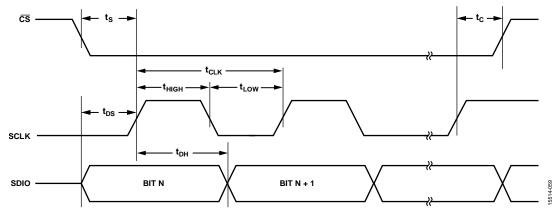

|    | SPI Serial Port Operation                       | 167 |

|    | I <sup>2</sup> C Serial Port Operation          |     |

| С  | Outline Dimensions                              | 173 |

|    | Ordering Guide                                  | 173 |

|    |                                                 |     |

# **REVISION HISTORY**

| 11/2021—Rev. B to Rev. C                                            |

|---------------------------------------------------------------------|

| Change to Output Distribution Driver On/Off Parameter, Table 410    |

| Changes to Table 5                                                  |

| Changes to Output Timing Skew Between Mx Pins and                   |

| OUTxyP and/or OUTxyN Pins Section and Table 1222                    |

| Changes to DPLL Propagation Delay Variation Section25               |

| Changes to Table 3032                                               |

| Changes to Table 3133                                               |

| Changes to Table 3437                                               |

| Change to Figure 5 Caption39                                        |

| Change to Figure 11 Caption40                                       |

| Changes to Figure 20 Caption41                                      |

| Changes to Figure 22 and Figure 2342                                |

| Changes to Theory of Operation Section45                            |

| Changes to Figure 29, Figure 30, Figure 31, Figure 32, and          |

| Figure 3446                                                         |

| Changes to Figure 3747                                              |

| Changes to Figure 4648                                              |

| Changes to Crystal Path Section49                                   |

| Added Frequency Doubler (2× Multiplier) Section49                   |

| Changes to Direct Path Section, Prescale Divider Section,           |

| System Clock PLL Lock Detector Section, and System Clock            |

| Calibration Section50                                               |

| Deleted 2× Frequency Multiplier Section50                           |

| Changes to System Clock Stability Compensation Section51            |

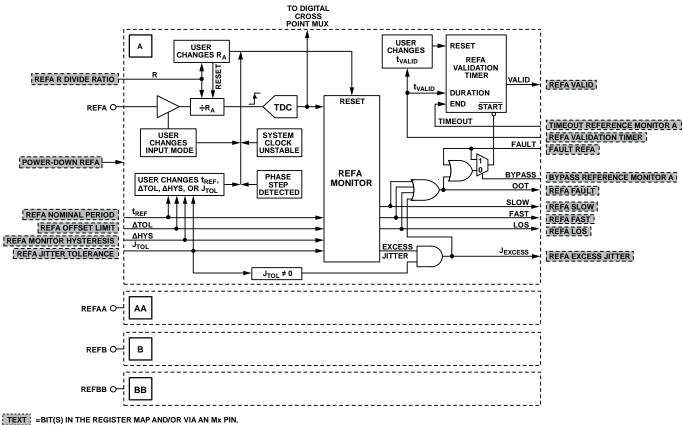

| Changes to Reference Monitor Overview Section55                     |

| Changes to REFx Nominal Period (t <sub>REF</sub> ) Section and REFx |

| Offset Limit (\Delta TOL) Section56                                 |

| Changes to Timeout Reference Monitor x (Timeout) Section 57         |

| Changes to Reference Demodulator Overview Section60                 |

| Changes to Figure 52 and Demodulator Polarity Section61             |

| Changes to Demodulator Persistence Section and Demodulator          |

| Bandwidth Section62                                                 |

| Changes to Output Driver Configurations Section and                 |

| Table 4163                                                          |

| Changes to Manual Output Muting Section65                           |

| Added Output Mute Retiming Section65                                |

| Changes to Q-Divider Clock Source Selection Section66               |

| Changes to Figure 5367                                              |

| Changes to Subsequent Phase Offsets Section69                       |

| Changes to N-Shot/PRBS Clocking Overview Section72                  |

| Change to Autosync Trigger Section83                                |

| Added Active Reference Indication Section85                         |

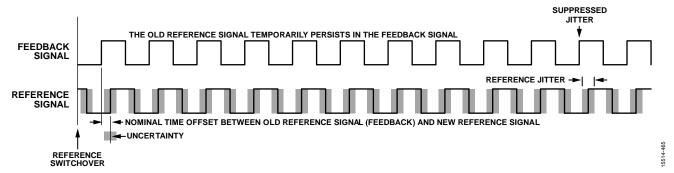

| Changes to Phase Buildout Mode Section and Figure 6987              |

| Change to Table 4889                                                |

| Changes to External Zero Delay (Hitless) Mode Section89             |

| Changes to Source Profiles Overview Section and Phase Step          |

| Limit Section91                                                     |

| Added Table 49; Renumbered Sequentially91                           |

| Changes to Figure 7393                                              |

| Changes to DPLL Feedback Divider (N-Divider) Section and            |

| N-Divider in Internal Zero Delay Mode Section95                     |

| Changes to N-Divider in External Zero Delay Mode Section      |

|---------------------------------------------------------------|

| and DPLL Loop Filter Section96                                |

| Changes to DPLL Loop Filter Base Coefficients Section and     |

| DPLL NCO Section97                                            |

| Changes to Figure 7798                                        |

| Changes to DPLL Phase Lock Detector Section99                 |

| Changes to DPLL Frequency Lock Detector Section100            |

| Deleted Figure 82; Renumbered Sequentially101                 |

| Changes to FACQ Bandwidth Control Section, FACQ Settling      |

| Time Control Section, and FACQ Timeout Control Section. 102   |

| Changes to Tuning Word Offset Clamp Section104                |

| Change to Averaging Processor Delay Section106                |

| Change to DPLLx Clear History Bit Section107                  |

| Changes to DPLLx Quick Start History Bit Section and          |

| Overview Section                                              |

| Changes to Caveats of Cascaded DPLL Operation Section114      |

| Changes to Charge Pump Section116                             |

| Change to Figure 89119                                        |

| Changes to Manual or Automatic Translation Profile Selection  |

| Section                                                       |

| Changes to Figure 93 and Figure 94                            |

| Changes to User Time Stamp System Clock Compensation          |

| Section                                                       |

| Changes to Timing Skew Measurements Using Two TDCs            |

| · · · · · · · · · · · · · · · · · · ·                         |

| Section and Figure 95                                         |

| Changes to Figure 96                                          |

| Changes to Auxiliary NCO Phase Offset Section and Auxiliary   |

| NCO Phase Slew Limit Section                                  |

| Changes to Open-Loop Method Section140                        |

| Changes to Programming the Coefficients (C <sub>k</sub> ) for |

| Compensation Method 1 Section                                 |

| Change to Compensation Method 3 Section145                    |

| Changes to Auxiliary DPLL Reference Monitor Section146        |

| Changes to Integrated Compensation Subsystem Section147       |

| Changes to System Clock Compensation Programming              |

| Registers Section148                                          |

| Changes to Figure 110149                                      |

| Changes to Figure 111150                                      |

| Changes to Figure 112 Caption154                              |

| Changes to Register Transfer Instructions (0x00 to 0x7F)      |

| Section                                                       |

| Changed to Table 71158                                        |

| Changes to Figure 117162                                      |

| Change to Figure 119163                                       |

| Changes to Serial Control Port Overview Section, Pin          |

| Descriptions Section, and Implementation Specific Details     |

| Section167                                                    |

| Change to SPI MSB-/LSB-First Transfers Section168             |

| Changes to Table 82172                                        |

| •                                                             |

| 10/2018—Rev. A to Rev. B                                      |

| Added Operating Temperature Section and Table 1; Renumbered   |

| Sequentially 8                                                |

| Changes to Table 2 and Supply Current Section 8                | Changes to Input/Output Termination Recommendations            |

|----------------------------------------------------------------|----------------------------------------------------------------|

| Changes to Table 510                                           | Section                                                        |

| Changes to Table 611                                           | Added Figure 39 and Figure 40; Renumbered Sequentially35       |

| Added Reference-to-Reference Coupling Section and Table 7 13   | Added System Clock PLL Overview Heading and Figure 42 36       |

| Added Reference-to-Mx- Pin Input Timing Skew Section and       | Changes to System Clock Input Frequency Declaration Section,   |

| Table 815                                                      | System Clock Source Section, Crystal Path Section, Direct Path |

| Changes to Table 1017                                          | Section                                                        |

| Added Output-to-Output Timing Skew Section and Table 11 20     | Added System Clock Calibration Section                         |

| Added Output Timing Skew Between Mx Pins and OUTxyP            | Changes to 2× Frequency Multiplier Section, Prescale Divider   |

| and/or OUTxyN Pins Section and Table 1221                      | Section, Feedback Divider Section, and System Clock PLL Lock   |

| Changes to Table 1321                                          | Detector Section                                               |

| Moved DPLL Phase Characteristics Section and Table 16 23       | Deleted System Clock Input Termination Recommendations         |

| Added DPLL Propagation Delay Section, Table 17, DPLL           | Section                                                        |

| Propagation Delay Variation Section, and Table 1824            | Added System Clock Stability Compensation Section 38           |

| Changes to Table 1925                                          | Added Reference Clock Input Receivers Section, Table 27, and   |

| Added Mx-to-Mx Pin Output Timing Skew Section and              | Table 28; Renumbered Sequentially                              |

| Table 2326                                                     | Added Reference Dividers (R-Dividers) Section                  |

| Moved Logic Output Specifications (M0 to M6) Section and       | Added Reference Monitor Section and Figure 43 42               |

| Table 27                                                       | Added Table 29 and Figure 44                                   |

| Changes to Table 27                                            | Added Table 30                                                 |

| Moved Serial Port Specifications Section and Table 28          | Added Reference Demodulator Section and Figure 45              |

| Changes to Table 32                                            | Added Figure 46                                                |

| Added Figure 21, Figure 24, Figure 25, and Figure 26;          | Added Distribution Clock Output Drivers Section, Table 31,     |

| Renumbered Sequentially41                                      | Table 32, and Table 3350                                       |

| Added Figure 27 and Figure 28                                  | Added Table 34                                                 |

| Change to Differential Mode Section                            | Added Distribution Dividers (Q-Dividers) Section               |

| Changes to Demodulation Bandwidth Section                      | Added Figure 4754                                              |

| Changes to N-Divider for Phase Buildout Mode Section and N-    | Added Distribution Phase Offset Control Section                |

| Divider in Internal Zero Delay Mode Section                    | Added Table 35                                                 |

| · ·                                                            | Added Distribution N-Shot/PRBS Output Clocking Section         |

| Changes to N-Divider in External Zero Delay Mode Section 93    | <u>.</u>                                                       |

| 4/2010 Para 0.4a Para A                                        | and Figure 48                                                  |

| 4/2018—Rev. 0 to Rev. A                                        | Added Table 36 and Figure 49                                   |

| Changes to Features Section, Applications Section, and General | Added Figure 50, Figure 51, and Figure 52                      |

| Description Section1                                           | Added Figure 53                                                |

| Changes to Figure 1                                            | Added Distribution Embedded Output Clock Modulation            |

| Changes to Table 3                                             | Section and Figure 54                                          |

| Changes to Table 4                                             | Added Figure 55                                                |

| Changes to Table 5                                             | Added Figure 56 and Figure 57                                  |

| Changes to Table 6                                             | Added Figure 58, Figure 59, and Figure 60                      |

| Change to Table 7                                              | Added Figure 61                                                |

| Change to Table 9                                              | Added Distribution Output Clock Synchronization Section 68     |

| Change to Table 10                                             | Added Table 37                                                 |

| Changes to Table 12                                            | Added Frequency Translation Loops Section and Figure 62 70     |

| Changes to Table 18                                            | Added Table 38                                                 |

| Changes to Table 19                                            | Added Table 39 and Figure 63                                   |

| Changes to Table 2019                                          | Added Figure 64                                                |

| Changes to Table 21 and Table 2220                             | Added Table 40                                                 |

| Changes to Table 2321                                          | Added Figure 65 75                                             |

| Changes to Thermal Resistance Section and Table 25 24          | Added Source Profiles Section and Figure 66                    |

| Changes to Table 2625                                          | Added Figure 67                                                |

| Changes to Typical Performance Characteristics Section 27      | Moved Digital PLL (DPLL) Section                               |

| Changes to Terminology Section                                 | Changes to Digital PLL (DPLL) Section                          |

| Moved Theory of Operation Section                              | Added Figure 69 and Figure 7081                                |

| Changes to Theory of Operation Section                         | Added Table 4182                                               |

| Moved Input/Output Termination Recommendations Section33       | Added Figure 7183                                              |

| Added Table 42 and Figure 7284                                |

|---------------------------------------------------------------|

| Added Table 43 and Table 4487                                 |

| Added Figure 7488                                             |

| Added Figure 75 and Figure 7689                               |

| Added Figure 7790                                             |

| Added Figure 7894                                             |

| Added Table 4595                                              |

| Added Cascaded DPLL Configuration Section and Figure 7997     |

| Added Figure 8098                                             |

| Added Analog PLL (APLL) Section, Table 46, and Figure 81100   |

| Added Table 47 and Table 48101                                |

| Added Figure 82 and Table 49102                               |

| Added Reference Switching Section103                          |

| Added Figure 83104                                            |

| Added Figure 84 and Table 50105                               |

| Added Figure 85107                                            |

| Added Figure 86108                                            |

| Added Time-to-Digital Converter (TDC) Section and             |

| Figure 87                                                     |

| Added Time Stamps Section and Table 51110                     |

| Added User Access to Time Stamps Section112                   |

| Added Figure 88 and Figure 89113                              |

| Added Timing Skew Measurements Using Two TDCs Section,        |

| Figure 90, and Table 52115                                    |

| Added Auxiliary TDCs Section and Figure 91117                 |

| Added Figure 92118                                            |

| Added Auxiliary NCOs Section, Figure 93, and Figure 94119     |

| Added Temperature Sensor Section, Figure 95, and Figure 96123 |

| Added System Clock Compensation Section and Figure 97125      |

| Added Figure 98126                                            |

| Added Figure 99, Table 53, and Figure 100127                  |

| Added Table 54129                                             |

| Added Figure 101 and Table 55130                              |

| Added Figure 102131                                           |

| Added Table 56 and Figure 103                          | 132 |

|--------------------------------------------------------|-----|

| Added Table 57 and Figure 104                          | 133 |

| Moved Status and Control Pins Section                  |     |

| Added Status and Control Pins Overview Section Heading | 134 |

| Changes to Status Functionality Section and Control    |     |

| Functionality Section                                  | 135 |

| Deleted Table 31; Renumbered Sequentially              | 136 |

| Moved Interrupt Request (IRQ) Section                  | 137 |

| Added IRQ Overview Section Heading                     | 137 |

| Changes to IRQ Clear Section                           | 137 |

| Moved Watchdog Timer Section                           | 139 |

| Changes to Watchdog Timer Section                      | 139 |

| Moved EEPROM Usage Section                             | 140 |

| Changed Overview Section Heading to EEPROM Overview    | N   |

| Section                                                | 140 |

| Changes to EEPROM Upload Section                       | 140 |

| Moved Applications Information Section                 | 145 |

| Added Figure 110 and Figure 111                        | 145 |

| Changes to Optical Networking Line Card Section        | 145 |

| Added Figure 112                                       | 146 |

| Changes to Small Cell Base Station Section             | 146 |

| Added Figure 113                                       | 147 |

| Moved Initialization Sequence Section                  | 148 |

| Changes to Figure 115                                  |     |

| Changes to Figure 116                                  | 150 |

| Moved Serial Control Port Section                      | 151 |

| Added Serial Control Port Overview Section Heading     | 151 |

| Changes to Write Section                               | 151 |

| Changes to Read Section, SPI MSB-/LSB-First Transfers  |     |

| Section, and Address Ascension Section                 | 152 |

| Changes to Data Transfer Format Section                | 156 |

6/2017—Revision 0: Initial Version

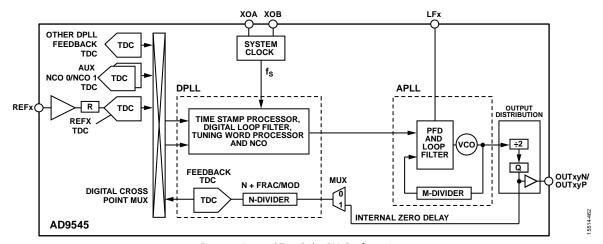

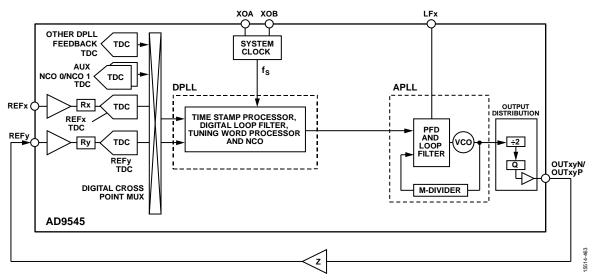

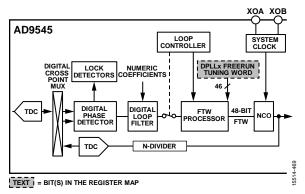

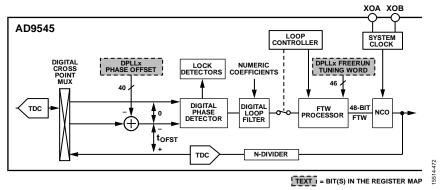

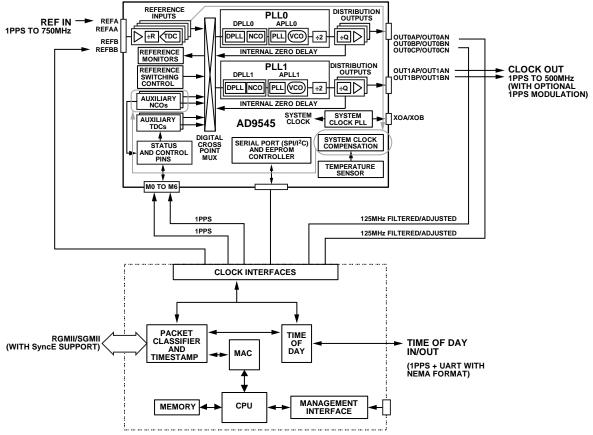

# **FUNCTIONAL BLOCK DIAGRAM**

# **SPECIFICATIONS**

The minimum and maximum values apply for the full range of supply voltage and operating temperature variations. Typical values apply for VDD = 1.8 V and  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.

#### **OPERATING TEMPERATURE**

Table 1.

| Parameter                        | Min | Тур | Max  | Unit | Test Conditions/Comments                                                                |

|----------------------------------|-----|-----|------|------|-----------------------------------------------------------------------------------------|

| OPERATING TEMPERATURE            |     |     |      |      |                                                                                         |

| Ambient Temperature <sup>1</sup> | -40 |     | +85  | °C   |                                                                                         |

| Die Temperature <sup>2</sup>     |     |     | +105 | °C   | Internal temperature sensor readings exceeding 105°C indicate excessive die temperature |

$<sup>^{\</sup>mbox{\tiny 1}}$  See the Thermal Resistance section for additional information.

## **SUPPLY VOLTAGE**

Table 2.

| Parameter         | Min  | Тур | Max   | Unit | Test Conditions/Comments                    |

|-------------------|------|-----|-------|------|---------------------------------------------|

| SUPPLY VOLTAGE    |      |     |       |      |                                             |

| VDDIOA and VDDIOB | 1.71 | 1.8 | 3.465 | V    | 1.8 V, 2.5 V, and 3.3 V operation supported |

| VDD               | 1.71 | 1.8 | 1.89  | V    |                                             |

#### **SUPPLY CURRENT**

The minimum, typical, and maximum supply voltage values given in Table 2 are the basis for the minimum, typical, and maximum supply current specifications, respectively (see Table 3).

Table 3.

| Parameter                                           | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                    |

|-----------------------------------------------------|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------|

| SUPPLY CURRENT FOR TYPICAL CONFIGURATION            |     |     |     |      | The Typical Configuration parameter in Table 4 is the basis for the values given for this set of parameters |

| Ivddiox                                             |     | 5   | 8   | mA   | Aggregate current for all VDDIOx pins (where $x = A$ or B)                                                  |

| l <sub>VDD</sub>                                    | 260 | 310 | 355 | mA   | Aggregate current for all VDD pins                                                                          |

| SUPPLY CURRENT FOR ALL BLOCKS RUNNING CONFIGURATION |     |     |     |      | The All Blocks Running parameter in Table 4 is the basis for the values given for this set of parameters    |

| Ivddiox                                             |     | 5   | 8   | mA   | Aggregate current for all VDDIOx pins (where $x = A$ or B)                                                  |

| I <sub>VDD</sub>                                    | 321 | 390 | 430 | mA   | Aggregate current for all VDD pins                                                                          |

<sup>&</sup>lt;sup>2</sup> The maximum die temperature supporting the performance stated in Table 2 to Table 31. The maximum operating die temperature takes precedence over the maximum ambient operating temperature. Use the internal temperature sensor to measure the AD9545 die temperature (see the Temperature Sensor section).

# **POWER DISSIPATION**

The typical values apply for VDD = 1.8 V, and the maximum values apply for VDD = 1.89 V.

Table 4.

| Parameter                                                              | Min | Тур | Max | Unit | Test Conditions/Comments                                                                                                                                                                                      |

|------------------------------------------------------------------------|-----|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DISSIPATION                                                      |     |     |     |      |                                                                                                                                                                                                               |

| Typical Configuration                                                  | 445 | 560 | 671 | mW   | System clock = 49.152 MHz crystal; two DPLLs active; two 19.44 MHz input references in differential mode; two ac-coupled PLL0 CML output drivers at 245.76 MHz; and two PLL1 CML output drivers at 156.25 MHz |

| All Blocks Running                                                     | 548 | 700 | 813 | mW   | System clock = 49.152 MHz crystal; two DPLLs active; two 19.44 MHz input references in differential mode; three ac-coupled PLL0 HCSL output drivers at 400 MHz; and two PLL1 HCSL output drivers at 400 MHz   |

| Full Power-Down                                                        |     | 125 |     | mW   | Based on the Typical Configuration specification with the power down all bit set to Logic 1                                                                                                                   |

| Incremental Power Dissipation                                          |     |     |     |      | Based on the Typical Configuration specification; the values in this section indicate the change in power due to the indicated operation relative to the Typical Configuration specification                  |

| Complete DPLL/APLL On/Off                                              |     | 200 |     | mW   | Change in dissipated power relative to the Typical Configuratio specification; the powered down blocks consist of one reference input, one DPLL, one APLL, two channel dividers, and two output drivers       |

| Input Reference On/Off                                                 |     |     |     |      |                                                                                                                                                                                                               |

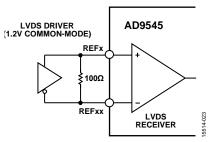

| Differential (AC-Coupled Mode)                                         |     | 20  |     | mW   | $f_{REF} = 19.44 \text{ MHz}$ (see Figure 35)                                                                                                                                                                 |

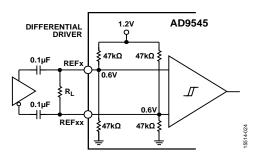

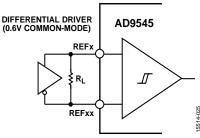

| Differential (DC-Coupled Mode)                                         |     | 21  |     | mW   | f <sub>REF</sub> = 19.44 MHz (see Figure 36)                                                                                                                                                                  |

| Single-Ended                                                           |     | 13  |     | mW   | $f_{REF} = 19.44 \text{ MHz}$                                                                                                                                                                                 |

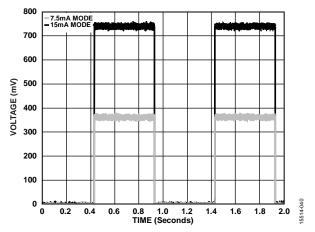

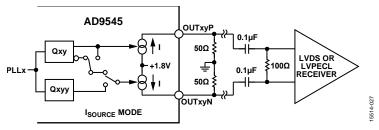

| Output Distribution Driver On/Off                                      |     |     |     |      | At 156.25 MHz                                                                                                                                                                                                 |

| 15 mA Mode                                                             |     | 30  |     | mW   |                                                                                                                                                                                                               |

| 12.5 mA Mode                                                           |     | 23  |     | mW   |                                                                                                                                                                                                               |

| 7.5 mA Mode                                                            |     | 15  |     | mW   |                                                                                                                                                                                                               |

| Auxiliary DPLL On/Off                                                  |     | 1   |     | mW   |                                                                                                                                                                                                               |

| Auxiliary Numerically Controlled<br>Oscillator (NCO) to Mx Pin On/Off  |     | 1   |     | mW   | Fundamental set to 50 kHz                                                                                                                                                                                     |

| Auxiliary Time to Digital Converters<br>(TDC) Input from Mx Pin On/Off |     | 1   |     | mW   | Input frequency = 10 MHz, auxiliary TDC rate = 200 kHz                                                                                                                                                        |

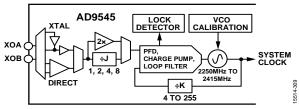

## **SYSTEM CLOCK INPUTS, XOA AND XOB**

Table 5.

| Parameter                                            | Min  | Тур  | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------------|------|------|------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM CLOCK MULTIPLIER                              |      |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Output Frequency Range                               | 2250 |      | 2415 | MHz    | The frequency range of the internal voltage controlled oscillator (VCO) places limits on the choice of the system clock input frequency                                                                                                                                                                                                                                                                                                                                         |

| Phase Frequency Detector (PFD) Rate                  | 20   |      | 300  | MHz    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SYSTEM CLOCK INPUT, DIRECT PATH                      |      |      |      |        | System clock input must be ac-coupled; do not enable the frequency doubler when using the direct path.                                                                                                                                                                                                                                                                                                                                                                          |

| Input Frequency Range                                | 20   |      | 300  | MHz    | Degraded phase noise performance typically occurs for frequencies below 50 MHz appearing at the input of the phase frequency detector of the system clock PLL; for optimal phase noise performance, the recommendation is to use the quartz crystal resonator path with a crystal resonator frequency of ≥50 MHz, with the frequency doubler enabled, and the device configured to use system clock compensation Method 3 (see the System Clock Stability Compensation section) |

| Input Duty Cycle                                     | 40   |      | 60   | %      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Self Biased Common-Mode Voltage                      |      | 0.75 |      | ٧      | Internally generated                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Input Voltage                                        |      |      |      |        | For dc-coupled, single-ended operation                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| High                                                 | 0.9  |      |      | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Low                                                  |      |      | 0.5  | V      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Differential Input Voltage Sensitivity               | 250  |      |      | mV p-p | Minimum voltage swing required (as measured with a differential probe) across the XOA/XOB pins to ensure switching between logic states; the instantaneous voltage on either pin must not exceed 1.2 V; accommodate the single-ended input by ac grounding the complementary input; 800 mV p-p recommended for optimal jitter performance                                                                                                                                       |

| Slew Rate for Sinusoidal Input                       |      |      |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Functional                                           |      | >6   |      | V/µs   | Required to provide a locked and stable system clock                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operational                                          |      | >31  |      | V/µs   | Required for <1 dBc phase noise degradation                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| System Clock Input Divider<br>(J Divider) Frequency  | 100  |      |      | MHz    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Input Resistance                                     |      | 5    |      | kΩ     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

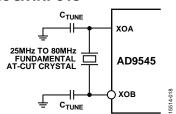

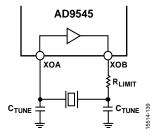

| SYSTEM CLOCK INPUT, QUARTZ<br>CRYSTAL RESONATOR PATH |      |      |      |        | The crystal resonator path includes an optional frequency doubler                                                                                                                                                                                                                                                                                                                                                                                                               |

| Resonator Frequency Range                            | 25   |      | 80   | MHz    | Fundamental mode, AT cut crystal                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Crystal Motional Resistance                          |      |      | 100  | Ω      | For crystal resonant frequency >52 MHz, the motional resistance must not exceed 50 $\Omega$ and the crystal load capacitance (C <sub>L</sub> ) must not exceed 8 pF                                                                                                                                                                                                                                                                                                             |

## **REFERENCE INPUTS**

Table 6.

Parameter

| Parameter                                                          | Min   | Тур  | Max                   | Unit   | Test Conditions/Comments                                                                                                                                                                                        |

|--------------------------------------------------------------------|-------|------|-----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

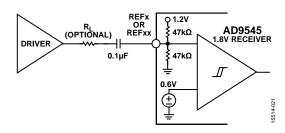

| DIFFERENTIAL MODE                                                  |       |      |                       |        | Differential mode specifications assume ac coupling of the input signal to the reference input pins                                                                                                             |

| Frequency Range                                                    |       |      |                       |        |                                                                                                                                                                                                                 |

| Sinusoidal Input                                                   |       |      | 750                   | MHz    | Lower limit dependent on input slew rate                                                                                                                                                                        |

| Low Voltage Positive<br>Emitter Coupled<br>Logic (LVPECL)<br>Input | 1     |      | 750 × 10 <sup>6</sup> | Hz     | Lower limit dependent on ac coupling                                                                                                                                                                            |

| LVDS Input                                                         | 1     |      | 500 × 10 <sup>6</sup> | Hz     | Assumes an LVDS minimum of 494 mV p-p differential amplitude; lower limit dependent on ac coupling                                                                                                              |

| Slew Rate                                                          |       | >4.1 |                       | V/µs   | Required for proper reference monitor operation; output jitter degradation can occur for slew rates <35 V/µs                                                                                                    |

| Common-Mode Input<br>Voltage                                       |       | 0.64 |                       | V      | Internally generated self bias voltage                                                                                                                                                                          |

| Differential Input<br>Amplitude                                    |       |      |                       |        | Peak-to-peak differential voltage swing across pins required<br>to ensure switching between logic levels as measured with a<br>differential probe; instantaneous voltage on either pin must<br>not exceed 1.3 V |

| $f_{\text{IN}}$ < 500 MHz                                          | 350   |      | 2100                  | mV p-p |                                                                                                                                                                                                                 |

| $f_{IN} = 500 \text{ MHz to}$ 750 MHz                              | 500   |      | 2100                  | mV p-p |                                                                                                                                                                                                                 |

| Differential Input Voltage<br>Hysteresis                           |       | 55   | 100                   | mV     |                                                                                                                                                                                                                 |

| Input Resistance<br>Input Pulse Width                              |       | 16   |                       | kΩ     | Equivalent differential input resistance                                                                                                                                                                        |

| LVPECL                                                             | 600   |      |                       | ps     |                                                                                                                                                                                                                 |

| LVDS                                                               | 900   |      |                       | ps     |                                                                                                                                                                                                                 |

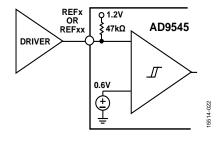

| DC-COUPLED, LVDS-<br>COMPATIBLE MODE                               |       |      |                       |        | Applies for dc coupling to an LVDS source                                                                                                                                                                       |

| Frequency Range                                                    | 1     |      | $450 \times 10^{6}$   | Hz     |                                                                                                                                                                                                                 |

| Slew Rate                                                          |       | >1.2 |                       | V/µs   | Required for proper reference monitor operation; output jitter degradation can occur for slew rates <35 V/µs                                                                                                    |

| Common-Mode Input<br>Voltage                                       | 1.125 |      | 1.375                 | V      |                                                                                                                                                                                                                 |

| Differential Input<br>Amplitude                                    | 400   |      | 1200                  | mV p-p | Differential voltage across pins required to ensure switching<br>between logic levels; instantaneous voltage on either pin<br>must not exceed the supply rails                                                  |

| Differential Input Voltage<br>Hysteresis                           |       | 55   | 100                   | mV     |                                                                                                                                                                                                                 |

| Input Resistance                                                   |       | 16   |                       | kΩ     |                                                                                                                                                                                                                 |

| Input Pulse Width                                                  | 1     |      |                       | ns     |                                                                                                                                                                                                                 |

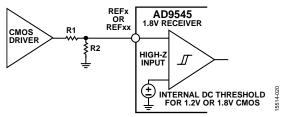

| SINGLE-ENDED MODE                                                  |       |      |                       |        | Single-ended mode specifications assume dc coupling of the input signal to the reference input pins                                                                                                             |

| 1.2 V CMOS                                                         |       |      |                       |        |                                                                                                                                                                                                                 |

| Frequency Range<br>Input Voltage                                   | 1     |      | 500 × 10 <sup>6</sup> | Hz     | Assumes dc-coupled input signal to the reference input pins                                                                                                                                                     |

| High, V <sub>IH</sub>                                              | 0.78  |      | 1.38                  | V      |                                                                                                                                                                                                                 |

| Low, V <sub>IL</sub>                                               |       |      | 0.42                  | V      |                                                                                                                                                                                                                 |

| Input Resistance                                                   |       | 30   |                       | kΩ     |                                                                                                                                                                                                                 |

| Slew Rate                                                          |       | >8   |                       | V/µs   | Required for proper reference monitor operation; output jitter degradation can occur for slew rates <35 V/µs                                                                                                    |

| Input Pulse Width                                                  | 900   |      |                       | ps     |                                                                                                                                                                                                                 |

| Parameter                                  | Min                  | Тур | Max                       | Unit  | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------|----------------------|-----|---------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.8 V CMOS                                 |                      |     |                           |       |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Frequency Range                            | 1                    |     | $500 \times 10^{6}$       | Hz    | Assumes dc-coupled input signal to the reference input pins                                                                                                                                                                                                                                                                                                                                         |

| Input Voltage                              |                      |     |                           |       |                                                                                                                                                                                                                                                                                                                                                                                                     |

| High, V <sub>IH</sub>                      | 1.17                 |     | 2.07                      | V     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Low, V <sub>IL</sub>                       |                      |     | 0.63                      | V     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Input Resistance                           |                      | 30  |                           | kΩ    |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Slew Rate                                  |                      | >8  |                           | V/µs  | Required for proper reference monitor operation; output jitter degradation can occur for slew rates <35 V/µs                                                                                                                                                                                                                                                                                        |

| Input Pulse Width                          | 900                  |     |                           | ps    |                                                                                                                                                                                                                                                                                                                                                                                                     |

| AC-Coupled                                 |                      |     |                           |       |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Frequency Range                            | 1                    |     | $500 \times 10^{6}$       | Hz    | Applies to 1.2 V CMOS ac-coupled                                                                                                                                                                                                                                                                                                                                                                    |

| Input Amplitude                            | 360                  |     | 1200                      | mV    | Peak-to-peak single-ended voltage swing; instantaneous voltage must not exceed 1.3 V                                                                                                                                                                                                                                                                                                                |

| Input Impedance                            |                      | 15  |                           | kΩ    |                                                                                                                                                                                                                                                                                                                                                                                                     |

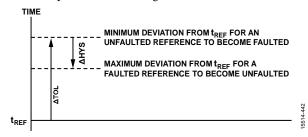

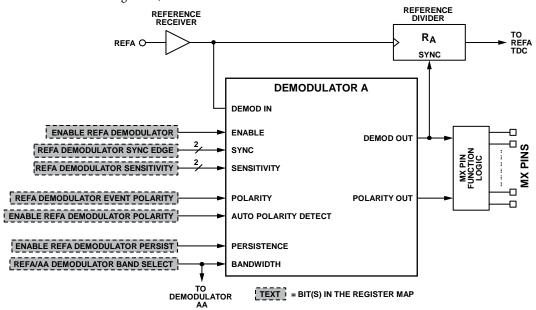

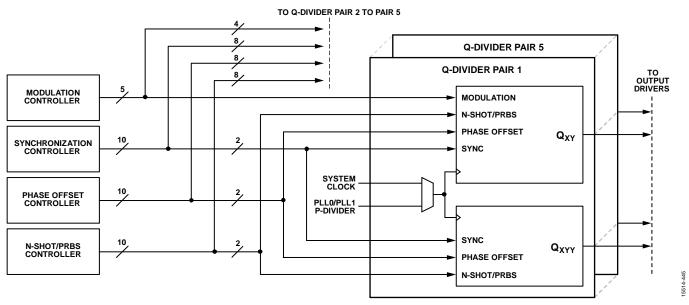

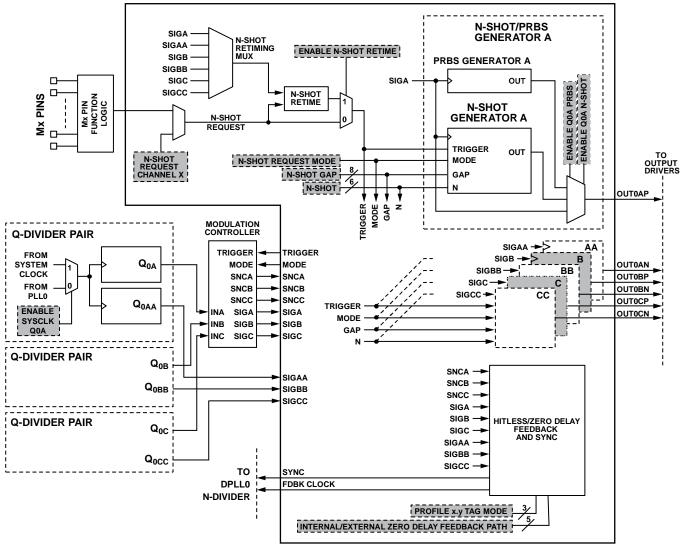

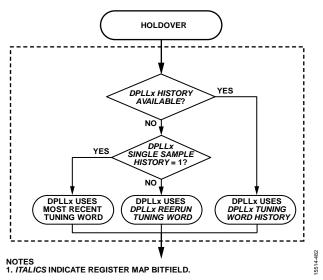

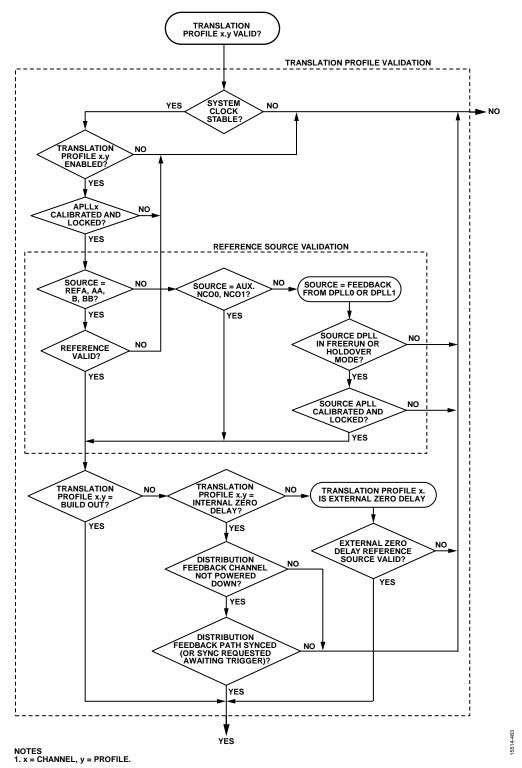

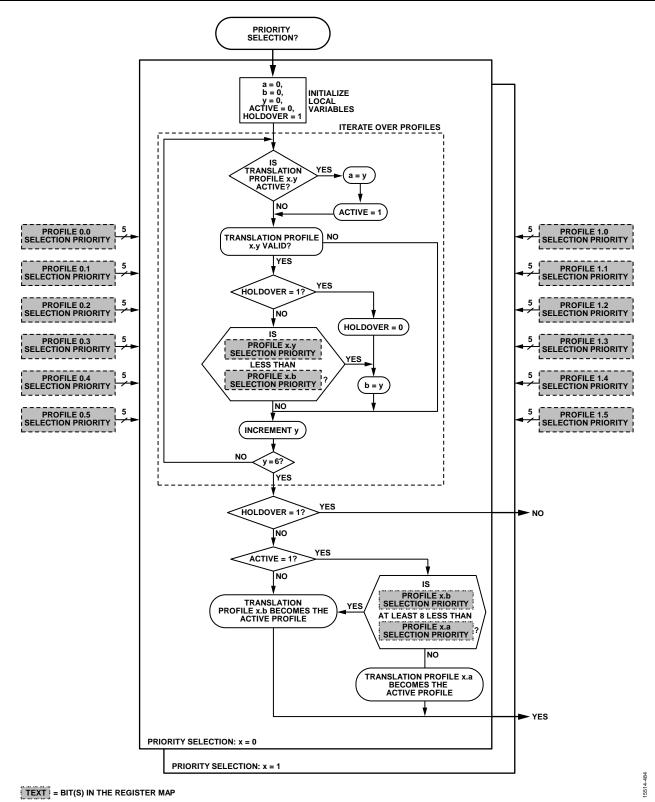

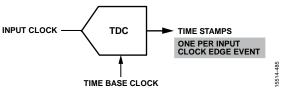

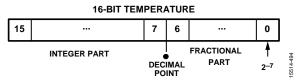

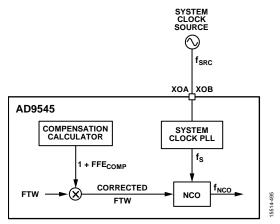

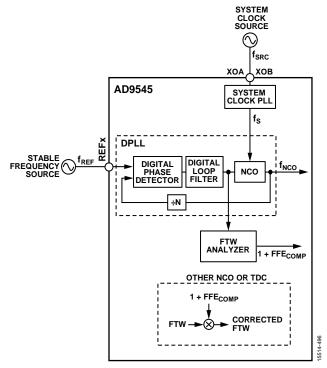

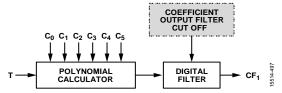

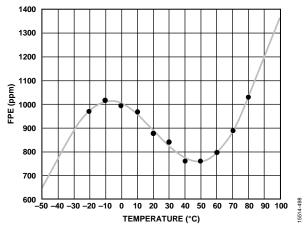

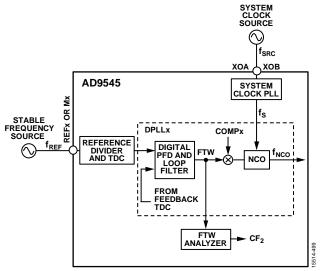

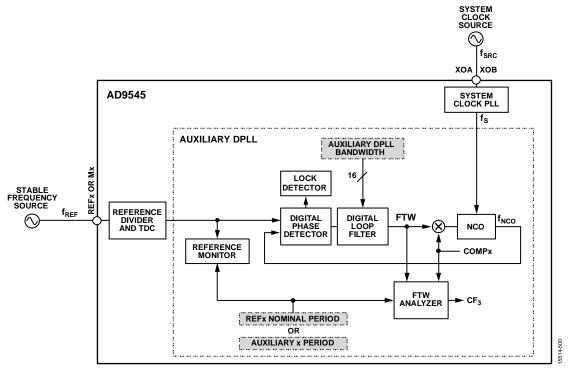

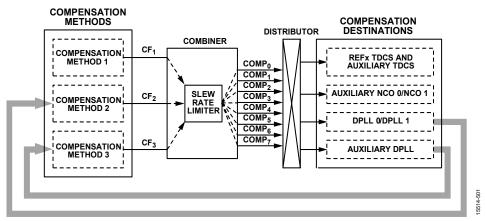

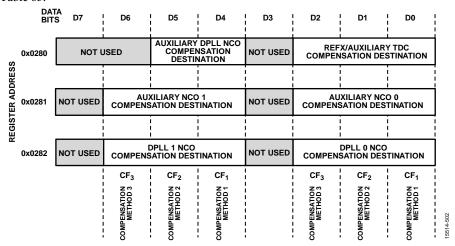

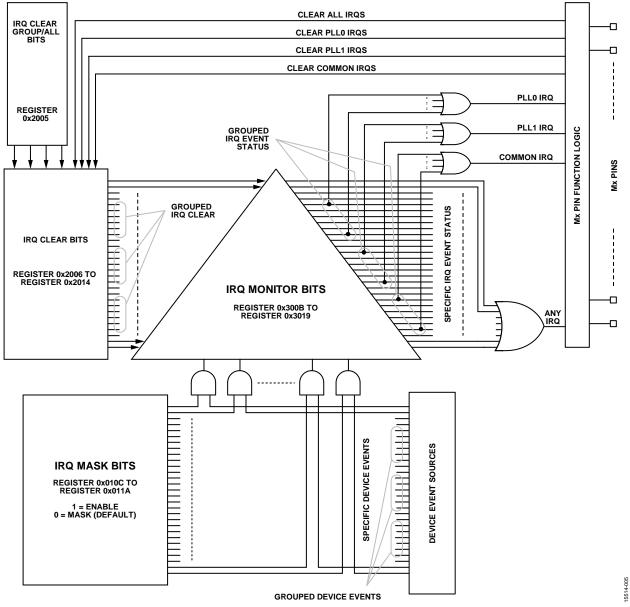

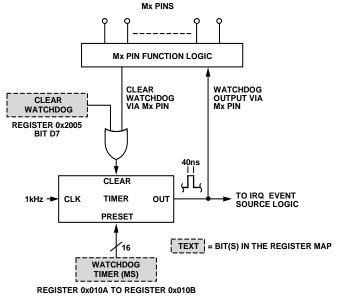

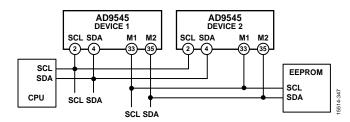

| Input Pulse Width                          | 900                  |     |                           | ps    |                                                                                                                                                                                                                                                                                                                                                                                                     |