# **Ethernet/Gigabit Ethernet Clock Generator**

## Data Sheet

# AD9574

### **FEATURES**

**Redundant input reference clock capability Reference monitoring function** Fully integrated VCO/PLL core Jitter (rms) 0.234 ps rms jitter (10 kHz to 10 MHz) at 156.25 MHz 0.243 ps rms jitter (12 kHz to 20 MHz) at 156.25 MHz Input frequency: 19.44 MHz or 25 MHz **Preset frequency translations** Using a 19.44 MHz input reference 19.44 MHz, 38.88 MHz, 77.76 MHz, 155.52 MHz Using a 25 MHz input reference 25 MHz, 33.33 MHz, 50 MHz, 66.67 MHz, 80 MHz, 100 MHz, 125 MHz, 133.3 MHz, 156.25 MHz, 160 MHz, 312.5 MHz Output drive formats: HSTL, LVDS, HCSL, and 1.8 V and 3.3 V CMOS Integrated loop filter (requires a single external capacitor) 2 copies of reference clock output Device configuration via strapping pins (PPRx) Space-saving 7 mm × 7 mm 48-lead LFCSP 3.3 V operation

#### APPLICATIONS

Ethernet line cards, switches, and routers SATA and PCI express Low jitter, low phase noise clock generation

#### **GENERAL DESCRIPTION**

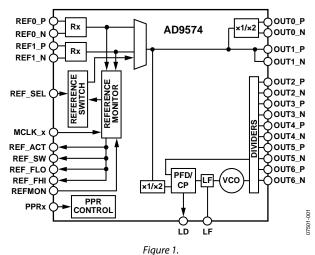

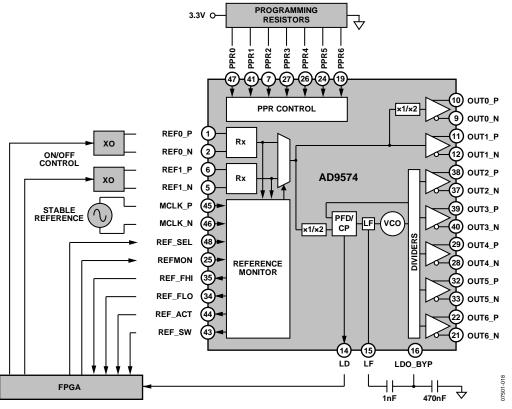

The AD9574 provides a multiple output clock generator function comprising a dedicated phase-locked loop (PLL) core optimized for Ethernet and gigabit Ethernet line card applications. The integer-N PLL design is based on the Analog Devices, Inc., proven portfolio of high performance, low jitter frequency synthesizers to maximize network performance. The AD9574 also benefits other applications requiring low phase noise and jitter performance.

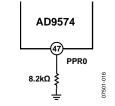

Configuring the AD9574 for a particular application requires only the connection of external pull-up or pull-down resistors to the appropriate pin program reader pins (PPRx). These pins provide control of the internal dividers for establishing the desired frequency translations, clock output functionality, and input reference functionality. Connecting an external 19.44 MHz or 25 MHz oscillator to one or both of the REF0\_P/REF0\_N or REF1\_P/REF1\_N reference inputs results in a set of output frequencies prescribed by the PPRx pins. Connecting a stable

#### Rev. B

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

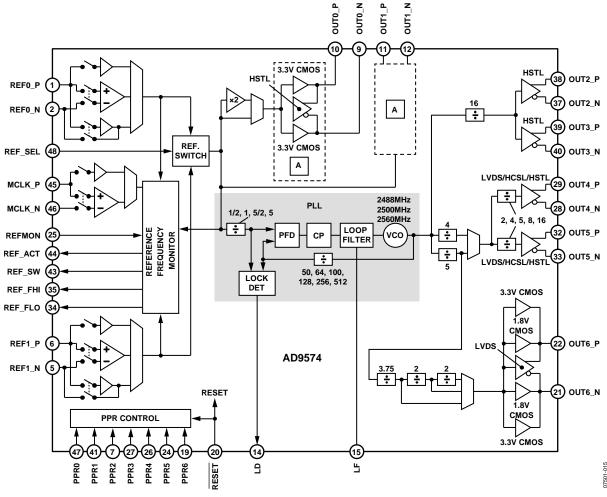

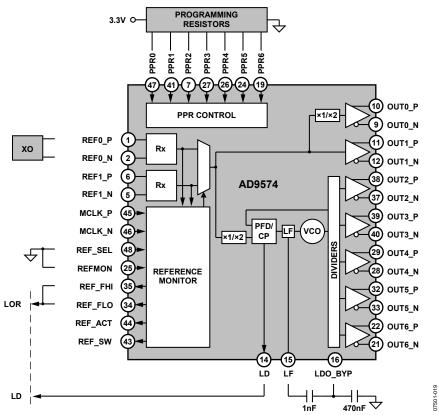

#### FUNCTIONAL BLOCK DIAGRAM

clock source (8 kHz/10 MHz/19.44 MHz/25 MHz/38.88 MHz) to the monitor clock input enables the optional monitor circuit providing quality of service (QoS) status for REF0 or REF1.

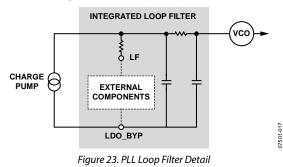

The PLL section consists of a low noise phase frequency detector (PFD), a precision charge pump (CP), a partially integrated loop filter (LF), a low phase noise voltage controlled oscillator (VCO), and feedback and output dividers. The divider values depend on the PPRx pins. The integrated loop filter requires only a single external capacitor connected to the LF pin.

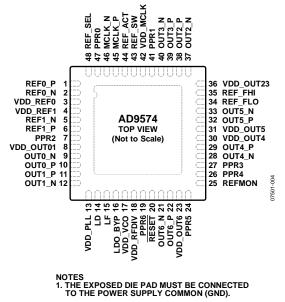

The AD9574 is packaged in a 48-lead 7 mm  $\times$  7 mm LFCSP, requiring only a single 3.3 V supply. The operating temperature range is  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Note that throughout this data sheet, OUT0 to OUT6, REF0, and REF1 refer to the respective channels, which consist of the differential pins, OUT0\_P/OUT0\_N to OUT6\_P/OUT6\_N, REF0\_P/REF0\_N, and REF1\_P/REF1\_N, respectively.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014–2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| Features                                               |

|--------------------------------------------------------|

| Applications                                           |

| Functional Block Diagram 1                             |

| General Description                                    |

| Revision History                                       |

| Specifications                                         |

| OUT0 Channel Absolute Clock Jitter 3                   |

| OUT1 Channel Absolute Clock Jitter 3                   |

| OUT2 and OUT3 Channels Absolute Clock Jitter 3         |

| OUT4 and OUT5 Channels Absolute Clock Jitter 4         |

| OUT6 Channel Absolute Clock Jitter 5                   |

| Clock Outputs (OUT0_x to OUT6_x)—Static                |

| Clock Outputs (OUT0_x to OUT6_x)—Dynamic6              |

| Monitor Clock Inputs (MCLK_x)—Static7                  |

| Monitor Clock Inputs (MCLK_x)—Dynamic                  |

| Reference Inputs (REF0_x and REF1_x)—Static            |

| Reference Inputs (REF0_x and REF1_x)—Dynamic           |

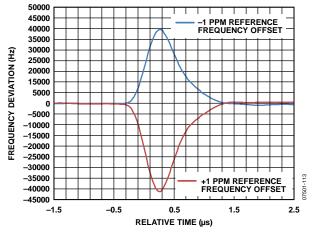

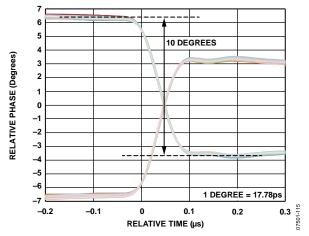

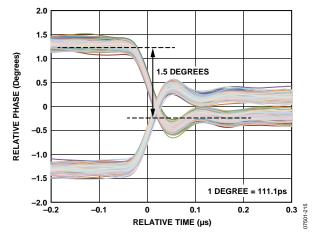

| Reference Switchover Output Disturbance                |

| Control Pins                                           |

| Status Pins10                                          |

| Power Supply and Dissipation10                         |

| Timing Specifications11                                |

| Timing Diagrams12                                      |

| Absolute Maximum Ratings                               |

| ESD Caution13                                          |

| Pin Configuration and Function Descriptions14          |

| Typical Performance Characteristics                    |

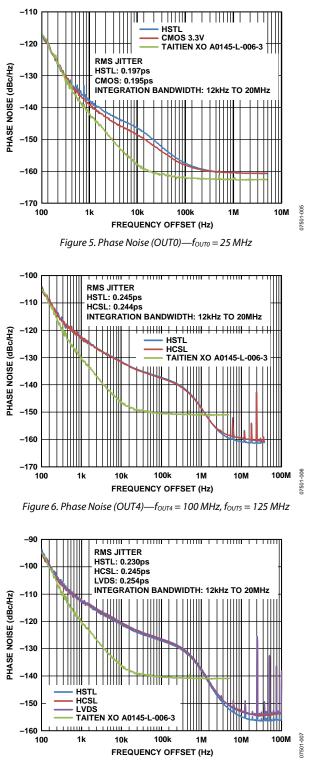

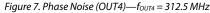

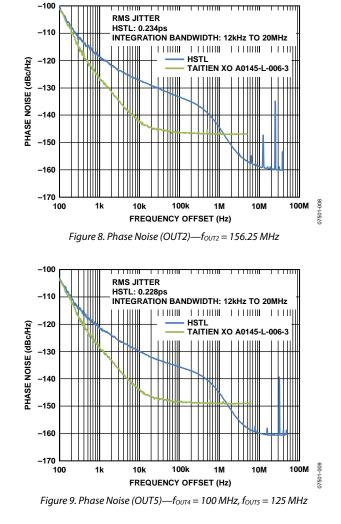

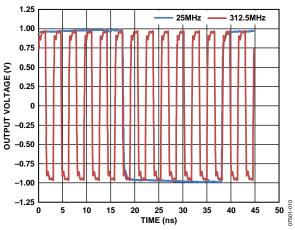

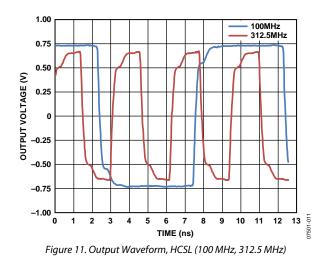

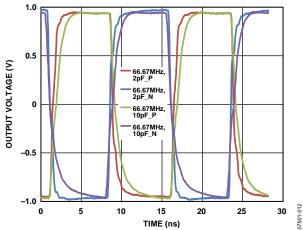

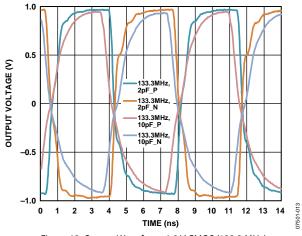

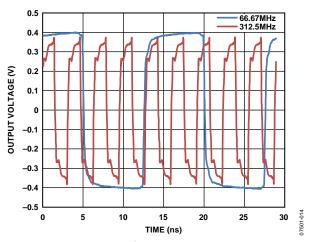

| Phase Noise and Voltage Waveforms                      |

| Reference Switching Frequency and Phase Disturbance 19 |

| Terminology                                            |

| Theory of Operation                                    |

| REVISION HISTORY                                       |

| 4/2017—Rev. A to Rev. B                                |

| Change to Figure 20                                    |

| Updated Outline Dimensions                             |

|                                                        |

| 1/2015—Rev. 0 to Rev. A                                |

| Changes to Table 13         | 9    |

|-----------------------------|------|

| Changes to Note 1, Table 17 | . 13 |

| Overview                                                         | 21 |

|------------------------------------------------------------------|----|

| PPRx Pins                                                        | 21 |

| PPR0—Reference Clock Input Configuration                         | 22 |

| PPR1—Frequency Translation Settings                              | 22 |

| PPR2—OUT0 and OUT1 Configuration                                 |    |

| PPR3—OUT4 and OUT5 Configuration                                 | 23 |

| PPR4—OUT6 Configuration                                          | 24 |

| PPR5—Reference Monitor Threshold                                 | 24 |

| PPR6—Monitor Clock (MCLK_x) Input Configuration . 2              | 24 |

| Dependency of PPR3 and PPR4 on PPR1                              | 24 |

| Power-On Reset (POR)                                             | 25 |

| Reference Clock Inputs                                           | 27 |

| Monitor Clock Input                                              | 27 |

| Reference Switching                                              | 27 |

| Reference Monitor                                                | 27 |

| PLL                                                              | 28 |

| Output Drivers                                                   | 29 |

| Output Clocks                                                    | 29 |

| Applications Information                                         | 30 |

| Dual Oscillator Reference Input Application                      | 30 |

| Simple, Single Oscillator Reference Input Application            | 31 |

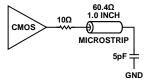

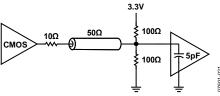

| Interfacing to CMOS Clock Outputs                                | 31 |

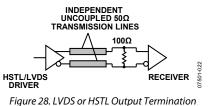

| Interfacing to LVDS and HSTL Clock Outputs                       | 32 |

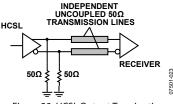

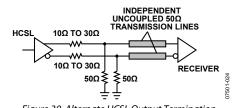

| Interfacing to HCSL Clock Outputs                                | 32 |

| Power Supply                                                     | 33 |

| Power and Grounding Considerations and Power Supply<br>Rejection | 33 |

| Thermal Performance                                              | 34 |

| Outline Dimensions                                               | 35 |

| Ordering Guide                                                   | 35 |

| Deleted Thermal Resistance Section and Table 18; Renumbered | L |

|-------------------------------------------------------------|---|

| Sequentially 13                                             | 3 |

| Changes to Power-On Reset (POR) Section                     |   |

| Added Figure 22; Renumbered Sequentially 20                 | 6 |

| Added Thermal Performance Section and Table 35              | 4 |

9/2014—Revision 0: Initial Version

## **SPECIFICATIONS**

## **OUTO CHANNEL ABSOLUTE CLOCK JITTER**

Typical values applicable under the conditions of  $V_S$  = 3.3 V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                                | Min | Тур   | Max | Unit   | Test Conditions/Comments                       |

|----------------------------------------------------------|-----|-------|-----|--------|------------------------------------------------|

| HIGH SPEED TRANSCEIVER LOGIC<br>(HSTL) INTEGRATED JITTER |     |       |     |        | Jitter integration bandwidth = 12 kHz to 5 MHz |

| 19.44 MHz Output                                         |     | 0.196 |     | ps rms |                                                |

| 25 MHz Output                                            |     | 0.179 |     | ps rms |                                                |

| 38.88 MHz Output                                         |     | 1.943 |     | ps rms |                                                |

| 50 MHz Output                                            |     | 1.523 |     | ps rms |                                                |

| 3.3 V CMOS INTEGRATED JITTER                             |     |       |     |        | Jitter integration bandwidth = 12 kHz to 5 MHz |

| 19.44 MHz Output                                         |     | 0.204 |     | ps rms |                                                |

| 25 MHz Output                                            |     | 0.178 |     | ps rms |                                                |

| 38.88 MHz Output                                         |     | 1.969 |     | ps rms |                                                |

| 50 MHz Output                                            |     | 1.446 |     | ps rms |                                                |

### **OUT1 CHANNEL ABSOLUTE CLOCK JITTER**

Typical values applicable under the conditions of  $V_S$  = 3.3 V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                    | Min | Тур   | Max | Unit   | Test Conditions/Comments                       |

|------------------------------|-----|-------|-----|--------|------------------------------------------------|

| HSTL INTEGRATED JITTER       |     |       |     |        | Jitter integration bandwidth = 12 kHz to 5 MHz |

| 19.44 MHz Output             |     | 0.175 |     | ps rms |                                                |

| 25 MHz Output                |     | 0.153 |     | ps rms |                                                |

| 3.3 V CMOS INTEGRATED JITTER |     |       |     |        | Jitter integration bandwidth = 12 kHz to 5 MHz |

| 19.44 MHz Output             |     | 0.184 |     | ps rms |                                                |

| 25 MHz Output                |     | 0.160 |     | ps rms |                                                |

## OUT2 AND OUT3 CHANNELS ABSOLUTE CLOCK JITTER

Typical values applicable under the conditions of  $V_s = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted. Frequency multiplier (×2) at PLL input enabled.

| Table 3.                                           |     |       |     |        |                                                 |

|----------------------------------------------------|-----|-------|-----|--------|-------------------------------------------------|

| Parameter                                          | Min | Тур   | Max | Unit   | Test Conditions/Comments                        |

| HSTL INTEGRATED JITTER                             |     |       |     |        |                                                 |

| Jitter Integration Bandwidth = 10 kHz to 10 MHz    |     |       |     |        |                                                 |

| 155.52 MHz Output                                  |     | 0.244 |     | ps rms |                                                 |

| 156.25 MHz Output                                  |     | 0.234 |     | ps rms |                                                 |

| 160 MHz Output                                     |     | 1.290 |     | ps rms | Frequency multiplier (×2) at PLL input bypassed |

| Jitter Integration Bandwidth = 12 kHz to 20 MHz    |     |       |     |        |                                                 |

| 155.52 MHz Output                                  |     | 0.470 |     | ps rms |                                                 |

| 156.25 MHz Output                                  |     | 0.243 |     | ps rms |                                                 |

| 160 MHz Output                                     |     | 1.329 |     | ps rms | Frequency multiplier (×2) at PLL input bypassed |

| Jitter Integration Bandwidth = 1.875 MHz to 20 MHz |     |       |     |        |                                                 |

| 155.52 MHz Output                                  |     | 0.409 |     | ps rms |                                                 |

| 156.25 MHz Output                                  |     | 0.100 |     | ps rms |                                                 |

| 160 MHz Output                                     |     | 1.257 |     | ps rms | Frequency multiplier (×2) at PLL input bypassed |

## OUT4 AND OUT5 CHANNELS ABSOLUTE CLOCK JITTER

Typical values applicable under the conditions of  $V_s = 3.3 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ . Frequency multiplier (×2) at PLL input enabled unless otherwise indicated.

| HSTL INTEGRATED JITTER     Input = crystal oscillator       Jitter Integration Bandwidth = 10 kHz to 10 MHz     0.251     ps rms       38.88 MHz Output     0.245     ps rms       80 MHz Output     0.245     ps rms       100 MHz Output     0.240     ps rms       125 MHz Output     0.228     ps rms       160 MHz Output     0.234     ps rms       17.76 MHz Output     0.228     ps rms       160 MHz Output     0.234     ps rms       17.76 MHz Output     0.234     ps rms       17.76 MHz Output     0.234     ps rms       180 MHz Output     0.234     ps rms       1125 MHz Output     0.234     ps rms       1125 MHz Output     0.234     ps rms       100 MHz Output     0.232     ps rms       100 MHz Output     0.232     ps rms       100 MHz Output     0.233     ps rms       160 MHz Output     0.236     ps rms       1125 MHz Output     0.389     ps rms       1125 MHz Output     0.430     ps rms       125 MHz Output     0.115     ps rms       125 M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |         |     |          |                                                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------|-----|----------|-------------------------------------------------|

| Jitter Integration Bandwidth = 10 kHz to 10 MHz<br>38.88 MHz Output<br>77.76 MHz Output<br>100 MHz Output<br>125 MHz Output<br>100 MHz Output<br>125 MHz Output<br>160 MHz Output<br>125 MHz Output<br>0226 ps rms<br>125 MHz Output<br>125 MHz Outp |                                         | Min Typ | Мах | Unit     | Test Conditions/Comments                        |

| 38.88 MHz Output         0.251         ps rms         ps rms           77.76 MHz Output         0.245         ps rms         ps rms           80 MHz Output         1.267         ps rms         ps rms           100 MHz Output         0.240         ps rms         ps rms           125 MHz Output         0.228         ps rms         ps rms           160 MHz Output         0.234         ps rms         Frequency multiplier (x2) at input bypassed           312.5 MHz Output         0.234         ps rms         Frequency multiplier (x2) at input bypassed           312.5 MHz Output         0.438         ps rms         Frequency multiplier (x2) at input bypassed           312.5 MHz Output         0.488         ps rms         Frequency multiplier (x2) at input bypassed           100 MHz Output         0.252         ps rms         Frequency multiplier (x2) at input bypassed           100 MHz Output         0.233         ps rms         Frequency multiplier (x2) at input bypassed           312.5 MHz Output         0.389         ps rms         Frequency multiplier (x2) at input bypassed           312.5 MHz Output         0.389         ps rms         Frequency multiplier (x2) at input bypassed           312.5 MHz Output         0.430         ps rms         Frequency multiplier (x2) at input bypassed <td>RATED JITTER</td> <td></td> <td></td> <td></td> <td>Input = crystal oscillator</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RATED JITTER                            |         |     |          | Input = crystal oscillator                      |

| 77.76 MHz Output0.245ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.240ps rmsFrequency multiplier (x2) at<br>input bypassed125 MHz Output0.228ps rmsFrequency multiplier (x2) at<br>input bypassed160 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed310 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.252ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at<br>input bypassed1100 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.430ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.0115ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.0115ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.0115ps rmsFrequency multiplier (x2) at<br>input bypassed1105 MHz Output0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | gration Bandwidth = 10 kHz to 10 MHz    |         |     |          |                                                 |

| 80 MHz Output1.267ps rms<br>ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.240ps rms<br>ps rmsFrequency multiplier (x2) at<br>input bypassed160 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassedJitter Integration Bandwidth = 12 kHz to 20 MHz0.488ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.252ps rmsFrequency multiplier (x2) at<br>input bypassedps rms100 MHz Output0.252ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed1100 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed1100 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.430ps rmsJitter Integration Bandwidth = 50 kHz to 80 MHz<br>312.5 MHz Output1.242ps rmsJitter Integration Bandwidth = 10.875 MHz to 20 MHz1.242ps rms100 MHz Output0.430ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms100 MHz Output0.238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MHz Output                              | 0.251   |     | ps rms   |                                                 |

| 100 MHz Output0.240ps rmsinput bypassed125 MHz Output0.228ps rmsFrequency multiplier (x2) at<br>input bypassed160 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.488ps rmsJitter Integration Bandwidth = 12 kHz to 20 MHz0.488ps rms77.76 MHz Output0.488ps rms80 MHz Output0.488ps rms100 MHz Output0.252ps rms100 MHz Output0.252ps rms125 MHz Output0.233ps rms160 MHz Output0.236ps rms125 MHz Output0.389ps rms160 MHz Output0.389ps rms17.76 MHz Output0.430ps rms160 MHz Output0.430ps rms125 MHz Output0.430ps rms160 MHz Output0.430ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms160 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.238ps rms125 MHz Output0.22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MHz Output                              | 0.245   |     | ps rms   |                                                 |

| 100 MHz Output0.240ps rmsps rms125 MHz Output0.228ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.234ps rmsFrequency multiplier (x2) at<br>input bypassed30 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed30 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.480ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output1.242ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.015ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.072ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.072ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.0480ps rmsFrequency multipl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                       | 1.267   |     | ps rms   | Frequency multiplier (×2) at PLL input bypassed |

| 160 MHz Output1.277ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.234ps rmsps rmsJitter Integration Bandwidth = 12 kHz to 20 MHz0.488ps rmsFrequency multiplier (x2) at<br>input bypassed77.76 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.252ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at<br>input bypassed160 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassedJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rms77.76 MHz Output0.115ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at<br>input bypassed125 MHz Output0.072ps rmsFrequency multiplier (x2) at<br>input bypassed125 MHz Output0.072ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.072ps rmsInput = crystal oscillatorJITTERJITTERJITTERJITTERJITTERJITTER <td< td=""><td>Hz Output</td><td>0.240</td><td></td><td>ps rms</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Hz Output                               | 0.240   |     | ps rms   |                                                 |

| 312.5 MHz Output0.234ps rmsinput bypassedJitter Integration Bandwidth = 12 kHz to 20 MHz0.488ps rmsps rms77.76 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.252ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at<br>input bypassed160 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at<br>input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at<br>input bypassedJitter Integration Bandwidth = 50 kHz to 80 MHz0.430ps rmsFrequency multiplier (x2) at<br>input bypassedJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsFrequency multiplier (x2) at<br>input bypassedJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at<br>input bypassedps rms125 MHz Output0.072ps rmsInput bypassed160 MHz Output0.072ps rmsInput bypassed312.5 MHz Output0.072ps rmsInput erystal oscillatorJITTERJITTERUndut = 10 kHz to 10 MHz0.236ps rmsJITTER100 MHz Output0.226ps rmsInput erystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Hz Output                               | 0.228   |     | ps rms   |                                                 |

| Jitter Integration Bandwidth = 12 kHz to 20 MHzNPrequency multiplier (x2) at<br>input bypassed77.76 MHz Output0.488ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.252ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.233ps rms125 MHz Output0.233ps rms160 MHz Output0.236ps rmsJitter Integration Bandwidth = 50 kHz to 80 MHz0.389ps rmsJitter Integration Bandwidth = 50 kHz to 80 MHz0.430ps rmsJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rms100 MHz Output0.115ps rmsFrequency multiplier (x2) at<br>input bypassed100 MHz Output0.115ps rms125 MHz Output0.089ps rms100 MHz Output0.072ps rms125 MHz Output0.072ps rms125 MHz Output0.072ps rms117 ERInput bypassedJITTERInput bypassedJITTERInput bypassedJITTERInput bypassed100 MHz Output0.238JITTERInput bypassedJITTERInput bypassedJITTERInput bypassedJITTERInput bypassedJITTERInput bypassedJITTER0.236JITTERInput bypassedJITTERInput bypassedJITTERInput bypassedJITTERInput bypasse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hz Output                               | 1.277   |     | ps rms   | Frequency multiplier (×2) at PLL input bypassed |

| 77.76 MHz Output0.488ps rmsFrequency multiplier (x2) at input bypassed80 MHz Output0.252ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at input bypassed160 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.430ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.430ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.089ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.072ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.072ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.072ps rmsInput erystal oscillatorJITTERInput bypassedInput erystal oscillatorJITTERInput Erystal oscillatorInput erystal oscillatorJITTER0.026ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.238ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MHz Output                              | 0.234   |     | ps rms   |                                                 |

| 77.76 MHz Output0.488ps rmsFrequency multiplier (x2) at input bypassed80 MHz Output0.252ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.233ps rmsFrequency multiplier (x2) at input bypassed160 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.389ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.430ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.430ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.089ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.072ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.072ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.072ps rmsInput erystal oscillatorJITTERInput bypassedInput erystal oscillatorJITTERInput Erystal oscillatorInput erystal oscillatorJITTER0.026ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.238ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                       |         |     |          |                                                 |

| 80 MHz Output1.314ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.252ps rmsinput bypassed125 MHz Output0.233ps rmsFrequency multiplier (x2) at input bypassed160 MHz Output1.321ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassedJitter Integration Bandwidth = 50 kHz to 80 MHz0.389ps rmsFrequency multiplier (x2) at input bypassedJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsFrequency multiplier (x2) at input bypassedJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.0115ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.072ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.072ps rmsInput bypassed100 MHz Output0.072ps rmsInput erystal oscillatorJITTERInput = 10 kHz to 10 MHz0.238ps rmsInput = crystal oscillatorJITTER0.0142 Output0.238ps rmsInput = crystal oscillatorJITTER0.026ps rmsps rmsInput = crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                       | 0.488   |     | ps rms   |                                                 |

| 100 MHz Output0.252ps rms125 MHz Output0.233ps rms160 MHz Output1.321ps rms312.5 MHz Output0.236ps rmsJitter Integration Bandwidth = 50 kHz to 80 MHz0.236ps rmsJitter Integration Bandwidth = 50 kHz to 80 MHz0.389ps rmsJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rmsJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rms77.76 MHz Output0.430ps rms100 MHz Output0.115ps rms100 MHz Output0.115ps rms125 MHz Output0.089ps rms160 MHz Output0.072ps rms160 MHz Output0.072ps rms1125 MHz Output0.238ps rms1125 MHz Output0.238ps rms1125 MHz Output0.238ps rms1125 MHz Output0.238ps rms100 MHz Output0.238ps rms100 MHz Output0.238ps rms100 MHz Output0.236ps rms125 MHz Output0.226ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                       | 1.314   |     |          | Frequency multiplier (×2) at PLL input bypassed |

| 125 MHz Output0.233ps rmsFrequency multiplier (x2) at input bypassed160 MHz Output0.236ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Hz Output                               | 0.252   |     | ps rms   |                                                 |

| 160 MHz Output1.321ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.236ps rmsinput bypassedJitter Integration Bandwidth = 50 kHz to 80 MHz0.389ps rmsrms312.5 MHz Output0.389ps rmsrmsJitter Integration Bandwidth = 1.875 MHz to 20 MHz0.430ps rms77.76 MHz Output0.430ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.115ps rmsFrequency multiplier (x2) at input bypassed100 MHz Output0.072ps rmsFrequency multiplier (x2) at input bypassed312.5 MHz Output0.072ps rmsInput = crystal oscillatorHIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED<br>JITTERJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rms100 MHz Output0.238ps rmsInput = crystal oscillatorJitter Integration Bandwidth = 10 kHz to 10 MHz0.226ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                       | 0.233   |     |          |                                                 |

| 312.5 MHz Output0.236ps rmsn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                       | 1.321   |     |          | Frequency multiplier (×2) at PLL input bypassed |

| Jitter Integration Bandwidth = 50 kHz to 80 MHz<br>312.5 MHz Output 0.389 ps rms<br>Jitter Integration Bandwidth = 1.875 MHz to 20 MHz<br>77.76 MHz Output 0.430 ps rms<br>80 MHz Output 1.242 ps rms<br>100 MHz Output 0.115 ps rms<br>125 MHz Output 0.115 ps rms<br>160 MHz Output 1.248 ps rms<br>160 MHz Output 0.072 ps rms<br>312.5 MHz Output 0.0GIC (HCSL) INTEGRATED<br>JITTER<br>Jitter Integration Bandwidth = 10 kHz to 10 MHz<br>125 MHz Output 0.238 ps rms<br>125 MHz Output 0.226 ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MHz Output                              | 0.236   |     | ps rms   |                                                 |

| 312.5 MHz Output0.389ps rmsIndex of the second sec                                                                                                                                                                                                                                                                                                      | •                                       |         |     |          |                                                 |

| Jitter Integration Bandwidth = 1.875 MHz to 20 MHz<br>77.76 MHz Output 0.430 ps rms<br>80 MHz Output 1.242 ps rms Frequency multiplier (×2) at input bypassed<br>100 MHz Output 0.115 ps rms<br>125 MHz Output 0.089 ps rms<br>160 MHz Output 1.248 ps rms Frequency multiplier (×2) at input bypassed<br>312.5 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at input bypassed<br>1125 MHz Output 0.072 ps rms Frequency multiplier (×2) at                                                                                                                                                                                                 | -                                       | 0.389   |     | ps rms   |                                                 |

| 77.76 MHz Output0.430ps rmsps rmsFrequency multiplier (×2) at input bypassed80 MHz Output0.115ps rmsFrequency multiplier (×2) at input bypassed100 MHz Output0.0115ps rmsFrequency multiplier (×2) at input bypassed125 MHz Output0.089ps rmsFrequency multiplier (×2) at input bypassed160 MHz Output1.248ps rmsFrequency multiplier (×2) at input bypassed312.5 MHz Output0.072ps rmsFrequency multiplier (×2) at input bypassed312.5 MHz Output0.072ps rmsFrequency multiplier (×2) at input bypassedJITTER100 MHz Output0.072ps rmsJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rmsInput = crystal oscillator100 MHz Output0.226ps rmsps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •                                       |         |     |          |                                                 |

| 80 MHz Output1.242ps rmsFrequency multiplier (×2) at<br>input bypassed100 MHz Output0.115ps rms125 MHz Output0.089ps rms160 MHz Output1.248ps rms160 MHz Output0.072ps rms312.5 MHz Output0.072ps rmsHIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED<br>JITTERrecrystal oscillatorJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rms125 MHz Output0.226ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                       | 0.430   |     | ps rms   |                                                 |

| 100 MHz Output0.115ps rms125 MHz Output0.089ps rms160 MHz Output1.248ps rms312.5 MHz Output0.072ps rmsHIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED<br>JITTERps rmsInput = crystal oscillatorJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rms125 MHz Output0.226ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | •                                       |         |     |          | Frequency multiplier (×2) at PLL input bypassed |

| 125 MHz Output0.089ps rmsFrequency multiplier (×2) at<br>input bypassed160 MHz Output1.248ps rmsFrequency multiplier (×2) at<br>input bypassed312.5 MHz Output0.072ps rmsInput = crystal oscillatorHIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED<br>JITTERInput = crystal oscillatorInput = crystal oscillatorJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rmsps rms100 MHz Output0.226ps rmssrms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Hz Output                               | 0.115   |     | ps rms   |                                                 |

| 160 MHz Output1.248ps rmsFrequency multiplier (×2) at input bypassed312.5 MHz Output0.072ps rmsInput bypassedHIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED JITTERInput = crystal oscillatorInput = crystal oscillatorJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rmsInput = crystal oscillator100 MHz Output0.236ps rmsInput = crystal oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                       | 0.089   |     |          |                                                 |

| 312.5 MHz Output0.072ps rmsHIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED<br>JITTER<br>Jitter Integration Bandwidth = 10 kHz to 10 MHzInput = crystal oscillator100 MHz Output0.238ps rms125 MHz Output0.226ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                       |         |     |          | Frequency multiplier (×2) at PLL input bypassed |

| HIGH SPEED CURRENT SINKING LOGIC (HCSL) INTEGRATED<br>JITTERInput = crystal oscillatorJitter Integration Bandwidth = 10 kHz to 10 MHz0.238ps rms100 MHz Output0.226ps rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MHz Output                              | 0.072   |     | ps rms   |                                                 |