# 4-Channel AFE, Digital Controller, and PWM for Battery Formation and Testing

## **FEATURES**

- ▶ Precise measurement of the voltage and current

- ▶ 4 PWM control channels up to 14 bits (effective) resolution

- ▶ Selectable synchronous and asynchronous rectifier operation

- ▶ Programmable dead time compensation

- ▶ Programmable switching frequency from 62.5 kHz to 500 kHz in powers of 2 steps

- ▶ Multiphase operation

- Interchip digital current sharing

- ▶ Interchip frequency synchronization

- ▶ Digital control loop

- ▶ Programmable PID loop filters

- ▶ Fast dc bus voltage feedforward

- ▶ Integrated spectrum analysis per channel

- ▶ SPI port control and status interface

- ▶ Host interrupt on programmable status changes

- ▶ Constant current and constant voltage operating modes

- ▶ 15-bit setpoint resolution

- ▶ Input and output inrush current protection

- ▶ External NTC thermistor temperature sensing

- ▶ Internal die temperature measurement

- User calibration of input voltages and currents

- ▶ 0°C to 85°C operation

## **APPLICATIONS**

- Battery formation and testing

- ▶ High efficiency battery test systems with recycle capability

- ▶ Battery conditioning (charging and discharging) systems

## **GENERAL DESCRIPTION**

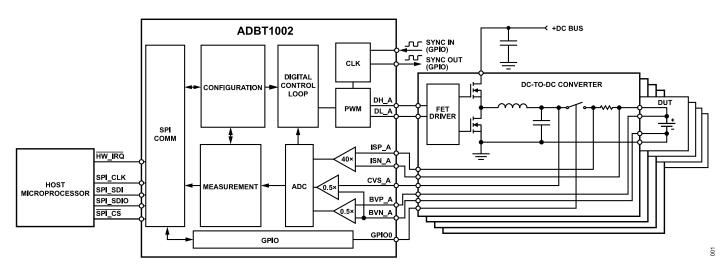

The ADBT1002 is a flexible, feature rich digital controller that targets high volume battery testing and formation manufacturing and precision battery test instrumentation applications. The ADBT1002 is optimized for minimal component count, maximum flexibility, and minimum design time. Features include differential remote voltage sense, current sense, pulse-width modulation (PWM) generation, frequency synchronization, overvoltage protection (OVP), and current sharing. Programmable protection features include overcurrent protection (OCP), OVP limiting, and external overtemperature protection (OTP).

Parameters can be programmed over the serial peripheral interface (SPI), providing extensive programming of the integrated loop filter, PWM signal timing, and soft start timing. The SPI provides access to the many monitoring and system test functions. Reliability is improved through a built-in checksum and programmable protection circuits.

A comprehensive graphical user interface (GUI) is provided for simple system and channel configuration and programming of the safety features. The ADBT1002 is available in a 100-lead LQFP EP.

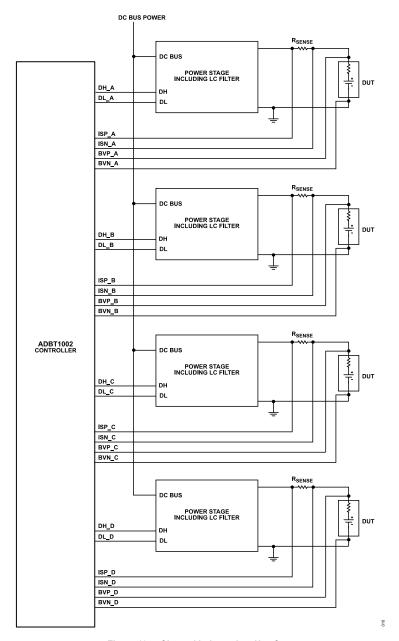

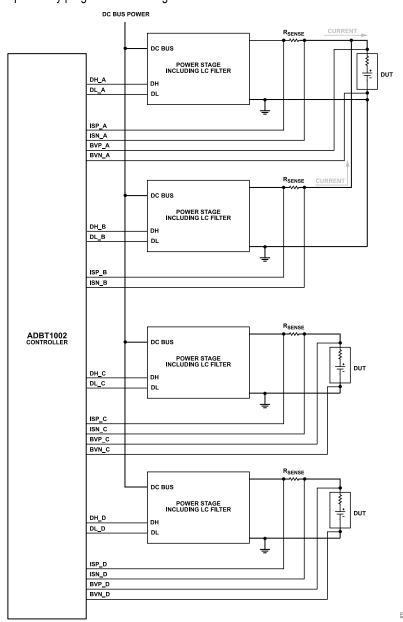

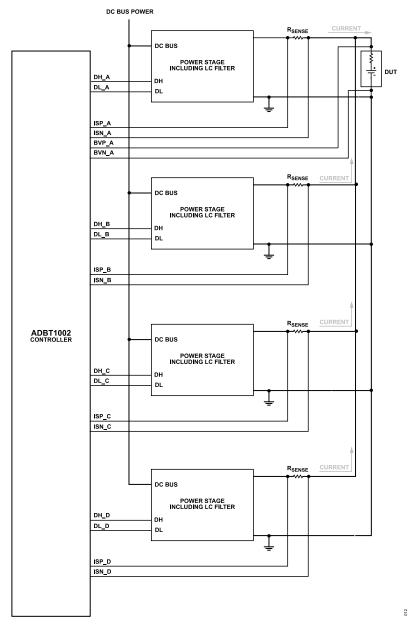

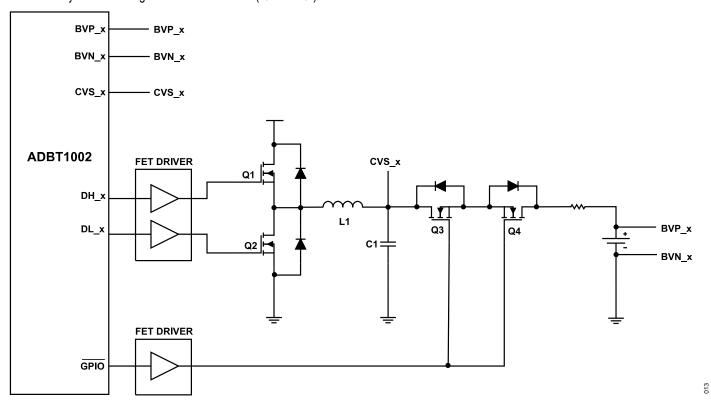

## TYPICAL APPLICATION DIAGRAM

Figure 1.

**Data Sheet**

# **TABLE OF CONTENTS**

| Features                                    | . 1 |

|---------------------------------------------|-----|

| Applications                                | .1  |

| General Description                         |     |

| Typical Application Diagram                 | . 1 |

| Specifications                              | . 3 |

| Analog Front End and Controller             |     |

| Specifications                              | . 3 |

| Absolute Maximum Ratings                    | 8   |

| Thermal Resistance                          | . 8 |

| Soldering                                   | . 8 |

| Electrostatic Discharge (ESD) Ratings       | 8   |

| ESD Caution                                 | 8   |

| Pin Configuration and Function Descriptions | . 9 |

| Theory of Operation                         |     |

| Overview                                    | 13  |

| Analog Front End                            | 14  |

| Digital Controller                          | 14  |

| Host SPI                                    | 14  |

| Host Interrupt Request                      | 14  |

| Clocking                                    | 14  |

| GPIOx Pins                                  |     |

| Auxiliary ADC                               |     |

| Supports Coulombic Efficiency Measurement   | 14  |

| Supports Precharge Operation            | 15 |

|-----------------------------------------|----|

| Sequencer                               |    |

| Instruction Definition                  |    |

| Sequencing Modes                        |    |

| Charge and Discharge Instruction Modes  |    |

| Charge and Discharge Instruction Limits |    |

| Slew Rate                               | 19 |

| Parallel Operation                      | 19 |

| Flags                                   |    |

| Global Register Settings                | 20 |

| Channel Static Settings                 | 20 |

| Instruction Set Architecture            | 20 |

| Sequencer Operation Example             | 24 |

| Memory Mapped Registers                 | 25 |

| Host SPI Interface Details              | 37 |

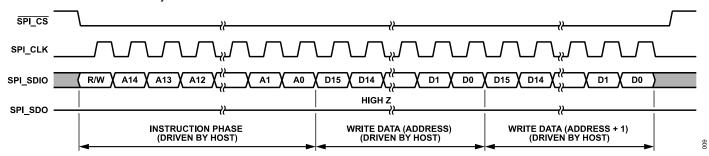

| SPI Overview                            | 37 |

| Communications Protocols                | 37 |

| Applications Information                | 39 |

| Calibration                             | 39 |

| Diagnostics                             | 39 |

| Operating Use Cases                     | 39 |

| Outline Dimensions                      |    |

| Ordering Guide                          | 44 |

# **SPECIFICATIONS**

$AHVDD = 15 \text{ V, AHVSS} = -15 \text{ V, VDDIO} = AVDD = DVDD = 3.3 \text{ V, and } T_A = 0 ^{\circ}\text{C to } 85 ^{\circ}\text{C, unless otherwise noted.}$

# ANALOG FRONT END AND CONTROLLER SPECIFICATIONS

Table 1.

| Parameter                                             | Test Conditions/Comments                             | Min       | Тур | Max       | Unit   |

|-------------------------------------------------------|------------------------------------------------------|-----------|-----|-----------|--------|

| CURRENT SENSE CHANNEL                                 |                                                      |           |     |           |        |

| Gain                                                  |                                                      |           | 40  |           | V/V    |

| Gain Error                                            | V <sub>OUT</sub> =±2 V                               |           |     | 0.2       | %      |

| Gain Drift                                            |                                                      |           |     | 10        | ppm/°C |

| System Input Offset Voltage                           |                                                      | -10       |     | +10       | LSB    |

| System Input Offset Voltage Drift                     | RTI                                                  |           |     | 0.235     | LSB/°C |

| Input Bias Current                                    | V <sub>ICM</sub> = V <sub>REF</sub> /2               |           | 30  | 500       | nA     |

| Input Differential Voltage Range                      |                                                      | -62.5     |     | +62.5     | mV     |

| Input Common-Mode Voltage Range                       |                                                      | AHVSS + 5 |     | AHVDD - 5 | V      |

| Differential Input Impedance                          | By design                                            |           | 24  |           | kΩ     |

| Common-Mode Input Impedance                           | By design                                            |           | 246 |           | kΩ     |

| Input Resistance                                      | Both input pins                                      |           | 492 |           | kΩ     |

| Common-Mode Rejection Ratio (CMRR)                    |                                                      | 100       | 110 |           | dB     |

| CMRR Drift                                            |                                                      |           |     | 0.05      | ppm/°C |

| Small Signal −3 dB Bandwidth (Gain = 40) <sup>1</sup> | T <sub>A</sub> = 25°C, V <sub>OUT</sub> = 100 mV p-p |           | 600 |           | kHz    |

| Power Supply Rejection Ratio (PSRR)                   | Supply voltage (Vs) = ±5 V to ±18 V                  | 120       |     |           | dB     |

| Slew Rate                                             | V <sub>OUT</sub> = ±2 V                              |           | 0.6 |           | V/µs   |

| Readout Data Signal-to-Noise Ratio (SNR)              | $MAF^2 = 16$ , FIR <sup>3</sup> on                   |           |     |           | '      |

| Update Rate <sup>4</sup>                              |                                                      |           |     |           |        |

| 31.25 kHz (OSR = 32)                                  |                                                      |           | 66  |           | dB     |

| 15.625 kHz (OSR = 64)                                 |                                                      |           | 69  |           | dB     |

| 7.8125 kHz (OSR = 128)                                |                                                      |           | 72  |           | dB     |

| 3.90625 kHz (OSR = 256)                               |                                                      |           | 75  |           | dB     |

| Full-Scale Input Range                                |                                                      | -60       |     | +60       | mV     |

| VOLTAGE SENSE AND CAPACITOR VOLTAGE<br>SENSE CHANNEL  |                                                      |           |     |           |        |

| Gain                                                  |                                                      |           | 0.5 |           | V/V    |

| Gain Error                                            | V <sub>OUT</sub> = ±2 V                              |           |     | 0.2       | %      |

| Gain Drift                                            |                                                      |           |     | 10        | ppm/°C |

| Input Offset Voltage                                  |                                                      | -10       |     | +10       | LSB    |

| Offset Voltage Drift                                  |                                                      |           |     | 0.235     | LSB/°C |

| Input Common-Mode Voltage Range                       |                                                      | AHVSS + 5 |     | AHVDD - 5 | V      |

| Differential Input Impedance                          | By design                                            | 0.85      | 1   |           | ΜΩ     |

| Common-Mode Input Impedance                           | By design                                            |           | 375 |           | kΩ     |

| Input Resistance                                      | Noninverting pin                                     |           | 750 |           | kΩ     |

|                                                       | Inverting pin                                        |           | 375 |           | kΩ     |

| Small Signal −3 dB Bandwidth (G = 0.5) <sup>5</sup>   | $T_A = 25^{\circ}C$ , $V_{OUT} = 100 \text{ mV p-p}$ |           | 200 |           | kHz    |

| CMRR                                                  |                                                      |           |     |           |        |

| BVx_x                                                 |                                                      | 80        | 90  |           | dB     |

| CVS_x                                                 |                                                      | 78        | 90  |           | dB     |

analog.com Rev. 0 | 3 of 44

# **SPECIFICATIONS**

Table 1.

| Parameter                                       | Test Conditions/Comments          | Min   | Тур    | Max   | Unit         |

|-------------------------------------------------|-----------------------------------|-------|--------|-------|--------------|

| CMRR Drift                                      |                                   |       |        |       |              |

| BVx_x                                           |                                   |       |        | 0.235 | ppm/°C       |

| CVS_x                                           |                                   |       |        | 3     | ppm/°C       |

| PSRR                                            |                                   | 100   | 120    |       | dB           |

| Slew Rate                                       |                                   |       | 0.15   |       | V/µs         |

| Power Dissipation                               |                                   |       | 30     |       | mW           |

| Readout Data SNR                                | MAF = 16, FIR on                  |       |        |       |              |

| Update Rate                                     |                                   |       |        |       |              |

| 31.25 kHz (OSR = 32)                            |                                   |       | 79     |       | dB           |

| 15.625 kHz (OSR = 64)                           |                                   |       | 80     |       | dB           |

| 7.8125 kHz (OSR = 128)                          |                                   |       | 81     |       | dB           |

| 3.90625 kHz (OSR = 256)                         |                                   |       | 81     |       | dB           |

| Full-Scale Input Range                          |                                   | -4.8  | 0.     | +4.8  | V            |

| BATTERY CURRENT AND VOLTAGE ADCS                | V <sub>REF</sub> = 2.5 V          | 7.0   |        |       | v            |

| SNR                                             | 1 kHz sine wave at 80% full scale |       | 70     |       | dB           |

| Signal-to-Noise-and-Distortion (SINAD) Ratio    | TRIESTIC WAVE at 00 /0 Idil Scale |       | 70     |       | dB           |

| Resolution                                      |                                   |       | 12     |       | Bits         |

| Differential Nonlinearity (DNL) <sup>6</sup>    |                                   | -1    | 12     | +1    | LSB          |

| Integral Nonlinearity (INL)                     | Internal valtage reference        | -3    |        | +3    | LSB          |

| , ,                                             | Internal voltage reference        | -3    | 4      | +3    | MHz/Channel  |

| Sampling Rate                                   |                                   |       | 1      |       | MINZ/Channel |

| VOLTAGE REFERENCE (INTERNAL)                    |                                   | 0.405 | 0.500  | 0.505 | .,           |

| Voltage Range                                   |                                   | 2.495 | 2.500  | 2.505 | V            |

| Temperature Coefficient                         | DEFOAD 4 5                        |       | 7      | 11    | ppm/°C       |

| RMS Noise                                       | REFCAP = 1 µF                     |       | 7      |       | μV rms       |

| PULSE-WIDTH MODULATION (PWM)                    | External CLK = 16 MHz             |       |        |       |              |

| Resolution                                      |                                   |       | 14     |       | Bits         |

| Switching Frequency                             | f <sub>SW</sub>                   | 62.5  |        | 500   | kHz          |

| Programmable Dead Time                          | Minimum                           |       | 0      |       | ns           |

| _                                               | Maximum                           |       | 992.2  |       | ns           |

| Dead Time Resolution <sup>7</sup>               |                                   |       | 7.8125 |       | ns           |

| Delay from External SYNC (Programmable)         | Minimum <sup>8</sup>              |       | 0      |       | μs           |

|                                                 | Maximum at f <sub>SW</sub> =      |       | 16     |       | μs           |

|                                                 | 62.5 kHz <sup>9</sup>             |       |        |       |              |

| Delay Resolution                                |                                   |       | 7.8125 |       | ns           |

| Effective Phase Shift Resolution                |                                   |       |        |       |              |

| $f_{SW}$ = 62.5 kHz                             |                                   |       | 0.176  |       | Degrees      |

| f <sub>SW</sub> = 125 kHz                       |                                   |       | 0.352  |       | Degrees      |

| f <sub>SW</sub> = 250 kHz                       |                                   |       | 0.703  |       | Degrees      |

| f <sub>SW</sub> = 500 kHz                       |                                   |       | 1.406  |       | Degrees      |

| CHANNEL AC PERFORMANCE                          |                                   |       |        |       |              |

| Loop Bandwidth (Cross over Frequency)           |                                   |       | 10     | 50    | kHz          |

| Constant Current to Constant Voltage Transition | f <sub>SW</sub> = 500 kHz         |       | 2      |       | μs           |

| Time                                            |                                   |       |        |       |              |

|                                                 | $f_{SW} = 62.5 \text{ kHz}$       |       | 16     |       | μs           |

| Channel to Channel Isolation                    |                                   |       | 100    |       | dB           |

| Current and Voltage Readout Rate <sup>10</sup>  | Minimum OSR <sup>11</sup>         |       | 31,250 |       | Samples/sec  |

|                                                 | Maximum OSR                       |       | 15.26  |       | Samples/sec  |

| Output Data Resolution                          |                                   |       | 16     |       | Bits         |

analog.com Rev. 0 | 4 of 44

# **SPECIFICATIONS**

Table 1.

| Parameter                                                                     | Test Conditions/Comments | Min         | Тур        | Max         | Unit        |

|-------------------------------------------------------------------------------|--------------------------|-------------|------------|-------------|-------------|

| AUXILIARY ADC                                                                 |                          |             |            |             |             |

| Resolution (Effective)                                                        |                          |             | 12         |             | Bits        |

| Sampling Rate                                                                 | DC bus monitor disabled  |             | 100,000    |             | Samples/sec |

| •                                                                             | DC bus monitor enabled   |             | 50,000     |             | Samples/sec |

| Input Voltage Range                                                           |                          |             |            |             | ·           |

| Reference Voltage                                                             |                          | 0.1         |            | 2.4         | V           |

| Unity-Gain Offset                                                             |                          | -1          |            | +1          | LSB         |

| Unity-Gain Offset Drift                                                       |                          |             |            | 0.02        | LSB/°C      |

| Current Excitation (4-Bit Programmable)                                       | Minimum                  |             | 0          |             | μA          |

|                                                                               | Maximum                  |             | 750        |             | μA          |

| Resolution                                                                    |                          |             | 50         |             | μA          |

| LOGIC INPUTS (SPI_CS, SPI_SCK, SPI_SDIO, SPI_SDO, FAULT_x, GPIOx, AND HW_IRQ) | Hysteresis = 600 mV      |             |            |             | pr t        |

|                                                                               |                          | VDDIO × 0.8 |            |             | V           |

| Input Voltage High (V <sub>IH</sub> )                                         |                          | VDDIO × 0.6 |            | VDDIO × 0.2 |             |

| Input Voltage Low (V <sub>IL</sub> )                                          | V = VDDIO                | 4           |            | VDDIO * 0.2 | V           |

| Input Current High (I <sub>IH</sub> )                                         | V <sub>IN</sub> = VDDIO  | <b>-1</b>   |            | 4           | μA          |

| Input Current Low (I <sub>IL</sub> )                                          | V <sub>IN</sub> = DVSS   |             | 45         | 1           | μA          |

| Input Pull-Down Current (HW_IRQ Only)                                         |                          |             | 15         | 115         | μA          |

| Input Capacitance                                                             |                          |             | 4          |             | pF          |

| LOGIC OPEN-DRAIN OUTPUTS (SPI_SDIO, SPI_SDO, AND HW_IRQ)                      | 1 mA load                |             |            |             |             |

| Output Low Voltage (V <sub>OL</sub> )                                         |                          |             |            | 0.4         | V           |

| Output High Leakage Current (I <sub>OH</sub> )                                |                          |             | ±0.1       | ±1.0        | μA          |

| LOGIC OUTPUTS (GPIO)                                                          | 1 mA load                |             |            |             |             |

| Output Low Voltage (V <sub>OL</sub> )                                         |                          |             |            | 0.4         | V           |

| Output High Leakage Current (I <sub>OH</sub> )                                |                          |             | ±0.1       | ±1.0        | μA          |

| Output High Voltage (V <sub>OH</sub> )                                        | VDDIO = 3.0 V            |             | 3          |             | V           |

|                                                                               | VDDIO = 3.3 V            |             | 3.3        |             | V           |

|                                                                               | VDDIO = 3.6 V            |             | 3.6        |             | V           |

| Slew Rate <sup>12</sup>                                                       | Default settings         |             |            |             |             |

| Falling Edge                                                                  |                          |             | 5.2        |             | ns          |

| Rising Edge                                                                   |                          |             | 4          |             | ns          |

| Internal Oscillator Frequency                                                 |                          |             | 16         |             | MHz         |

| External Oscillator Frequency                                                 |                          |             | 16         |             | MHz         |

| Power Supplies                                                                |                          |             |            |             |             |

| AHVDD                                                                         |                          | 5.3         |            | 30.7        | V           |

| Quiescent Current                                                             | Active and standby       |             | 3          | 4.2         | mA          |

| AHVSS                                                                         |                          | -26         |            | -5.3        | V           |

|                                                                               | Active and standby       |             | 4          | 6           | mA          |

| High Voltage Supply Range (AHVDD to AHVSS)                                    | ,                        | 10.6        |            | 36          | V           |

| AVDD                                                                          |                          | 3           | 3.3        | 3.6         | V           |

|                                                                               | Active                   |             | 40         | 47          | mA          |

|                                                                               | Standby                  |             | 3.6        | 4.5         | mA          |

| AVSS                                                                          |                          |             | 0.0        |             | V           |

| VDDIO                                                                         |                          |             | 3.3        |             | V           |

| 15510                                                                         | Active and standby       |             | 2          | 6           | μA          |

| VDDDRV                                                                        | / louve and standby      |             | 3.3        | U           | V           |

| \ DDDI\\                                                                      | Active                   |             | 3.3<br>4.6 | 4.8         | mA          |

|                                                                               |                          |             |            |             |             |

|                                                                               | Standby                  |             | 26         | 30          | μA          |

analog.com Rev. 0 | 5 of 44

# **SPECIFICATIONS**

Table 1.

| Parameter                               | Test Conditions/Comments          | Min | Тур  | Max | Unit |

|-----------------------------------------|-----------------------------------|-----|------|-----|------|

| DVDD                                    |                                   |     | 3.3  |     | V    |

|                                         | Active                            |     | 21   | 22  | mA   |

|                                         | Standby                           |     | 4.8  | 5.2 | mA   |

| Power Dissipation                       |                                   |     |      |     |      |

| AHVDD                                   | AHVDD = 12 V, active and standby  |     | 50.4 |     | mW   |

| AHVSS                                   | AHVSS = -12 V, active and standby |     | 63.6 |     | mW   |

| VDDIO                                   | Active and standby                |     | 19.8 |     | μW   |

| AVDD                                    | Active                            |     | 155  |     | mW   |

|                                         | Standby                           |     | 14.9 |     | mW   |

| DVDD                                    | Active                            |     | 72.6 |     | mW   |

|                                         | Standby                           |     | 17.2 |     | mW   |

| VDDDRV                                  | Active                            |     | 15.8 |     | mW   |

|                                         | Standby                           |     | 99   |     | μW   |

| PWM DRIVE LOGIC                         |                                   |     |      |     |      |

| DLx and DHx Drive Voltage <sup>13</sup> | PWM_DRV = 0                       |     |      |     |      |

| $V_{OH}$                                | 0 mA load                         | 3   | 3.29 | 3.3 | V    |

|                                         | 15 mA load                        | 2.6 | 2.8  | 2.9 | V    |

| $V_{OL}$                                | 0 mA load                         |     | 17   | 25  | mV   |

|                                         | 15 mA load                        | 0.6 | 0.8  | 1   | V    |

| DLx and DHx Sink Resistance             | PWM_DRV = 0                       | 10  | 23   | 40  | Ω    |

|                                         | PWM_DRV = 15                      | 1.8 | 2.6  | 5   | Ω    |

| DLx and DHx Source Resistance           | PWM_DRV = 0                       | 30  | 41   | 55  | Ω    |

|                                         | PWM_DRV = 15                      | 2.2 | 3.2  | 5.1 | Ω    |

| Internal Pull-Down Resistance           |                                   |     | 1    |     | ΜΩ   |

| Drive Capacitive Load                   |                                   | 10  |      | 100 | pF   |

<sup>&</sup>lt;sup>1</sup> Bandwidth is analog only. The readout data bandwidth is limited by the selected over sampling rate (OSR).

analog.com Rev. 0 | 6 of 44

<sup>&</sup>lt;sup>2</sup> The moving average filter (MAF) is a 3-bit field in the MAF CFG register (one per channel). The default value is 8.

<sup>&</sup>lt;sup>3</sup> The finite impulse response (FIR) filter in the readout filter is not bypassed (default).

<sup>&</sup>lt;sup>4</sup> The readout filter update rate is selected in a 5-bit field in the DSP\_READOUT\_FILT\_CFG register.

<sup>&</sup>lt;sup>5</sup> The bandwidth is analog only. The readout data bandwidth is limited by the selected OSR.

<sup>&</sup>lt;sup>6</sup> Guaranteed by design.

<sup>&</sup>lt;sup>7</sup> For sync mode only.

<sup>&</sup>lt;sup>8</sup> CHANNEL A PHASE = 0x000 in the PMU CHANNEL CFG1 register.

<sup>&</sup>lt;sup>9</sup> The 11-bit CHANNEL A PHASE in the PMU CHANNEL CFG1 register = 0x07FF and is the same for other channels.

<sup>&</sup>lt;sup>10</sup>The readout update rate is set in a 5-bit field in the DSP\_READOUT\_FILT\_CFG register. There is one per channel.

<sup>&</sup>lt;sup>11</sup>Minimum OSR is based on the maximum readout rate of the current and voltage data for all four channels.

<sup>&</sup>lt;sup>12</sup>The output pins (SPI\_SDIO, SPI\_SDO, GPIOx, EXTCLKIO, and HW\_IRQ) have xxx\_PAD\_CFG registers with a 3-bit xxx\_SLEW bitfield. The default is 0x7, which is the fastest slew rate.

<sup>&</sup>lt;sup>13</sup>PWM\_DRV is a 4-bit field in the PWM\_CFG1 channel register.

# **SPECIFICATIONS**

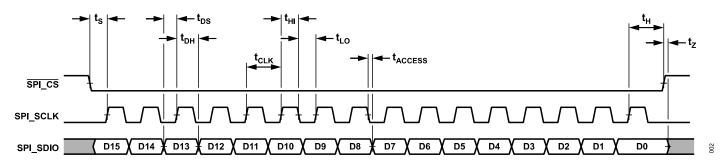

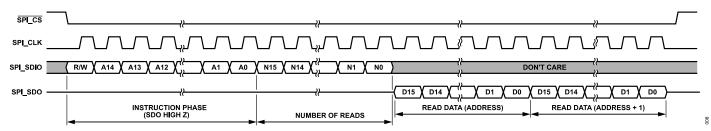

Table 2. SPI Bus Timing

| Parameter                                     | Symbol              | Min | Тур   | Max | Unit |  |

|-----------------------------------------------|---------------------|-----|-------|-----|------|--|

| TIMING REQUIREMENTS                           |                     |     |       |     |      |  |

| Set-Up SPI_CS to SPI_CLK Edge                 | t <sub>S</sub>      |     | 4     |     | ns   |  |

| Minimum SPI_CLK Low Pulse Width               | t <sub>LO</sub>     |     | 31.25 |     | ns   |  |

| Minimum SPI_CLK High Pulse Width              | t <sub>HI</sub>     |     | 31.25 |     | ns   |  |

| Minimum SPI_CLK Period                        | t <sub>CLK</sub>    |     | 62.5  |     | ns   |  |

| Data Input Setup Time Before SPI_CLK Edge     | t <sub>DS</sub>     |     | 4     |     | ns   |  |

| Data Input Hold Time After SPI_CLK Edge       | t <sub>DH</sub>     |     | 4     |     | ns   |  |

| Hold SCLK to SPI_CS Deactivate t <sub>H</sub> |                     |     | 4     |     | ns   |  |

| SWITCHING CHARACTERISTICS                     |                     |     |       |     |      |  |

| Data Output Valid After SPI_CLK Edge          | t <sub>ACCESS</sub> |     | 4     |     | ns   |  |

| SPI_CS to SPI_SDIO/SPI_SDO High-Z             | t <sub>Z</sub>      |     | 4     |     | ns   |  |

Figure 2. 3-Wire SPI Bus Timing Diagram

analog.com Rev. 0 | 7 of 44

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                                                  | Rating                          |  |

|------------------------------------------------------------|---------------------------------|--|

| Analog High Voltage Supply (Continuous),<br>AHVDD - AHVSS  | 50 V                            |  |

| AHVDD - AVSS                                               | 50 V                            |  |

| AVSS - AHVSS                                               | 30 V                            |  |

| Input Pin Voltages (ISP_x, ISN_x, BVP_x, BVN_x, and CVS_x) | -0.3 V + AHVSS to AHVDD + 0.3 V |  |

| Digital Pins (Relative to DVSS)                            | -0.3 V to DVDD + 0.3 V          |  |

| DVSS and AVSS                                              | -0.3 V to +0.3 V                |  |

| DVDD, AVDD, and VDDDRV                                     | -0.3 V to DVDD + 0.3 V          |  |

| SPI_SCK, SPI_CS, SPI_SDIO, and SPI_SDO                     | -0.3 V to DVDD + 0.3 V          |  |

| REFIO                                                      | -0.3 V to DVDD + 0.3 V          |  |

| Temperature                                                |                                 |  |

| Operating Range                                            | 0°C to +85°C                    |  |

| Storage Range                                              | -65°C to +150°C                 |  |

| Junction                                                   | 125°C                           |  |

| Peak Solder Reflow                                         |                                 |  |

| RoHS-Compliant Assemblies (20 sec to 40 sec)               | 260°C                           |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Careful attention to PCB thermal design is required.

$\theta_{JA}$  is the natural convection junction-to-ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction-to-case thermal resistance.

Table 4. Thermal Resistance

| Package Type | $\theta_{JA}$ | $\theta_{JC}$ | Unit |

|--------------|---------------|---------------|------|

| SW-100-2     | 27.8          | 3.9           | °C/W |

## **SOLDERING**

It is important to follow the correct guidelines when laying out the PCB footprint for the ADBT1002 and when soldering the device onto the PCB. For detailed information about these guidelines, see the EE-352 Engineer-to-Engineer Note.

# **ELECTROSTATIC DISCHARGE (ESD) RATINGS**

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Charged device model (CDM) per ANSI/ESDA/JEDEC JS-002.

# **ESD Ratings for ADBT1002**

Table 5. ADBT1002, 100-Lead LQFP EP

| ESD Model | Withstand Threshold | Class |  |

|-----------|---------------------|-------|--|

| НВМ       | 1.5 kV              | 1C    |  |

| CDM       | 750 V               | 1B    |  |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage

without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. 0 | 8 of 44

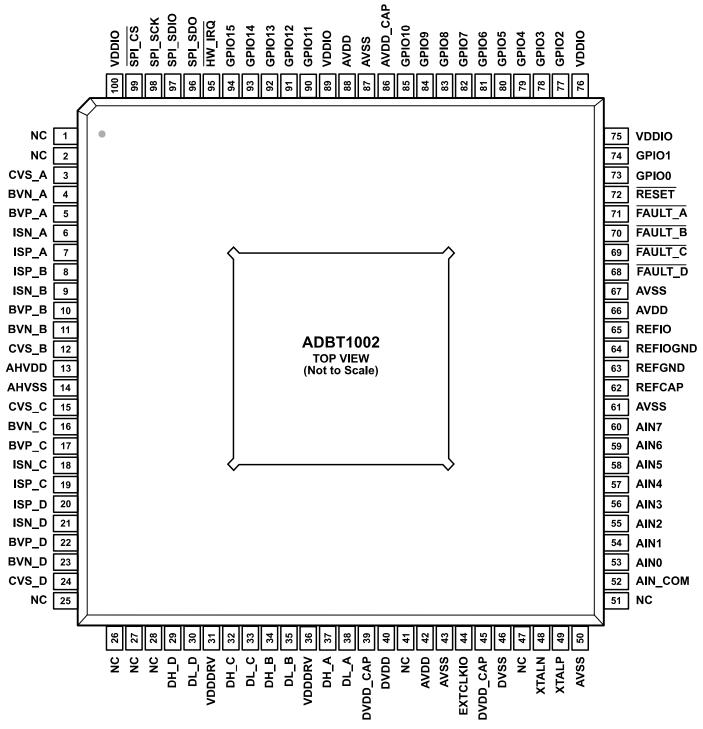

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**NOTES**

1. NC MEANS NO CONNECT.

2. EXPOSED PAD. DVSS FOR DVDD, VDDIO, AND VDDDRV.

Figure 3. Pin Configuration

003

analog.com Rev. 0 | 9 of 44

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions

| Pin No.  | Mnemonic | Description                                                                                  |

|----------|----------|----------------------------------------------------------------------------------------------|

| 1        | NC       | No Connect.                                                                                  |

| 2        | NC       | No Connect.                                                                                  |

| 3        | CVS_A    | Channel A Capacitor Voltage Sense Input.                                                     |

| 4        | BVN_A    | Channel A Voltage Sense Negative Input.                                                      |

| 5        | BVP_A    | Channel A Voltage Sense Positive Input.                                                      |

| 6        | ISN_A    | Channel A Current Sense Negative Input.                                                      |

| 7        | ISP_A    | Channel A Current Sense Positive Input.                                                      |

| 8        | ISP_B    | Channel B Current Sense Positive Input.                                                      |

| 9        | ISN_B    | Channel B Current Sense Negative Input.                                                      |

| 10       | BVP_B    | Channel B Voltage Sense Positive Input.                                                      |

| 11       | BVN_B    | Channel B Voltage Sense Negative Input.                                                      |

| 12       | CVS_B    | Channel B Capacitor Voltage Sense Input.                                                     |

| 13       | AHVDD    | AFE Positive Supply.                                                                         |

| 14       | AHVSS    | AFE Negative Supply. Ensure AVDD is applied before applying AHVSS.                           |

| 15       | CVS_C    | Channel C Capacitor Voltage Sense Input.                                                     |

| 16       | BVN_C    | Channel C Voltage Sense Negative Input.                                                      |

| 17       | BVP_C    | Channel C Voltage Sense Positive Input.                                                      |

| 18       | ISN_C    | Channel C Current Sense Negative Input.                                                      |

| 19       | ISP_C    | Channel C Current Sense Positive Input.                                                      |

| 20       | ISP_D    | Channel D Current Sense Positive Input.  Channel D Current Sense Positive Input.             |

| 21       |          | ·                                                                                            |

|          | ISN_D    | Channel D Current Sense Negative Input.                                                      |

| 22<br>23 | BVP_D    | Channel D Voltage Sense Positive Input.                                                      |

|          | BVN_D    | Channel D Voltage Sense Negative Input.                                                      |

| 24       | CVS_D    | Channel D Capacitor Voltage Sense Input.                                                     |

| 25       | NC       | No Connect.                                                                                  |

| 26       | NC<br>NO | No Connect.                                                                                  |

| 27       | NC       | No Connect.                                                                                  |

| 28       | NC       | No Connect.                                                                                  |

| 29       | DH_D     | PWM Drive High, Channel D.                                                                   |

| 30       | DL_D     | PWM Drive Low, Channel D.                                                                    |

| 31       | VDDDRV   | PWM Driver Supply.                                                                           |

| 32       | DH_C     | PWM Drive High, Channel C                                                                    |

| 33       | DL_C     | PWM Drive Low, Channel C.                                                                    |

| 34       | DH_B     | PWM Drive High, Channel B.                                                                   |

| 35       | DL_B     | PWM Drive Low, Channel B.                                                                    |

| 36       | VDDDRV   | PWM Driver Supply.                                                                           |

| 37       | DH_A     | PWM Drive High, Channel A.                                                                   |

| 38       | DL_A     | PWM Drive Low, Channel A.                                                                    |

| 39       | DVDD_CAP | Digital Supply Source Capacitor. Connect a 10 μF decoupling capacitor from DVDD_CAP to DVSS. |

| 40       | DVDD     | Digital Supply Source, 3.3 V Typical.                                                        |

| 41       | NC       | No Connect.                                                                                  |

| 42       | AVDD     | Analog Supply Source, 3.3 V Typical. Ensure AVDD is applied before applying AHVSS.           |

| 43       | AVSS     | Analog Supply Return.                                                                        |

| 44       | EXTCLKIO | External Oscillator Input and Clock Output.                                                  |

| 45       | DVDD_CAP | Digital Supply Source Capacitor. Connect a 10 µF decoupling capacitor from DVDD_CAP to DVSS. |

| 46       | DVSS     | Digital Supply Return.                                                                       |

| 47       | NC       | No Connect.                                                                                  |

| 48       | XTALP    | External Crystal High-Side Excitation Pin.                                                   |

| 49       | XTALN    | External Crystal Low-Side Excitation Pin.                                                    |

analog.com Rev. 0 | 10 of 44

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 6. Pin Function Descriptions

| Pin No. | Mnemonic | Description                                                                                |

|---------|----------|--------------------------------------------------------------------------------------------|

| 50      | AVSS     | Analog Supply Return.                                                                      |

| 51      | NC       | No Connect.                                                                                |

| 52      | AIN_COM  | Analog Input, ADC Common.                                                                  |

| 53      | AIN0     | Analog Input, ADC Channel 0.                                                               |

| 54      | AIN1     | Analog Input, ADC Channel 1.                                                               |

| 55      | AIN2     | Analog Input, ADC Channel 2.                                                               |

| 56      | AIN3     | Analog Input, ADC Channel 3.                                                               |

| 57      | AIN4     | Analog Input, ADC Channel 4.                                                               |

| 58      | AIN5     | Analog Input, ADC Channel 5.                                                               |

| 59      | AIN6     | Analog Input, ADC Channel 6.                                                               |

| 60      | AIN7     | Analog Input, ADC Channel 7.                                                               |

| 61      | AVSS     | Analog Power Return.                                                                       |

| 62      | REFCAP   | Internal Reference Capacitor.                                                              |

| 63      | REFGND   | Internal Reference Ground.                                                                 |

| 64      | REFIOGND | Ground for Reference Input and Output.                                                     |

| 65      | REFIO    | Reference Input and Output. Connect a 10 μF from REFIO to AVSS.                            |

| 66      | AVDD     | Analog Power Supply. Ensure AVDD is applied before applying AHVSS.                         |

| 67      | AVSS     | Analog Power Return.                                                                       |

| 68      | FAULT_D  | Fault Detect Input, PWM Channel D Shutdown. Active low.                                    |

| 69      | FAULT C  | Fault Detect Input, PWM Channel C Shutdown. Active low.                                    |

| 70      | FAULT B  | Fault Detect Input, PWM Channel B Shutdown. Active low.                                    |

| 71      | FAULT_A  | Fault Detect Input, PWM Channel A Shutdown. Active low.                                    |

| 72      | RESET    | Chip Reset. Active low.                                                                    |

| 73      | GPIO0    | General-Purpose Digital Input and Output 0.                                                |

| 74      | GPIO1    | General-Purpose Digital Input and Output 1.                                                |

| 75      | VDDIO    | Input and Output Supply.                                                                   |

| 76      | VDDIO    | Input and Output Supply.                                                                   |

| 77      | GPIO2    | General-Purpose Digital Input and Output 2.                                                |

| 78      | GPIO3    | General-Purpose Digital Input and Output 3.                                                |

| 79      | GPIO4    | General-Purpose Digital Input and Output 4.                                                |

| 80      | GPIO5    | General-Purpose Digital Input and Output 5.                                                |

| 81      | GPIO6    | General-Purpose Digital Input and Output 6.                                                |

| 82      | GPIO7    | General-Purpose Digital Input and Output 7.                                                |

| 83      | GPIO8    | General-Purpose Digital Input and Output 8.                                                |

| 84      | GPIO9    | General-Purpose Digital Input and Output 9.                                                |

| 85      | GPIO10   | General-Purpose Digital Input and Output 10.                                               |

| 86      | AVDD_CAP | Analog Power Return Capacitor. Connect a 10 µF decoupling capacitor from AVDD_CAP to AVSS. |

| 87      | AVSS     | Analog Power Return.                                                                       |

| 88      | AVDD     | Analog Power Supply. Ensure AVDD is applied before applying AHVSS.                         |

| 89      | VDDIO    | Digital Input and Output Supply.                                                           |

| 90      | GPIO11   | General-Purpose Digital Input and Output 11.                                               |

| 91      | GPIO12   | General-Purpose Digital Input and Output 12.                                               |

| 92      | GPIO13   | General-Purpose Digital Input and Output 13.                                               |

| 93      | GPIO14   | General-Purpose Digital Input and Output 14.                                               |

| 94      | GPIO15   | General-Purpose Digital Input and Output 15.                                               |

| 95      | HW_IRQ   | Host Interrupt Request. Active low.                                                        |

| 96      | SPI_SDO  | Host SPI Master Input, Slave Output (MISO).                                                |

| 97      | SPI_SDIO | Host SPI Master Output, Slave Input (MOSI) or Bidirectional.                               |

| 98      | SPI_SCK  | Host SPI Clock.                                                                            |

analog.com Rev. 0 | 11 of 44

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

# Table 6. Pin Function Descriptions

| Pin No. | Mnemonic | Description                                    |

|---------|----------|------------------------------------------------|

| 99      | SPI_CS   | Host SPI Select. Active low.                   |

| 100     | VDDIO    | Input and Output Supply.                       |

| EPAD    | DVSS     | Exposed Pad. DVSS for DVDD, VDDIO, and VDDDRV. |

analog.com Rev. 0 | 12 of 44

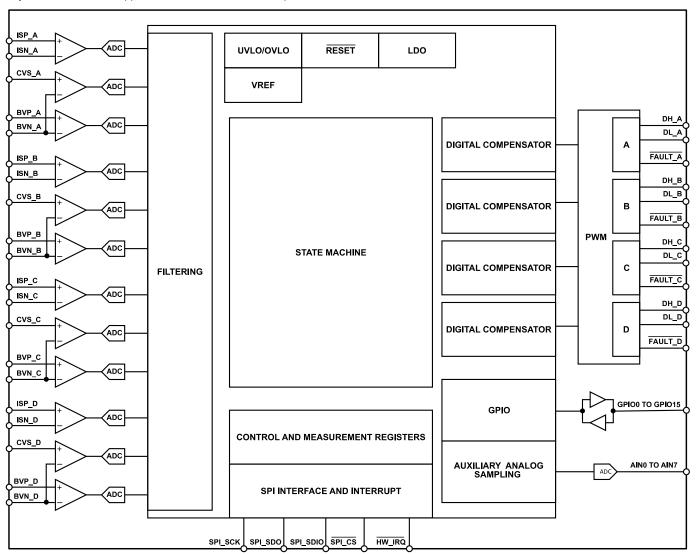

## THEORY OF OPERATION

## **OVERVIEW**

The ADBT1002 is a highly integrated digital controller that provides four channels of charge and discharge control with a focus on battery formation and test applications. Each channel is composed of

a precision analog front end (AFE), measuring both battery current and voltage using a high accuracy ADC, a user programmable digital compensator, and a precision PWM. Additionally, there are 8 auxiliary ADC channels and 16 GPIOx pins.

Figure 4. Functional Block Diagram

analog.com Rev. 0 | 13 of 44

#### THEORY OF OPERATION

#### ANALOG FRONT END

Each channel has a precision current sense differential amplifier with a fixed gain of 40 and a precision voltage sense differential amplifier with a fixed gain of 0.5. A pair of simultaneous sampling ADCs converts the conditioned current and voltage signals to 12-bit digital representations before transferring the signals to the digital controller.

## **DIGITAL CONTROLLER**

A finite state machine (FSM)-based proportional integral derivative (PID) controller provides digital loop control. The controller has user-programmable filter coefficients for control loop compensation. Current and voltage setpoints are register based and are configured by the user over a host SPI. Separate current and voltage control loops support constant current and constant voltage operation modes. The controller output is used to command the duty cycle of an 14-bit digital PWM. Operation of the controller is discussed in the Sequencer Operation Example section.

## **HOST SPI**

Control is provided by an external host through a 3-wire or a 4-wire SPI. Use the SPI\_CS, SPI\_SCK, and SPI\_SDIO pins for the 3-wire SPI and use the SPI\_CS, SPI\_SCK, SPI\_SDIO, and SPI\_SDO pins for the 4-wire SPI. This interface is used to configure the controller through the memory mapped registers. These registers are introduced in Table 11.

## **HOST INTERRUPT REQUEST**

Use the HW\_IRQ signal, \(\overline{HW\_IRQ}\), to provide interrupt requests to the host. Use the SPI port accessible set of registers to select which internal events generate host interrupt requests. Event options include system errors, channel data ready, channel voltage and current over limit detection, channel operation complete, and auxiliary ADC high and low threshold detection.

## **CLOCKING**

The ADBT1002 derives all internal clocking from either an internal oscillator, an external 16 MHz crystal, or an external 16 MHz oscillator. Phase interleaving can be configured to help minimize input ripples as well as output ripples when channels are paralleled for greater current capacity. The ADBT1002 also has a feature that allows multiple ADBT1002 devices to be synchronized together, which enables parallel channel operation in multiples of four.

## **GPIOX PINS**

There are 16 GPIOx pins on the ADBT1002. Typical GPIOx pin usage includes controlling the dc bus and battery isolation switches or getting the digital inputs from the digital sources. The GPIOx pins are user-programmable through the following set of memory mapped registers. The GPIOx pins used for the battery isolation switches can be assigned in the global registers for sequencer control. This assigning facilitates the precharge operation at start-up that prevents reverse current when connecting to the battery.

Additionally, the GPIOx pins can be configured to provide interdevice digital current sharing communications when using multiple ADBT1002 devices in parallel.

The GPIO\_PAD\_CFG register is used to configure the GPIOx pin parameters including slew rate, hysteresis, and drive strength. The default bitfields, GPIO\_SLEW, GPIO\_HYST, and GPIO\_DRV, have default settings of 5 ns, 600 mV, and 10  $\Omega$ , respectively. These default values are typically acceptable for most applications.

The GPIOx pins can be individually configured as inputs or outputs by using the 16-bit GPIO\_IEN\_CFG and GPIO\_OEN\_CFG registers, respectively. Bits[15:0] in each register corresponds to GPIO0 through GPIO15.

When configured as standard GPIOx pins, there are five 16-bit registers that can interact with these pins. In each case, Bit 0 corresponds to GPIO0, and Bit 15 corresponds to GPIO15. The GPIO\_READ register can be read to see the state of each GPIOx pin, and the GPIO\_WRITE register can be written to set the output pins as 1 or 0. The GPIO\_SET, GPIO\_CLEAR, and GPIO\_TOG-GLE registers set, clear, or toggle, respectively, the GPIOx pins that are set as standard GPIOx pin outputs.

In addition to basic user-controlled GPIO operations, the GPIOx pins can be configured for specific operation modes. This configuration is done through the GPIO\_MODE\_CFG0 (for GPIO0 through GPIO7 pins) and the GPIO\_MODE\_CFG1 (for GPIO8 through GPIO15 pins) registers. All GPIOx pins can be configured as either standard GPIO input and output functions or can be controlled by the sequencer. The latter is used to control a battery isolation switch that is used as part of the precharge operation. Additional options for GPIO0 through GPIO7 are unique functions used for interdevice communications when multiple devices are used in parallel.

When a GPIOx pin is controlled by the sequencer in a particular channel, there is also a channel GPIO\_CFG register where the 4 LSBs are used to select which GPIOx pin is controlled by the sequencer of the channel.

## **AUXILIARY ADC**

An 8-channel, 12-bit ADC is available for dedicated (for example, internal temperature) or general-purpose external measurements. Note that four of the channels have optional current sources for use with the external thermistors for temperature measurement. The dc bus voltage can also be sensed on an ADC channel and used in a feedforward control mechanism to reduce the effect of dc bus transients. All auxiliary ADC operations are user configurable.

# SUPPORTS COULOMBIC EFFICIENCY MEASUREMENT

Coulombic efficiency is a ratio of the capacity during discharge to the capacity during charge. The ADBT1002 supports this efficiency through the integration of current over time. The integration results are accessible through a set of registers.

analog.com Rev. 0 | 14 of 44

# THEORY OF OPERATION

# SUPPORTS PRECHARGE OPERATION

When connecting to a cell before a new formation or test cycle, there is a possibility of having a large inrush current from the battery to the discharged output stage. The ADBT1002 allows a

user to precharge the output stage before connecting to the cell, which is described in additional detail in the Precharge Operation section.

analog.com Rev. 0 | 15 of 44

# **SEQUENCER**

#### INSTRUCTION DEFINITION

The ADBT1002 works by executing instructions on each of the four channels. Each instruction manages the control loop. The ADBT1002 can operate with both constant current and constant voltage.

## **SEQUENCING MODES**

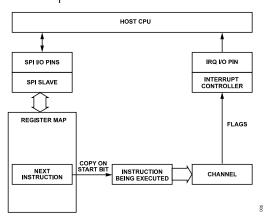

Three possible sequencing modes exist to execute instructions from a user point of view: manual, semiautomatic, and automatic.

## **Manual Mode**

In manual sequencing mode, the host central processing unit (CPU) is responsible for feeding instructions to the ADBT1002. The user writes the full instruction into the next instruction area (that is, the registers prefixed with SEQ\_NEXT\_xxx) of the channel register map. The user writes to the self clearing start bit after, which initiates the execution of this instruction. The instruction provides a

limit or a timeout that the ADBT1002 uses to generate a flag that goes into the ADBT1002 interrupt controller. The user must service the interrupt, write the next instruction, and set the start bit. The ADBT1002 continues to execute the last instruction until the host CPU services the interrupt.

The register map inside the channel provides a fixed layout for the instruction. The repercussion of this layout is that all possible fields are available independently, whether the instruction uses that information or not. The host CPU is responsible for writing to all the required fields for the instruction to execute as expected.

A double buffer mechanism exists to write the instruction. Only when the start bit is written to the channel is a copy of the instruction forwarded to the state machine and executed. This technique allows the next instruction to be written in advance. Access to the registers regarding the instruction executing is available as a debug feature.

Figure 5. Manual Sequencing Mode

analog.com Rev. 0 | 16 of 44

## **SEQUENCER**

## **Semiautomatic Mode**

In semiautomatic mode, the copy of the next instruction executes when the following conditions are met:

- ► The current instruction hits the limits (voltage, current, or time), which are the same reasons why an interrupt can be raised in manual mode.

- A new instruction has been completely written in the register map

To avoid executing the same instruction sequentially, there is a bitfield that indicates when the next instruction is fully programmed as follows:

- ▶ A flag is set by the user through the self clearing NEXT INSTR READY bit in the register map.

- ▶ A flag is cleared whenever the instruction is copied from the register map.

The start bit copies the instruction regardless of what the status of the previous instruction is. Such an operation clears the internal register. A readback for the internal flag is then provided through the register map for debug purposes.

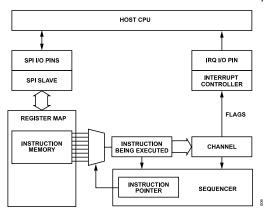

#### **Automatic Mode**

In automatic sequencing mode, all instructions must be programmed into the instruction memory before setting the start bit. The start bit resets the instruction pointer to the start of the channel memory. Each instruction provides a limit or a timeout that terminates the current instruction and advances the instruction pointer to the next instruction. The channel issues a flag to the interrupt controller when all instructions complete execution. The ADBT1002 inhibits any activity on the DH and DL signals once the instruction sequence terminates.

The instructions stored in the channel memory have variable length payloads using 16-bit words. A fixed header is a one word length. The payload depends on the instruction declared in the header. The instruction pointer advances according to the expected payload. A GUI is available to help users code instruction memory.

Figure 6. Automatic Sequencing Mode

analog.com Rev. 0 | 17 of 44

## **SEQUENCER**

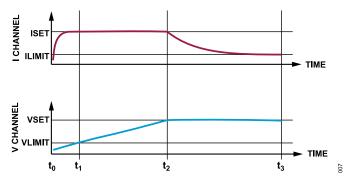

# CHARGE AND DISCHARGE INSTRUCTION MODES

The ADBT1002 provides two PID control loops per channel, the current loop and the voltage loop. Only one PID control loop is in control at any given time. The PID control loop in control is the one with the smallest error between the filtered ADC sample and the target setpoint. Note that, VMEAS is the measurement on the V channel.

There are two independent bits to configure how the control loop behaves:

- ▶ Constant current, where the I channel is in control, and the loop target is set to the current setpoint (ISET).

- ➤ Constant voltage, where the V channel is in control, and the loop target is set to the voltage setpoint (VSET).

There are four possible mode combinations or eight including whether the loop is charging or discharging the battery.

The VSET bits (15 LSBs in Register SEQ\_NEXT\_VSET) can refer to either the absolute value or a delta value based on VMEAS, as determined by the VSET\_DELTA bit (MSB in Register SEQ\_NEXT\_VSET). The main purpose of the delta is to allow the programming of a VSET value at some offset from the last VMEAS value. The start-up (that is, precharge) procedure uses the VSET\_DELTA bit with zero offset to get to the current battery voltage value. The precharge operation is discussed in the Precharge Operation section.

# CHARGE AND DISCHARGE INSTRUCTION LIMITS

There are three 16-bit programmable fields that represent instruction limits. VLIMIT is associated with the constant current mode of operation and can be used to signal the end point of a constant current charge or discharge. ILIMIT is associated with the constant voltage mode of operation and is typically used to signal the end point for a constant voltage charge or discharge operation. TLIMIT can be used to either set the duration of an instruction or to set an error overlimit when an instruction should have completed earlier.

#### **VLIMIT**

The following details the operation of the VLIMIT bits (Register SEQ\_VLIMIT):

- ▶ The VLIMIT threshold flags the instruction end on a charge or discharge instruction with constant current mode.

- ▶ In an instruction with both the constant voltage and constant current modes, VLIMIT avoids early instruction termination by not letting any crossing through ILIMIT (Bits[14:0], Register SEQ\_ILIMIT) to end the instruction before VLIMIT is crossed. In addition, the V channel PID is not allowed to take control until this threshold is reached.

- ▶ If the VLIMIT\_DELTA (MSB) bit is cleared, the VLIMIT bits, Bits[14:0], represent an absolute positive voltage.

- ▶ If the VLIMIT\_DELTA bit is set, the limit is understood as an increment (charge) or a decrement (discharge) from the first VMEAS value read during the execution of an instruction. The main purpose of this bit is to set this limit dynamically without having to read the ADC value before programming this instruction. This bit is related to the VSET\_DELTA bit (Register SEQ VSET).

- ► The VLIMIT is reached when the measured voltage is higher or equal to the VLIMIT threshold with a charge instruction.

- ▶ The VLIMIT is reached when the measured voltage is lower or equal to the VLIMIT threshold with a discharge instruction.

## **ILIMIT**

The following details the operation of the ILIMIT bits (Register SEQ ILIMIT):

- ▶ The ILIMIT threshold flags the instruction end on a charge or discharge instruction with the constant voltage mode active.

- ► The ILIMIT bits, Bits[14:0], always represent the absolute current magnitude.

- ► The ILIMIT is reached when the measured current is lower or equal to the ILIMIT threshold with a charge instruction. A reverse current while charging triggers the limit.

- ➤ The ILIMIT is reached when the measured current is higher or equal to the negative value of the ILIMIT threshold with a battery discharge instruction. A reverse current while discharging triggers the limit.

## **TLIMIT**

The following details the usage of the NEXT\_TLIMIT\_SCALE and NEXT\_TLIMIT\_VAL bitfields (Register SEQ\_NEXT\_TLIMIT):

- ► TLIMIT is the target for a timeout trigger event. The trigger is asserted when the elapsed time is equal or greater than TLIMIT.

- ➤ A timeout trigger event can be used for either an error, if an instruction must terminate through another limit, or for a timed execution of an instruction (no error).

- The SEQ\_NEXT\_TLIMIT, Bits[15:0], are encoded as the following:

- ▶ NEXT\_TLIMIT\_SCALE, Bits[15:14] are the time units, 3 = minutes, 2 = minutes, 1 = milliseconds, and 0 = microseconds.

- ▶ NEXT\_TLIMIT\_VAL, Bits[13:0] are the integer value.

- ➤ The time units set the resolution and the maximum time value. On a scale of minutes, the resolution is minutes, and the maximum time is 11.3 days. On a scale of microseconds, the resolution is microseconds, and the maximum time is approximately 16.5 ms.

analog.com Rev. 0 | 18 of 44

## **SEQUENCER**

## Zero Value Limit Implications

The following limit values have special meaning:

- TLIMIT\_VAL = 0 means that the timeout is disabled, and no flag is generated.

- ▶ ILIMIT = 0, or any low value, means that a constant voltage operation can take a long time to complete.

- VLIMIT = 0 causes a constant current operation to terminate immediately.

## **SLEW RATE**

The ADBT1002 provides a slew rate function of the programmed targets that smooths out the transition between instructions. With this function disabled, a step waveform is seen at the error signal of the control loop. With this function enabled, the step waveform is transformed into a ramp waveform.

If the target value slewing function is enabled, the ADBT1002 ramps the target value from its measured value into the programmed target value as part of the instruction. The register map provides the slew rate for the ISET and VSET bits. The rate is described within two fields: code and time. The code units are in ADC codes, and the time is within the PID and PWM update rate.

The starting point for the ramp is the first value measured with the following limitations:

- ▶ In a charge instruction, ISET cannot be a negative value. If there is a back current, ISET starts from 0, ramping up to the setpoint target.

- ▶ In a discharge instruction, ISET cannot be a positive value. If there is a positive current, ISET starts from 0, ramping down to the setpoint target.

- VSET is always positive.

A charge and discharge instruction that uses constant current ramps ISET. A charge and discharge instruction for constant voltage ramps VSET.

# **PARALLEL OPERATION**

Multiple channels can work in parallel to increase the working current. When multiple channels work in parallel, a channel is declared as the master and transmits the measurement for the I channel (IMEAS) to the other channels. The master channel works as described in the Two Parallel—Two Independent Channels Use Case section and the Four Channels in Parallel Use Case section. The other channels operate in constant current mode and target the raw IMEAS from the master channel. Note that the IMEAS value compensates for gain and offset.

Groups of channels working in parallel can span multiple ADBT1002 chips.

Transmitting of the IMEAS between channels on a single ADBT1002 chip happens inside a PID cycle. Transmitting of the IMEAS between channels of different ADBT1002 chips is

dependent on the interchip SPI communications rate of 8 MHz. Communications between the master and slave devices take 2  $\mu$ s per 16-bit IMEAS transfer.

## **FLAGS**

The flag block generates flags that end up in the interrupt controller block of the ADBT1002. The user then unmasks individual flags (in the INT\_EN\_CH\_x registers), as required, to generate interrupts. Flags are cleared when the channel interrupt status register containing the flag is read.

The INSTR\_DONE flag is set when an instruction hits the last limit, or if it was the REST instruction when the timeout is reached. Keep this flag separate from the SEQ\_DONE flag for debug purposes. When a new instruction loads, the INSTR\_DONE flag resets in automatic mode. The start bit can only reset the INSTR\_DONE flag in manual mode.

If in automatic mode, the SEQ\_DONE flag is set when the last instruction finishes. When in manual mode, this flag is never set, and the start bit resets the SEQ\_DONE flag.

The INSTR\_TIMEOUT flag results when the timeout is reached if the flag was not another limit termination or the HALT instruction.

The VMEAS\_OVER\_LMT and IMEAS\_OVER\_LMT flags result when the input data (ADC raw data for better latency) reaches user specified VMEAS and IMEAS low and high levels, specifically VMEAS\_OVER\_LIMITS\_LOW\_THLD and VMEAS\_OVER\_LIMITS\_HIGH\_THLD, as well as IMEAS\_OVER\_LIMITS\_LOW\_THLD and IMEAS\_OVER\_LIMITS\_HIGH\_THLD, respectively. User can also specify the number of consecutive overlimit samples for detection.

The INSTR\_USER\_IRQ flag is set when the sequencer reads the next instruction with the NEXT\_USER\_IRQ bit set in the channel SEQ\_NEXT\_INST register and finishes the execution of that instruction.

The INSTR\_ERR flag is set during various events that are not part of the instruction. An instruction error writes a debug error code in the channel register map so that it can be read by the host. Codes include malformed instruction and division by zero.

The INSTR\_MODE\_TRANS flag is set upon detection of a mode transition, such as a constant current to constant voltage transition.

Table 7. Sequencer Flags

| Table 1. Sequencer Flags         |                                                                                              |

|----------------------------------|----------------------------------------------------------------------------------------------|

| Flag                             | Description                                                                                  |

| Instruction Finished, INSTR_DONE | Instruction has ended. If in manual sequencing mode, the ADBT1002 expects a new instruction. |

| Sequence Finished, SEQ_DONE      | Instruction halt was run or instruction pointer points outside of the instruction memory.    |

| Timeout, INSTR_TIMEOUT           | If instruction is set to flag timeouts, TLIMIT was met.                                      |

analog.com Rev. 0 | 19 of 44

# **SEQUENCER**

#### Table 7. Sequencer Flags

| Flag                                                                      | Description                                                                                                                                                        |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Measurement Current (I <sub>MEASUREMENT</sub> ) Overlimit, IMEAS_OVER_LMT | IMEAS is outside of the globally programmed thresholds.                                                                                                            |

| Measurement Voltage<br>(VMEASUREMENTS) Overlimit,<br>VMEAS_OVER_LMT       | VMEAS is outside of the globally programmed thresholds.                                                                                                            |

| User Interrupt, INSTR_USER_IRQ                                            | The instruction with the NEXT_USER_IRQ bit was executed.                                                                                                           |

| Instruction Error, INSTR_ERR                                              | Various motives. This flag is a read instruction error code.                                                                                                       |

| Instruction Mode Transition, INSTR_MODE_TRANS                             | The instruction transitioned from one mode to another, such as from constant current to constant voltage mode in a constant current to constant voltage operation. |

# **GLOBAL REGISTER SETTINGS**

The following global register settings list sits outside of the channel register map, and these settings affect all four channels:

- ▶ PWM and loop update rate, which is common for all changes, and the rates can be configured for 500 kHz, 250 kHz, 125 kHz, and 62.5 kHz.

- Configuration of channels for parallel operation.

- Interrupt controller settings.

- Auxiliary ADC configuration and readout.

## **CHANNEL STATIC SETTINGS**

The channel static settings that follow are registers that reside in each of the channel register maps, but these settings are not controllable per instruction.

- ▶ Slew rate settings (the enable bit is in the instruction)

- Measurement overlimit thresholds (hard limits that automatically turn-off the channel)

- ▶ PWM automatic asynchronous mode transition thresholds

- Digital signal processor (DSP) datapath settings follow:

- Readout filter decimation rate

- Numerically controlled oscillator (NCO)

- ▶ Frequency response analysis (FRA) demodulator

#### INSTRUCTION SET ARCHITECTURE

The instructions that can be programmed into the channel sequencer follow. The word size in memory is 16 bits wide. Each instruction has one word as the header and zero or more words as the payloads.

To simplify register diagrams, 16-bit words are drawn into two rows describing the lower 8 bits first and the higher 8 bits second.

Manual sequencing mode provides a limited set of instructions.

Bits marked with the X mean that the contents of those bits are do not care. It is recommended to write 0s in these bits.

Bits[1:0] of the header define the instruction, INST\_TYPE. Instructions include rest, stop, charge, or discharge.

CC and CV are bits in the header that represent a mode of operation for the charge or the discharge of the battery.

DISABLE\_VI\_LIMITS disables the use of VLIMIT or ILIMIT for determining instruction end conditions. This bit also disables flagging any voltage or current measurement overlimits.

PWM\_AUTO\_ASYNC\_ENABLE enables or disables the automatic PWM asynchronous mode transition based on current measurements.

TLIMIT\_MODE indicates whether the time limit is a normal end condition, or if this bit is a timeout error that, if reached, raises a flag.

SLEW\_EN enables a procedure in the charge or the discharge where either ISET or VSET targets are ramped.

GPIO\_VAL sets the value of the channel associated GPIOx. In a standard application, this associated GPIOx controls a switch that connects or disconnects the battery from the voltage regulator. A static register inside the channel register map determines which GPIOx that this GPIO\_VAL bit controls.

LOOP\_START, when set, represents the first instruction that is part of a loop. The hardware stores the address pointer. When set, the first word in the payload must be the number of iterations of the loop. The instruction sets the loop counter with this value if the internal loop counter is 0.

LOOP\_END, when set, represents the last instruction that is part of the loop. The loop counter decrements. If the new loop counter value is not 0, the program jumps to the first instruction of the loop.

The V\_SEL bit represents the two following options for feeding data into the V channel:

- ▶ Battery voltage measurement = 1'b0 means that the measurement is taken across the BVP\_x and BVN\_x pins.

- ► Capacitor voltage measurement = 1'b1 means that the measurement is taken across the CVS x and BVN x pins.

PID\_COEF\_SET represents the different options for the PID coefficients. It is desirable to reserve one set for the start-up procedure when the battery is not connected, and another set for the charge or discharge instructions.

USER\_IRQ makes the instruction raise a user-defined interrupt at instruction completion.

analog.com Rev. 0 | 20 of 44

# **SEQUENCER**

# Table 8. Instruction Header

| Header          | 7                             | 6                     | 5            | 4        | 3        | 2          | 1        | 0        |

|-----------------|-------------------------------|-----------------------|--------------|----------|----------|------------|----------|----------|

| Header LSB Bits | PWM_AUTO_<br>ASYNC_<br>ENABLE | DISABLE_VI_<br>LIMITS | RESERVED     | RESERVED | CC       | CV         | INST_T   | YPE[1:0] |

| Header MSB Bits | TLIMIT_MODE                   | USER_IRQ              | PID_COEF_SET | V_SEL    | LOOP_END | LOOP_START | GPIO_VAL | SLEW_EN  |

analog.com Rev. 0 | 21 of 44

# **SEQUENCER**

#### Halt

Halt is coded with INST TYPE = 2'b00.