# 5-Channel Integrated Power Solution with Quad Buck Regulators and 200 mA LDO Regulator

Data Sheet ADP5050

#### **FEATURES**

Wide input voltage range: 4.5 V to 15 V ±1.5% output accuracy over full temperature range 250 kHz to 1.4 MHz adjustable switching frequency Adjustable/fixed output options via factory fuse or I<sup>2</sup>C interface I<sup>2</sup>C interface with interrupt on fault conditions Power regulation

Channel 1 and Channel 2: programmable 1.2 A/2.5 A/4 A sync buck regulators with low-side FET driver Channel 3 and Channel 4: 1.2 A sync buck regulators

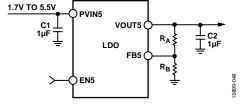

Channel 5: 200 mA low dropout (LDO) regulator

Single 8 A output (Channel 1 and Channel 2 operated in parallel)

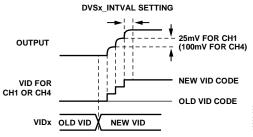

Dynamic voltage scaling (DVS) for Channel 1 and Channel 4

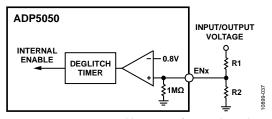

Precision enable with 0.8 V accurate threshold

Active output discharge switch

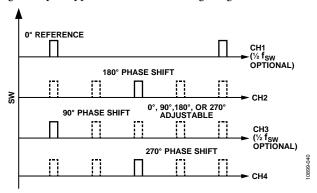

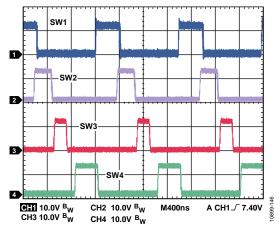

Programmable phase shift in  $90^{\circ}$  steps

Individual channel FPWM/PSM mode selection

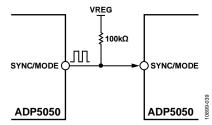

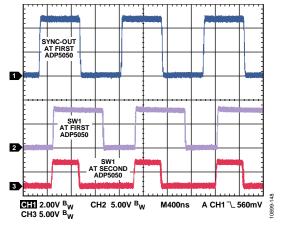

Frequency synchronization input or output

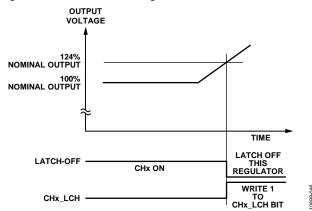

Optional latch-off protection on OVP/OCP failure

Power-good flag on selected channels

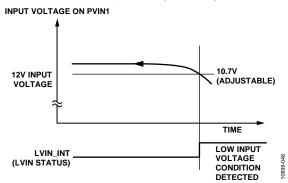

Low input voltage detection

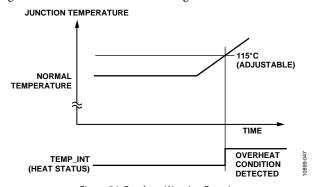

Overheat detection on junction temperature

UVLO, OCP, and TSD protection

48-lead, 7 mm × 7 mm LFCSP package

-40°C to +125°C junction temperature

#### **APPLICATIONS**

Small cell base stations FPGA and processor applications Security and surveillance Medical applications

#### **GENERAL DESCRIPTION**

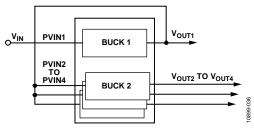

The ADP5050 combines four high performance buck regulators and one 200 mA low dropout (LDO) regulator in a 48-lead LFCSP package that meets demanding performance and board space requirements. The device enables direct connection to high input voltages up to 15 V with no preregulators.

Channel 1 and Channel 2 integrate high-side power MOSFETs and low-side MOSFET drivers. External NFETs can be used in low-side power devices to achieve an efficiency optimized solution and deliver a programmable output current of 1.2 A, 2.5 A, or 4 A. Combining Channel 1 and Channel 2 in a parallel configuration can provide a single output with up to 8 A of current.

Channel 3 and Channel 4 integrate both high-side and low-side MOSFETs to deliver output current of 1.2 A.

# Rev. C Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

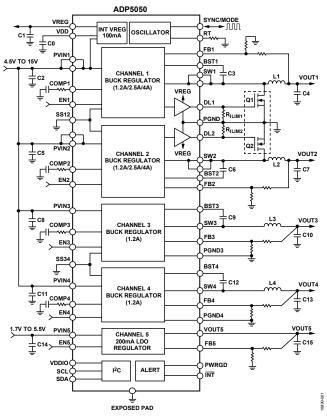

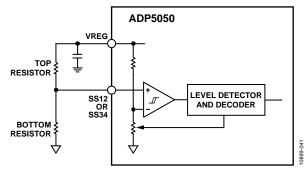

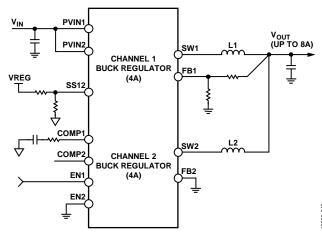

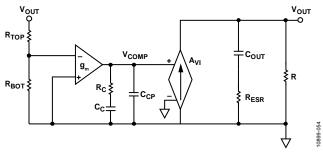

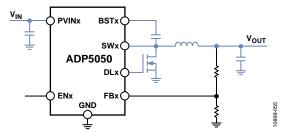

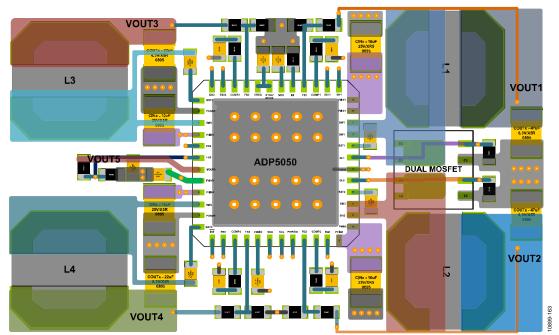

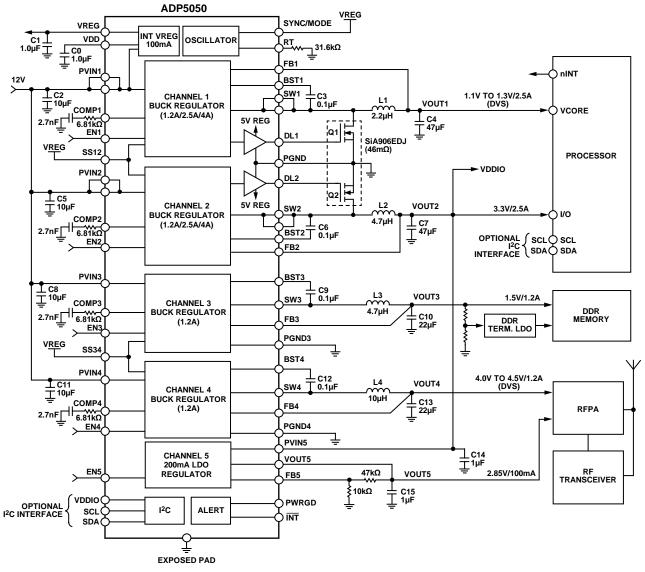

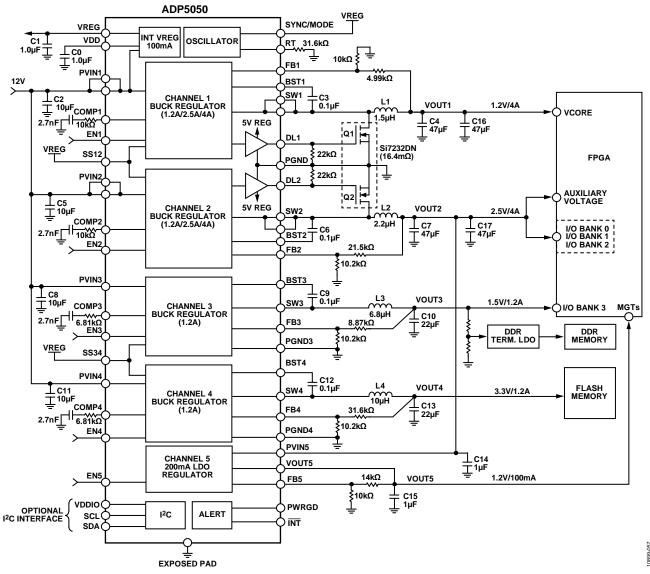

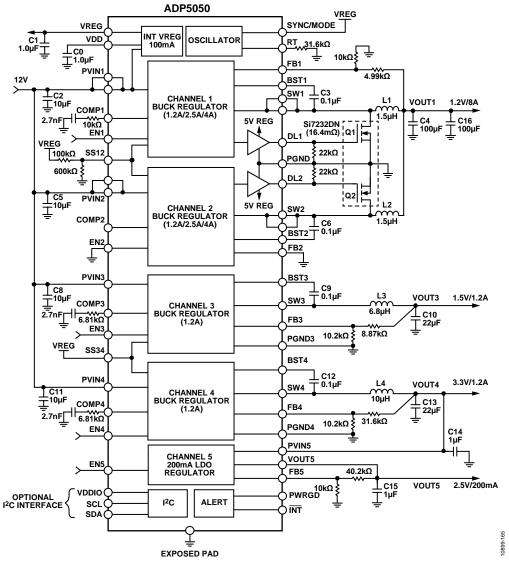

#### TYPICAL APPLICATION CIRCUIT

Figure 1.

**Table 1. Family Models**

| Model   | Channels                | I <sup>2</sup> C | Package       |

|---------|-------------------------|------------------|---------------|

| ADP5050 | Four bucks, one LDO     | Yes              | 48-Lead LFCSP |

| ADP5051 | Four bucks, supervisory | Yes              | 48-Lead LFCSP |

| ADP5052 | Four bucks, one LDO     | No               | 48-Lead LFCSP |

| ADP5053 | Four bucks, supervisory | No               | 48-Lead LFCSP |

| ADP5054 | Four high current bucks | No               | 48-Lead LFCSP |

The switching frequency of the ADP5050 can be programmed or synchronized to an external clock. The ADP5050 contains a precision enable pin on each channel for easy power-up sequencing or adjustable UVLO threshold.

The ADP5050 integrates a general-purpose LDO regulator with low quiescent current and low dropout voltage that provides up to 200 mA of output current.

The optional I<sup>2</sup>C interface provides the user with flexible configuration options, including adjustable and fixed output voltage options, junction temperature overheat warning, low input voltage detection, and dynamic voltage scaling (DVS).

**Data Sheet**

## ADP5050

| TAE | ) I C ( | NE 1 | ቦበ | NTE   | :NTC |

|-----|---------|------|----|-------|------|

| IAC | )LC (   | UF ( | しし | N I C | ENTS |

| Features1                                         | LDO Regulator                                                             |

|---------------------------------------------------|---------------------------------------------------------------------------|

| Applications1                                     | I <sup>2</sup> C Interface                                                |

| General Description1                              | SDA and SCL Pins                                                          |

| Typical Application Circuit                       | I <sup>2</sup> C Addresses                                                |

| Revision History                                  | Self-Clear Register Bits                                                  |

| Detailed Functional Block Diagram4                | I <sup>2</sup> C Interface Timing Diagrams                                |

| Specifications5                                   | Applications Information                                                  |

| Buck Regulator Specifications6                    | ADIsimPower Design Tool                                                   |

| LDO Regulator Specifications8                     | Programming the Adjustable Output Voltage                                 |

| I <sup>2</sup> C Interface Timing Specifications9 | Voltage Conversion Limitations                                            |

| Absolute Maximum Ratings                          | Current-Limit Setting                                                     |

| Thermal Resistance                                | Soft Start Setting30                                                      |

| ESD Caution10                                     | Inductor Selection                                                        |

| Pin Configuration and Function Descriptions11     | Output Capacitor Selection30                                              |

| Typical Performance Characteristics               | Input Capacitor Selection31                                               |

| Theory of Operation                               | Low-Side Power Device Selection                                           |

| Buck Regulator Operational Modes                  | Programming the UVLO Input31                                              |

| Adjustable and Fixed Output Voltages              | Compensation Components Design                                            |

| Dynamic Voltage Scaling (DVS)20                   | Power Dissipation                                                         |

| Internal Regulators (VREG and VDD)20              | Junction Temperature                                                      |

| Separate Supply Applications                      | Design Example                                                            |

| Low-Side Device Selection                         | Setting the Switching Frequency                                           |

| Bootstrap Circuitry                               | Setting the Output Voltage34                                              |

| Active Output Discharge Switch21                  | Setting the Current Limit                                                 |

| Precision Enabling21                              | Selecting the Inductor                                                    |

| Oscillator                                        | Selecting the Output Capacitor                                            |

| Synchronization Input/Output                      | Selecting the Low-Side MOSFET35                                           |

| Soft Start                                        | Designing the Compensation Network35                                      |

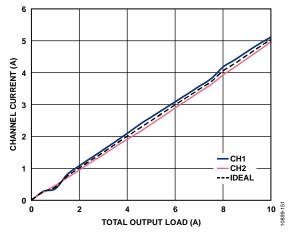

| Parallel Operation                                | Selecting the Soft Start Time35                                           |

| Startup with Precharged Output23                  | Selecting the Input Capacitor                                             |

| Current-Limit Protection24                        | Recommended External Components                                           |

| Frequency Foldback                                | Circuit Board Layout Recommendations                                      |

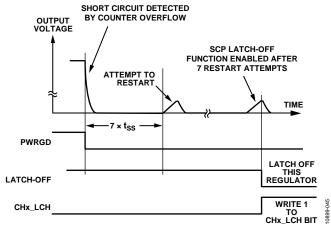

| Hiccup Protection                                 | Typical Application Circuits                                              |

| Latch-Off Protection                              | Register Map41                                                            |

| Undervoltage Lockout (UVLO)25                     | Detailed Register Descriptions                                            |

| Power-Good Function                               | Register 1: PCTRL (Channel Enable Control), Address 0x01 42               |

| Interrupt Function                                | Register 2: VID1 (VID Setting for Channel 1), Address 0x02                |

| Thermal Shutdown                                  |                                                                           |

| Overheat Detection                                | Register 3: VID23 (VID Setting for Channel 2 and Channel 3), Address 0x03 |

| Low Input Voltage Detection 26                    | 1 Mates 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1                             |

| Register 4: VID4 (VID Setting for Channel 4), Address 0x04                                                                |

|---------------------------------------------------------------------------------------------------------------------------|

| Register 5: DVS_CFG (DVS Configuration for Channel 1 and Channel 4), Address 0x0544                                       |

| Register 6: OPT_CFG (FPWM/PSM Mode and Output Discharge Function Configuration), Address 0x0645                           |

| Register 7: LCH_CFG (Short-Circuit Latch-Off and Overvoltage Latch-Off Configuration), Address 0x0746                     |

| Register 8: SW_CFG (Switching Frequency and Phase Shift Configuration), Address 0x0847                                    |

| $\label{eq:Register 9: TH_CFG (Temperature Warning and Low $V_{\rm IN}$ Warning Threshold Configuration), Address 0x0948$ |

| Register 10: HICCUP_CFG (Hiccup Configuration), Address 0x0A49                                                            |

| REVISION HISTORY                                                                                                          |

|                                                                                                                           |

| 10/2016—Rev. B to Rev. CDeleted Factory Programmable Options Section and Table 52 toTable 65; Renumbered Sequentially     |

| Deleted Factory Programmable Options Section and Table 52 to Table 65; Renumbered Sequentially                            |

| Deleted Factory Programmable Options Section and Table 52 to Table 65; Renumbered Sequentially                            |

| Register 11: PWRGD_MASK (Channel Mask Configuration for PWRGD Pin), Address 0x0B50 |

|------------------------------------------------------------------------------------|

| Register 12: LCH_STATUS (Latch-Off Status Readback), Address 0x0C51                |

| Register 13: STATUS_RD (Status Readback), Address 0x0D51                           |

| Register 14: INT_STATUS (Interrupt Status Readback), Address 0x0E52                |

| Register 15: INT_MASK (Interrupt Mask Configuration), Address 0x0F53               |

| Register 17: DEFAULT_SET (Default Reset), Address 0x11.53                          |

| Factory Default Options54                                                          |

| Outline Dimensions55                                                               |

| Ordering Guide55                                                                   |

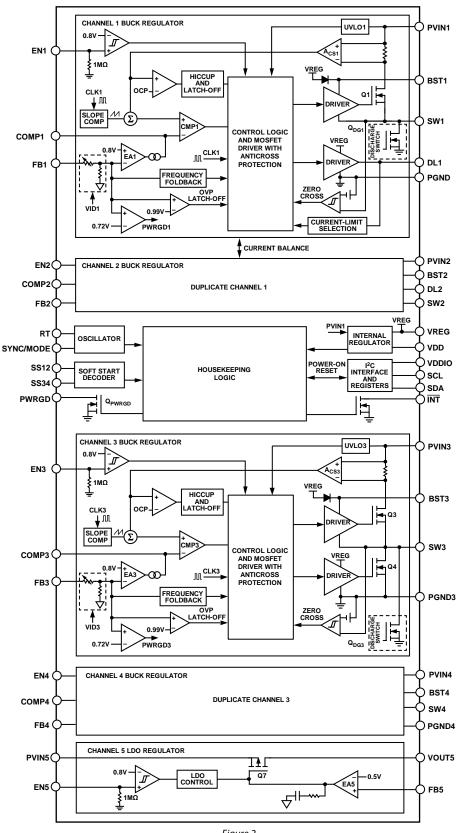

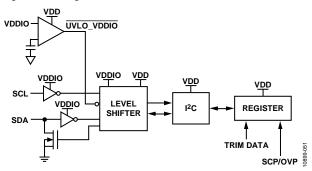

## **DETAILED FUNCTIONAL BLOCK DIAGRAM**

Figure 2.

## **SPECIFICATIONS**

$V_{\rm IN}$  = 12 V,  $V_{\rm VREG}$  = 5.1 V,  $T_{\rm J}$  = -40°C to +125°C for minimum and maximum specifications, and  $T_{\rm A}$  = 25°C for typical specifications, unless otherwise noted.

Table 2.

| Parameter                            | Symbol                        | Min        | Тур               | Max       | Unit | Test Conditions/Comments                         |

|--------------------------------------|-------------------------------|------------|-------------------|-----------|------|--------------------------------------------------|

| INPUT SUPPLY VOLTAGE RANGE           | V <sub>IN</sub>               | 4.5        |                   | 15.0      | V    | PVIN1, PVIN2, PVIN3, PVIN4 pins                  |

| QUIESCENT CURRENT                    |                               |            |                   |           |      | PVIN1, PVIN2, PVIN3, PVIN4 pins                  |

| Operating Quiescent Current          | I <sub>Q(4-BUCKS)</sub>       |            | 4.8               | 6.25      | mA   | No switching, all ENx pins high                  |

|                                      | I <sub>SHDN(4BUCKS+LDO)</sub> |            | 25                | 65        | μΑ   | All ENx pins low                                 |

| UNDERVOLTAGE LOCKOUT                 | UVLO                          |            |                   |           |      | PVIN1, PVIN2, PVIN3, PVIN4 pins                  |

| Rising Threshold                     | V <sub>UVLO-RISING</sub>      |            | 4.2               | 4.36      | V    |                                                  |

| Falling Threshold                    | V <sub>UVLO-FALLING</sub>     | 3.6        | 3.78              |           | V    |                                                  |

| Hysteresis                           | V <sub>HYS</sub>              |            | 0.42              |           | ٧    |                                                  |

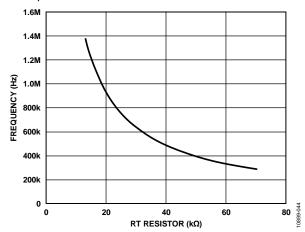

| OSCILLATOR CIRCUIT                   |                               |            |                   |           |      |                                                  |

| Switching Frequency                  | f <sub>sw</sub>               | 700        | 740               | 780       | kHz  | $RT = 25.5 \text{ k}\Omega$                      |

| Switching Frequency Range            |                               | 250        |                   | 1400      | kHz  |                                                  |

| SYNC Input                           |                               |            |                   |           |      |                                                  |

| Input Clock Range                    | f <sub>SYNC</sub>             | 250        |                   | 1400      | kHz  |                                                  |

| Input Clock Pulse Width              |                               |            |                   |           |      |                                                  |

| Minimum On Time                      | tsync_min_on                  | 100        |                   |           | ns   |                                                  |

| Minimum Off Time                     | t <sub>SYNC_MIN_OFF</sub>     | 100        |                   |           | ns   |                                                  |

| Input Clock High Voltage             | V <sub>H(SYNC)</sub>          | 1.3        |                   |           | V    |                                                  |

| Input Clock Low Voltage              | $V_{L(SYNC)}$                 |            |                   | 0.4       | V    |                                                  |

| SYNC Output                          |                               |            |                   |           |      |                                                  |

| Clock Frequency                      | f <sub>CLK</sub>              |            | $f_{\text{SW}}$   |           | kHz  |                                                  |

| Positive Pulse Duty Cycle            | tclk_pulse_duty               |            | 50                |           | %    |                                                  |

| Rise or Fall Time                    | tclk_rise_fall                |            | 10                |           | ns   |                                                  |

| High Level Voltage                   | V <sub>H</sub> (SYNC_OUT)     |            | $V_{\text{VREG}}$ |           | V    |                                                  |

| PRECISION ENABLING                   |                               |            |                   |           |      | EN1, EN2, EN3, EN4, EN5 pins                     |

| High Level Threshold                 | V <sub>TH_H(EN)</sub>         |            | 0.806             | 0.832     | V    |                                                  |

| Low Level Threshold                  | V <sub>TH_L(EN)</sub>         | 0.688      | 0.725             |           | V    |                                                  |

| Pull-Down Resistor                   | R <sub>PULL-DOWN(EN)</sub>    |            | 1.0               |           | ΜΩ   |                                                  |

| POWER GOOD                           |                               |            |                   |           |      |                                                  |

| Internal Power-Good Rising Threshold | V <sub>PWRGD(RISE)</sub>      | 86.3       | 90.5              | 95        | %    |                                                  |

| Internal Power-Good Hysteresis       | V <sub>PWRGD(HYS)</sub>       |            | 3.3               |           | %    |                                                  |

| Internal Power-Good Falling Delay    | t <sub>PWRGD_FALL</sub>       |            | 50                |           | μs   |                                                  |

| Rising Delay for PWRGD Pin           | tpwrgd_pin_rise               |            | 1                 | _         | ms   |                                                  |

| Leakage Current for PWRGD Pin        | Ipwrgd_leakage                |            | 0.1               | 1         | μΑ   |                                                  |

| Output Low Voltage for PWRGD Pin     | V <sub>PWRGD_LOW</sub>        |            | 50                | 100       | mV   | I <sub>PWRGD</sub> = 1 mA                        |

| LOGIC INPUTS (SCL AND SDA PINS)      | .,                            | 0.7 1/0010 |                   |           |      | VDDIO = 3.3 V                                    |

| High Level Threshold                 | V <sub>LOGIC_HIGH</sub>       | 0.7×VDDIO  |                   | 0.3\/DDIO | V    |                                                  |

| Low Level Threshold                  | V <sub>LOGIC_LOW</sub>        |            |                   | 0.3×VDDIO | V    |                                                  |

| LOGIC OUTPUTS                        |                               |            |                   |           |      |                                                  |

| Low Level Output Voltage             | V                             |            |                   | 0.4       | V    | VDDIO 3.3V I 3.55A                               |

| SDA Pin                              | V <sub>SDA_LOW</sub>          |            |                   | 0.4       | V    | $VDDIO = 3.3 \text{ V, } I_{SDA} = 3 \text{ mA}$ |

| INT Pin                              | V <sub>INT_LOW</sub>          |            |                   | 0.4       | V    | I <sub>INT</sub> = 3 mA                          |

| INTERNAL REGULATORS                  | .,                            |            | 2 2 2 5           | 2.4       |      |                                                  |

| VDD Output Voltage                   | V <sub>VDD</sub>              | 3.2        | 3.305             | 3.4       | V    | $I_{VDD} = 10 \text{ mA}$                        |

| VDD Current Limit                    | I <sub>LIM_VDD</sub>          | 20         | 51                | 80        | mA   |                                                  |

| VREG Output Voltage                  | V <sub>VREG</sub>             | 4.9        | 5.1               | 5.3       | V    |                                                  |

| VREG Dropout Voltage                 | V <sub>DROPOUT</sub>          | 50         | 225               | 140       | mV   | $I_{VREG} = 50 \text{ mA}$                       |

| VREG Current Limit                   | I <sub>LIM_</sub> VREG        | 50         | 95                | 140       | mA   |                                                  |

| Parameter                         | Symbol                | Min   | Тур   | Max  | Unit | Test Conditions/Comments                    |

|-----------------------------------|-----------------------|-------|-------|------|------|---------------------------------------------|

| LOW INPUT VOLTAGE DETECTION       |                       |       |       |      |      |                                             |

| Low Input Voltage Threshold       | $V_{\text{LVIN-TH}}$  | 4.07  | 4.236 | 4.39 | V    | LVIN_TH[3:0] = 0000                         |

|                                   |                       | 10.05 | 10.25 | 10.4 | V    | LVIN_TH[3:0] = 1100                         |

| Low Input Voltage Threshold Range |                       | 4.2   |       | 11.2 | V    | I <sup>2</sup> C programmable (4-bit value) |

| THERMAL SHUTDOWN                  |                       |       |       |      |      |                                             |

| Thermal Shutdown Threshold        | T <sub>SHDN</sub>     |       | 150   |      | °C   |                                             |

| Thermal Shutdown Hysteresis       | T <sub>HYS</sub>      |       | 15    |      | °C   |                                             |

| THERMAL OVERHEAT WARNING          |                       |       |       |      |      |                                             |

| Thermal Overheat Threshold        | T <sub>HOT</sub>      |       | 115   |      | °C   | $TEMP_TH[1:0] = 10$                         |

| Overheat Threshold Range          |                       | 105   |       | 125  | °C   | I <sup>2</sup> C programmable (2-bit value) |

| Thermal Overheat Hysteresis       | T <sub>HOT(HYS)</sub> |       | 5     |      | °C   |                                             |

#### **BUCK REGULATOR SPECIFICATIONS**

$V_{IN} = 12 \text{ V}, V_{VREG} = 5.1 \text{ V}, f_{SW} = 600 \text{ kHz}$  for all channels,  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for minimum and maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

Table 3.

| Parameter                                       | Symbol                     | Min   | Тур                      | Max   | Unit | <b>Test Conditions/Comments</b>                       |

|-------------------------------------------------|----------------------------|-------|--------------------------|-------|------|-------------------------------------------------------|

| CHANNEL 1 SYNC BUCK REGULATOR                   |                            |       | -                        |       |      |                                                       |

| FB1 Pin                                         |                            |       |                          |       |      |                                                       |

| Fixed Output Options                            | V <sub>OUT1</sub>          | 0.85  |                          | 1.60  | V    | Fuse trim or I <sup>2</sup> C interface (5-bit value) |

| Adjustable Feedback Voltage                     | $V_{FB1}$                  |       | 0.800                    |       | V    |                                                       |

| Feedback Voltage Accuracy                       | V <sub>FB1</sub> (DEFAULT) | -0.55 |                          | +0.55 | %    | T <sub>J</sub> = 25°C                                 |

|                                                 |                            | -1.25 |                          | +1.0  | %    | 0°C ≤ T <sub>J</sub> ≤ 85°C                           |

|                                                 |                            | -1.5  |                          | +1.5  | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                       |

| Feedback Bias Current                           | I <sub>FB1</sub>           |       |                          | 0.1   | μΑ   | Adjustable voltage                                    |

| SW1 Pin                                         |                            |       |                          |       |      |                                                       |

| High-Side Power FET On Resistance               | R <sub>DSON(1H)</sub>      |       | 100                      |       | mΩ   | Pin-to-pin measurement                                |

| Current-Limit Threshold                         | I <sub>TH(ILIM1)</sub>     | 3.50  | 4.4                      | 5.28  | Α    | R <sub>ILIM1</sub> = floating                         |

|                                                 |                            | 1.91  | 2.63                     | 3.08  | Α    | $R_{ILIM1} = 47 \text{ k}\Omega$                      |

|                                                 |                            | 4.95  | 6.44                     | 7.48  | Α    | $R_{ILIM1} = 22 \text{ k}\Omega$                      |

| Minimum On Time                                 | t <sub>MIN_ON1</sub>       |       | 117                      | 155   | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Minimum Off Time                                | t <sub>MIN_OFF1</sub>      |       | $1/9 \times t_{SW}$      |       | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Low-Side Driver, DL1 Pin                        |                            |       |                          |       |      |                                                       |

| Rising Time                                     | t <sub>RISING1</sub>       |       | 20                       |       | ns   | $C_{ISS} = 1.2 \text{ nF}$                            |

| Falling Time                                    | t <sub>FALLING1</sub>      |       | 3.4                      |       | ns   | $C_{ISS} = 1.2 \text{ nF}$                            |

| Sourcing Resistor                               | tsourcing1                 |       | 10                       |       | Ω    |                                                       |

| Sinking Resistor                                | tsinking1                  |       | 0.95                     |       | Ω    |                                                       |

| Error Amplifier (EA), COMP1 Pin                 |                            |       |                          |       |      |                                                       |

| EA Transconductance                             | g <sub>m1</sub>            | 310   | 470                      | 620   | μS   |                                                       |

| Soft Start                                      |                            |       |                          |       |      |                                                       |

| Soft Start Time                                 | t <sub>SS1</sub>           |       | 2.0                      |       | ms   | SS12 connected to VREG                                |

| Programmable Soft Start Range                   |                            | 2.0   |                          | 8.0   | ms   |                                                       |

| Hiccup Time                                     | <b>t</b> HICCUP1           |       | $7\times t_{\text{SS1}}$ |       | ms   |                                                       |

| C <sub>OUT</sub> Discharge Switch On Resistance | R <sub>DIS1</sub>          |       | 250                      |       | Ω    |                                                       |

| Parameter                                       | Symbol                    | Min   | Тур                 | Max   | Unit | Test Conditions/Comments                              |

|-------------------------------------------------|---------------------------|-------|---------------------|-------|------|-------------------------------------------------------|

| CHANNEL 2 SYNC BUCK REGULATOR                   |                           |       |                     |       |      |                                                       |

| FB2 Pin                                         |                           |       |                     |       |      |                                                       |

| Fixed Output Options                            | V <sub>OUT2</sub>         | 3.3   |                     | 5.0   | V    | Fuse trim or I <sup>2</sup> C interface (3-bit value) |

| Adjustable Feedback Voltage                     | $V_{FB2}$                 |       | 0.800               |       | V    |                                                       |

| Feedback Voltage Accuracy                       | V <sub>FB2(DEFAULT)</sub> | -0.55 |                     | +0.55 | %    | T <sub>J</sub> = 25°C                                 |

|                                                 |                           | -1.25 |                     | +1.0  | %    | 0°C ≤ T <sub>J</sub> ≤ 85°C                           |

|                                                 |                           | -1.5  |                     | +1.5  | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                       |

| Feedback Bias Current<br>SW2 Pin                | I <sub>FB2</sub>          |       |                     | 0.1   | μΑ   | Adjustable voltage                                    |

| High-Side Power FET<br>On Resistance            | R <sub>DSON(2H)</sub>     |       | 110                 |       | mΩ   | Pin-to-pin measurement                                |

| Current-Limit Threshold                         | I <sub>TH(ILIM2)</sub>    | 3.50  | 4.4                 | 5.28  | Α    | $R_{ILIM2} = floating$                                |

|                                                 |                           | 1.91  | 2.63                | 3.08  | Α    | $R_{ILIM2} = 47 \text{ k}\Omega$                      |

|                                                 |                           | 4.95  | 6.44                | 7.48  | Α    | $R_{ILIM2} = 22 \text{ k}\Omega$                      |

| Minimum On Time                                 | t <sub>MIN_ON2</sub>      |       | 117                 | 155   | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Minimum Off Time                                | t <sub>MIN_OFF2</sub>     |       | $1/9 \times t_{SW}$ |       | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Low-Side Driver, DL2 Pin                        |                           |       |                     |       |      |                                                       |

| Rising Time                                     | t <sub>RISING2</sub>      |       | 20                  |       | ns   | C <sub>ISS</sub> = 1.2 nF                             |

| Falling Time                                    | tFALLING2                 |       | 3.4                 |       | ns   | $C_{ISS} = 1.2 \text{ nF}$                            |

| Sourcing Resistor                               | t <sub>SOURCING2</sub>    |       | 10                  |       | Ω    |                                                       |

| Sinking Resistor                                | tsinking2                 |       | 0.95                |       | Ω    |                                                       |

| Error Amplifier (EA), COMP2 Pin                 | 33111111102               |       |                     |       |      |                                                       |

| EA Transconductance                             | g <sub>m2</sub>           | 310   | 470                 | 620   | μS   |                                                       |

| Soft Start                                      | 92                        |       |                     | 020   | P.0  |                                                       |

| Soft Start Time                                 | t <sub>SS2</sub>          |       | 2.0                 |       | ms   | SS12 connected to VREG                                |

| Programmable Soft Start Range                   | <b>C</b> 332              | 2.0   | 2.0                 | 8.0   | ms   | 5512 connected to VII20                               |

| Hiccup Time                                     | t <sub>HICCUP2</sub>      | 2.0   | $7 \times t_{SS2}$  | 0.0   | ms   |                                                       |

| C <sub>OUT</sub> Discharge Switch On Resistance | R <sub>DIS2</sub>         |       | 250                 |       | Ω    |                                                       |

| CHANNEL 3 SYNC BUCK REGULATOR                   | 110132                    |       |                     |       |      |                                                       |

| FB3 Pin                                         |                           |       |                     |       |      |                                                       |

| Fixed Output Options                            | V <sub>ОUТЗ</sub>         | 1.20  |                     | 1.80  | V    | Fuse trim or I <sup>2</sup> C interface (3-bit value) |

| Adjustable Feedback Voltage                     | V <sub>FB3</sub>          |       | 0.800               |       | V    | ,                                                     |

| Feedback Voltage Accuracy                       | V <sub>FB3(DEFAULT)</sub> | -0.55 |                     | +0.55 | %    | T <sub>1</sub> = 25°C                                 |

|                                                 | 105(021/1021)             | -1.25 |                     | +1.0  | %    | 0°C ≤ T <sub>J</sub> ≤ 85°C                           |

|                                                 |                           | -1.5  |                     | +1.5  | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                       |

| Feedback Bias Current<br>SW3 Pin                | I <sub>FB3</sub>          |       |                     | 0.1   | μΑ   | Adjustable voltage                                    |

| High-Side Power FET On Resistance               | R <sub>DSON(3H)</sub>     |       | 225                 |       | mΩ   | Pin-to-pin measurement                                |

| Low-Side Power FET<br>On Resistance             | R <sub>DSON(3L)</sub>     |       | 150                 |       | mΩ   | Pin-to-pin measurement                                |

| Current-Limit Threshold                         | I <sub>TH(ILIM3)</sub>    | 1.7   | 2.2                 | 2.55  | Α    |                                                       |

| Minimum On Time                                 | t <sub>MIN_ON3</sub>      |       | 90                  | 120   | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Minimum Off Time                                | t <sub>MIN_OFF3</sub>     |       | $1/9 \times t_{SW}$ |       | ns   | f <sub>sw</sub> = 250 kHz to 1.4 MHz                  |

| Error Amplifier (EA), COMP3 Pin                 |                           |       |                     |       |      |                                                       |

| EA Transconductance                             | G <sub>m3</sub>           | 310   | 470                 | 620   | μS   |                                                       |

| Soft Start                                      |                           |       |                     |       | Ι΄.  |                                                       |

| Soft Start Time                                 | t <sub>SS3</sub>          |       | 2.0                 |       | ms   | SS34 connected to VREG                                |

| Programmable Soft Start Range                   |                           | 2.0   |                     | 8.0   | ms   |                                                       |

| Hiccup Time                                     | t <sub>HICCUP3</sub>      |       | $7 \times t_{SS3}$  |       | ms   |                                                       |

| <b>-</b>                                        | 1                         | ĺ     | 250                 |       | 1    | İ                                                     |

| Parameter                                       | Symbol                    | Min   | Тур                      | Max   | Unit | Test Conditions/Comments                              |

|-------------------------------------------------|---------------------------|-------|--------------------------|-------|------|-------------------------------------------------------|

| CHANNEL 4 SYNC BUCK REGULATOR                   |                           |       |                          |       |      |                                                       |

| FB4 Pin                                         |                           |       |                          |       |      |                                                       |

| Fixed Output Options                            | V <sub>OUT4</sub>         | 2.5   |                          | 5.5   | V    | Fuse trim or I <sup>2</sup> C interface (5-bit value) |

| Adjustable Feedback Voltage                     | $V_{FB4}$                 |       | 0.800                    |       | V    |                                                       |

| Feedback Voltage Accuracy                       | V <sub>FB4(DEFAULT)</sub> | -0.55 |                          | +0.55 | %    | T <sub>J</sub> = 25°C                                 |

|                                                 |                           | -1.25 |                          | +1.0  | %    | 0°C ≤ T <sub>J</sub> ≤ 85°C                           |

|                                                 |                           | -1.5  |                          | +1.5  | %    | -40°C ≤ T <sub>J</sub> ≤ +125°C                       |

| Feedback Bias Current                           | I <sub>FB4</sub>          |       |                          | 0.1   | μΑ   |                                                       |

| SW4 Pin                                         |                           |       |                          |       |      |                                                       |

| High-Side Power FET On Resistance               | R <sub>DSON(4H)</sub>     |       | 225                      |       | mΩ   | Pin-to-pin measurement                                |

| Low-Side Power FET On Resistance                | R <sub>DSON(4L)</sub>     |       | 150                      |       | mΩ   | Pin-to-pin measurement                                |

| Current-Limit Threshold                         | I <sub>TH(ILIM4)</sub>    | 1.7   | 2.2                      | 2.55  | Α    |                                                       |

| Minimum On Time                                 | t <sub>MIN_ON4</sub>      |       | 90                       | 120   | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Minimum Off Time                                | t <sub>MIN_OFF4</sub>     |       | $1/9 \times t_{SW}$      | ı     | ns   | $f_{SW} = 250 \text{ kHz to } 1.4 \text{ MHz}$        |

| Error Amplifier (EA), COMP4 Pin                 |                           |       |                          |       |      |                                                       |

| EA Transconductance                             | g <sub>m4</sub>           | 310   | 470                      | 620   | μS   |                                                       |

| Soft Start                                      |                           |       |                          |       |      |                                                       |

| Soft Start Time                                 | t <sub>SS4</sub>          |       | 2.0                      |       | ms   | SS34 connected to VREG                                |

| Programmable Soft Start Range                   |                           | 2.0   |                          | 8.0   | ms   |                                                       |

| Hiccup Time                                     | t <sub>HICCUP4</sub>      |       | $7\times t_{\text{SS4}}$ |       | ms   |                                                       |

| C <sub>OUT</sub> Discharge Switch On Resistance | R <sub>DIS4</sub>         |       | 250                      |       | Ω    |                                                       |

#### LDO REGULATOR SPECIFICATIONS

$V_{IN5}$  = (VOUT5 + 0.5 V) or 1.7 V (whichever is greater) to 5.5 V;  $C_{IN}$  =  $C_{OUT}$  = 1  $\mu$ F;  $T_J$  =  $-40^{\circ}$ C to +125 $^{\circ}$ C for minimum and maximum specifications, and  $T_A$  = 25 $^{\circ}$ C for typical specifications, unless otherwise noted.

Table 4.

| Parameter                      | Min  | Тур   | Max  | Unit   | Test Conditions/Comments                                                     |

|--------------------------------|------|-------|------|--------|------------------------------------------------------------------------------|

| INPUT SUPPLY VOLTAGE RANGE     | 1.7  |       | 5.5  | V      | PVIN5 pin                                                                    |

| OPERATIONAL SUPPLY CURRENT     |      |       |      |        |                                                                              |

| Bias Current for LDO Regulator |      | 30    | 130  | μΑ     | Ι <sub>ΟυΤ5</sub> = 200 μΑ                                                   |

|                                |      | 60    | 170  | μΑ     | $I_{OUT5} = 10 \text{ mA}$                                                   |

|                                |      | 145   | 320  | μΑ     | I <sub>OUT5</sub> = 200 mA                                                   |

| VOLTAGE FEEDBACK (FB5 PIN)     |      |       |      |        |                                                                              |

| Adjustable Feedback Voltage    |      | 0.500 |      | V      |                                                                              |

| Feedback Voltage Accuracy      | -1.0 |       | +1.0 | %      | T <sub>J</sub> = 25°C                                                        |

|                                | -1.6 |       | +1.6 | %      | 0°C ≤ T <sub>J</sub> ≤ 85°C                                                  |

|                                | -2.0 |       | +2.0 | %      | -40°C ≤ T <sub>J</sub> ≤ +125°C                                              |

| DROPOUT VOLTAGE                |      |       |      |        | I <sub>OUT5</sub> = 200 mA                                                   |

|                                |      | 80    |      | mV     | VOUT5 = 3.3 V                                                                |

|                                |      | 100   |      | mV     | VOUT5 = 2.5 V                                                                |

|                                |      | 180   |      | mV     | VOUT5 = 1.5 V                                                                |

| CURRENT-LIMIT THRESHOLD        | 250  | 510   |      | mA     | Specified from the output voltage drop to 90% of the specified typical value |

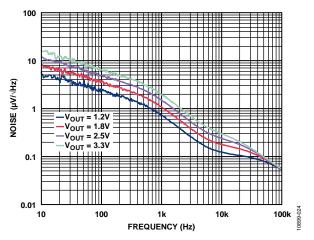

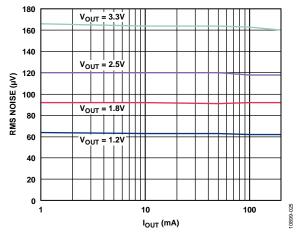

| OUTPUT NOISE                   |      | 92    |      | μV rms | 10 Hz to 100 kHz, V <sub>PVIN5</sub> = 5 V, VOUT5 = 1.8 V                    |

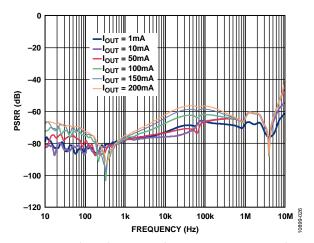

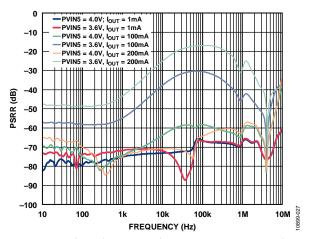

| POWER SUPPLY REJECTION RATIO   |      |       |      |        | $V_{PVIN5} = 5 \text{ V, VOUT5} = 1.8 \text{ V, } I_{OUT5} = 1 \text{ mA}$   |

|                                |      | 77    |      | dB     | 10 kHz                                                                       |

|                                |      | 66    |      | dB     | 100 kHz                                                                      |

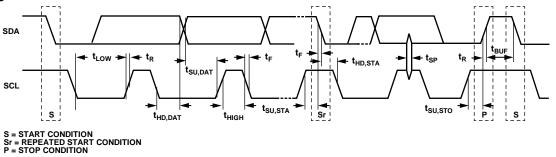

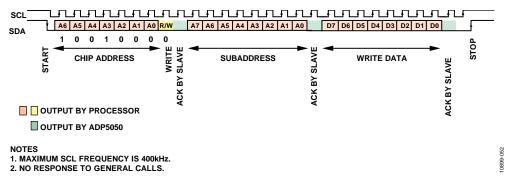

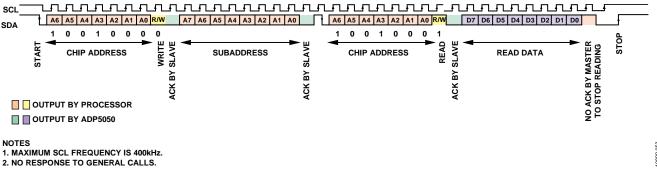

#### I<sup>2</sup>C INTERFACE TIMING SPECIFICATIONS

$T_{\text{A}}$  = 25°C,  $V_{\text{VDD}}$  = 3.3 V,  $V_{\text{VDDIO}}$  = 3.3 V, unless otherwise noted.

Table 5.

| Parameter                   | Min                 | Тур | Max | Unit | Description                                                  |

|-----------------------------|---------------------|-----|-----|------|--------------------------------------------------------------|

| f <sub>SCL</sub>            |                     |     | 400 | kHz  | SCL clock frequency                                          |

| t <sub>HIGH</sub>           | 0.6                 |     |     | μs   | SCL high time                                                |

| t <sub>LOW</sub>            | 1.3                 |     |     | μs   | SCL low time                                                 |

| t <sub>SU,DAT</sub>         | 100                 |     |     | ns   | Data setup time                                              |

| t <sub>HD,DAT</sub>         | 0                   |     | 0.9 | μs   | Data hold time <sup>1</sup>                                  |

| t <sub>SU,STA</sub>         | 0.6                 |     |     | μs   | Setup time for a repeated start condition                    |

| t <sub>HD,STA</sub>         | 0.6                 |     |     | μs   | Hold time for a start or repeated start condition            |

| t <sub>BUF</sub>            | 1.3                 |     |     | μs   | Bus free time between a stop condition and a start condition |

| t <sub>su,sto</sub>         | 0.6                 |     |     | μs   | Setup time for a stop condition                              |

| $t_R$                       | $20 + 0.1C_B^2$     |     | 300 | ns   | Rise time of SCL and SDA                                     |

| $t_{F}$                     | $20 + 0.1C_{B}^{2}$ |     | 300 | ns   | Fall time of SCL and SDA                                     |

| $t_{SP}$                    | 0                   |     | 50  | ns   | Pulse width of suppressed spike                              |

| C <sub>B</sub> <sup>2</sup> |                     |     | 400 | pF   | Capacitive load for each bus line                            |

<sup>&</sup>lt;sup>1</sup> A master device must provide a hold time of at least 300 ns for the SDA signal (referred to the V<sub>H</sub> minimum of the SCL signal) to bridge the undefined region of the SCL falling edge.

#### **Timing Diagram**

Figure 3. I<sup>2</sup>C Interface Timing Diagram

$<sup>^2\,</sup>C_B$  is the total capacitance of one bus line in picofarads (pF).

## **ABSOLUTE MAXIMUM RATINGS**

Table 6.

| Table 6.                               | T                       |

|----------------------------------------|-------------------------|

| Parameter                              | Rating                  |

| PVIN1 to PGND                          | −0.3 V to +18 V         |

| PVIN2 to PGND                          | −0.3 V to +18 V         |

| PVIN3 to PGND3                         | −0.3 V to +18 V         |

| PVIN4 to PGND4                         | −0.3 V to +18 V         |

| PVIN5 to GND                           | −0.3 V to +6.5 V        |

| SW1 to PGND                            | −0.3 V to +18 V         |

| SW2 to PGND                            | −0.3 V to +18 V         |

| SW3 to PGND3                           | −0.3 V to +18 V         |

| SW4 to PGND4                           | −0.3 V to +18 V         |

| PGND to GND                            | −0.3 V to +0.3 V        |

| PGND3 to GND                           | −0.3 V to +0.3 V        |

| PGND4 to GND                           | −0.3 V to +0.3 V        |

| BST1 to SW1                            | −0.3 V to +6.5 V        |

| BST2 to SW2                            | −0.3 V to +6.5 V        |

| BST3 to SW3                            | −0.3 V to +6.5 V        |

| BST4 to SW4                            | −0.3 V to +6.5 V        |

| DL1 to PGND                            | −0.3 V to +6.5 V        |

| DL2 to PGND                            | −0.3 V to +6.5 V        |

| SS12, SS34 to GND                      | −0.3 V to +6.5 V        |

| EN1, EN2, EN3, EN4, EN5 to GND         | −0.3 V to +6.5 V        |

| VREG to GND                            | −0.3 V to +6.5 V        |

| SYNC/MODE to GND                       | −0.3 V to +6.5 V        |

| VOUT5, FB5 to GND                      | −0.3 V to +6.5 V        |

| RT to GND                              | −0.3 V to +3.6 V        |

| ĪNT, PWRGD to GND                      | −0.3 V to +6.5 V        |

| FB1, FB2, FB3, FB4 to GND <sup>1</sup> | −0.3 V to +3.6 V        |

| FB2 to GND <sup>2</sup>                | −0.3 V to +6.5 V        |

| FB4 to GND <sup>2</sup>                | −0.3 V to +7 V          |

| COMP1, COMP2, COMP3, COMP4             | −0.3 V to +3.6 V        |

| to GND                                 |                         |

| VDD, VDDIO to GND                      | −0.3 V to +3.6 V        |

| SCL, SDA                               | -0.3 V to VDDIO + 0.3 V |

| Storage Temperate Range                | −65°C to +150°C         |

| Operational Junction Temperature       | -40°C to +125°C         |

| Range                                  |                         |

<sup>&</sup>lt;sup>1</sup> This rating applies to the adjustable output voltage models of the ADP5050.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 7. Thermal Resistance

| Package Type  | <b>Ө</b> ЈА | θις  | Unit |

|---------------|-------------|------|------|

| 48-Lead LFCSP | 27.87       | 2.99 | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> This rating applies to the fixed output voltage models of the ADP5050.

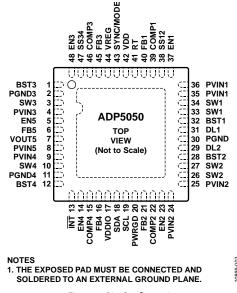

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 8. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                    |

|---------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | BST3     | High-Side FET Driver Power Supply for Channel 3.                                                                                                                                                                                                                                                                                                               |

| 2       | PGND3    | Power Ground for Channel 3.                                                                                                                                                                                                                                                                                                                                    |

| 3       | SW3      | Switching Node Output for Channel 3.                                                                                                                                                                                                                                                                                                                           |

| 4       | PVIN3    | Power Input for Channel 3. Connect a bypass capacitor between this pin and ground.                                                                                                                                                                                                                                                                             |

| 5       | EN5      | Enable Input for Channel 5. An external resistor divider can be used to set the turn-on threshold.                                                                                                                                                                                                                                                             |

| 6       | FB5      | Feedback Sensing Input for Channel 5.                                                                                                                                                                                                                                                                                                                          |

| 7       | VOUT5    | Power Output for Channel 5.                                                                                                                                                                                                                                                                                                                                    |

| 8       | PVIN5    | Power Input for Channel 5. Connect a bypass capacitor between this pin and ground.                                                                                                                                                                                                                                                                             |

| 9       | PVIN4    | Power Input for Channel 4. Connect a bypass capacitor between this pin and ground.                                                                                                                                                                                                                                                                             |

| 10      | SW4      | Switching Node Output for Channel 4.                                                                                                                                                                                                                                                                                                                           |

| 11      | PGND4    | Power Ground for Channel 4.                                                                                                                                                                                                                                                                                                                                    |

| 12      | BST4     | High-Side FET Driver Power Supply for Channel 4.                                                                                                                                                                                                                                                                                                               |

| 13      | ĪNT      | Interrupt Output on Fault Condition. Open-drain output port.                                                                                                                                                                                                                                                                                                   |

| 14      | EN4      | Enable Input for Channel 4. An external resistor divider can be used to set the turn-on threshold.                                                                                                                                                                                                                                                             |

| 15      | COMP4    | Error Amplifier Output for Channel 4. Connect an RC network from this pin to ground.                                                                                                                                                                                                                                                                           |

| 16      | FB4      | Feedback Sensing Input for Channel 4.                                                                                                                                                                                                                                                                                                                          |

| 17      | VDDIO    | Power Supply for the I <sup>2</sup> C Interface.                                                                                                                                                                                                                                                                                                               |

| 18      | SDA      | Data Input/Output for the I <sup>2</sup> C Interface. Open-drain I/O port.                                                                                                                                                                                                                                                                                     |

| 19      | SCL      | Clock Input for the I <sup>2</sup> C Interface.                                                                                                                                                                                                                                                                                                                |

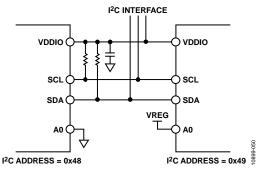

| 20      | PWRGD    | Power-Good Signal Output. This open-drain output is the power-good signal for the selected channels.  This pin can be programmed by the factory to set the I <sup>2</sup> C address of the part; the I <sup>2</sup> C address setting function replaces the power-good function on this pin. For more information, see the I <sup>2</sup> C Addresses section. |

| 21      | FB2      | Feedback Sensing Input for Channel 2.                                                                                                                                                                                                                                                                                                                          |

| 22      | COMP2    | Error Amplifier Output for Channel 2. Connect an RC network from this pin to ground.                                                                                                                                                                                                                                                                           |

| 23      | EN2      | Enable Input for Channel 2. An external resistor divider can be used to set the turn-on threshold.                                                                                                                                                                                                                                                             |

| 24, 25  | PVIN2    | Power Input for Channel 2. Connect a bypass capacitor between this pin and ground.                                                                                                                                                                                                                                                                             |

| 26, 27  | SW2      | Switching Node Output for Channel 2.                                                                                                                                                                                                                                                                                                                           |

| 28      | BST2     | High-Side FET Driver Power Supply for Channel 2.                                                                                                                                                                                                                                                                                                               |

| 29      | DL2      | Low-Side FET Gate Driver for Channel 2. Connect a resistor from this pin to ground to program the current-limit threshold for Channel 2.                                                                                                                                                                                                                       |

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30      | PGND      | Power Ground for Channel 1 and Channel 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 31      | DL1       | Low-Side FET Gate Driver for Channel 1. Connect a resistor from this pin to ground to program the current-limit threshold for Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 32      | BST1      | High-Side FET Driver Power Supply for Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 33, 34  | SW1       | Switching Node Output for Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 35, 36  | PVIN1     | Power Input for the Internal 5.1 V VREG Linear Regulator and the Channel 1 Buck Regulator. Connect a bypass capacitor between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 37      | EN1       | Enable Input for Channel 1. An external resistor divider can be used to set the turn-on threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 38      | SS12      | Connect a resistor divider from this pin to VREG and ground to configure the soft start time for Channel 1 and Channel 2 (see the Soft Start section). This pin is also used to configure parallel operation of Channel 1 and Channel 2 (see the Parallel Operation section).                                                                                                                                                                                                                                                                                                                                                                         |

| 39      | COMP1     | Error Amplifier Output for Channel 1. Connect an RC network from this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 40      | FB1       | Feedback Sensing Input for Channel 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 41      | RT        | Connect a resistor from RT to ground to program the switching frequency from 250 kHz to 1.4 MHz. For more information, see the Oscillator section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 42      | VDD       | Output of the Internal 3.3 V Linear Regulator. Connect a 1 µF ceramic capacitor between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 43      | SYNC/MODE | Synchronization Input/Output (SYNC). To synchronize the switching frequency of the part to an external clock, connect this pin to an external clock with a frequency from 250 kHz to 1.4 MHz. This pin can also be configured as a synchronization output using the I <sup>2</sup> C interface or by factory fuse.  Forced PWM or Automatic PWM/PSM Selection Pin (MODE). When this pin is logic high, each channel operates in forced PWM or automatic PWM/PSM mode, as specified by the PSMx_ON bits in Register 6. When this pin is logic low, all channels operate in automatic PWM/PSM mode, and the PSMx_ON settings in Register 6 are ignored. |

| 44      | VREG      | Output of the Internal 5.1 V Linear Regulator. Connect a 1 µF ceramic capacitor between this pin and ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 45      | FB3       | Feedback Sensing Input for Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 46      | COMP3     | Error Amplifier Output for Channel 3. Connect an RC network from this pin to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 47      | SS34      | Connect a resistor divider from this pin to VREG and ground to configure the soft start time for Channel 3 and Channel 4 (see the Soft Start section).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 48      | EN3       | Enable Input for Channel 3. An external resistor divider can be used to set the turn-on threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | EPAD      | Exposed Pad (Analog Ground). The exposed pad must be connected and soldered to an external ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

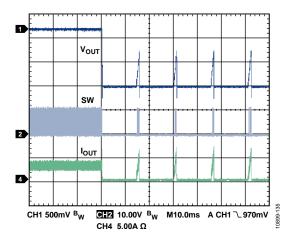

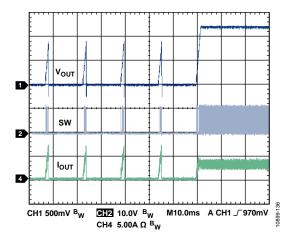

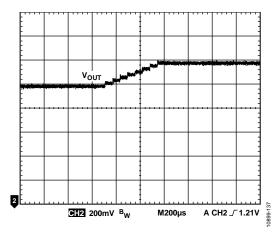

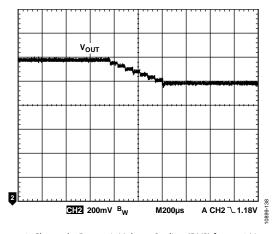

## TYPICAL PERFORMANCE CHARACTERISTICS

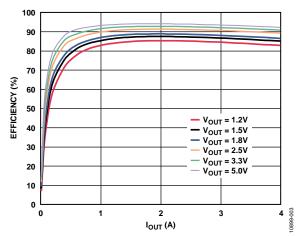

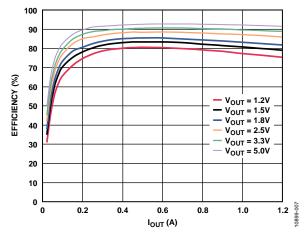

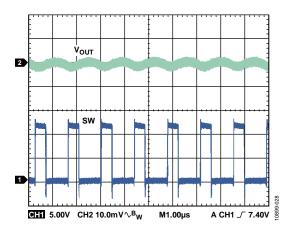

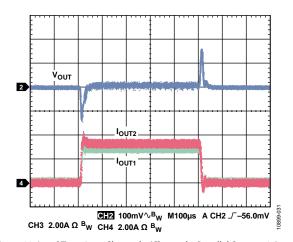

Figure 5. Channel 1/Channel 2 Efficiency Curve,  $V_{IN} = 12 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$ , FPWM Mode

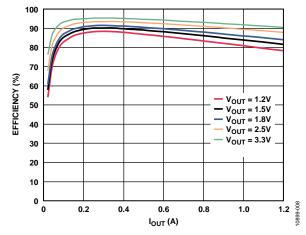

Figure 6. Channel 1/Channel 2 Efficiency Curve,  $V_{\rm IN} = 5.0$  V,  $f_{\rm SW} = 600$  kHz, FPWM Mode

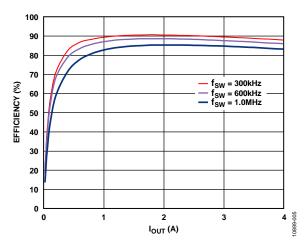

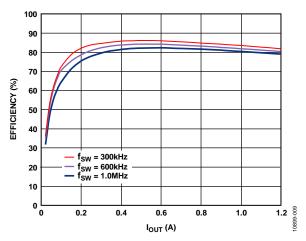

Figure 7. Channel 1/Channel 2 Efficiency Curve,  $V_{\text{IN}} = 12 \text{ V}$ ,  $V_{\text{OUT}} = 1.8 \text{ V}$ , FPWM Mode

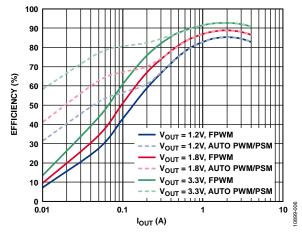

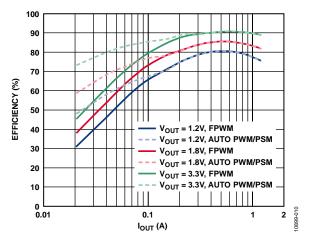

Figure 8. Channel 1/Channel 2 Efficiency Curve, V<sub>IN</sub> = 12 V, f<sub>SW</sub> = 600 kHz, FPWM and Automatic PWM/PSM Modes

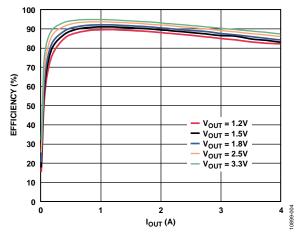

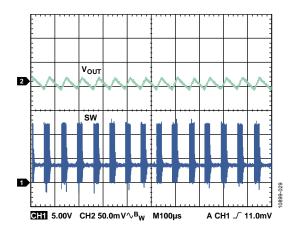

Figure 9. Channel 3/Channel 4 Efficiency Curve,  $V_{IN} = 12 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$ , FPWM Mode

Figure 10. Channel 3/Channel 4 Efficiency Curve,  $V_{IN} = 5.0 \text{ V}$ ,  $f_{SW} = 600 \text{ kHz}$ , FPWM Mode

Figure 11. Channel 3/Channel 4 Efficiency Curve,  $V_{IN} = 12 \text{ V}$ ,  $V_{OUT} = 1.8 \text{ V}$ , FPWM Mode

Figure 12. Channel 3/Channel 4 Efficiency Curve,  $V_{\rm IN}$  = 12 V,  $f_{\rm SW}$  = 600 kHz, FPWM and and Automatic PWM/PSM Modes

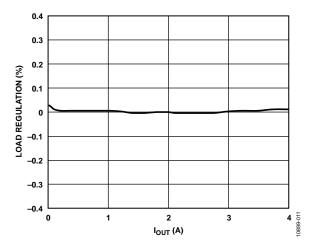

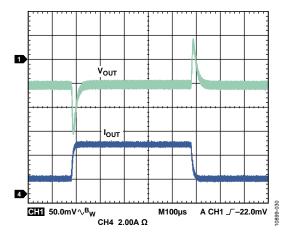

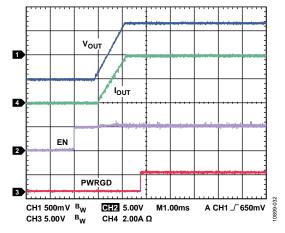

Figure 13. Channel 1 Load Regulation,  $V_{\rm IN}$  = 12 V,  $V_{\rm OUT}$  = 3.3 V,  $f_{\rm SW}$  = 600 kHz, FPWM Mode

Figure 14. Channel 1 Line Regulation,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 4 A,  $f_{SW}$  = 600 kHz, FPWM Mode

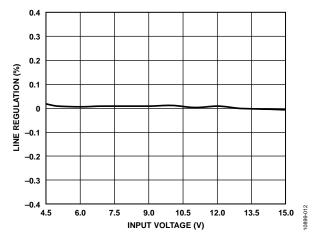

Figure 15. Channel 3 Load Regulation,  $V_{\rm IN}$  = 12 V,  $V_{\rm OUT}$  = 3.3 V,  $f_{\rm SW}$  = 600 kHz, FPWM Mode

Figure 16. Channel 3 Line Regulation,  $V_{OUT}$  = 3.3 V,  $I_{OUT}$  = 1 A,  $f_{SW}$  = 600 kHz, FPWM Mode

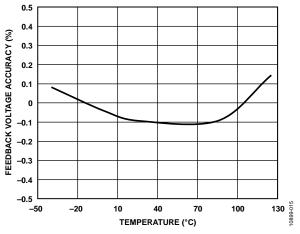

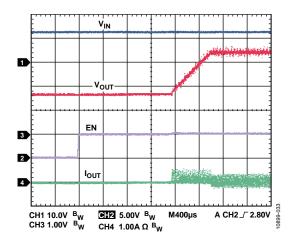

Figure 17. 0.8 V Feedback Voltage Accuracy vs. Temperature for Channel 1, Adjustable Output Model

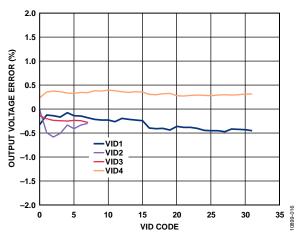

Figure 18. Output Voltage Error vs. VID Code, Adjustable Output Model

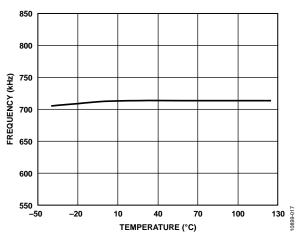

Figure 19. Frequency vs. Temperature,  $V_{IN} = 12 V$

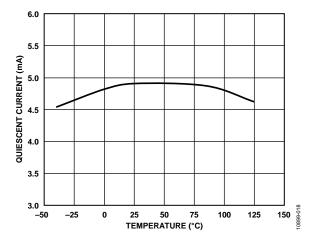

Figure 20. Quescient Current vs. Temperature (Includes PVIN1, PVIN2, PVIN3, and PVIN4)

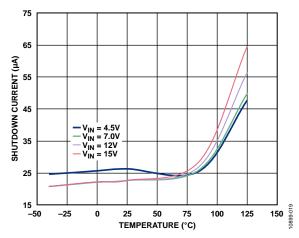

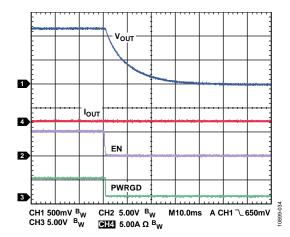

Figure 21. Shutdown Current vs. Temperature (EN1, EN2, EN3, EN4, and EN5 Low)

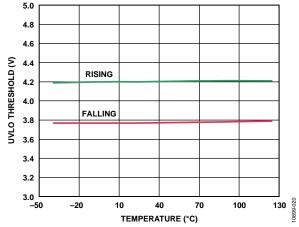

Figure 22. UVLO Threshold vs. Temperature

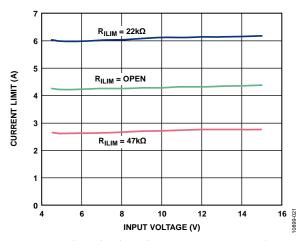

Figure 23. Channel 1/Channel 2 Current Limit vs. Input Voltage

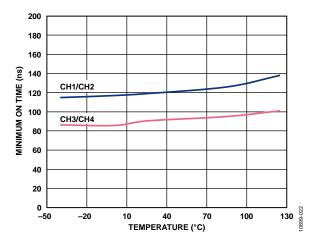

Figure 24. Minimum On Time vs. Temperature

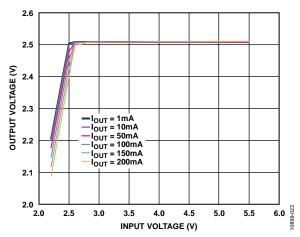

Figure 25. Channel 5 (LDO Regulator) Line Regulation over Output Load