# **ANALOG DEVICES**

# Advanced Battery Management PMIC with Inductive Boost LED and Three LDO Regulators

### **Data Sheet**

# ADP5350

### **FEATURES**

- Switching mode USB battery charger

- High accuracy and programmable charge terminal voltage and charge current

- 3 MHz buck for high efficiency and small footprint

- Tolerant input voltage from -0.5 V to +20 V (USB V<sub>VBUSx</sub>) Power path control allows system to operate with dead or missing battery

- Compliant with JEITA charge temperature specification

- Voltage-based state of charge (SOC) calculation algorithm Extra low quiescent current in sleep mode

- Battery impedance chemistry (Li-lon) compensation Battery temperature compensation

- No need for external sense resistor

- Boost regulator with 5-channel LED driver Support up to 4 LED in series or in parallel 5 independent programmable LED current sinks 64 programmable LED current levels (up to 20 mA) Programmable on and off timer for LED blinking Adaptive headroom control to maximize the efficiency

- Three 150 mA linear LDO regulators Ultralow Ιο with zero load at 1 μA typical for LDO1

- Optional load-switch full turn-on mode

- Full I<sup>2</sup>C programmability with dedicated interrupt pin

### APPLICATIONS

- Rechargeable Li-Ion and Li-Ion polymer battery-powered devices

- Portable consumer devices Portable medical devices Portable instrumentation devices Wearable devices

### **GENERAL DESCRIPTION**

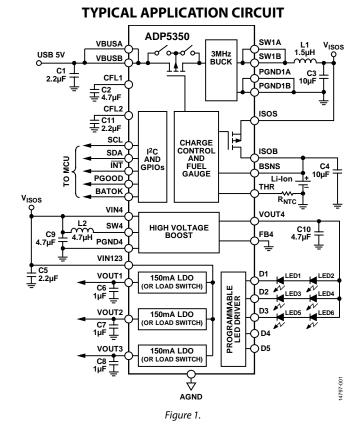

The ADP5350, a power management IC (PMIC), combines one high performance buck regulator for single Li-Ion/Li-Ion polymer battery charging, a fuel gauge, a highly programmable boost regulator for LED backlight illumination, and three 150 mA LDO regulators.

The ADP5350 operates in trickle charge mode and in constant current (CC) and constant voltage (CV) fast charge mode. It features an internal field effect transistor (FET) that permits battery isolation on the system power side.

The ADP5350 fuel gauge is a space-saving and low current consuming solution. It is optimal for rechargeable Li-Ion battery-powered devices, and features a voltage-based, battery SOC measurement function.

#### Rev. B

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

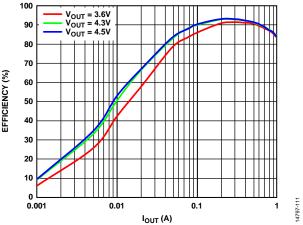

The ADP5350 boost regulator operates at a 1.5 MHz switching frequency. It can be operated as a constant voltage regulator or as a supplemental constant current regulator for multiple LED backlight drivers.

The ADP5350 LED drivers can support a wide range of LED backlight configurations, either multiple LEDs in parallel or in series.

The ADP5350 low dropout (LDO) regulators are optimized to operate at low shutdown current and quiescent current to extend battery life. The device also operates as a load switch that can be fully turned off or on.

The I<sup>2</sup>C-compatible interface enables the programmability of all parameters, including status bit readback for operation monitoring and safety control.

The ADP5350 operates over the  $-40^{\circ}$ C to  $+125^{\circ}$ C junction temperature range and is available in a 32-lead, 5 mm × 5 mm LFCSP package and a 32-ball, 3 mm × 3 mm WLCSP package.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017-2018 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **TABLE OF CONTENTS**

| Features                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                           |

| General Description                                                                                                                                                                                                                                     |

| Typical Application Circuit                                                                                                                                                                                                                             |

| Revision History                                                                                                                                                                                                                                        |

| Detailed Functional Block Diagram                                                                                                                                                                                                                       |

| Specifications                                                                                                                                                                                                                                          |

| Battery Charger Specifications 4                                                                                                                                                                                                                        |

| Battery Fuel Gauge Specifications 6                                                                                                                                                                                                                     |

| Boost and LED Driver Specifications7                                                                                                                                                                                                                    |

| LDO Specifications                                                                                                                                                                                                                                      |

| Recommended Input and Output Capacitance and<br>Inductance Specifications10                                                                                                                                                                             |

|                                                                                                                                                                                                                                                         |

| I <sup>2</sup> C-Compatible Interface Timing Specifications                                                                                                                                                                                             |

| I <sup>2</sup> C-Compatible Interface Timing Specifications 11<br>Absolute Maximum Ratings                                                                                                                                                              |

|                                                                                                                                                                                                                                                         |

| Absolute Maximum Ratings                                                                                                                                                                                                                                |

| Absolute Maximum Ratings       12         Thermal Resistance       12         ESD Caution       12         Pin Configuration and Function Descriptions       13         Typical Performance Characteristics       15         Typical Waveforms       19 |

### **REVISION HISTORY**

| 4  |

|----|

| 7  |

| 8  |

| 24 |

| 27 |

| 31 |

| 37 |

| 41 |

| 53 |

| 63 |

|    |

#### 11/2017—Rev. 0 to Rev. A

| Added CB-32-1                 | . Throughout |

|-------------------------------|--------------|

| Change to General Description |              |

| Battery Isolation FET                 | . 23 |

|---------------------------------------|------|

| Battery Detection                     | . 23 |

| Battery Temperature                   | . 24 |

| Battery Charger Operational Flowchart | . 26 |

| Battery Voltage-Based Fuel Gauge      | . 26 |

| Flowchart of SOC Calculation          | . 28 |

| Boost and White LED Drivers           | . 29 |

| Linear Low Dropout (LDO) Regulators   | . 33 |

| Thermal Management                    | . 34 |

| I <sup>2</sup> C Interface            | . 35 |

| I <sup>2</sup> C Addresses            | . 35 |

| SDA and SCL Pins                      | . 35 |

| Default Reset                         | . 35 |

| Interrupts                            | . 36 |

| Control Register Map                  | . 37 |

| Register Bit Descriptions             | . 39 |

| Applications Information              | . 58 |

| External Components                   | . 58 |

| PCB Layout Guidelines                 | . 60 |

| Typical Application Circuits          | . 61 |

| Factory-Programmable Options          | . 62 |

| Outline Dimensions                    | . 63 |

| Ordering Guide                        | . 63 |

|                                       |      |

| Changes to Table 1                            | 3  |

|-----------------------------------------------|----|

| Changes to Table 4                            | 8  |

| Changes to Figure 4 Caption and Table 9 Title | 13 |

| Added Figure 5; Renumbered Sequentially       | 14 |

| Added Table 10; Renumbered Sequentially       | 14 |

| Change to Figure 15 Caption                   |    |

| Change to Figure 23 Caption                   | 17 |

| Change to Figure 24 Caption                   |    |

| Changes to Figure 59                          | 60 |

| Updated Outline Dimensions                    | 61 |

| Changes to Ordering Guide                     | 61 |

|                                               |    |

2/2017—Revision 0: Initial Version

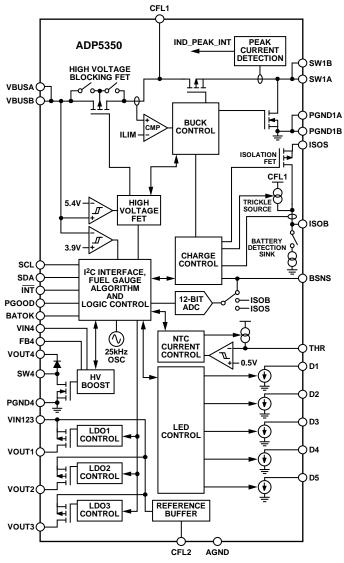

# DETAILED FUNCTIONAL BLOCK DIAGRAM

Figure 2. Detailed Functional Block Diagram

14797-022

### **SPECIFICATIONS** BATTERY CHARGER SPECIFICATIONS

$-40^{\circ}C < T_J < 125^{\circ}C, V_{VBUSx} = 5.0 \text{ V}, R_{NTC} = 47 \text{ k}\Omega, V_{VIN4} = V_{VIN123} = V_{ISOS} = 3.6 \text{ V}, C1 = 2.2 \text{ }\mu\text{F}, C2 = 4.7 \text{ }\mu\text{F}, C3 = 10 \text{ }\mu\text{F}, C4 = 10 \text{ }\mu\text{F}, C11 = 2.2 \text{ }\mu\text{F}, L1 = 1.5 \text{ }\mu\text{H}, all registers are at default values, unless otherwise noted.}$

| Table | 1. |

|-------|----|

|       |    |

| Parameter                                                      | Symbol                        | Test Conditions/Comments                                                                        | Min                      | Тур                    | Max   | Unit |

|----------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------------------------------------|--------------------------|------------------------|-------|------|

| GENERAL PARAMETERS                                             |                               | $T_J = 0^{\circ}C \text{ to } 85^{\circ}C$                                                      |                          |                        |       |      |

| Undervoltage Lockout                                           | V <sub>UVLO</sub>             | On BSNS, rising threshold, no $V_{VBUSx}$                                                       |                          | 2.45                   | 2.6   | V    |

|                                                                |                               | On BSNS, falling threshold, no VVBUSx                                                           | 2.2                      | 2.3                    |       | V    |

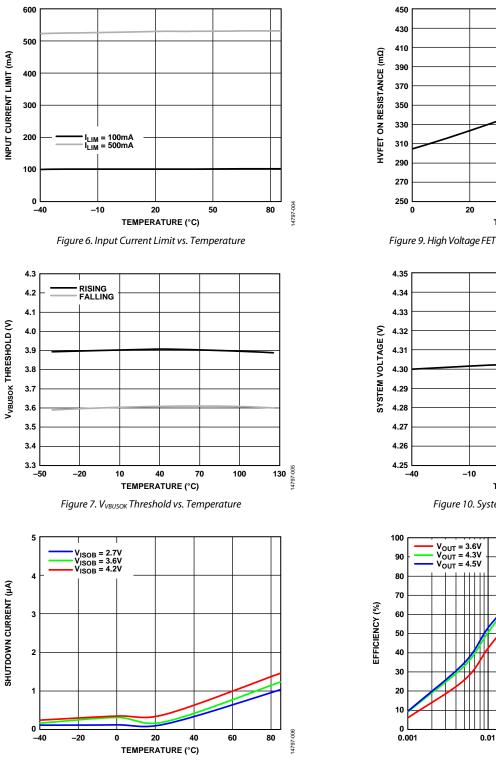

| Input Current Limit                                            | I <sub>LIM</sub>              | Set ILIM[3:0] = 100 mA                                                                          |                          | 92                     | 100   | mA   |

|                                                                |                               | Set ILIM[3:0] = 500 mA                                                                          |                          | 475                    | 500   | mA   |

| Operation Current                                              | lq                            | All enabled, no load, from VBUSx pin                                                            |                          | 4                      | 6     | mA   |

|                                                                |                               | Only fuel gauge enabled (active), from ISOB, no V <sub>VBUSx</sub>                              |                          | 160                    | 230   | μΑ   |

|                                                                |                               | Only fuel gauge enabled (sleep), from ISOB, no V <sub>VBUSx</sub> <sup>1</sup>                  |                          | 4                      |       | μΑ   |

|                                                                |                               | Only boost regulator enabled, all LEDs enabled, no LED current, from ISOB, no $V_{\text{VBUS}}$ |                          | 2                      | 2.6   | mA   |

|                                                                |                               | Only LDO1 enabled, from ISOB, no<br>V <sub>VBUSx</sub>                                          |                          | 0.8                    | 4     | μΑ   |

|                                                                |                               | Only LDO2 enabled, from ISOB, no V <sub>VBUSx</sub>                                             |                          | 160                    | 230   | μA   |

|                                                                |                               | Only LDO3 enabled, from ISOB, no V <sub>VBUSx</sub>                                             |                          | 160                    | 230   | μA   |

| Shutdown Current                                               | Istdn                         | All disabled, from ISOB and BSNS, no V <sub>VBUSx</sub>                                         |                          | 0.2                    | 2.8   | μA   |

| CHARGING PARAMETERS                                            |                               |                                                                                                 |                          |                        |       |      |

| Fast Charge Current, Constant<br>Current Mode                  | Існд                          | Programmable via l <sup>2</sup> C,<br>battery voltage > V <sub>TRK_DEAD</sub>                   | 25                       |                        | 650   | mA   |

| Fast Charge Current Accuracy                                   |                               | $I_{CHG} = 200 \text{ mA}$                                                                      | 180                      | 200                    | 220   | mA   |

|                                                                |                               | $T_J = 25^{\circ}C, I_{CHG} = 200 \text{ mA}$                                                   | -2.5                     |                        | +2.5  | %    |

| Trickle Charge Current <sup>2</sup>                            | I <sub>TRK_DEAD</sub>         |                                                                                                 | 16                       | 20                     | 25    | mA   |

| Weak Charge Current                                            | ICHG_WEAK                     | When V <sub>TRK_DEAD</sub> < V <sub>BSNS</sub> < V <sub>WEAK</sub>                              |                          | Ichg + Itrk_dead       |       | mA   |

| Dead Battery, Trickle to Weak<br>Charge Threshold <sup>2</sup> | $V_{\text{TRK}\_\text{DEAD}}$ | On BSNS                                                                                         | 2.4                      | 2.5                    | 2.62  | V    |

| Weak Battery                                                   |                               |                                                                                                 |                          |                        |       |      |

| Weak to Fast Charge Threshold <sup>2</sup>                     | VWEAK                         | On BSNS                                                                                         | 2.9                      | 3.0                    | 3.15  | V    |

| Weak Battery Threshold<br>Hysteresis <sup>1</sup>              | $\Delta V_{\text{WEAK}}$      |                                                                                                 |                          | 90                     |       | mV   |

| Battery Termination Voltage <sup>2</sup>                       | VTRM                          | On BSNS, T <sub>J</sub> = 0°C to 85°C                                                           | 4.158                    | 4.200                  | 4.242 | V    |

|                                                                |                               | On BSNS, TJ = 25°C                                                                              | -0.3                     |                        | +0.3  | %    |

| Battery Overvoltage Threshold                                  | VBAT_OV                       | Relative to CFL1 voltage, BSNS rising, $V_{CLF1} = 4.0 V$                                       | V <sub>CFL1</sub> – 0.15 |                        |       | V    |

| Charge Complete Current <sup>2</sup>                           | I <sub>END</sub>              | $V_{BSNS} = V_{TRM}$ , $T_J = 0^{\circ}C$ to $85^{\circ}C$                                      | 20                       | 35                     | 50    | mA   |

| Recharge Voltage Differential <sup>2</sup>                     | V <sub>RCH</sub>              | Relative to V <sub>TRM</sub> , BSNS falling                                                     |                          | 260                    |       | mV   |

| Battery Node Short Threshold<br>Voltage <sup>2</sup>           | $V_{\text{BAT}\_\text{SHR}}$  |                                                                                                 | 2.3                      | 2.4                    | 2.52  | V    |

| CHARGER DC-TO-DC REGULATOR                                     |                               |                                                                                                 |                          |                        |       |      |

| Switching Frequency                                            | <b>f</b> sw_chg               |                                                                                                 | 2.7                      | 3                      | 3.3   | MHz  |

| Maximum Duty Cycle <sup>3</sup>                                | D <sub>MAX</sub>              |                                                                                                 |                          | 96                     |       | %    |

| Peak Inductor Current                                          | I <sub>L1_PK</sub>            |                                                                                                 | 1500                     | 1750                   | 2200  | mA   |

| Regulated System Voltage                                       | V <sub>ISOS_TRK</sub>         | $V_{BSNS} < V_{TRK_{DEAD}}$ , trickle charge mode                                               |                          | V <sub>TRM</sub> + 0.1 |       | V    |

# **Data Sheet**

# ADP5350

| Parameter                                                    | Symbol                 | Test Conditions/Comments                                                           | Min  | Тур   | Мах  | Unit |

|--------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------|------|-------|------|------|

| DC to DC Power                                               |                        |                                                                                    |      |       |      |      |

| PMOS On Resistance                                           | R <sub>DSON_P</sub>    |                                                                                    |      | 220   | 280  | mΩ   |

| NMOS On Resistance                                           | Rdson n                |                                                                                    |      | 160   | 210  | mΩ   |

| SW1x Pin Leakage Current                                     | I <sub>SW1x</sub>      | $V_{SW1x} = 5.0 V$                                                                 |      |       | 2    | μA   |

| BATTERY ISOLATION FIELD EFFECT                               |                        |                                                                                    |      |       |      |      |

| TRANSISTOR (FET)                                             |                        |                                                                                    |      |       |      |      |

| LFCSP Package                                                |                        |                                                                                    |      | 202   | 300  | mΩ   |

| WLCSP Package                                                |                        |                                                                                    |      | 125   | 170  | mΩ   |

|                                                              | V <sub>ISOS_FC</sub>   | V <sub>TRK_DEAD</sub> < V <sub>BSNS</sub> , fast charging constant current mode    | 3.15 | 3.3   | 3.45 | V    |

| Battery Supplementary Threshold                              | V <sub>TH_ISO</sub>    | V <sub>ISOS</sub> < V <sub>ISOB</sub>                                              | 0    | 5     | 14   | mV   |

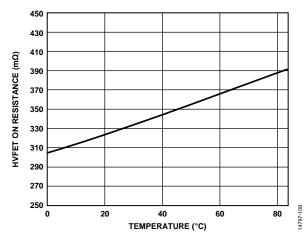

| HIGH VOLTAGE BLOCKING FET                                    |                        |                                                                                    |      |       |      |      |

| VBUSx Input                                                  |                        |                                                                                    |      |       |      |      |

| High Voltage Blocking FET On<br>Resistance                   | Rdson_hv               | $I_{VBUS} = 100 \text{ mA}, T_J = 0^{\circ}\text{C to } 85^{\circ}\text{C}$        |      | 330   |      | mΩ   |

| Current, Suspend Mode                                        | ISUSPEND               | EN_DCDC = low                                                                      |      | 1.45  | 1.8  | mA   |

| Input Voltage                                                |                        |                                                                                    |      |       |      |      |

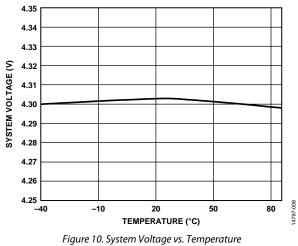

| Power-Good Threshold                                         | <b>V</b> VBUSOK        |                                                                                    |      |       |      |      |

| Rising                                                       | VVBUSOK RISE           |                                                                                    | 3.77 | 3.9   | 4.03 | v    |

| Falling                                                      | VVBUSOK FALL           |                                                                                    | 3.47 | 3.6   | 3.73 | v    |

| Overvoltage Threshold                                        | VVBUS OV               |                                                                                    | 5.38 | 5.45  | 5.53 | v    |

| Overvoltage Threshold                                        | _                      |                                                                                    |      | 75    |      | mV   |

| Hysteresis                                                   |                        |                                                                                    |      |       |      |      |

| THERMAL CONTROL                                              |                        |                                                                                    |      |       |      |      |

| Thermal Early Warning<br>Temperature <sup>1</sup>            | $T_{SD_W}$             |                                                                                    |      | 130   |      | °C   |

| Thermal Shutdown Temperature <sup>1</sup>                    | T <sub>SD</sub>        | T, rising                                                                          |      | 140   |      | °C   |

|                                                              |                        | T⊥falling                                                                          |      | 110   |      | °C   |

| THERMISTOR CONTROL                                           |                        |                                                                                    |      |       |      |      |

| Resistance Thresholds by Battery<br>Temperature <sup>4</sup> |                        | $R_{NTC} = 47 \text{ k}\Omega$ , BETA_NTC = 3800,<br>T <sub>J</sub> = 0°C to +85°C |      |       |      |      |

| LFCSP Package                                                |                        |                                                                                    |      |       |      |      |

| Cool to Cold                                                 | R <sub>COOL_COLD</sub> |                                                                                    | 131  | 151.2 | 175  | kΩ   |

| Cold to Cool                                                 | RCOLD_COOL             |                                                                                    | 126  | 145.6 | 168  | kΩ   |

| Typical to Cool⁴                                             | R <sub>TYP_COOL</sub>  |                                                                                    | 75   | 86.5  | 99   | kΩ   |

| Cool to Typical <sup>4</sup>                                 | RCOOL_TPY              |                                                                                    | 72.5 | 83.1  | 95   | kΩ   |

| Warm to Typical <sup>₄</sup>                                 | RWARM_TYP              |                                                                                    | 20   | 23.7  | 27   | kΩ   |

| Typical to Warm <sup>₄</sup>                                 | R <sub>TYP_WARM</sub>  |                                                                                    | 19.3 | 22    | 24.6 | kΩ   |

| Hot to Warm                                                  | RHOT_WARM              |                                                                                    | 12   | 13.9  | 16   | kΩ   |

| Warm to Hot                                                  | Rwarm_hot              |                                                                                    | 11   | 12.7  | 14.4 | kΩ   |

| WLCSP Package                                                |                        |                                                                                    |      |       |      |      |

| Cool to Cold                                                 | RCOOL_COLD             |                                                                                    | 140  | 162   | 185  | kΩ   |

| Cold to Cool                                                 | RCOLD_COOL             |                                                                                    | 133  | 156   | 180  | kΩ   |

| Typical to Cool⁴                                             | R <sub>TYP_COOL</sub>  |                                                                                    | 77   | 90    | 102  | kΩ   |

| Cool to Typical <sup>4</sup>                                 | RCOOL_TPY              |                                                                                    | 75   | 86    | 100  | kΩ   |

| Warm to Typical <sup>4</sup>                                 | Rwarm_typ              |                                                                                    | 20   | 23    | 26   | kΩ   |

| Typical to Warm <sup>4</sup>                                 | R <sub>TYP_warm</sub>  |                                                                                    | 18.5 | 21    | 24   | kΩ   |

| Hot to Warm                                                  | RHOT_WARM              |                                                                                    | 11.5 | 13    | 15   | kΩ   |

| Warm to Hot                                                  | Rwarm_hot              |                                                                                    | 10.5 | 12    | 13.5 | kΩ   |

| Parameter                             | Symbol                  | Test Conditions/Comments                                                         | Min | Тур | Max  | Unit |

|---------------------------------------|-------------------------|----------------------------------------------------------------------------------|-----|-----|------|------|

| BATTERY DETECTION                     |                         |                                                                                  |     |     |      |      |

| Sink Current                          | Isink                   |                                                                                  | 15  | 25  | 35   | mA   |

| Source Current                        | ISOURCE                 |                                                                                  | 7   | 10  | 13   | mA   |

| Battery Threshold                     |                         |                                                                                  |     |     |      |      |

| Low                                   | VBATL                   |                                                                                  | 1.8 | 1.9 | 2.0  | V    |

| High                                  | VBATH                   |                                                                                  | 3.3 | 3.4 | 3.55 | V    |

| Battery Detection Timer               | tваток                  |                                                                                  |     | 333 |      | ms   |

| TIMERS                                |                         |                                                                                  |     |     |      |      |

| Start Charging Delay Timer            | tstart                  |                                                                                  |     | 1   |      | sec  |

| Trickle Charge Timer <sup>2</sup>     | t <sub>TRK</sub>        |                                                                                  |     | 60  |      | min  |

| Fast Charge Timer <sup>2</sup>        | t <sub>снд</sub>        |                                                                                  |     | 600 |      | min  |

| Charge Complete Timer                 | t <sub>end</sub>        | V <sub>BSNS</sub> = V <sub>TRM</sub> , I <sub>CHG</sub> < I <sub>END</sub>       |     | 7.5 |      | min  |

| Deglitch Timer                        | t <sub>DG</sub>         | Applies to VTRM, VRCH, IEND, VWEAK, VTRK_DEAD,<br>VVBUSOK_FALL, and VVBUSOK_RISE |     | 31  |      | ms   |

| Watchdog Timer <sup>2</sup>           | t <sub>WD</sub>         |                                                                                  |     | 32  |      | sec  |

| Safety Timer                          | t <sub>SAFE</sub>       |                                                                                  |     | 40  |      | min  |

| Battery Node Short Timer <sup>2</sup> | t <sub>BAT_SHR</sub>    |                                                                                  |     | 30  |      | sec  |

| I <sup>2</sup> C (SCL AND SDA)        |                         |                                                                                  |     |     |      |      |

| Input Voltage                         |                         |                                                                                  |     |     |      |      |

| Low Level                             | VIL                     | Applies to SCL, SDA                                                              |     |     | 0.5  | V    |

| High Level                            | VIH                     | Applies to SCL, SDA                                                              | 1.2 |     |      | V    |

| Low Level Output Voltage              | Vol                     | Applies to SDA, I <sub>SDA_SINK</sub> = 2 mA                                     |     |     | 0.4  | V    |

| PGOOD AND BATOK                       |                         |                                                                                  |     |     |      |      |

| PGOOD Pin                             |                         |                                                                                  |     |     |      |      |

| Leakage Current                       | IPGOOD_LEAK             | $V_{PGOOD} = 5 V$                                                                |     |     | 0.5  | μΑ   |

| Output Low Voltage                    | $V_{PGOOD\_LOW}$        | $I_{PGOOD} = 1 \text{ mA}$                                                       |     | 50  | 100  | mV   |

| BATOK Pin                             |                         |                                                                                  |     |     |      |      |

| Leakage Current                       | I <sub>BATOK_LEAK</sub> | $V_{BATOK} = 5 V$                                                                |     |     | 0.5  | μΑ   |

| Output Low Voltage                    | VBATOK_LOW              | $I_{BATOK} = 1 \text{ mA}$                                                       |     | 50  | 100  | mV   |

<sup>1</sup> Specification is not production tested, but is supported by characterization data at initial product release. <sup>2</sup> These values are programmable via the I<sup>2</sup>C interface. Values are given with default register values.

<sup>3</sup> Guaranteed by design.

<sup>4</sup> Typical temperature is the normal operation temperature.

#### **BATTERY FUEL GAUGE SPECIFICATIONS**

$V_{VIN4} = V_{VIN123} = V_{ISOS} = 4.2 \text{ V}, T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted

#### Table 2.

| Parameter                  | Test Conditions/Comments                    | Min   | Тур  | Мах   | Unit |

|----------------------------|---------------------------------------------|-------|------|-------|------|

| BATTERY VOLTAGE MONITORING |                                             |       |      |       |      |

| Battery Monitor Voltage    |                                             |       |      |       |      |

| Range                      |                                             | 2.7   |      | 4.5   | V    |

| Resolution                 | Based on 12-bit ADC                         |       | 1.09 |       | mV   |

| Voltage Reading Accuracy   | $T_J = 25^{\circ}C$                         | -12.5 |      | +12.5 | mV   |

|                            | $T_J = 0^{\circ}C \text{ to } +85^{\circ}C$ | -30   |      | +30   | mV   |

### **BOOST AND LED DRIVER SPECIFICATIONS**

$V_{VIN4} = V_{VIN123} = V_{ISOS} = 3.6$  V, C9 = 4.7  $\mu$ F, C10 = 4.7  $\mu$ F, L2 = 4.7  $\mu$ H, T<sub>J</sub> = -40°C to +125°C for minimum/maximum specifications, and T<sub>A</sub> = 25°C for typical specifications, unless otherwise noted.

#### Table 3. Parameter Symbol **Test Conditions/Comments** Min Тур Max Unit INPUT CHARACTERISTICS Input Voltage Range $V_{\text{VIN4}}$ 2.85 5.5 ۷ UNDERVOLTAGE LOCKOUT VIN4 rising 2.7 2.85 V VUVLO\_VIN4\_RISE $V_{\text{UVLO}\_\text{VIN4}\_\text{FALL}}$ VIN4 falling 2.5 2.6 V **OUTPUT CHARACTERISTICS** Standalone operation mode **Output Voltage Range** ۷ VVOUT4 Visos 16 **FB4 Voltage Reference** 0.62 0.65 0.68 ٧ $V_{FB4}$ T<sub>J</sub> = 25°C -1.5 +1.5% Line Regulation<sup>1</sup> $\Delta V_{VOUT4}/V_{VIN4}$ %/V 0.1 POWER GOOD (PGOOD) Standalone operation mode **PGOOD** Rising Threshold 90 % VPGOOD4 RISE **PGOOD Hysteresis** 5.5 $V_{\text{PGOOD4}_\text{HYS}}$ % **PGOOD Falling Delay** 2 ms tpgood4\_fall **PGOOD** Rising Delay 2 ms tpg004\_RISE SW4 CHARACTERISTICS NFET at $V_{VIN4} = 3.6 V$ SW4 On Resistance RDSON\_NFET 460 800 mΩ **Overvoltage Threshold** V<sub>OVP4</sub> Boost OVP threshold = 18.5 V 17.5 18.5 19.5 V Boost OVP threshold = 15 V14.2 ۷ 15 15.8 Boost OVP threshold = 10 V 9.5 10.5 ۷ 10 Boost OVP threshold = 5.6 V ۷ 5.32 5.6 5.9 $V_{\text{OVP4}\_\text{HYS}}$ OVP recovery hysteresis<sup>1</sup> 5 % Start-Up Time 1.0 2.7 ms tss4 CURRENT LIMIT $BST_IPK = 0$ 510 600 690 ILIM4 mΑ $BST_IPK = 1$ 300 mΑ OSCILLATOR CIRCUIT Switching Frequency 1.35 1.65 MHz $f_{SW4}$ 1.5 **Minimum On Time** 50 t<sub>MIN\_ON4</sub> ns LED CURRENT CONTROL LED Current Range, 6-Bit 0 20 mΑ **I**<sub>Dx</sub> Accuracy $I_{Dx} = 20 \text{ mA}$ -10 +10 % $I_{Dx} = 20 \text{ mA}$ 2.0 % Matching LED Pin Leakage Current 0.5 μA Dx\_LEAK LED Current Ramp-Up Time t<sub>Dx</sub> rise $I_{Dx} = 20 \text{ mA}$ 20 μs 20 LED Current Ramp-Down Time $I_{\text{Dx}} = 20 \text{ mA}$ t<sub>Dx\_FALL</sub> μs LED Source Headroom ILEDx[5:0] =11111 V $V_{\text{Dx}_{\text{HDRM}}}$ 0.65 0.75 LED ON/OFF TIMER +10 LED Timer Accuracy Including on timer and off timer -10 %

<sup>1</sup> Specification is not production tested, but is supported by characterization data at initial product release.

### LDO SPECIFICATIONS

$V_{VBUSx} = 5.0 \text{ V}, V_{VIN4} = V_{VIN123} = V_{ISOS} = 3.6 \text{ V}, C5 = C6 = C7 = C8 = 1 \ \mu\text{F}; T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

| Parameter                                 | Symbol                                     | Test Conditions/Comments                                                                   | Min   | Тур | Max   | Unit  |

|-------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------|-------|-----|-------|-------|

| LDO1 INPUT VOLTAGE RANGE                  | V <sub>VIN123</sub>                        |                                                                                            | 2.56  |     | 5.5   | V     |

| KEEPALIVE LDO1                            |                                            |                                                                                            |       |     |       |       |

| UNDERVOLTAGE LOCKOUT                      | VUVLO_LDO1_RISE                            | VIN123 rising                                                                              |       |     | 2.56  | V     |

|                                           | VUVLO_LDO1_FALL                            | VIN123 falling                                                                             | 1.78  |     |       | V     |

|                                           | VUVLO_LDO1_HYS                             |                                                                                            |       | 200 |       | mV    |

| Output Voltage Range                      | V <sub>VOUT1</sub>                         | Fuse trim or I <sup>2</sup> C, four bits                                                   | 1.0   |     | 4.2   | V     |

| Output Accuracy                           |                                            | $I_{OUT1} = 10 \text{ mA}, T_J = 25^{\circ}\text{C}$                                       | -1    |     | +1    | %     |

|                                           |                                            | I <sub>OUT1</sub> = 10 mA                                                                  | -2.0  |     | +2.0  | %     |

| Line Regulation                           | $\Delta V_{VOUT1}/V_{IN123}$               | $V_{VIN123} = (V_{VOUT1} + 0.5 V)$ to 5.5 V                                                | -0.1  |     | +0.1  | %/V   |

| Load Regulation                           | $\Delta V_{VOUT1}/I_{OUT1}$                | I <sub>OUT1</sub> = 100 μA to 150 mA                                                       |       |     | 0.015 | %/m/  |

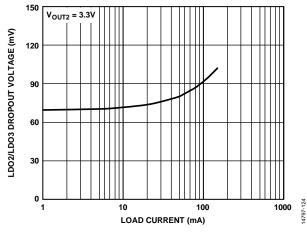

| Dropout Voltage                           | V <sub>DROP_OUT1</sub>                     | V <sub>VOUT1</sub> = 3.3 V, I <sub>OUT1</sub> = 10 mA                                      |       | 54  | 130   | mV    |

| . 5                                       |                                            | Vvout1 = 3.3 V, Iout1 = 150 mA                                                             |       | 150 | 240   | mV    |

| Current-Limit Threshold                   | ILIM LDO1                                  |                                                                                            | 200   | 300 | 440   | mA    |

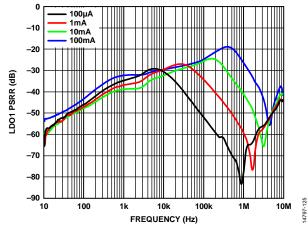

| Output Noise <sup>1</sup>                 | V <sub>NOISE_LDO1</sub>                    | 10 Hz to 100 kHz, VVIN123= 3.6 V, VVOUT1 = 3.3 V                                           |       | 100 | -     | μV rn |

| Power Supply Rejection Ratio <sup>1</sup> | PSRR                                       | 100 Hz, V <sub>VIN123</sub> = 3.6 V, V <sub>VOUT1</sub> = 3.3 V, I <sub>OUT1</sub> = 10 mA |       | 40  |       | dB    |

|                                           |                                            | 1 kHz, V <sub>VIN123</sub> = 3.6 V, V <sub>VOUT1</sub> = 3.3 V, I <sub>OUT1</sub> = 10 mA  |       | 35  |       | dB    |

| LDO Start-Up Time                         | t <sub>ss LDO1</sub>                       | V <sub>VOUT1</sub> = 3.3 V, LDO mode                                                       |       | 600 |       | μs    |

| PGOOD Rising Threshold                    | VPGOOD1 RISE                               | Only effective in LDO mode                                                                 |       | 90  |       | %     |

| PGOOD Hysteresis                          | V <sub>PGOOD1_HYS</sub>                    |                                                                                            |       | 4.5 |       | %     |

| PGOOD Falling Delay                       | tpgood1 Fall                               |                                                                                            |       | 120 |       | μs    |

| PGOOD Rising Delay                        | t <sub>PGOOD1_RISE</sub>                   |                                                                                            |       | 2   |       | ms    |

| Load Switch Turn-On Rise Time             | t <sub>RISE_SWITCH1</sub>                  | $V_{OUT1} = 3.3 V$ , load switch mode                                                      |       | 120 |       | μs    |

| Load Switch On Resistance                 | R <sub>DSON</sub> SWITCH1                  |                                                                                            |       | 700 |       | mΩ    |

| Cout Discharge Switch On<br>Resistance    | R <sub>DIS_LD01</sub>                      | V <sub>VIN123</sub> = 3.6 V                                                                |       | 500 |       | Ω     |

| LDO2 INPUT VOLTAGE RANGE                  | V <sub>VIN4</sub>                          | V <sub>VIN4</sub> = V <sub>VIN123</sub>                                                    | 2.85  |     | 5.5   | V     |

| GENERAL-PURPOSE LDO2                      |                                            |                                                                                            |       |     |       |       |

| Undervoltage Lockout                      | VUVLO_LDO2_RISE                            | VIN4 rising                                                                                |       | 2.7 | 2.85  | V     |

|                                           | VUVLO_LDO2_FALL                            | VIN4 falling                                                                               | 2.5   | 2.6 |       | V     |

|                                           | VUVLO_LDO2_HYS                             |                                                                                            |       | 100 |       | mV    |

| Output Voltage Range                      | V <sub>VOUT2</sub>                         | Fuse trim or I <sup>2</sup> C, 4 bits                                                      | 1.0   |     | 4.2   | V     |

| Output Accuracy                           |                                            | I <sub>OUT2</sub> = 10 mA, T <sub>J</sub> = 25°C                                           | -0.75 |     | +0.75 | %     |

|                                           |                                            | I <sub>OUT2</sub> = 10 mA                                                                  | -1.5  |     | +1.5  | %     |

| Line Regulation                           | (ΔV <sub>VOUT2</sub> )/V <sub>VIN123</sub> | $V_{VIN123} = (V_{VOUT2} + 0.5 V)$ to 5.5 V                                                | -0.1  |     | +0.1  | %/V   |

| Load Regulation                           | (ΔVvout2)/Ιουτ2                            | I <sub>OUT2</sub> = 100 μA to 150 mA                                                       |       |     | 0.01  | %/m   |

| Dropout Voltage                           |                                            |                                                                                            |       |     |       |       |

| LFCSP Package                             | VDROP_OUT2                                 | V <sub>VOUT2</sub> = 3.3 V, I <sub>OUT2</sub> = 10 mA                                      |       | 76  | 140   | mV    |

| WFCSP Package                             | VDROP_OUT2                                 | V <sub>VOUT2</sub> = 3.3 V, I <sub>OUT2</sub> = 10 mA                                      |       | 65  | 120   | mV    |

| LFCSP Package                             | V <sub>DROP_OUT2</sub>                     | V <sub>VOUT2</sub> = 3.3 V, I <sub>OUT2</sub> = 150 mA                                     |       | 100 | 180   | mV    |

| WFCSP Package                             | VDROP_OUT2                                 | V <sub>VOUT2</sub> = 3.3 V, I <sub>OUT2</sub> = 150 mA                                     |       | 80  | 150   | mV    |

| Current-Limit Threshold                   | ILIM_LDO2                                  |                                                                                            | 220   | 320 | 430   | mA    |

# **Data Sheet**

# ADP5350

| Parameter                                 | Symbol                       | Test Conditions/Comments                                                                 | Min   | Тур | Max   | Unit   |

|-------------------------------------------|------------------------------|------------------------------------------------------------------------------------------|-------|-----|-------|--------|

| Output Noise <sup>1</sup>                 | V <sub>NOISE_LDO2</sub>      | 10 Hz to 100 kHz, V <sub>VIN123</sub> = 3.6 V, V <sub>VOUT2</sub> = 3.3 V                |       | 120 |       | μV rms |

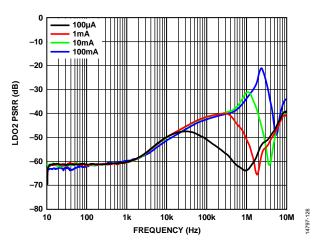

| Power Supply Rejection Ratio <sup>1</sup> | PSRR                         | 100 Hz, V <sub>IN123</sub> = 3.6 V, V <sub>VOUT2</sub> = 3.3V, I <sub>OUT2</sub> = 10 mA |       | 60  |       | dB     |

|                                           |                              | 1 kHz, V <sub>IN123</sub> = 3.6 V, V <sub>VOUT2</sub> = 3.3 V, I <sub>OUT2</sub> = 10 mA |       | 50  |       | dB     |

| LDO Start-Up Time                         | tss_ldo2                     | V <sub>VOUT2</sub> = 3.3 V, LDO mode                                                     |       | 80  |       | μs     |

| Load Switch Turn-On Rise Time             | trise_switch2                | V <sub>VOUT2</sub> = 3.3 V, load switch mode                                             |       | 80  |       | μs     |

| Load Switch On Resistance                 |                              |                                                                                          |       |     |       |        |

| LFCSP Package                             | Rdson_switch2                |                                                                                          |       | 400 | 600   | mΩ     |

| WFCSP Package                             | Rdson_switch2                |                                                                                          |       | 300 | 500   | mΩ     |

| Cout Discharge Switch On<br>Resistance    | Rdis_ldo2                    | V <sub>VIN123</sub> = 3.6 V                                                              |       | 500 |       | Ω      |

| LDO3 INPUT VOLTAGE RANGE                  | V <sub>VIN4</sub>            | $V_{VIN4} = V_{VIN123}$                                                                  | 2.85  |     | 5.5   | V      |

| GENERAL-PURPOSE LDO3                      |                              |                                                                                          |       |     |       |        |

| UNDERVOLTAGE LOCKOUT                      | VUVLO_LDO3_RISE              | VIN4 rising                                                                              |       | 2.7 | 2.85  | V      |

|                                           | VUVLO_LDO3_FALL              | VIN4 falling                                                                             | 2.5   | 2.6 |       | V      |

|                                           | VUVLO_LDO3_HYS               |                                                                                          |       | 100 |       | mV     |

| Output Voltage Range                      | V <sub>VOUT3</sub>           | Fuse trim or I <sup>2</sup> C, four bits                                                 | 1.0   |     | 4.2   | V      |

| Output Accuracy                           | V <sub>VOUT3</sub>           | I <sub>OUT3</sub> = 10 mA, T <sub>J</sub> = +25°C                                        | -0.75 |     | +0.75 | %      |

|                                           |                              | I <sub>ОUT3</sub> = 10 mA                                                                | -1.5  |     | +1.5  | %      |

| Line Regulation                           | $\Delta V_{OUT3}/V_{VIN123}$ | V <sub>VIN123</sub> = (V <sub>VOUT3</sub> + 0.5 V) to 5.5 V                              | -0.1  |     | +0.1  | %/V    |

| Load Regulation                           | ΔVουτ3/Ιουτ3                 | I <sub>OUT3</sub> = 100 μA to 150 mA                                                     |       |     | 0.01  | %/mA   |

| Dropout Voltage                           |                              |                                                                                          |       |     |       |        |

| LFCSP Package                             | Vdrop_out3                   | V <sub>VOUT3</sub> = 3.3 V, I <sub>OUT3</sub> = 10 mA                                    |       | 76  | 140   | mV     |

| WFCSP Package                             | V <sub>DROP_OUT3</sub>       | V <sub>VOUT3</sub> = 3.3 V, I <sub>OUT3</sub> = 10 mA                                    |       | 65  | 120   | mV     |

| LFCSP Package                             | Vdrop_out3                   | V <sub>VOUT3</sub> = 3.3 V, I <sub>OUT3</sub> = 150 mA                                   |       | 100 | 180   | mV     |

| WFCSP Package                             | V <sub>DROP_OUT3</sub>       | $V_{VOUT3} = 3.3 \text{ V}, I_{OUT3} = 150 \text{ mA}$                                   |       | 80  | 150   | mV     |

| Current Limit Threshold                   | ILIM_LDO3                    |                                                                                          | 220   | 320 | 430   | mA     |

| Output Noise <sup>1</sup>                 | V <sub>NOISE_LDO3</sub>      | 10 Hz to 100 kHz, $V_{VIN123}$ = 3.6 V, $V_{VOUT3}$ = 3.3 V                              |       | 120 |       | μV rms |

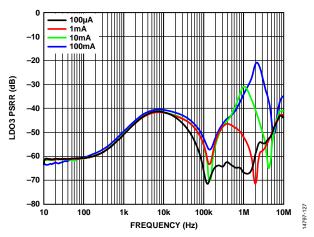

| Power Supply Rejection Ratio <sup>1</sup> | PSRR                         | 100 Hz, $V_{VIN123}$ = 3.6 V, $V_{VOUT3}$ = 3.3 V, $I_{OUT3}$ = 10 mA                    |       | 60  |       | dB     |

|                                           |                              | 1 kHz, $V_{VIN123}$ = 3.6 V, $V_{VOUT3}$ = 3.3 V, $I_{OUT3}$ = 10 mA                     |       | 50  |       | dB     |

| LDO Start-Up Time                         | tss_ldo3                     | V <sub>VOUT3</sub> = 3.3 V, LDO mode                                                     |       | 80  |       | μs     |

| Load Switch Turn-On Rise Time             | t <sub>RISE_SWITCH3</sub>    | $V_{VOUT3} = 3.3 V$ , load switch mode                                                   |       | 80  |       | μs     |

| Load Switch On Resistance                 |                              |                                                                                          |       |     |       |        |

| LFCSP Package                             | R <sub>DSON_SWITCH3</sub>    |                                                                                          |       | 400 | 600   | mΩ     |

| WFCSP Package                             | Rdson_switch3                |                                                                                          |       | 300 | 500   | mΩ     |

| Cout Discharge Switch On<br>Resistance    | Rdis_ldo3                    | $V_{IN123} = 3.6 V$                                                                      |       | 500 |       | Ω      |

<sup>1</sup> Guaranteed by design.

### **RECOMMENDED INPUT AND OUTPUT CAPACITANCE AND INDUCTANCE SPECIFICATIONS**

| Parameter             | Min  | Тур | Max | Unit |

|-----------------------|------|-----|-----|------|

| EFFECTIVE CAPACITANCE |      |     |     |      |

| Charger Capacitance   |      |     |     |      |

| VBUSx Pin             | 1.0  | 2.2 |     | μF   |

| CFL1 Pin              | 2.0  | 4.7 |     | μF   |

| CFL2 Pin              | 1.0  | 2.2 |     | μF   |

| ISOS Pin              | 4.0  | 10  |     | μF   |

| ISOB Pin              | 4.0  | 10  |     | μF   |

| LDO Capacitance       |      |     |     |      |

| VIN123 Pin            | 0.7  | 1   |     | μF   |

| LDO1                  | 0.7  | 1   |     | μF   |

| LDO2                  | 0.7  | 1   |     | μF   |

| LDO3                  | 0.7  | 1   |     | μF   |

| Boost Capacitance     |      |     |     |      |

| VIN4 Pin              | 1    | 4.7 |     | μF   |

| VOUT4 Pin             | 0.47 | 4.7 |     | μF   |

| NDUCTANCE             |      |     |     |      |

| Buck                  | 0.5  | 1.5 | 2.2 | μH   |

| Boost                 | 2    | 4.7 | 10  | μH   |

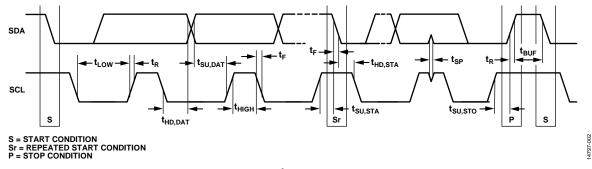

### I<sup>2</sup>C-COMPATIBLE INTERFACE TIMING SPECIFICATIONS

#### Table 6.

| Parameter                                          | Symbol                  | Min | Тур | Max | Unit |

|----------------------------------------------------|-------------------------|-----|-----|-----|------|

| I <sup>2</sup> C-COMPATIBLE INTERFACE              |                         |     |     |     |      |

| Capacitive Load, Each Bus Line                     | Cs                      |     |     | 400 | pF   |

| SCL                                                |                         |     |     |     |      |

| Clock Frequency                                    | <b>f</b> <sub>SCL</sub> |     |     | 400 | kHz  |

| High Time                                          | tніgн                   | 0.6 |     |     | μs   |

| Low Time                                           | t <sub>LOW</sub>        | 1.3 |     |     | μs   |

| Data                                               |                         |     |     |     |      |

| Setup Time                                         | t <sub>su,DAT</sub>     | 100 |     |     | ns   |

| Hold Time <sup>1</sup>                             | thd,dat                 | 0   |     | 0.9 | μs   |

| Setup Time for Repeated Start                      | t <sub>su,sta</sub>     | 0.6 |     |     | μs   |

| Hold Time for Start/Repeated Start                 | thd,sta                 | 0.6 |     |     | μs   |

| Bus Free Time Between a Stop and a Start Condition | t <sub>BUF</sub>        | 1.3 |     |     | μs   |

| Setup Time for Stop Condition                      | t <sub>su,sto</sub>     | 0.6 |     |     | μs   |

| SCL/SDA                                            |                         |     |     |     |      |

| Rise Time                                          | t <sub>R</sub>          |     |     | 300 | ns   |

| Fall Time                                          | t <sub>F</sub>          |     |     | 300 | ns   |

| Pulse Width of Suppressed Spike                    | t <sub>SP</sub>         | 0   |     | 50  | ns   |

<sup>1</sup> A master device must provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL. See Figure 3, the I<sup>2</sup>C timing diagram.

#### Timing Diagram

Figure 3. I<sup>2</sup>C Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 7.

| Parameter                                                                                 | Rating           |

|-------------------------------------------------------------------------------------------|------------------|

| VBUSA, VBUSB to PGND1                                                                     | –0.5 V to +20 V  |

| SW4, VOUT4, D1, D2, D3, D4, D5 to PGND4                                                   | –0.5 V to +20 V  |

| FB4                                                                                       | –0.3 V to +6 V   |

| CFL2 to AGND                                                                              | –0.3 V to +3.3 V |

| PGND1, PGND4 to AGND                                                                      | –0.3 V to +0.3 V |

| All Other Pins to AGND                                                                    | –0.3 V to +6 V   |

| Continuous Drain Current, Battery<br>Supplementary Mode, from ISOB to<br>ISOS, TJ = 125°C | 1.1 A            |

| Storage Temperature Range                                                                 | –65°C to +150°C  |

| Operating Junction Temperature Range                                                      | -40°C to +125°C  |

| Soldering Conditions                                                                      | JEDEC J-STD-020  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment.

Careful attention to PCB thermal design is required.  $\theta_{JA}$  is the natural convection junction to ambient thermal resistance measured in a one cubic foot sealed enclosure.  $\theta_{JC}$  is the junction to case thermal resistance.

#### Table 8. Thermal Resistance

| Package Type | θ <sub>JA</sub> | οιθ | Unit |  |

|--------------|-----------------|-----|------|--|

| CP-32-121    | 42              | 2.1 | °C/W |  |

| CB-32-1      | 64              | 0.7 | °C/W |  |

<sup>1</sup> Thermal impedance simulated values are based on a JEDEC 2S2P thermal test board with nine thermal vias. See JEDEC JESD51.

#### Maximum Power Dissipation

The maximum safe power dissipation in the ADP5350 package is limited by the associated rise in junction temperature  $(T_I)$  on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, permanently shifting the parametric performance of the ADP5350. Exceeding a junction temperature of 175°C for an extended period of time can result in changes in the silicon devices that potentially cause failure.

#### ESD CAUTION

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

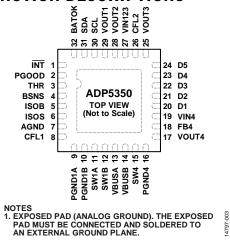

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. LFCSP Pin Configuration (Top View)

| Pin No. | Mnemonic          | Description                                                                                                                                                                        |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INT               | Processor Interrupt (Active Low). This pin requires an external pull-up resistor. If this pin is not used, it can be left floating.                                                |

| 2       | PGOOD             | Power-Good Signal Output. This open-drain output is the power-good signal for the selected channels.                                                                               |

| 3       | THR               | Battery Pack Thermistor Connection.                                                                                                                                                |

| 4       | BSNS              | Battery Voltage Sense Pin.                                                                                                                                                         |

| 5       | ISOB              | Battery Supply Side Input to Internal Isolation FET/Battery Current Regulation FET.                                                                                                |

| 6       | ISOS              | Charger Supply Side Input to Internal Isolation FET/Battery Current Regulation FET.                                                                                                |

| 7       | AGND              | Analog Ground.                                                                                                                                                                     |

| 8       | CFL1              | Power input to the charger regulator. Connect a ceramic filter capacitor between this pin and either PGND1A or PGND1B.                                                             |

| 9, 10   | PGND1A,<br>PGND1B | Power Ground for the Battery Charger.                                                                                                                                              |

| 11, 12  | SW1A, SW1B        | Switching Node for the Battery Charger.                                                                                                                                            |

| 13, 14  | VBUSA, VBUSB      | Power Connection to USB Bus Voltage.                                                                                                                                               |

| 15      | SW4               | Switching Node for the Boost Regulator.                                                                                                                                            |

| 16      | PGND4             | Power Ground for the Boost Regulator.                                                                                                                                              |

| 17      | VOUT4             | Power Output for the Boost Regulator.                                                                                                                                              |

| 18      | FB4               | Feedback Sensing Input for the Boost Regulator. In standalone mode, connect this pin to a resistor divider from V <sub>VOUT4</sub> . In LED operation mode, connect FB4 to ground. |

| 19      | VIN4              | Input Voltage for the Boost Regulator and LDO Control Block.                                                                                                                       |

| 20      | D1                | LED 1 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| 21      | D2                | LED 2 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| 22      | D3                | LED 3 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| 23      | D4                | LED 4 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| 24      | D5                | LED 5 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| 25      | VOUT3             | Power Output for LDO3.                                                                                                                                                             |

| 26      | CFL2              | Internal Regulator Output for the Fuel Gauge. Connect a ceramic capacitor between this pin and AGND.                                                                               |

| 27      | VIN123            | Power Input for LDO1, LDO2, and LDO3.                                                                                                                                              |

| 28      | VOUT2             | Power Output for LDO2.                                                                                                                                                             |

| 29      | VOUT1             | Power Output for LDO1.                                                                                                                                                             |

| 30      | SCL               | I <sup>2</sup> C Serial Clock. This pin requires an external pull-up resistor.                                                                                                     |

| 31      | SDA               | I <sup>2</sup> C Serial Data. This pin requires an external pull-up resistor.                                                                                                      |

| 32      | ВАТОК             | Battery Status Open-Drain Output Flag (Active High). This pin enables the system when the battery reaches $V_{\text{WEAK}}$ .                                                      |

|         | EPAD              | Exposed Pad (Analog Ground). The exposed pad must be connected and soldered to an external ground plar                                                                             |

|   | 1     | 2    | 3                          | 4     | 5     | 6      | _         |

|---|-------|------|----------------------------|-------|-------|--------|-----------|

| A | VOUT3 | CFL2 | VIN123                     | VOUT2 | VOUT1 | PGOOD  |           |

| в | D4    | D5   | SDA                        | SCL   | BATOK | INT    |           |

| с | D2    | D3   | ADP5350                    |       | THR   | ISOB   |           |

| D | D1    | VIN4 | TOP VIEW<br>(Not to Scale) |       | BSNS  | ISOS   |           |

| E | VOUT4 | FB4  | VBUSA                      | AGND  | SW1A  | PGND1A |           |

| F | PGND4 | SW4  | VBUSB                      | CFL1  | SW1B  | PGND1B | 14797-105 |

Figure 5. WLCSP Pin Configuration (Top View)

### Table 10. WLCSP Pin Function Descriptions

| Pin No. | Mnemonic          | Description                                                                                                                                                                        |

|---------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B6      | INT               | Processor Interrupt (Active Low). This pin requires an external pull-up resistor. If this pin is not used, it can be left floating.                                                |

| A6      | PGOOD             | Power-Good Signal Output. This open-drain output is the power-good signal for the selected channels.                                                                               |

| C5      | THR               | Battery Pack Thermistor Connection.                                                                                                                                                |

| D5      | BSNS              | Battery Voltage Sense Pin.                                                                                                                                                         |

| C6      | ISOB              | Battery Supply Side Input to Internal Isolation FET/Battery Current Regulation FET.                                                                                                |

| D6      | ISOS              | Charger Supply Side Input to Internal Isolation FET/Battery Current Regulation FET.                                                                                                |

| E4      | AGND              | Analog Ground.                                                                                                                                                                     |

| F4      | CFL1              | Power input to the charger regulator. Connect a ceramic filter capacitor between this pin and either PGND1A or PGND1B.                                                             |

| E6, F6  | PGND1A,<br>PGND1B | Power Ground for the Battery Charger.                                                                                                                                              |

| E5, F5  | SW1A, SW1B        | Switching Node for the Battery Charger.                                                                                                                                            |

| E3, F3  | VBUSA, VBUSB      | Power Connection to USB Bus Voltage.                                                                                                                                               |

| F2      | SW4               | Switching Node for the Boost Regulator.                                                                                                                                            |

| F1      | PGND4             | Power Ground for the Boost Regulator.                                                                                                                                              |

| E1      | VOUT4             | Power Output for the Boost Regulator.                                                                                                                                              |

| E2      | FB4               | Feedback Sensing Input for the Boost Regulator. In standalone mode, connect this pin to a resistor divider from V <sub>VOUT4</sub> . In LED operation mode, connect FB4 to ground. |

| D2      | VIN4              | Input Voltage for the Boost Regulator and LDO Control Block.                                                                                                                       |

| D1      | D1                | LED 1 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| C1      | D2                | LED 2 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| C2      | D3                | LED 3 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| B1      | D4                | LED 4 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| B2      | D5                | LED 5 Sink Channel. Connect this pin to the cathode of the LED.                                                                                                                    |

| A1      | VOUT3             | Power Output for LDO3.                                                                                                                                                             |

| A2      | CFL2              | Internal Regulator Output for the Fuel Gauge. Connect a ceramic capacitor between this pin and AGND.                                                                               |

| A3      | VIN123            | Power Input for LDO1, LDO2, and LDO3.                                                                                                                                              |

| A4      | VOUT2             | Power Output for LDO2.                                                                                                                                                             |

| A5      | VOUT1             | Power Output for LDO1.                                                                                                                                                             |

| B4      | SCL               | I <sup>2</sup> C Serial Clock. This pin requires an external pull-up resistor.                                                                                                     |

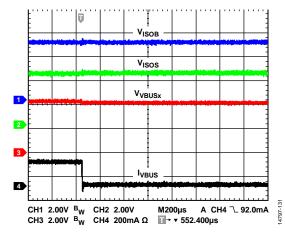

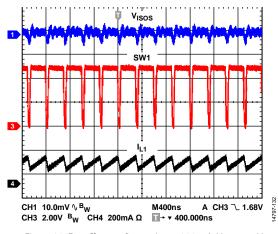

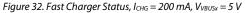

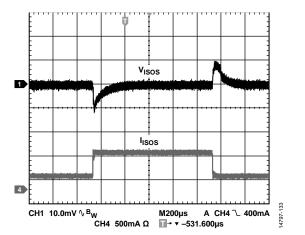

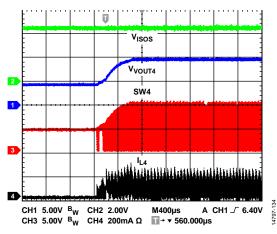

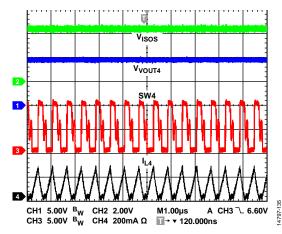

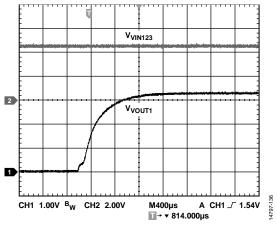

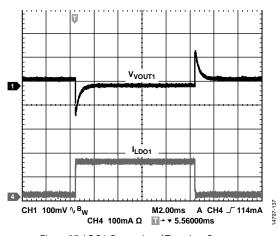

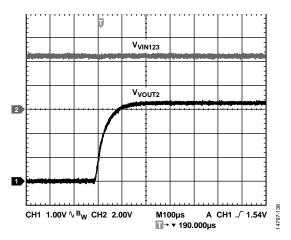

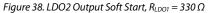

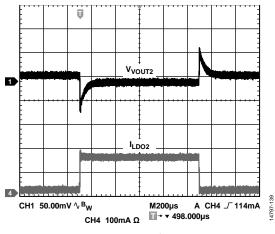

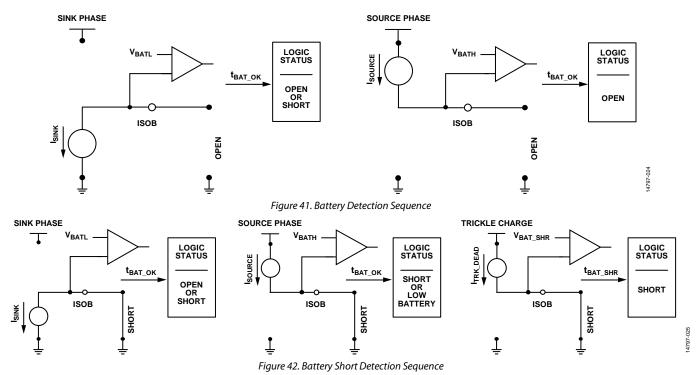

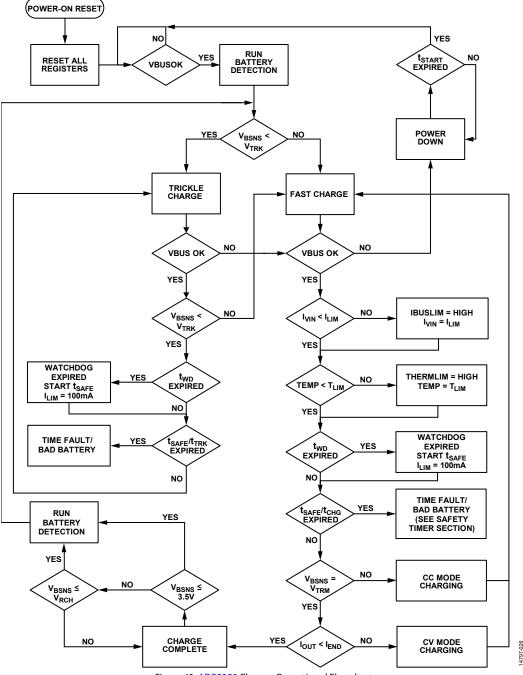

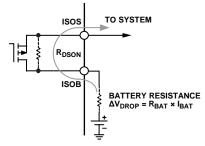

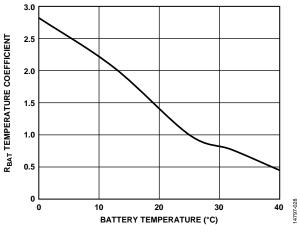

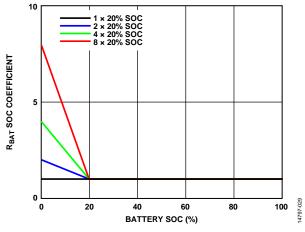

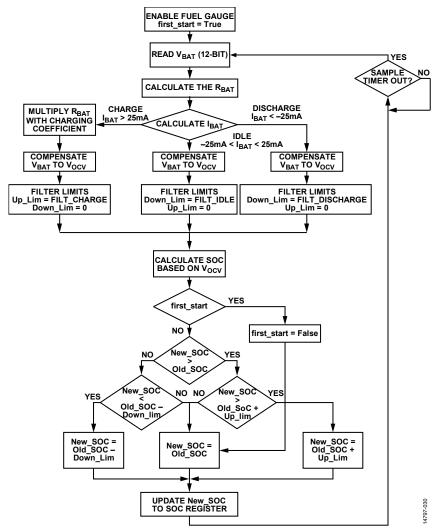

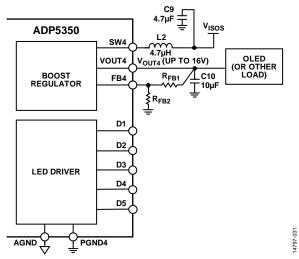

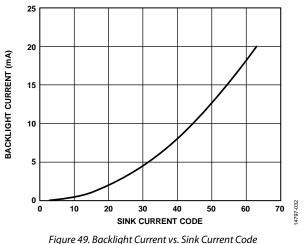

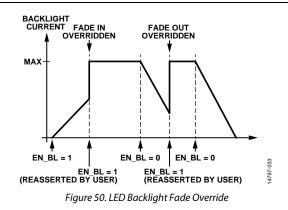

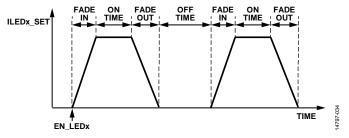

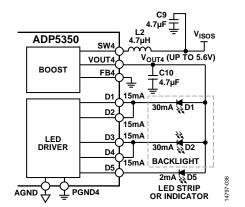

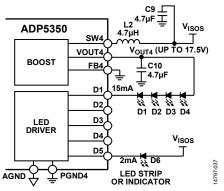

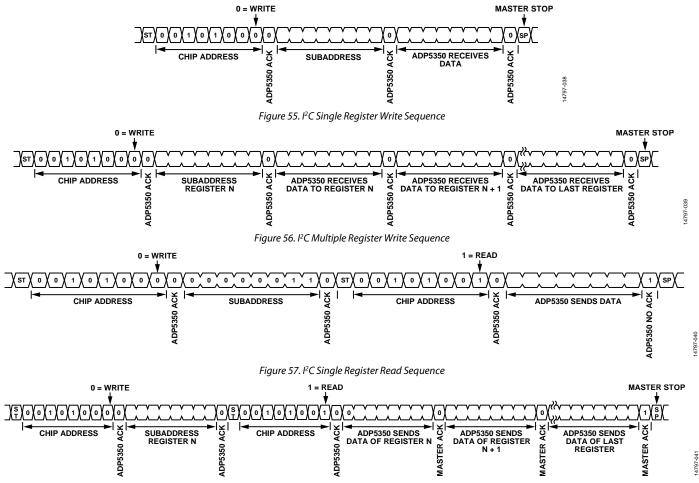

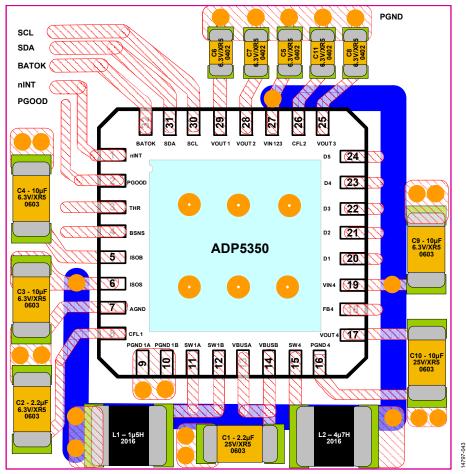

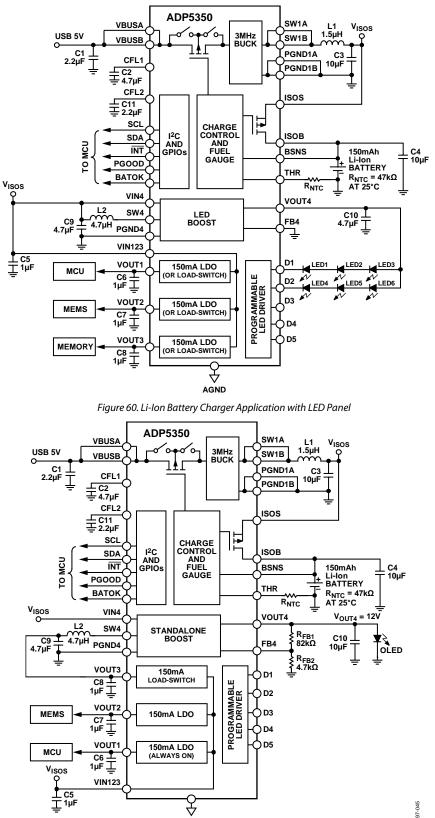

| B3      | SDA               | I <sup>2</sup> C Serial Data. This pin requires an external pull-up resistor.                                                                                                      |