Data brief

#### Class D automotive audio amplifier board with advanced diagnostics

#### **Features**

- With FDA903D class D automotive grade audio amp

- · Mono channel up to 45 W

- Supports audio stream via I<sup>2</sup>S interface

- Configurable through dedicated I<sup>2</sup>C bus

- · Dedicated DC diagnostic interrupt pin to signal faults

- · Dedicated hardware MUTE pin

- · Open load in play detection

- Short to Vcc / GND diagnostic

- Thermal protection

- Part of the AutoDevKit initiative

- RoHS compliant

#### **Description**

This evaluation board for the FDA903D 1  $\times$  45 W class D digital input automotive power amplifier, with load current monitoring and wide voltage operation range, is highly suitable for typical automotive audio, infotainment and telematic applications in conjunction with suitable automotive microcontrollers.

The amplifier can also be interfaced with the SPC582B Chorus automotive microcontroller and can also provide Electric Vehicle Warning Sounds (or Acoustic Vehicle Alerting Systems, AVAS) solutions.

The FDA903D amplifier comes in a PowerSSO-36 slug-down package and features a configurable power limiting function, high-speed I<sup>2</sup>C and legacy mode interfaces, and an internal finite state machine.

The initial state of the device is the standby state from which it will not be possible to exit until the I2C interface has been correctly enabled: this means providing correct supply voltage, the I2S clock, the I2S data and a valid combination of enable pins in order to determine the I2C device address.

This system is required by new vehicles to alert pedestrians of the presence of electric powered vehicles that are generating much less noise. Warning sounds may be driver triggered (like a horn) or automatic mimicking engine sounds. From 2021 according to government regulations, the vehicle must make a continuous noise level of at least 56 dBA (within 2 meters) if the car is going 20 km/h (12 mph) or slower, and a maximum of 75 dBA.

Each combination of the Enable pins represents an address. Up to eight devices can be used in the same application with a single I2C bus. The internal I2C registers are pre-set in "default condition", waiting for the I2C next instruction. The return in Standby condition, (i.e. all enable pins at 0), will result in a reset for the amplifier. As defined in the finite state machine, the same event will happen if PLL is not locked, I2S is missing or not correct, Vcc is removed for system reset. FDA903D works only in I2C slave mode.

The combination of AEK-AUD-D903V1 with AEK-MCU-C1MLIT1 hosting SPC582B Chorus automotive microcontroller offers a viable low-cost solution for entry-level AVAS systems.

|                               | Product summa                                                                                                                                       | ary                 |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SP                            | CU discovery board for<br>C5 Chorus 1M<br>omotive microcontroller                                                                                   | AEK-MCU-<br>C1MLIT1 |

|                               | toDevKit library plugin<br>SPC5-STUDIO                                                                                                              | STSW-<br>AutoDevKit |

| inp<br>am<br>mo<br>ope<br>aud | 45 W class D digital ut automotive power plifier with load current nitoring, wide voltage eration range for car dio and telematic - slug wn version | FDA903D             |

# 1 Block diagrams and schematic diagrams

# 1.1 Block diagrams

AutoDevkit

5V

12C SCL

12C SDA

12S SCL

12S SDA

12S SCL

12S SDA

12S CR

12S SDA

12S CR

12D SDA

Figure 1. Block diagram

DB4202 - Rev 1 page 2/5

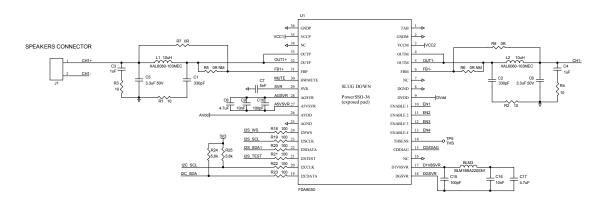

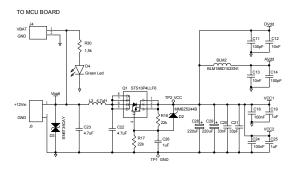

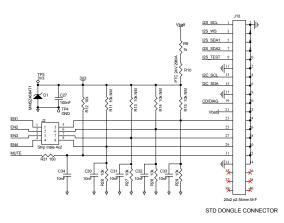

### 1.2 Schematic diagram

Figure 2. Schematic diagram

## **Revision history**

**Table 1. Document revision history**

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 24-Jun-2020 | 1       | Initial release. |

DB4202 - Rev 1 page 4/5