### HIGH FREQUENCY PRIMARY SIDE POWER SWITCHER FOR OFF-LINE SMPS

### **Description**

The AP3987CT is a high performance AC/DC power switcher for battery charger and adapter applications with a built-in high performance controller and a built-in 650V high performance MOSFET. It can meet less than 10mW standby power for "Super Star" charger criteria. The device uses Pulse Frequency Modulation (PFM) method to build Discontinuous Conduction Mode (DCM) Flyback power supplies.

The AP3987CT provides accurate Constant Voltage (CV), Constant Current (CC) and outstanding dynamic performance without requiring an opto-coupler. It also eliminates the need of loop compensation circuitry while maintaining stability.

The AP3987CT is equipped with built-in 0.35V output cable drop compensation.

The AP3987CT has internal over temperature protection, and also provides dedicated pin for external over temperature protection.

When the AP3987CT is used with AP4341 or APR3415CT series synchronous rectifier solution, better under-shoot performance and higher conversion efficiency can be achieved.

The AP3987CT provides operating frequency dithering function to improve system EMC performance.

The AP3987CT is packaged in SO-7.

### **Applications**

- Adapter/Chargers for Shaver, Cell/Cordless Phones, PDAs, MP3 and Other Portable Apparatus

- Standby and Auxiliary Power Supplies

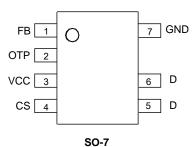

### **Pin Assignments**

#### (Top View)

#### **Features**

- Primary-Side Control for Eliminating Opto-Coupler

- 10mW No-Load Input Power

- Built-In 650V High Performance MOSFET

- Flyback Topology in DCM Operation

- Built-In 0.35V Cable Compensation for CV

- Multiple PWM/PFM Control Mode to Improve Audio Noise and Efficiency

- VCS Jitter to Reduce System EMI

- Valley-On for the Higher Efficiency and Better EMI

- Multiple Protections:

- Over Voltage Protection (OVP)

- Output Short Circuit Protection (SCP)

- Transformer Saturation Protection (TSP) via Primary Peak Current Limitation

- Internal and External Over Temperature Protection (OTP)

- Matching AP4341 with Schottky or APR3415CT Series Synchronous Rectifier Solution

- SO-7 Package

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

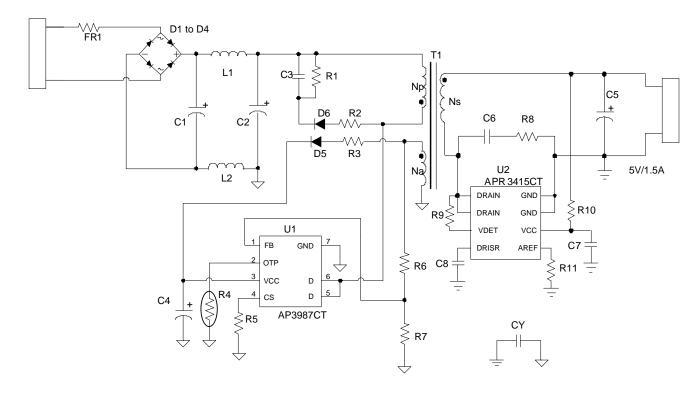

## **Typical Applications Circuit**

5V/1.5A Solution with AP3987CT+APR3415CT

# **Pin Descriptions**

| Pin Number | Pin Name | Function                                                    |

|------------|----------|-------------------------------------------------------------|

| 1          | FB       | The Voltage Feedback from Auxiliary Winding                 |

| 2          | OTP      | The External Over Temperature Protection                    |

| 3          | VCC      | Supply Voltage Pin                                          |

| 4          | CS       | Current Sense for Primary Side of Transformer               |

| 5, 6       | D        | This pin is connected with an internal power MOSFET's drain |

| 7          | GND      | This pin is the signal reference ground                     |

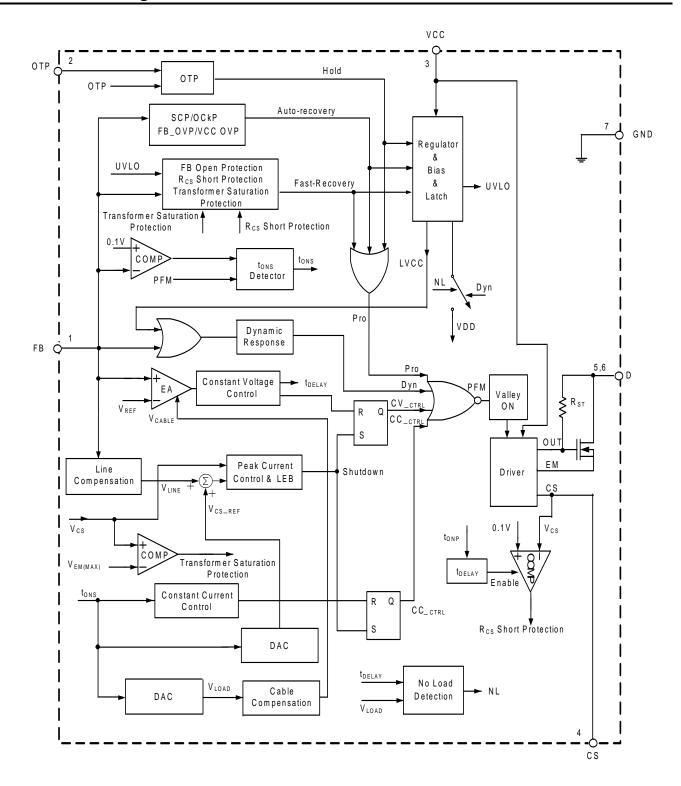

## **Functional Block Diagram**

### **Absolute Maximum Ratings** (Note 4)

| Symbol            | Parameter                                        | Rating       | Unit |

|-------------------|--------------------------------------------------|--------------|------|

| V <sub>CC</sub>   | Supply Voltage                                   | -0.3 to 28.5 | V    |

| Vcs               | Voltage on CS Pin                                | -0.3 to 7.4  | V    |

| V <sub>FB</sub>   | FB Input Voltage                                 | -0.7 to 7.4  | V    |

| BV <sub>DSS</sub> | Drain Voltage (T <sub>J</sub> =+25°C)            | 650          | V    |

| I <sub>D</sub>    | Drain Continuous Current (T <sub>J</sub> =+25°C) | 2            | А    |

| TJ                | Operating Junction Temperature                   | -40 to +150  | °C   |

| T <sub>STG</sub>  | Storage Temperature                              | -65 to +150  | °C   |

| T <sub>LEAD</sub> | Lead Temperature (Soldering, 10s)                | +260         | °C   |

| _                 | ESD (Charge Device Model)                        | 1000         | V    |

| _                 | ESD (Human Body Model)                           | 2000         | V    |

| $P_{D}$           | Total Power Dissipation                          | 1            | W    |

Note: 4. Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to *Absolute Maximum Ratings* for extended periods can affect device reliability.

## **Recommended Operating Conditions**

| Symbol          | Parameter                   | Min | Max | Unit |

|-----------------|-----------------------------|-----|-----|------|

| V <sub>CC</sub> | Supply Voltage              | _   | 25  | V    |

| T <sub>OP</sub> | Operating Temperature Range | -40 | +85 | °C   |

## Thermal Impedance (Note 5)

| Symbol        | Parameter           | Value | Unit |

|---------------|---------------------|-------|------|

| $\theta_{JA}$ | Junction to Ambient | 92    | °C/W |

Note: 5. Test condition: Device mounted on FR-4 substrate PC board, 2oz copper, with 1inch<sup>2</sup> cooling area.

## Electrical Characteristics (@V<sub>CC</sub>=15V, T<sub>J</sub>=+25°C, unless otherwise specified.) (Note 7)

| Symbol                            | Parameter                                                          | Condition                                                 | Min   | Тур   | Max      | Unit |

|-----------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------|-------|-------|----------|------|

| STARTUP AND                       | UVLO SECTION                                                       |                                                           |       |       |          |      |

| V <sub>TH_ST</sub>                | Turn-On Voltage                                                    | _                                                         | 11    | 13    | 15       | V    |

| V <sub>U</sub> VLO                | Turn-Off Voltage                                                   | _                                                         | 5.5   | 5.9   | 6.3      | V    |

|                                   | RRENT SECTION                                                      |                                                           |       |       | <u>I</u> |      |

| I <sub>ST</sub>                   | Turn-On Current                                                    | V <sub>CC</sub> =V <sub>TH_ST</sub> -1V before<br>Startup | 0.01  | 0.2   | 0.6      |      |

| ICC OPR                           | Operating Current                                                  | Static Current                                            | 400   | 550   | 700      | μΑ   |

| I <sub>CC_NL</sub>                | Standby Current                                                    | At No Load                                                | 5     | 17.5  | 30       |      |

|                                   | JITTER SECTION                                                     |                                                           | 1     |       | 1        |      |

| ΔV <sub>CS</sub> /V <sub>CS</sub> | V <sub>CS</sub> Modulation                                         |                                                           | 4.5   | 5     | 5.5      | %    |

| t <sub>MOD</sub>                  | V <sub>CS</sub> Modulation Period                                  | NL to Full Load                                           | 366   | 488   | 610      | μS   |

| CURRENT SEI                       | •                                                                  |                                                           | I.    | I     | I        | P**  |

| V <sub>CS_H</sub>                 | Peak Current Sense Voltage Reference in Heavy Load                 | 45% to 100% of Full<br>Load (Note 8)                      | 540   | 600   | 660      | mV   |

| V <sub>CS_L</sub>                 | Peak Current Sense Voltage Reference in Light Load                 | 0% to 8% Full Load<br>(Note 8)                            | 225   | 250   | 275      | mV   |

| RLINE                             | Built-In Line Compensation Resistance                              | @CP (Note 9)                                              | 108   | 120   | 132      | Ω    |

| t <sub>LEB</sub>                  | Leading Edge Blanking                                              | <b>  -</b>                                                | 300   | 550   | 800      | ns   |

|                                   | OLTAGE SECTION                                                     |                                                           | 1     |       | 1.0      | ·    |

| V <sub>FB</sub>                   | Feedback Threshold Voltage                                         | Tested @75% of Maximum I <sub>OUT</sub>                   | 2.505 | 2.556 | 2.607    | V    |

| V <sub>CABLE(MAX)</sub>           | Cable Compensation Voltage                                         | _                                                         | _     | 0.35  | _        | V    |

| CONSTANT C                        | URRENT SECTION                                                     | •                                                         | -     | •     | •        | •    |

| tons/tsw                          | Secondary Winding Conduction Duty                                  | Tested @V <sub>FB</sub> =2V                               | _     | 4/8   | _        | _    |

| VALLEY-ON S                       |                                                                    |                                                           | 1     |       | 11       | I.   |

| t <sub>VAL-ON</sub>               | Valid Off Time of Valley-On                                        | From the End of tons                                      | 20    | 27    | 34       | μS   |

| DYNAMIC SEC                       |                                                                    |                                                           |       |       |          |      |

| $V_{TRIGGER}$                     | Trigger Voltage for Dynamic Function                               | _                                                         | 40    | 62.5  | 85       | mV   |

| t <sub>DELAY</sub>                | Delay Time for Dynamic Function                                    | From the End of tons                                      | 95    | 122   | 150      | μS   |

| V <sub>UV_H</sub>                 | Under Voltage of FB Pin for V <sub>CS_H</sub>                      | _                                                         | 2.34  | 2.39  | 2.44     | V    |

| POWER MOSE                        |                                                                    |                                                           |       |       |          |      |

| $BV_{DSS}$                        | Drain-Source Breakdown Voltage (Note 6)                            | @CP Test                                                  | 650   | _     | _        | V    |

| R <sub>DS(ON)</sub>               | On State Resistance                                                | @CP Test                                                  | _     | 4     | _        | Ω    |

| DRIVER SECT                       | ION                                                                |                                                           |       |       |          |      |

| Isource                           | Peak Driver Source Current                                         | @CP Test                                                  | 18    | 22    | 26       | mA   |

| PROTECTION                        | FUNCTION SECTION                                                   |                                                           |       |       |          |      |

| V <sub>FB(OVP)</sub>              | Over Voltage Protection at FB Pin                                  | _                                                         | 3.5   | 3.75  | 4        | V    |

| V <sub>CC(OVP)</sub>              | Over Voltage Protection at VCC Pin                                 | _                                                         | 27    | 28.5  | 30       | V    |

| t <sub>ONP(MAX)</sub>             | Maximum Turn-On Time                                               | _                                                         | 14    | 18    | 22       | μS   |

|                                   | Minimum Peak Current Sense Voltage                                 |                                                           |       |       |          |      |

| $V_{CS(MIN)}$                     | at tonp(MAX)                                                       | _                                                         | 135   | 150   | 165      | mV   |

| $V_{\text{EM}(\text{MAX})}$       | Maximum EM Voltage for Transformer Saturation Protection (Note 10) | (Note 7)                                                  | 1.8   | 2     | 2.2      | V    |

| V <sub>FB(SCP)</sub>              | Short Circuit Protection                                           | V <sub>FB</sub> @ Hiccup                                  | 1.83  | 1.87  | 1.92     | V    |

| t <sub>SCP</sub>                  | Time under V <sub>FB(SCP)</sub>                                    | _                                                         | 32    | 51.5  | 71       | ms   |

| $V_{OTP}$                         | External OTP Shutdown Threshold                                    | _                                                         | 0.49  | 0.52  | 0.55     | V    |

| V <sub>OTP_REC</sub>              | External OTP Recovery Threshold                                    | _                                                         | 0.58  | 0.62  | 0.66     | V    |

| I <sub>OTP</sub>                  | External OTP Shutdown Current                                      | _                                                         | 94    | 102   | 110      | μA   |

| T <sub>OTP</sub>                  | Shutdown Temperature                                               | _                                                         | +135  | +145  | +155     | °C   |

| $T_{HYS}$                         | Temperature Hysteresis                                             | _                                                         | +37   | +40   | +43      | °C   |

Notes:

- 6. The drain-source voltage is 80% of BV<sub>DSS</sub> in the aging condition.

- 6. The drain-source voltage is out on by DSS in the aging contained.

7. These parameters are not 100% tested, guaranteed by design and characterization.

8. Peak current sense voltage reference without line compensation.  $V_{CS\_REF} = 0.35 \times \frac{R_{LINE}}{R_{FBI} + R_{LINE}} \times V_{AUX}$

- 9. Line compensation voltage on CS reference.

10. EM is an internal pin which is connected to the source of power MOSFET inside.

### **Operation Description**

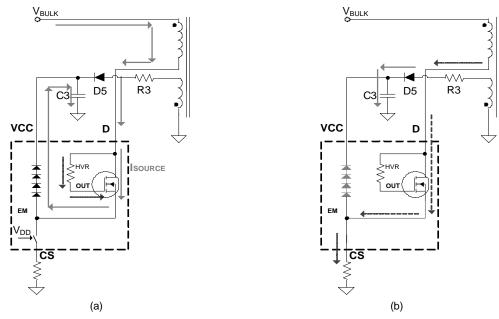

### 1. Start-Up Circuit

Figure 1. Startup Circuit

#### Figure 1 (a) shows the Startup Phase

- Before V<sub>CC</sub> reaches V<sub>TH(ST)</sub>, V<sub>DD</sub> is zero and EM (internal pin) to CS pin is open.

- C3 is charged by I<sub>SOURCE</sub>.

#### Figure 1 (b) shows the Normal Operation Phase

- When V<sub>CC</sub> reaches V<sub>TH(ST)</sub>, V<sub>DD</sub> is high and EM to CS pin is short.

- The voltage of EM is lower than 1V so that the four diodes in chip are open.

- C3 is supplied by auxiliary winding of transformer.

#### 2. Operation Mode

The typical application circuit of AP3987CT is a conventional Flyback converter with a 3-winding transformer---primary winding ( $N_P$ ), secondary winding ( $N_S$ ) and auxiliary winding ( $N_{AUX}$ ), as shown in typical application with APR3415CT. The auxiliary winding is used for providing VCC supply voltage for IC and sensing the output voltage feedback signal to FB pin.

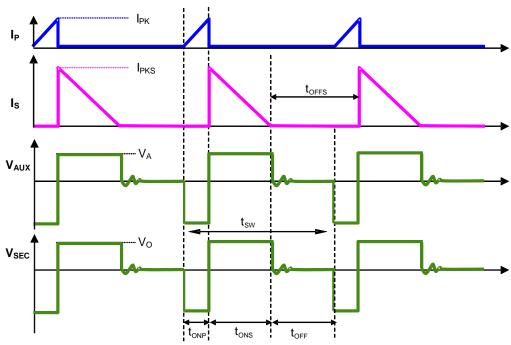

Figure 2 shows the typical waveforms which demonstrate the basic operating principle of AP3987CT application. And the parameters are defined as following.

- Ip---The primary-side current

- Is --- The secondary-side current

- IPK---Peak value of primary-side current

- IPKS---Peak value of secondary-side current

- Vsec---The transient voltage at secondary winding

- Vo---The output voltage

- V<sub>AUX</sub>---The transient voltage at auxiliary winding

- V<sub>A</sub>--- The stable voltage at auxiliary winding when rectification diode is in conducting status, which equals the sum of voltage V<sub>CC</sub> and the forward voltage drop of auxiliary diode

- tsw ---The period of switching frequency

- tonp --- The conduction time when primary-side switch is "ON"

- tons --- The conduction time when secondary-side switch is "ON"

- toff --- The dead time when neither primary-side switch nor secondary-side switch is "ON"

- toffs --- The time when secondary-side switch is "OFF"

Figure 2. The Operation Waveform of Flyback PSR System

### 3. Constant Voltage Operation

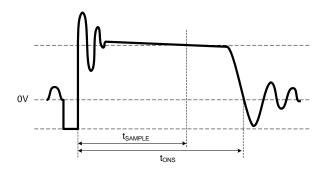

As to Constant Voltage (CV) operation mode, the AP3987CT detects the auxiliary winding voltage at FB pin to regulate the output voltage. The auxiliary winding voltage is coupled with secondary side winding voltage, so the auxiliary winding voltage during tons is:

$$V_{AUX} = \frac{N_{AUX}}{N_S} \times (V_{OUT} + V_D)$$

(1

Where V<sub>D</sub> is the conduction voltage drop of MOSFET in APR3415CT.

Figure 3. Auxiliary Voltage Waveform

The voltage detection point is at the t<sub>SAMPLE</sub> of t<sub>ONS</sub>. The voltage detection point is changed with the different primary peak current. The CV loop control function of AP3987CT then generates a t<sub>OFF</sub> to regulate the output voltage.

### 4. Constant Current Operation

The AP3987CT can work in Constant Current (CC) mode. Figure 2 shows the secondary current waveforms.

In CC operation mode, the CC control loop of AP3987CT will keep a fixed proportion between tons and toffs. The fixed proportion is

$$\frac{t_{ONS}}{t_{OFFS}} = \frac{4}{4} \tag{2}$$

The relationship between the output current and secondary peak current I<sub>PKS</sub> is given by:

$$I_{OUT} = \frac{1}{2} \times I_{PKS} \times \frac{t_{ONS}}{t_{ONS} + t_{OFFS}}$$

(3)

As to tight coupled primary and secondary winding, the secondary peak current is

$$I_{PKS} = \frac{N_P}{N_S} \times I_{PK} \tag{4}$$

Thus the output constant current is given by:

$$I_{\text{OUT}} = \frac{1}{2} \times \frac{N_{\text{P}}}{N_{\text{S}}} \times I_{\text{PK}} \times \frac{t_{\text{ONS}}}{t_{\text{ONS}} + t_{\text{OFFS}}} = \frac{2}{8} \times \frac{N_{\text{P}}}{N_{\text{S}}} \times I_{\text{PK}}$$

(5

Therefore, AP3987CT can realize CC mode operation by constant primary peak current and fixed secondary side conduction duty cycle.

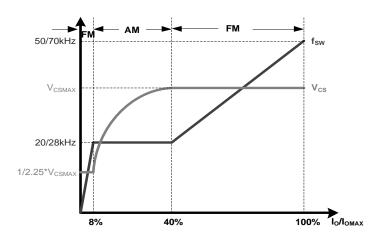

#### 5. Multiple Segment Peak Current

As to the original PFM PSR system, the switching frequency decreases with decreasing of output current, which will encounter audible noise issue since switching frequency decreases to audio frequency range, about less than 20kHz.

In order to avoid audible noise issue, AP3987CT uses 3-segment primary peak current control method at Constant Voltage (CV) mode, the current sense threshold voltages are multiple segments with different loading, as shown in Figure 4, which are V<sub>CS\_H</sub> for high load, varied V<sub>CS\_M</sub> for medium load and V<sub>CS\_L</sub> for light load. In no load and ultra light load condition (NL mode), the current reference is also V<sub>CS\_L</sub>. But the operation in NL mode is different, which will be described in next section.

At Constant Current (CC) mode, the peak current is still V<sub>CS\_H</sub> when V<sub>O</sub>>V<sub>FB(SCP)</sub>. If not, the peak current is 2/3\* V<sub>CS\_H</sub>.

It can be seen from the following figure that with multiple segment peak current control. The AP3987CT power system can keep switching frequency above 20kHz from light load to heavy load and guarantee the audible-noise-free performance, and the maximum load system switching frequency is not less than 50kHz, and no more than 70kHz.

Figure 4. Segment Peak Current and Operating Frequency at CV Mode

### 6. Operating Frequency

For primary-side regulation, the primary current ip(t) is sensed by a current sense resistor R<sub>CS</sub> (R4 as shown in Typical Applications). The current rises up linearly at a rate of:

$$\frac{\operatorname{dip}(t)}{\operatorname{dt}} = \frac{V_{\text{IN}}(t)}{L_{\text{M}}} \tag{6}$$

As illustrated in Figure 2, when the current ip(t) rises up to I<sub>PK</sub>, the switch Q1 turns off. The constant peak current is given by:

$$I_{PK} = \frac{V_{CS}}{R_{CS}} \tag{7}$$

The energy stored in the magnetizing inductance L<sub>M</sub> each cycle is therefore:

$$E_G = \frac{1}{2} \times L_M \cdot I_{PK}^2 \tag{8}$$

So the power transferring from the input to the output is given by:

$$P = \frac{1}{2} \times L_{M} \times I_{PK}^{2} \times f_{SW}$$

(9)

$$\eta \times \frac{1}{2} \times L_P \times I_{PK}^2 \times f_{SW} = P_O = V_O \times I_O$$

(10)

Where,  $f_{SW}$  is the switching frequency,  $\eta$  is the transferring efficiency.

In AP3987CT, the high load mode and light load mode adopt the Frequency Modulation (FM), and the middle load mode uses the Amplitude Modulation (AM).

During FM, the peak current IPK is constant, the output power depends on the switching frequency f<sub>SW</sub>.

During AM, the frequency is fixed, V<sub>CS\_M</sub> is varied. Below is the analysis of V<sub>CS\_M</sub>.

The square root equation can be got from the following equation:

$$\eta \times \frac{1}{2} \times L_{P} \times I_{PK}^{2} \times f_{SW} = \eta \times \frac{1}{2} \times L_{P} \times \left(\frac{V_{CS}}{R_{CS}}\right)^{2} \times f_{SW} = V_{O} \times I_{O}$$

(11)

So,

$$V_{CS} = \sqrt{\frac{2 \cdot R_{CS}^2 \cdot V_O \cdot I_O}{\eta \cdot L_p \cdot f_{SW}}}$$

(12)

During AM, the frequency is fixed, assume V<sub>O</sub> and η are constants, then

$$V_{CS} = k \cdot \sqrt{I_O} \quad (k = \sqrt{\frac{2 \cdot R_{CS}^2 \cdot V_O}{\eta \cdot L_p \cdot f_{SW}}})$$

(13)

#### 7. NL Mode Operation (Typical Application with APR3415CT)

At no load and ultra light load, the AP3987CT works at No Load mode (NL mode) and the output voltage is detected by APR3415CT. In order to achieve ultra low standby power at NL mode, the static current is reduced to I<sub>CC\_NL</sub>.

- The conditions of exiting NL mode---VCBC> VCBC(EN) or tOFF< tOFF(EX)

- The conditions of entering NL mode-- V<sub>CBC</sub>< V<sub>CBC(EN)</sub> and t<sub>OFF</sub>≥ t<sub>OFF(EN)</sub>

At NL mode, the internal reference voltage  $V_{DD}$  is pulled to ground. For normal NL working state, when the APR3415CT detects the output voltage is lower than its trigger voltage, the APR3415CT VDET pin emits a periodical pulse current. This pulse current will generate a pulse voltage on feedback winding through the transformer coupling. When the FB pin detects this pulse ( $>V_{TRIGGER}$  is valid), the AP3987CT reestablishes the  $V_{DD}$  and turns on primary switch to provide one energy pulse to supply output terminal and primary VCC voltage.

#### 8. Leading Edge Blanking

When the power switch is turned on, a turn-on spike will occur on the sense-resistor. To avoid false-termination of the switching pulse, a leading-edge blanking (from power MOSFET on) is built in. During this blanking period, the current sense comparator is disabled and the gate driver can't be switched off.

#### 9. Valley Turn-On

When the off time (t<sub>OFF</sub>) is lower than t<sub>VAL-ON</sub>, the AP3987CT power system can work with valley turn-on. It can reduce MOSFET switching on power losses which is resulted from the equivalent output capacitance to achieve highest overall efficiency. At the same time, because of valley turn-on the switching frequency has the random jitter feature, which will be benefit for conductive EMI performance. And valley turn-on can also reduce the power switch turn-on spike current and then achieve the better radiative EMI performance.

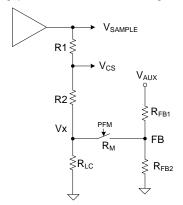

#### 10. Adjustable Line Compensation

Since there is a constant delay time from the CS pin voltage reaching the given V<sub>CS</sub> reference to the power switch turning off, the real primary peak current value always has a gap with the ideal value. The gap value changes with different input line voltage, which is caused by different current rising slope, and results in different system constant current value.

In order to eliminate the constant current deviation due to line voltage, the adjustable line compensation is introduced to the AP3987CT design. The negative voltage of FB pin which is linear to the line voltage is added up to V<sub>CS</sub> reference by a certain proportion and creates an adjustable compensation voltage to clear up the primary current gap, so that the excellent line regulation of output current will be achieved.

Figure 5. Adjustable Line Compensation Circuit

$$\Delta V_{CS} = -\frac{R_1}{R_1 + R_2} \cdot \frac{N_{AUX}}{N_P} \cdot \frac{R_{LC}}{R_{LC} + R_M + R_{FB1}} \cdot V_{LINE} \quad ......(14)$$

So, the AP3987CT can change the line compensation capability by adjusting the upper resistor at FB pin (R<sub>FB1</sub>). Higher resistance means lower line compensation capability.

#### 11. Protection

The AP3987CT has various built-in single point fault protection features: FB over voltage protection, VCC over voltage protection, output short circuit protection, FB open circuit protection, transformer saturation protection and current sense resistor fault (short or open) protection, over temperature protection. The fault conditions to trigger these protections are different and protection modes to enter are different after the protections are triggered.

#### 11.1 Protection Mode

The AP3987CT has three protection modes: auto-recovery, fast-recovery and hold. The operation principles are different.

When VCC over voltage protection, FB over voltage protection, output short circuit protection are activated, the AP3987CT enters the autorecovery mode. Once the AP3987CT enters the autorecovery mode, the device shuts down immediately and doesn't signal any pulse, the VCC static current is decreased from operating current  $I_{CC\_OPR}$  to standby current  $I_{CC\_NL}$ . Until VCC voltage drops to  $V_{OPR(MIN)}$ , the AP3987CT will enter the restart process, and VCC voltage changes between  $V_{TH(ST)}$  and  $V_{OPR(MIN)}$  until the fault condition is removed. The slope of VCC voltage to discharge is very small, and the time to drop to  $V_{OPR(MIN)}$  is very long. It can decrease the average power dissipation at a fault condition.

When FB open circuit protection, transformer saturation protection and current sense resistor fault (short or open) protection are triggered the device enters the fast recovery mode. The only difference with auto recovery is that the VCC discharge current is kept operating current I<sub>CC\_OPR</sub> and the system can fast restart.

When internal or external over temperature protection is activated, the device enters the hold mode. Once the hold mode is triggered, the AP3987CT doesn't signal any pulse until the fault condition is removed, and VCC Voltage is hold not lower than LVCC voltage.

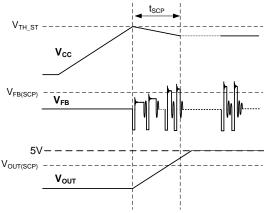

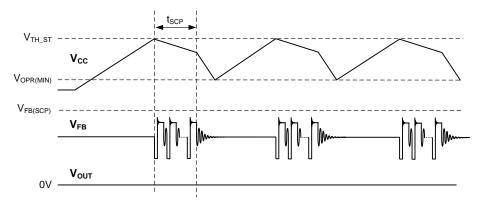

#### 11.2 Short Circuit Protection (SCP)

The Short Circuit Protection (SCP) detection principle is similar to the normal output voltage feedback detection by sensing FB pin voltage. When the detected FB pin voltage is below  $V_{FB(SCP)}$  for a duration of about  $t_{SCP}$ , the SCP is triggered. Then the AP3987CT enters hiccup mode that the IC immediately shuts down and then restarts, so that the VCC voltage changes between  $V_{TH\_ST}$  and UVLO threshold until  $V_{FB(SCP)}$  condition is removed.

As to the normal system startup, the time duration of FB pin voltage below V<sub>FB(SCP)</sub> should be less than t<sub>SCP</sub> to avoid entering SCP mode. But for the output short condition or the output voltage below a certain level, the SCP mode should happen.

Figure 6 is the AP3987CT normal start-up waveform that the voltage of FB pin is above  $V_{FB(SCP)}$  during  $t_{SCP}$  after  $V_{CC}$  gets to the  $V_{TH\_ST}$ , which doesn't enter the SCP mode. As shown in Figure 7,  $V_{OUT}$  is short and the voltage of FB pin is lower than  $V_{FB(SCP)}$  during  $t_{SCP}$ , the AP3987CT triggers the SCP and enters hiccup mode.

Figure 6. Normal Start-up

Figure 7. Short Circuit Protection (SCP) and Hiccup Mode

### 11.3 Transformer Saturation Protection via Primary Peak Current Limitation

When the transformer saturation happens, the voltage of EM pin (internal pin) will increase promptly and be over the reference voltage V<sub>EM(MAX)</sub>. If two consecutive pulses exceed the value, the device shuts down and enters into auto-recovery mode.

### 11.4 Internal Over Temperature Protection (Internal OTP)

If the IC junction temperature exceeds the threshold  $T_{OTP}$ , the AP3987CT shuts down immediately and enters the hold mode. If the junction temperature decreases by hysteresis temperature  $T_{HYS}$ , the AP3987CT can recover to normal operation. If not, the power system keeps the hold mode.

#### 11.5 External Over Temperature Protection (External OTP)

The AP3987CT provides external Over Temperature Protection (OTP) by connecting a Negative Temperature Coefficient (NTC) resistor from OTP pin to GND. Internally, a current source  $I_{OTP}$  is injected to the OTP pin, which generates a voltage proportional to the NTC resistance. At high ambient temperature, the NTC resistance gets lower and results in the OTP pin voltage decreasing. If the OTP pin voltage drops below an internally-set threshold  $V_{OTP}$ , then the OTP is triggered, and the AP3987CT shuts down immediately and enters the fast auto recovery mode. The power system will keep fast auto recovery mode until the ambient temperature decreases and OTP pin voltage increases over the voltage  $V_{OTP}$  REC, which the AP3987CT can recover to normal operation.

If the OTP pin is not connected to the NTC resistor, the external OTP function will not work and the IC can still work normally with internal OTP.

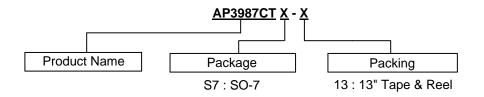

### **Ordering Information**

| Package | Temperature Range | Part Number   | Marking ID | 13"Tape and Reel   |                    |  |

|---------|-------------------|---------------|------------|--------------------|--------------------|--|

| Fackage | remperature Kange | rait Number   | Walking ID | Quantity           | Part Number Suffix |  |

| SO-7    | -40°C to +85°C    | AP3987CTS7-13 | AP3987CT   | 4000/Tape and Reel | -13                |  |

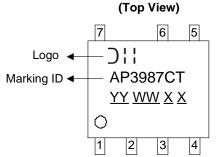

### **Marking Information**

YY: Year: 18,19, 20 ~

WW : Week : 01~52; 52

represents 52 and 53 week

$\underline{X} \underline{X}$ : Assembly Code

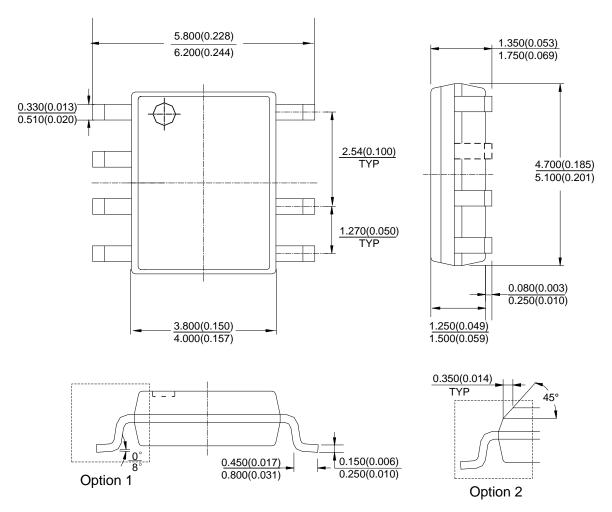

### Package Outline Dimensions (All dimensions in mm(inch).)

Please see http://www.diodes.com/package-outlines.html for the latest version.

### (1) Package Type: SO-7

Note: Eject hole, oriented hole and mold mark is optional.

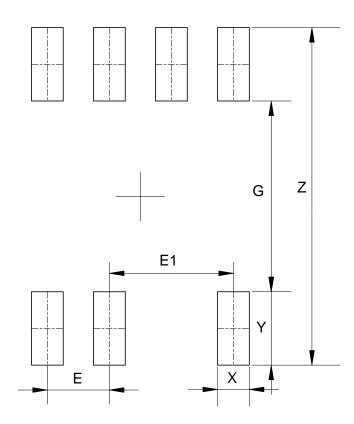

# Suggested Pad Layout

Please see http://www.diodes.com/package-outlines.html for the latest version.

(1) Package Type: SO-7

| Dimensions | Z           | G           | X           | Y           | E           | E1          |

|------------|-------------|-------------|-------------|-------------|-------------|-------------|

|            | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) | (mm)/(inch) |

| Value      | 6.900/0.272 | 3.900/0.154 | 0.650/0.026 | 1.500/0.059 | 1.270/0.050 | 2.540/0.100 |