### HIGH-PERFORMANCE USB PD CONTROLLER

### **Description**

The AP43770 is a USB Type-C power delivery controller dedicated to power source applications with legacy capability. It is compliant with USB Type-C specification release 1.3 and USB power delivery (PD) specification Rev3.0 V1.2.

The AP43770 can support PPS APDO with 20mV/step resolution and 50mA/step current resolution for power management. In addition, it supports Qualcomm Quick Charge 4 for mobile market. What's more, cable-loss compensation and SOP' command for e-Marker detection are embedded too.

In consideration of customer applications, the AP43770 supports options for non-PD protocols like BC 1.2, QC4/4+, QC3.0/QC2.0, and other legacy protocols with auto-detection. It maintains backwards compatibility with the existing environment. There are rich power-features embedded on the chip and they can be configured through CC channel.

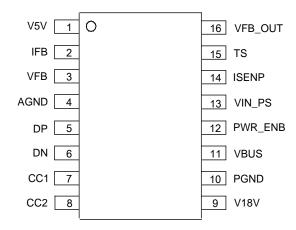

### **Pin Assignments**

### (Top View)

TSSOP-16

### **Features**

- Compliant with USB PD Rev3.0 V1.2

- USB-IF PD3.0/PPS Certificated TID = 1090017

- Qualcomm QC4 and QC4+,QC3.0, QC2.0 Built-in

- Support V<sub>OUT</sub> 20mV/Step from 3.3V to 20V

- Support Current Limit 50mA/Step up to 6A

- OTP(One-Time-Programmable) for Main Firmware

- MTP (Multi-Time-Programmable ) for System Configuration

- USB PD Transceiver with High Noise Immunity

- Built-In CC/CV Controller

- Support e-Marker Cable Detection

- Built-In V<sub>CONN</sub> Switch with OCP Protection

- Cable Compensation for Different Load Condition

- Programmable for Configuration through CC Line

- Support OCP/SCP/OTP/UVP with Auto-Restart

- Built-In 5V/1.8V LDO

- Low Standby Current: 550µA

- Maximum 32V Input Voltage Rating

- Support Non-USB PD Protocol Options

- BC 1.2 Legacy Built-In

- TID(11090017) for USB PD 3.0 PPS Compliance Test

- Package: TSSOP-16

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

## **Applications**

- AC Adapters

- Car Chargers

- USB PD Converter

- Power Hubs

- Power Banks

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

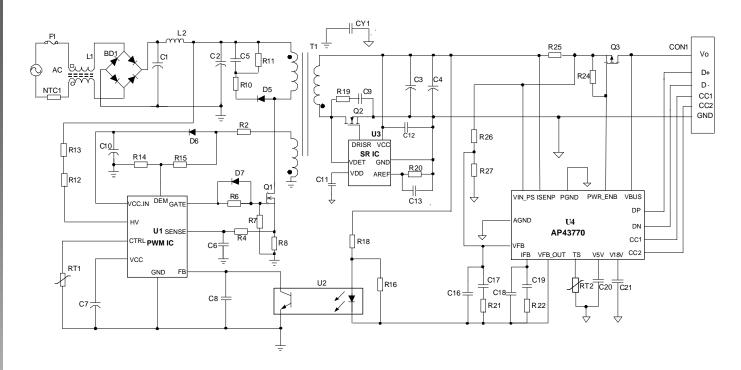

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Number | Pin Name | Description                                                                                             |

|------------|----------|---------------------------------------------------------------------------------------------------------|

| 1          | V5V      | LDO5V Output, 10µF to GND                                                                               |

| 2          | IFB      | CC Input. Negative Node of CC OPAM for Photocoupler                                                     |

| 3          | VFB      | CV Input. Negative Node of CV OPAM for Photocoupler                                                     |

| 4          | AGND     | Ground                                                                                                  |

| 5          | DP       | USB D+ Input                                                                                            |

| 6          | DN       | USB D- Input                                                                                            |

| 7          | CC1      | Type-C_CC1                                                                                              |

| 8          | CC2      | Type-C_CC2                                                                                              |

| 9          | V18V     | LDO1.8V Output, 0.1µF to GND                                                                            |

| 10         | PGND     | Ground                                                                                                  |

| 11         | VBUS     | VBUS Terminal for Discharge Path                                                                        |

| 12         | PWR_ENB  | External PMOS Gate Driver. To Control External MOS Switch: 0: To Enable VBUS Voltage 1: Disconnect VBUS |

| 13         | VIN_PS   | High Voltage Power Input (V <sub>MAX</sub> = 32V)                                                       |

| 14         | ISENP    | Input Current Sense Positive Node                                                                       |

| 15         | TS       | Source Current (100µA) to External NTC Sensor for External OTP (Over Temperature Protection)            |

| 16         | VFB_OUT  | CC / CV Output. Open-Drain Output for Photocoupler (For Example, TL431)                                 |

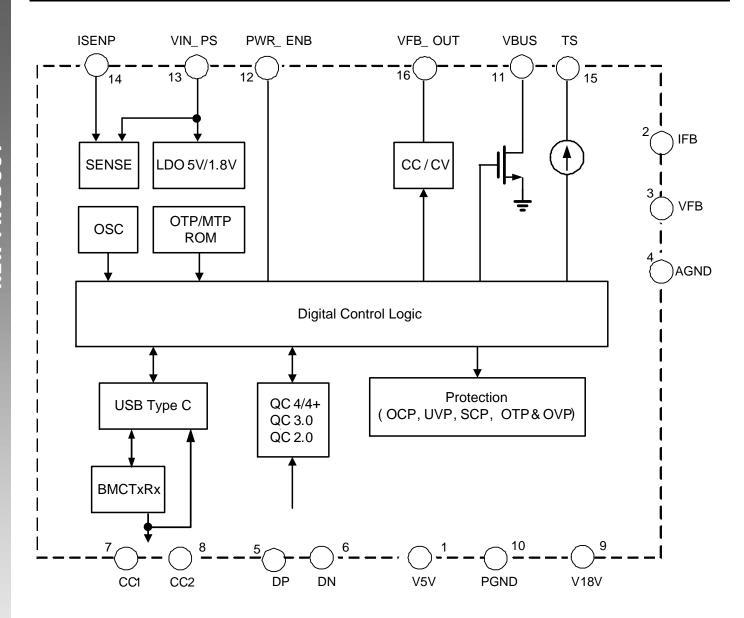

# **Functional Block Diagram**

## Absolute Maximum Ratings (@T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 4)

| Parameter                                                                                             | Rating      | Unit |

|-------------------------------------------------------------------------------------------------------|-------------|------|

| VIN_PS, VBUS, ISENP, PWR_ENB, VFB_OUT, TS Voltage                                                     | -0.3 to 32  | V    |

| V5V, IFB, VFB, DP, DN, CC1, CC2 Voltage                                                               | -0.3 to 7   | V    |

| V18V Voltage                                                                                          | -0.3 to 3.6 | V    |

| ESD (Human Body Model) Voltage on DP, DN, CC1, CC2 Pins                                               | 4           | kV   |

| ESD (Human Body Model) Voltage on VIN_PS, VBUS, ISENP, PWR_ENB, VFB_OUT, TS, V5V, IFB, VFB, V18V Pins | 2           | kV   |

| Maximum Junction-to-Ambient Thermal Resistance                                                        | 113         | °C/W |

| Maximum Junction-to-Case Thermal Resistance                                                           | 34          | °C/W |

| Operating Junction Temperature Range                                                                  | -40 to +150 | °C   |

| Storage Temperature Range                                                                             | -40 to +150 | °C   |

Note:

4. Stresses greater than those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods can affect device reliability.

# Recommended Operating Conditions (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol          | Parameter                   | Min | Max | Unit |

|-----------------|-----------------------------|-----|-----|------|

| $V_{IN\_PS}$    | Power Supply Voltage        | 0   | 25  | V    |

| T <sub>OP</sub> | Operating Temperature Range | -40 | +85 | °C   |

# **Electrical Characteristics** (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Parameter                      | Test Conditions                            | Min | Тур  | Max | Unit                |

|--------------------------------|--------------------------------------------|-----|------|-----|---------------------|

| UVLO Voltage                   | V <sub>IN_PS</sub> Rising                  | _   | 2.8  | _   | V                   |

| UVLO Hysteresis Voltage        | V <sub>IN_PS</sub> Falling                 | _   | 2.7  | _   | V                   |

| V5V Voltage                    | V <sub>IN_PS</sub> = 6V                    | _   | 5    | _   | V                   |

| V5V Output Current Limit       | _                                          | _   | 70   | _   | mA                  |

| V18V Voltage                   | _                                          | _   | 1.8  | _   | V                   |

| VIN_PS Current in Sleep Mode   | CC1/2 Detach after 3s                      | _   | 550  | _   | μΑ                  |

| VIN_PS Current in Normal Mode  | V <sub>IN_PS</sub> = 5V                    | _   | 4.5  | _   | mA                  |

| Internal CLK in Normal Mode    | _                                          | _   | 12   | _   | MHz                 |

| V <sub>IN_PS_OVP</sub> Voltage | _                                          | 110 | 120  | 130 | %V <sub>IN_PS</sub> |

| V <sub>IN_PS_UVP</sub> Voltage | _                                          | _   | 75   | _   | %V <sub>IN_PS</sub> |

| I <sub>OCP</sub> Current       | I <sub>MAX</sub> = Setting Maximum Current | _   | 30   | _   | %I <sub>MAX</sub>   |

| OCP Deglitch Time              | _                                          | 90  | _    | 110 | ms                  |

| Internal OTP                   | _                                          | _   | +140 | _   | °C                  |

| External OTP Current           | _                                          | _   | 100  | _   | μA                  |

### **Performance Characteristics**

The AP43770 includes a USB Type-C power delivery controller, which meets USB Power Delivery specification Rev3.0 v1.1. Because of its high voltage process, the AP43770 provides a cost-effective solution without requiring external discrete high voltage components, such as LDO, TL431, CC/CV, pre-driver for external PMOS power switch, buck or boost converter, etc. Meanwhile, it can provide robust protection scheme with built-in OVP/OCP/SCP/OTP features. What's more, it supports on-chip multi-time-programmable (MTP) for maximum four times during the configuration and ID data programming.

In consideration of the quick charge protocol migrating in portable device, the AP43770 supports options for QC4/4+,QC3.0/2.0 and BC 1.2. All of these protocols can be turned on or off and identified automatically. It can be configured with practical applications of users.

#### System Power-On Sequence

When the external power source is provided, the AP43770 wakes up after the power-on reset (V\_RST ~ 2.8V), then the internal 5V\_LDO and 1.8V\_LDO are settled, and the USB PD controller and MCU would be initialized. All analog control blocks are ready and waiting for PD negotiation process. Meanwhile, the AP43770 monitors the voltage and current conditions to avoid abnormal conditions. Once any unacceptable conditions happen, the AP43770 goes into protection procedure according to the types of abnormal condition.

#### **Voltage Transition**

According to the USB PD's protocol, once the PD device requests different power profiles, the AP43770's power control block starts to change the voltage and current values. The AP43770 provides corresponding Over-Voltage Protection (OVP), Over-Current Protection (OCP) schemes, and maintains the feedback system stability to guarantee monotonic voltage transition and avoid violating the USB PD electrical specification.

The AP43770 provides zero-mismatch voltage methodology which is more flexible for system design requirements of customers. When UFP/DFP makes an acceptable power request deal, the AP43770 changes VFB voltage according to the USB PD command, which is around 1/10 of expected voltage. The voltage regulator control loop (AC/DC or DC/DC) regulates the required V<sub>BUS</sub> voltage according to V<sub>FB</sub> voltage. In addition, the shunt regulator is built in to minimize the total external components and the cost.

### **Protection**

The AP43770 supports OVP/UVP/OCP/SCP/OTP and Constant Current (CC) functions. All of the protection thresholds would depend on the requested power profile and provide the most reliable protection scheme.

The AP43770 provides the OVP feature by turning off the power switch when  $V_{VBUS}$  is 20% higher than the target voltage. Meanwhile, it provides internal discharge path to reduce the overvoltage duration, and terminates discharge current as soon as  $V_{VBUS}$  reaches the target voltage. To avoid the  $V_{VBUS}$  working abnormally, the AP43770 provides UVP function if the  $V_{VBUS}$  is below 75% of the target voltage.

To ensure the USB PD safe operation, the AP43770 supports programmable OCP function to make sure output current would not be higher than the allowed maximum current. Once unacceptable conditions happen, the AP43770 would shut down the USB PD system and send "Hard Reset" to the UFP device.

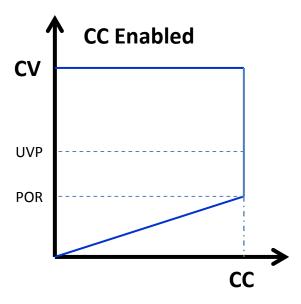

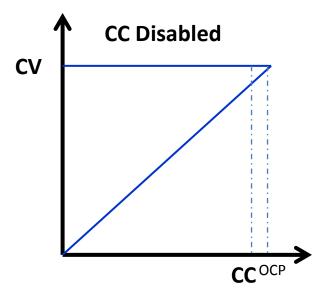

#### CV/CC

The AP43770 supports Constant Voltage (CV) and Constant Current (CC) functions. The functions can control the output voltage and current by the control pin VFB\_OUT and the feedback pins VFB and IFB. During the CV mode, the AP43770 operates in the fixed PDO, and the output voltage will be regulated to the request voltage if the output current is below the allowed maximum current. Once the sink device draws more than IoCP, overcurrent protection occurs. When the CC mode function is enabled, the output voltage drops, and the source current is limited within 150mA of the requested current whenever output current exceeds the allowed maximum current. When the output voltage drops below UVP, constant current limit turns off V<sub>BUS</sub> and starts error recovery procedure. The AP43770 will reset if the voltage continues dropping to power-on-reset (POR) threshold.

# **Performance Characteristics** (continued)

Figure 1 and Figure 2 show V/I profile of this CC/CV functions.

Figure 1. AP43770 V/I Profile When CC Enabled

Figure 2. AP43770 V/I Profile When CC Disabled

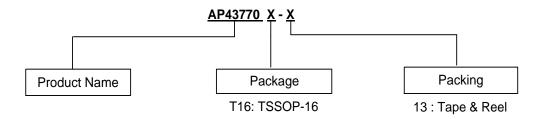

# **Ordering Information**

| Don't Neverland | Package  | Marking ID | 13" Tape and Reel  |                    |

|-----------------|----------|------------|--------------------|--------------------|

| Part Number     |          |            | Quantity           | Part Number Suffix |

| AP43770T16-13   | TSSOP-16 | AP43770    | 4000/Tape and Reel | -13                |

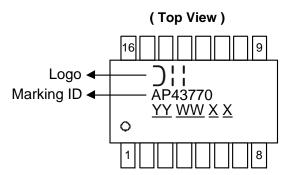

# **Marking Information**

### TSSOP-16

YY: Year: 18, 19, 20~ WW: Week: 01~52; 52 represents 52 and 53 week

$\underline{X} \underline{X}$ : Internal Code

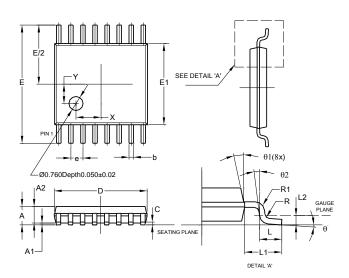

# Package Outline Dimensions (All dimensions in mm.)

Please see http://www.diodes.com/package-outlines.html for the latest version.

Package Type: TSSOP-16

| TSSOP-16             |          |      |       |

|----------------------|----------|------|-------|

| Dim                  | Min      | Max  | Тур   |

| Α                    | _        | 1.20 | _     |

| A1                   | 0.05     | 0.15 | _     |

| A2                   | 0.80     | 1.05 | _     |

| b                    | 0.19     | 0.30 | _     |

| C                    | 0.09     | 0.20 | _     |

| D                    | 4.90     | 5.10 | _     |

| Е                    | 6.40 BSC |      |       |

| E1                   | 4.30     | 4.50 | _     |

| е                    | 0.65 BSC |      |       |

| L                    | 0.45     | 0.75 | _     |

| L1                   | 1.00 REF |      |       |

| L2                   | 0.25 BSC |      |       |

| R / R1               | 0.09     | 1    | _     |

| X                    | -        | 1    | 1.350 |

| Υ                    |          | -    | 1.050 |

| θ                    | 0°       | 8°   |       |

| θ1                   | 5°       | 15°  | _     |

| θ2                   | 0°       | _    | _     |

| All Dimensions in mm |          |      |       |

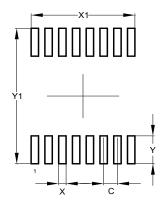

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

Package Type: TSSOP-16

| Dimensions | Value<br>(in mm) |

|------------|------------------|

| C          | 0.650            |

| X          | 0.350            |

| X1         | 4.900            |

| Y          | 1.400            |

| Y1         | 6.800            |