# onsemi

# AR0331 1/3-Inch 3.1 Mp/Full HD Digital Image Sensor

## AR0331

## **General Description**

The **onsemi** AR0331 is a 1/3-inch CMOS digital image sensor with an active-pixel array of 2048 (H) x 1536 (V). It captures images in either linear or high dynamic range modes, with a rolling-shutter readout. It includes sophisticated camera functions such as in-pixel binning, windowing and both video and single frame modes. It is designed for both low light and high dynamic range scene performance. It is programmable through a simple two-wire serial interface. The AR0331 produces extraordinarily clear, sharp digital pictures, and its ability to capture both continuous video and single frames makes it the perfect choice for a wide range of applications, including surveillance and HD video.

The **onsemi** AR0331 can be operated in its default mode or programmed for frame size, exposure, gain, and other parameters. The default mode output is a 1080p-resolution image at 60 frames per second (fps). In linear mode, it outputs 12-bit or 10-bit A-Law compressed raw data, using either the parallel or serial (HiSPi) output ports. In high dynamic range mode, it outputs 12-bit compressed data using parallel output. In HiSPi mode, 12- or 14-bit compressed, or 16-bit linearized data may be output. The device may be operated in video (master) mode or in single frame trigger mode.

FRAME\_VALID and LINE\_VALID signals are output on dedicated pins, along with a synchronized pixel clock in parallel mode.

The AR0331 includes additional features to allow application– specific tuning: windowing and offset, auto black level correction, and on–board temperature sensor. Optional register information and histogram statistic information can be embedded in the first and last 2 lines of the image frame.

The sensor is designed to operate in a wide temperature range  $(-30^{\circ}C \text{ to } +85^{\circ}C)$ .

## Features

- Superior Low-light Performance

- Latest 2.2 µm Pixel with onsemi A-Pix<sup>™</sup> Technology

- Full HD Support at 1080 P 60 fps for Superior Video Performance

- Linear or High Dynamic Range Capture

- 3.1 M (4:3) and 1080 P Full HD (16:9) Images

- Optional Adaptive Local Tone Mapping (ALTM)

- Interleaved T1/T2 Output

- Support for External Mechanical Shutter

- Support for External LED or Xenon Flash

- Slow-motion Video (VGA 120 fps)

- On-chip Phase-locked Loop (PLL) Oscillator

- Integrated Position-based Color and Lens Shading Correction

- Slave Mode for Precise Frame-rate Control

- Stereo/3D Camera Support

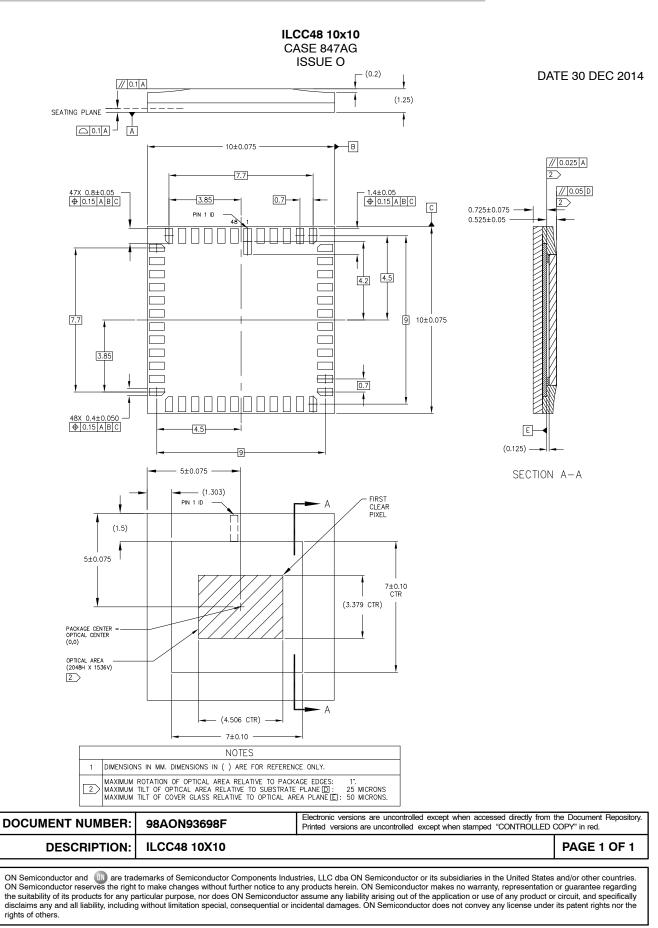

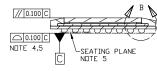

ILCC48 10x10 CASE 847AG IBGA52 9x9 CASE 503AA

#### ORDERING INFORMATION

See detailed ordering and shipping information on page 2 of this data sheet.

- Statistics Engine

- Data Interfaces: Four-lane Serial Highspeed Pixel Interface (HiSPi) Differential Signaling (SLVS and HiVCM), or Parallel

- Auto Black Level Calibration

- High-speed Context Switching

- Temperature Sensor

## Applications

- Video Surveillance

- Stereo Vision

- Smart Vision

- Automation

- Machine Vision

- 1080p60 Video Applications

- High Dynamic Range Imaging

## Table 1. KEY PARAMETERS

|                             | Parameter       | Typical Value                                                                                              |

|-----------------------------|-----------------|------------------------------------------------------------------------------------------------------------|

| Optical Format              |                 | 1/3-inch (5.8 mm)<br>Note: Sensor optical format will also work with lenses designed for<br>1/3.2" format. |

| Active Pixels               |                 | 2048 (H) x 1536 (V) (4:3, mode)                                                                            |

| Pixel Size                  |                 | 2.2 μm x 2.2 μm                                                                                            |

| Color Filter Array          |                 | RGB Bayer                                                                                                  |

| Shutter Type                |                 | Electronic rolling shutter and GRR                                                                         |

| Input Clock Range           |                 | 6 – 48 MHz                                                                                                 |

| Output Clock Maximu         | m               | 148.5 Mp/s (4-lane HiSPi)<br>74.25 Mp/s (Parallel)                                                         |

| Output                      | Serial          | HiSPi 10-, 12-, 14-, or 16-bit                                                                             |

|                             | Parallel        | 10–, 12–bit                                                                                                |

| Frame Rate                  | Full Resolution | 30 fps                                                                                                     |

|                             | 1080p           | 60 fps                                                                                                     |

| Responsivity                |                 | 1.9 V/lux-sec                                                                                              |

| SNR <sub>MAX</sub>          |                 | 39 dB                                                                                                      |

| Max Dynamic Range           |                 | Up to 100 dB                                                                                               |

| Supply Voltage              | I/O             | 1.8 or 2.8 V                                                                                               |

|                             | Digital         | 1.8 V                                                                                                      |

|                             | Analog          | 2.8 V                                                                                                      |

|                             | HiSPi           | 0.3 V–0.6 V, 1.7 V–1.9 V                                                                                   |

| Power Consumption (Typical) |                 | <780 mW                                                                                                    |

| Operating Temperatur        | e (Ambient)     | -30°C to +85° C                                                                                            |

| Package Options             |                 | 10 x 10 mm 48 pin iLCC<br>9.5 x 9.5 mm 63-pin iBGA                                                         |

## **ORDERING INFORMATION**

## Table 2. AVAILABLE PART NUMBERS

| Part Number                                   | Product Description          | Orderable Product Attribute Description                  |

|-----------------------------------------------|------------------------------|----------------------------------------------------------|

| AR0331SRSC00SHCA0-DRBR                        | 48-pin iLCC HiSPi, 0° CRA    | Dry Pack without Protective Film, Double Side BBAR Glass |

| AR0331SRSC00SHCAD3-GEVK                       | 48-pin iLCC HiSPi, 0° CRA    | Demo Kit 3                                               |

| AR0331SRSC00SHCAD-GEVK                        | 48-pin iLCC HiSPi, 0° CRA    | Demo Kit                                                 |

| AR0331SRSC00SHCAH-GEVB                        | 48-pin iLCC HiSPi, 0° CRA    | Demo Board                                               |

| AR0331SRSC00SUCA0-DPBR                        | 48-pin iLCC Parallel, 0° CRA | Dry Pack with Protective Film, Double Side BBAR Glass    |

| AR0331SRSC00SUCA0-DRBR                        | 48-pin iLCC Parallel, 0° CRA | Dry Pack without Protective Film, Double Side BBAR Glass |

| AR0331SRSC00SUCAD3-GEVK                       | 48-pin iLCC Parallel, 0° CRA | Demo Kit 3                                               |

| AR0331SRSC00SUCAD-GEVK                        | 48-pin iLCC Parallel, 0° CRA | Demo Kit                                                 |

| AR0331SRSC00SUCAH-GEVB                        | 48-pin iLCC Parallel, 0° CRA | Demo Board                                               |

| AR0331SRSC00XUEAD3-GEVK                       | 63-pin iBGA                  | Demo Kit 3                                               |

| AR0331SRSC00XUEAD-GEVK                        | 63-pin iBGA                  | Demo Kit                                                 |

| AR0331SRSC00XUEAH-GEVB 63-pin iBGA            |                              | Demo Board                                               |

| AR0331SRSC00XUEE0-BY-DRBR 63-pin iBGA, 0° CRA |                              | Dry Pack without Protective Film, Double Side BBAR Glass |

| AR0331SRSC00XUEE0–DPBR 63–pin iBGA, 0° CRA    |                              | Dry Pack with Protective Film, Double Side BBAR Glass    |

| AR0331SRSC00XUEE0-DRBR 63-pin iBGA, 0° CRA    |                              | Dry Pack without Protective Film, Double Side BBAR Glass |

| AR0331SRSC00XUEE0-DRBR1 63-pin iBGA, 0° CRA   |                              | Dry Pack without Protective Film, Double Side BBAR Glass |

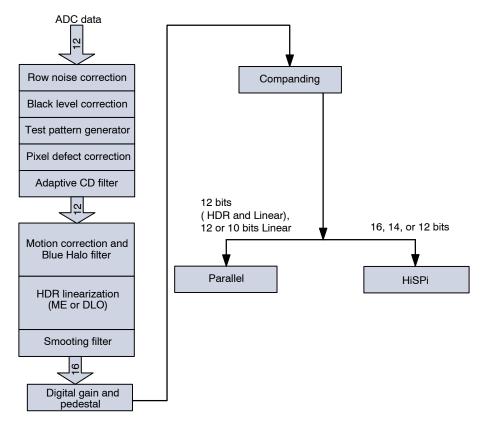

## FUNCTIONAL OVERVIEW

The AR0331 is a progressive–scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on–chip, phase–locked loop (PLL) that can be optionally enabled to generate all internal clocks from a single master input clock running between 6 and 48 MHz. The maximum output pixel rate is 148.5 Mp/s, corresponding to a clock rate of 74.25 MHz. Figure 1 shows a block diagram of the sensor.

Figure 1. Block Diagram

User interaction with the sensor is through the two-wire serial bus, which communicates with the array control, analog signal chain, and digital signal chain. The core of the sensor is a 3.1 Mp Active-pixel Sensor array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an analog-to-digital converter (ADC). The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and applies digital gain). The sensor also offers a high dynamic range mode of operation where multiple images are combined on-chip to produce a single image at 16-bit per pixel value. A compression mode is further offered to allow the 16-bit pixel value to be transmitted to the host system as a 12-bit value with close to zero loss in image quality.

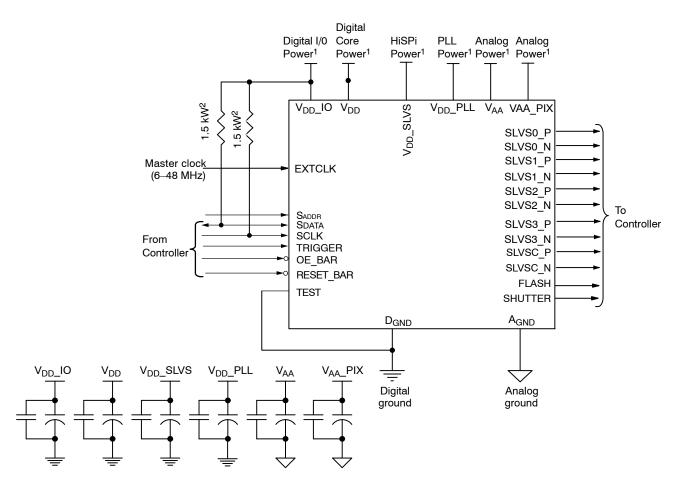

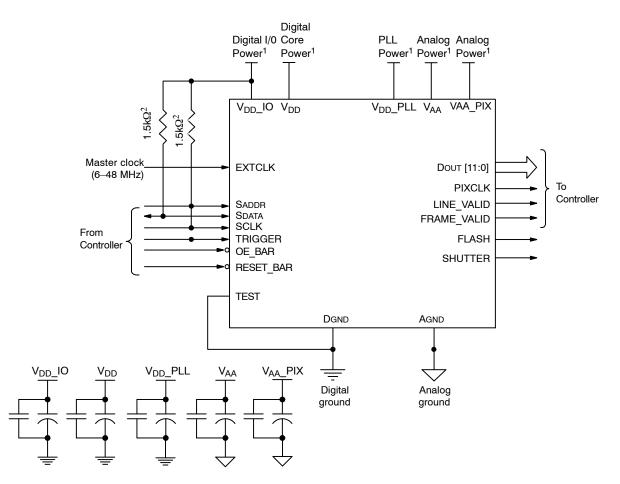

1. All power supplies should be adequately decoupled.

2. onsemi recommends a resistor value of 1.5 k $\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. The parallel interface output pads can be left unconnected if the serial output interface is used.

- onsemi recommends that 0.1 μF and 10 μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations.

- Refer to the AR0331 demo headboard schematics for circuit recommendations.5. **onsemi** recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. I/O signals voltage must be configured to match VDD\_IO voltage to minimize any leakage currents.

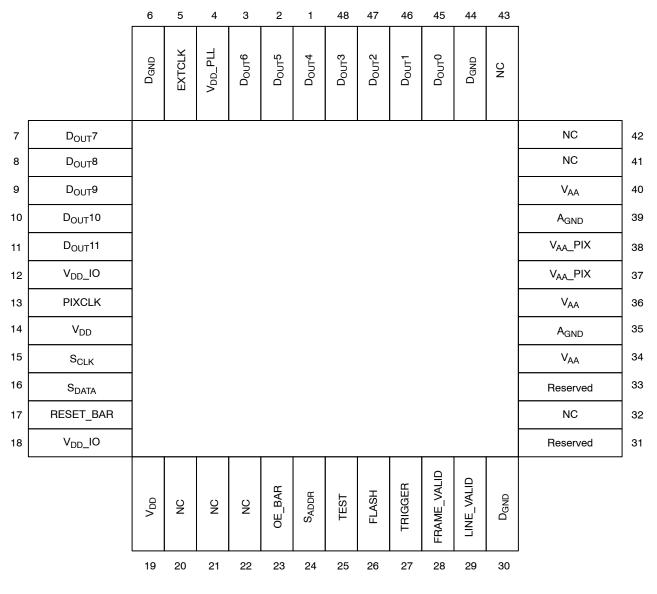

Figure 2. Typical Configuration: Serial Four-Lane HiSPi Interface

1. All power supplies should be adequately decoupled.

2. onsemi recommends a resistor value of 1.5 k $\Omega$ , but a greater value may be used for slower two-wire speed.

3. The serial interface output pads and VDDSLVS can be left unconnected if the parallel output interface is used.

- 4. onsemi recommends that 0.1 μF and 10 μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations. Refer to the AR0331 demo headboard schematics for circuit recommendations.

- 5. **onsemi** recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. I/O signals voltage must be configured to match VDD\_IO voltage to minimize any leakage currents.

7. The EXTCLK input is limited to 6–48 MHz.

Figure 3. Typical Configuration: Parallel Pixel Data Interface

## Table 3. PIN DESCRIPTION

| Pin<br>Number | Name                  | Туре   | Description                |

|---------------|-----------------------|--------|----------------------------|

| 1             | <b>D</b> ουτ4         | Output | Parallel Pixel Data Output |

| 2             | <b>D</b> ουτ5         | Output | Parallel Pixel Data Output |

| 3             | <b>D</b> ουτ6         | Output | Parallel Pixel Data Output |

| 4             | VDD_PLL               | Power  | PLL Power                  |

| 5             | EXTCLK                | Input  | External Input Clock       |

| 6             | Dgnd                  | Power  | Digital Ground             |

| 7             | <b>D</b> ουτ <b>7</b> | Output | Parallel Pixel Data Output |

| 8             | <b>D</b> ουτ <b>8</b> | Output | Parallel Pixel Data Output |

| 9             | <b>D</b> ουτ9         | Output | Parallel Pixel Data Output |

| 10            | Dout10                | Output | Parallel Pixel Data Output |

## Table 3. PIN DESCRIPTION (continued)

| Pin<br>Number | Name        | Туре   | Description                                                                                 |  |

|---------------|-------------|--------|---------------------------------------------------------------------------------------------|--|

| 11            | Dout11      | Output | Parallel Pixel Data Output (MSB)                                                            |  |

| 12            | Vdd_IO      | Power  | I/O Supply Power                                                                            |  |

| 13            | PIXCLK      | Output | Pixel Clock Out. Dout is Valid on Rising Edge of this Clock                                 |  |

| 14            | Vdd         | Power  | Digital Power                                                                               |  |

| 15            | Sclk        | Input  | Two-wire Serial Clock Input                                                                 |  |

| 16            | Sdata       | I/O    | Two-wire Serial Data I/O                                                                    |  |

| 17            | RESET_BAR   | Input  | Asynchronous Reset (Active LOW). All Settings are Restored to Factory Default               |  |

| 18            | VDD_IO      | Power  | I/O Supply Power                                                                            |  |

| 19            | Vdd         | Power  | Digital Power                                                                               |  |

| 20            | NC          |        |                                                                                             |  |

| 21            | NC          |        |                                                                                             |  |

| 22            | NC          |        |                                                                                             |  |

| 23            | OE_BAR      | Input  | Output Enable (Active LOW)                                                                  |  |

| 24            | SADDR       | Input  | Two-wire Serial Address Select. 0: 0x20. 1: 0x30                                            |  |

| 25            | TEST        | Input  | Manufacturing Test Enable Pin (Connect to DGND)                                             |  |

| 26            | FLASH       | Output | Flash Output Control                                                                        |  |

| 27            | TRIGGER     | Input  | Receives Slave Mode VD Signal for Frame Rate Synchronization and Trigg<br>Start a GRR Frame |  |

| 28            | FRAME_VALID | Output | Asserted when DOUT Frame Data is Valid                                                      |  |

| 29            | LINE_VALID  | Output | Asserted when DOUT Line Data is Valid.                                                      |  |

| 30            | Dgnd        | Power  | Digital Ground                                                                              |  |

| 31            | Reserved    |        |                                                                                             |  |

| 32            | SHUTTER     | Output | Control for External Mechanical Shutter. Can be Left Floating if not Used                   |  |

| 33            | Reserved    |        |                                                                                             |  |

| 34            | VAA         | Power  | Analog Power                                                                                |  |

| 35            | Agnd        | Power  | Analog Ground                                                                               |  |

| 36            | VAA         | Power  | Analog Power                                                                                |  |

| 37            | VAA_PIX     | Power  | Pixel Power                                                                                 |  |

| 38            | VAA_PIX     | Power  | Pixel Power                                                                                 |  |

| 39            | Agnd        | Power  | Analog Ground                                                                               |  |

| 40            | VAA         | Power  | Analog Power                                                                                |  |

| 41            | NC          |        |                                                                                             |  |

| 42            | NC          |        |                                                                                             |  |

| 43            | NC          |        |                                                                                             |  |

| 44            | Dgnd        | Power  | Digital Ground                                                                              |  |

| 45            | Dout0       | Output | Parallel Pixel Data Output (LSB)                                                            |  |

| 46            | Dout1       | Output | Parallel Pixel Data Output                                                                  |  |

| 47            | Dout2       | Output | tput Parallel Pixel Data Output                                                             |  |

| 48            | Dout3       | Output | Parallel Pixel Data Output                                                                  |  |

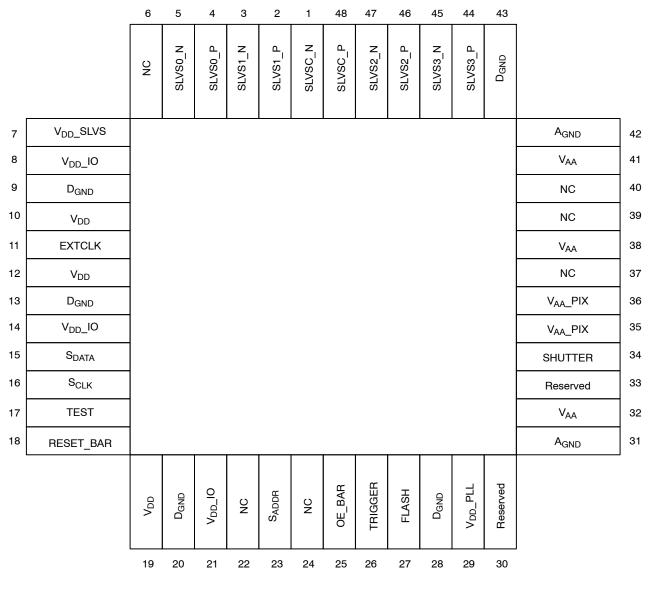

## Table 4. PIN DESCRIPTION, 48 ILCC

| Pin Number | Name     | Туре                                             | Description                                                                                                                           |  |

|------------|----------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | SLVSC_N  | Output                                           | HiSPi Serial DDR Clock Differential N                                                                                                 |  |

| 2          | SLVS1_P  | Output                                           | HiSPi Serial Data, Lane 1, Differential P                                                                                             |  |

| 3          | SLVS1_N  | Output                                           | HiSPi Serial Data, Lane 1, Differential N                                                                                             |  |

| 4          | SLVS0_P  | Output HiSPi Serial Data, Lane 0, Differential P |                                                                                                                                       |  |

| 5          | SLVS0_N  | Output                                           | HiSPi Serial Data, Lane 0, Differential N                                                                                             |  |

| 6          | NC       |                                                  |                                                                                                                                       |  |

| 7          | VDD_SLVS | Power                                            | 0.3 V–0.6 V or 1.7 V–1.9 V Port to HiSPi Output Driver. Set the High_VCM (R0x306E[9]) Bit to 1 when Configuring VDD_SLVS to 1.7–1.9 V |  |

| 8          | VDD_IO   | Power                                            | I/O Supply Power                                                                                                                      |  |

| 9          | Dgnd     | Power                                            | Digital Ground                                                                                                                        |  |

| 10         | Vdd      | Power                                            | Digital Power                                                                                                                         |  |

## Table 4. PIN DESCRIPTION, 48 ILCC (continued)

| Pin Number | Name      | Туре   | Description                                                                                   |

|------------|-----------|--------|-----------------------------------------------------------------------------------------------|

| 11         | EXTCLK    | Input  | External Input Clock                                                                          |

| 12         | Vdd       | Power  | Digital Power                                                                                 |

| 13         | Dgnd      |        | Digital Ground                                                                                |

| 14         | VDD_IO    | Power  | I/O Supply Power                                                                              |

| 15         | Sdata     | I/O    | Two-wire Serial Data I/O                                                                      |

| 16         | Sclk      | Input  | Two-wire Serial Clock Input                                                                   |

| 17         | TEST      |        | Manufacturing Test Enable Pin (Connect to DGND)                                               |

| 18         | RESET_BAR | Input  | Asynchronous Reset (Active LOW). All Settings are Restored to Factory Default                 |

| 19         | VDD       | Power  | Digital Power                                                                                 |

| 20         | Dgnd      | Power  | Digital Ground                                                                                |

| 21         | VDD_IO    | Power  | I/O Supply Power                                                                              |

| 22         | NC        |        |                                                                                               |

| 23         | SADDR     | Input  | Two-wire Serial Address Select. 0: 0x20. 1: 0x30                                              |

| 24         | NC        |        |                                                                                               |

| 25         | OE_BAR    |        | Output Enable (active LOW)                                                                    |

| 26         | TRIGGER   | Input  | Receives Slave Mode VD Signal for Frame Rate Synchronization and Trigger to Start a GRR Frame |

| 27         | FLASH     | Output | Flash Output Control                                                                          |

| 28         | Dgnd      | Power  |                                                                                               |

| 29         | VDD_PLL   | Power  | PLL Power                                                                                     |

| 30         | Reserved  |        |                                                                                               |

| 31         | Agnd      | Power  | Analog Ground                                                                                 |

| 32         | VAA       | Power  | Analog Power                                                                                  |

| 33         | Reserved  |        |                                                                                               |

| 34         | SHUTTER   | Output | Control for External Mechanical Shutter. Can be Left Floating if not Used                     |

| 35         | VAA_PIX   | Power  | Pixel Power                                                                                   |

| 36         | VAA_PIX   | Power  | Pixel Power                                                                                   |

| 37         | NC        |        |                                                                                               |

| 38         | VAA       | Power  | Analog Power                                                                                  |

| 39         | NC        |        |                                                                                               |

| 40         | NC        |        |                                                                                               |

| 41         | VAA       | Power  | Analog Power                                                                                  |

| 42         | Agnd      | Power  | Analog Ground                                                                                 |

| 43         | Dgnd      | Power  | Digital Ground                                                                                |

| 44         | SLVS3_P   | Output | HiSPi Serial Data, Lane 3, Differential P                                                     |

| 45         | SLVS3_N   | Output | HiSPi Serial Data, Lane 3, Differential N                                                     |

| 46         | SLVS2_P   | Output | HiSPi Serial Data, Lane 2, Differential P                                                     |

| 47         | SLVS2_N   | Output | HiSPi Serial Data, Lane 2, Differential N                                                     |

| 48         | SLVSC_P   | Output | HiSPi Serial DDR Clock Differential P                                                         |

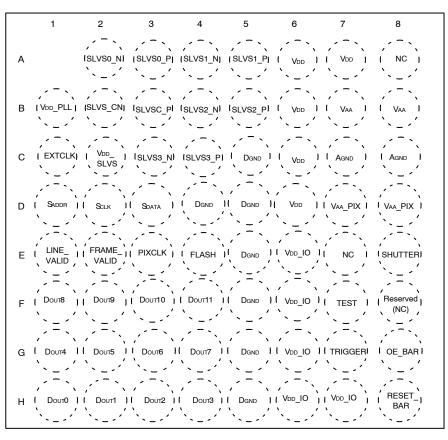

Top View (Ball Down)

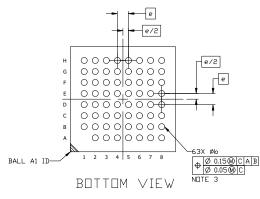

## Table 5. PIN DESCRIPTIONS, 9.5 x 9.5 mm, 63-BALL IBGA

| Name     | iBGA Pin                      | Туре   | Description                                                                                                                                 |

|----------|-------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| SLVS0_N  | A2                            | Output | HiSPi Serial Data, Lane 0, Differential N                                                                                                   |

| SLVS0_P  | A3                            | Output | HiSPi Serial Data, Lane 0, Differential P                                                                                                   |

| SLVS1_N  | A4                            | Output | HiSPi Serial Data, Lane 1, Differential N                                                                                                   |

| SLVS1_P  | A5                            | Output | HiSPi Serial Data, Lane 1, Differential P                                                                                                   |

| VDD_PLL  | B1                            | Power  | PLL power.                                                                                                                                  |

| SLVSC_N  | B2                            | Output | HiSPi Serial DDR Clock Differential N                                                                                                       |

| SLVSC_P  | B3                            | Output | HiSPi Serial DDR Clock Differential P                                                                                                       |

| SLVS2_N  | B4                            | Output | HiSPi Serial Data, Lane 2, Differential N                                                                                                   |

| SLVS2_P  | B5                            | Output | HiSPi Serial Data, Lane 2, Differential P                                                                                                   |

| VAA      | B7, B8                        | Power  | Analog Power                                                                                                                                |

| EXTCLK   | C1                            | Input  | External Input Clock.                                                                                                                       |

| VDD_SLVS | C2                            | Power  | 0.3 V-0.6 V or 1.7 V-1.9 V port to HiSPi Output Driver. Set the<br>High_VCM (R0x306E[9]) bit to 1 when configuring VDD_SLVS to<br>1.7-1.9 V |

| SLVS3_N  | C3                            | Output | HiSPi Serial Data, Lane 3, Differential N                                                                                                   |

| SLVS3_P  | C4                            | Output | HiSPi Serial Data, Lane 3, Differential P                                                                                                   |

| Dgnd     | C5, D4, D5, E5,<br>F5, G5, H5 | Power  | Digital Ground                                                                                                                              |

## Table 5. PIN DESCRIPTIONS, 9.5 x 9.5 mm, 63-BALL IBGA (continued)

| Name        | iBGA Pin           | Туре   | Description                                                                   |

|-------------|--------------------|--------|-------------------------------------------------------------------------------|

| Vdd         | A6, A7, B6, C6, D6 | Power  | Digital Power                                                                 |

| Agnd        | C7, C8             | Power  | Analog Ground                                                                 |

| SADDR       | D1                 | Input  | Two-wire Serial Address Select. 0: 0x20. 1: 0x30                              |

| Sclk        | D2                 | Input  | Two-wire Serial Clock Input                                                   |

| Sdata       | D3                 | I/O    | Two-Wire Serial Data I/O                                                      |

| VAA_PIX     | D7, D8             | Power  | Pixel Power                                                                   |

| LINE_VALID  | E1                 | Output | Asserted when DOUT Line Data is Valid                                         |

| FRAME_VALID | E2                 | Output | Asserted when DOUT Frame Data is Valid.                                       |

| PIXCLK      | E3                 | Output | Pixel Clock Out. DOUT is Valid on Rising Edge of this Clock.                  |

| VDD_IO      | E6, F6, G6, H6, H7 | Power  | I/O Supply Power                                                              |

| Dout8       | F1                 | Output | Parallel Pixel Data Output                                                    |

| Dout9       | F2                 | Output | Parallel Pixel Data Output                                                    |

| Dout10      | F3                 | Output | Parallel Pixel Data Output                                                    |

| Dout11      | F4                 | Output | Parallel Pixel Data Output (MSB)                                              |

| TEST        | F7                 | Input. | Manufacturing Test Enable Pin (Connect to DGND)                               |

| Dout4       | G1                 | Output | Parallel Pixel Data Output                                                    |

| Dout5       | G2                 | Output | Parallel Pixel Data Output                                                    |

| Dout6       | G3                 | Output | Parallel Pixel Data Output                                                    |

| Dout7       | G4                 | Output | Parallel Pixel Data Output                                                    |

| TRIGGER     | G7                 | Input  | Exposure Synchronization Input                                                |

| OE_BAR      | G8                 | Input  | Output Enable (Active LOW)                                                    |

| Dout0       | H1                 | Output | Parallel Pixel Data Output (LSB)                                              |

| Dout1       | H2                 | Output | Parallel Pixel Data Output                                                    |

| Dout2       | H3                 | Output | Parallel Pixel Data Output                                                    |

| Dout3       | H4                 | Output | Parallel Pixel Data Output                                                    |

| RESET_BAR   | H8                 | Input  | Asynchronous reset (active LOW). All settings are restored to factory default |

| SHUTTER     | E8                 | Output | Control for external mechanical shutter. Can be left floating if not used     |

| FLASH       | E4                 | Output | Flash Control Output                                                          |

| NC          | A8, E7             |        |                                                                               |

| Reserved    | F8                 |        |                                                                               |

## **PIXEL DATA FORMAT**

## **Pixel Array Structure**

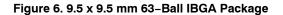

While the sensor's format is  $2048 \times 1536$ , additional active columns and active rows are included for use when horizontal or vertical mirrored readout is enabled, to allow

readout to start on the same pixel. The pixel adjustment is always performed for monochrome or color versions. The active area is surrounded with optically transparent dummy pixels to improve image uniformity within the active area. Not all dummy pixels or barrier pixels can be read out.

1. Maximum of 2048 columns is supported. Additional columns included for mirroring operations.

Figure 7. Pixel Array Description

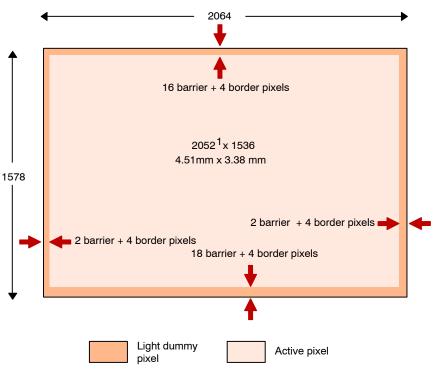

Figure 8. Pixel Color Pattern Detail (Top Right Corner)

## **Default Readout Order**

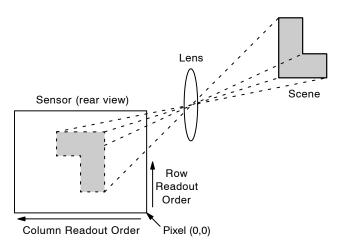

By convention, the sensor core pixel array is shown with pixel (0,0) in the top right corner (see Figure 8). This reflects the actual layout of the array on the die. Also, the first pixel data read out of the sensor in default condition is that of pixel (0, 0).

When the sensor is imaging, the active surface of the sensor faces the scene as shown in Figure 9. When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced as shown in Figure 9.

## Figure 9. Imaging a Scene

## **PIXEL OUTPUT INTERFACES**

## **Parallel Interface**

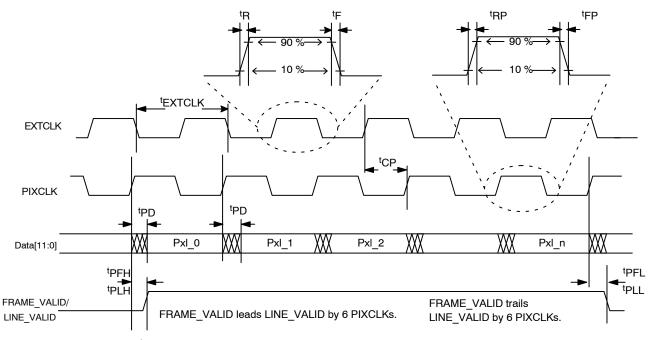

The parallel pixel data interface uses these output-only signals:

- FRAME\_VALID

- LINE\_VALID

- PIXCLK

- DOUT[11:0]

The parallel pixel data interface is disabled by default at power up and after reset. It can be enabled by programming R0x301A. Table 7 shows the recommended settings.

When the parallel pixel data interface is in use, the serial data output signals can be left unconnected. Set reset\_register [bit 12 (R0x301A[12] = 1)] to disable the serializer while in parallel output mode.

## Output Enable Control

When the parallel pixel data interface is enabled, its signals can be switched asynchronously between the driven and High–Z under pin or register control, as shown in Table 6.

## Table 6. OUTPUT ENABLE CONTROL

| OE_BAR Pin | Drive Pins R0x301A[6] | Description      |

|------------|-----------------------|------------------|

| 1          | 0                     | Interface High-Z |

| X          | 1                     | Interface Driven |

| 0          | X                     | Interface Driven |

Configuration of the Pixel Data Interface

Fields in R0x301A are used to configure the operation of the pixel data interface. The supported combinations are shown in Table 7.

| Table 7. CONFIGURATION OF THE FIXEL DATA INTERFACE |                 |            |  |  |

|----------------------------------------------------|-----------------|------------|--|--|

| Serializer Disable                                 | Parallel Enable |            |  |  |

| R0x301 A[12]                                       | R0x301 A[7]     | Descriptio |  |  |

TAKE & CONFIGURATION OF THE DIVEL DATA INTERFACE

| R0x301 A[12] | R0x301 A[7] | Description                                                                                                                                                                                                                             |

|--------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | 0           | Power up default<br>Serial pixel data interface and its clocks are enabled. Transitions to soft standby<br>are synchronized to the end of frames on the serial pixel data interface                                                     |

| 1            | 1           | Parallel pixel data interface, sensor core data output. Serial pixel data interface<br>and its clocks disabled to save power. Transitions to soft standby are<br>synchronized to the end of frames in the parallel pixel data interface |

## High Speed Serial Pixel Data Interface

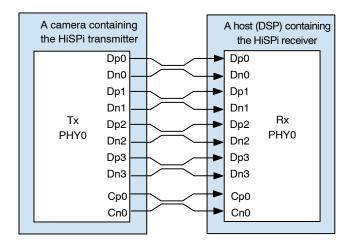

The High Speed Serial Pixel (HiSPi) interface uses four data lanes and one clock as output.

- SLVSC\_P

- SLVSC N

- SLVS0 P

- SLVS0 N

- SLVS1 P

- SLVS1 N

- SLVS2 P

- SLVS2 N

- SLVS3\_P

- SLVS3\_N

The HiSPi interface supports three protocols, Streaming–S, Streaming–SP, and Packetized SP. The streaming protocols conform to a standard video application where each line of active or intra–frame blanking provided by the sensor is transmitted at the same length. The Packetized SP protocol will transmit only the active data ignoring line-to-line and frame-to-frame blanking data.

These protocols are further described in the High–Speed Serial Pixel (HiSPi) Interface Protocol Specification V1.50.00.

The HiSPi interface building block is a unidirectional differential serial interface with four data and one double data rate (DDR) clock lanes. One clock for every four serial data lanes is provided for phase alignment across multiple lanes. Figure 10 shows the configuration between the HiSPi transmitter and the receiver.

The HiSPi interface building block is a unidirectional differential serial interface with four data and one double data rate (DDR) clock lanes. One clock for every four serial data lanes is provided for phase alignment across multiple lanes. Figure 10 shows the configuration between the HiSPi transmitter and the receiver.

Figure 10. HiSPi Transmitter and Receiver Interface Block Diagram

## HiSPi Physical Layer

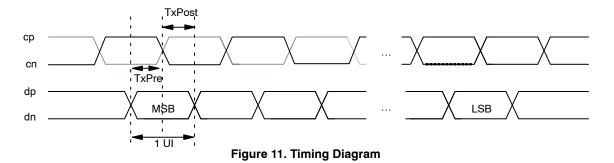

The HiSPi physical layer is partitioned into blocks of four data lanes and an associated clock lane. Any reference to the PHY in the remainder of this document is referring to this minimum building block.

The PHY will serialize 10–, 12–, 14–, or 16–bit data words and transmit each bit of data centered on a rising edge

of the clock, the second on the falling edge of the clock. Figure 11 shows bit transmission. In this example, the word is transmitted in order of MSB to LSB. The receiver latches data at the rising and falling edge of the clock.

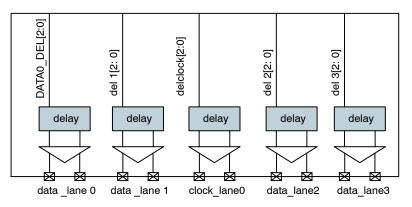

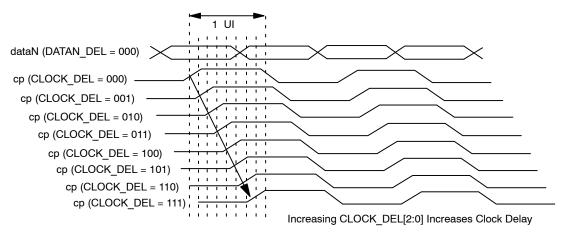

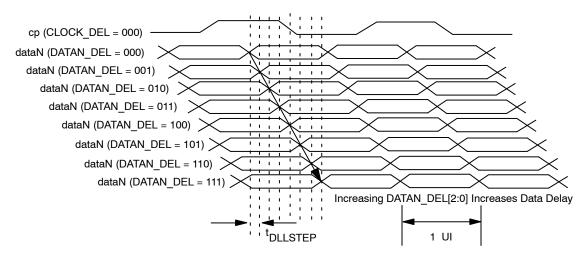

### **DLL Timing Adjustment**

The specification includes a DLL to compensate for differences in group delay for each data lane. The DLL is connected to the clock lane and each data lane, which acts as a control master for the output delay buffers. Once the DLL has gained phase lock, each lane can be delayed in 1/8 unit interval (UI) steps. This additional delay allows the user to increase the setup or hold time at the receiver circuits and can be used to compensate for skew introduced in PCB design.

Delay compensation may be set for clock and/or data lines in the hispi\_timing register R0x31C0. If the DLL timing adjustment is not required, the data and clock lane delay settings should be set to a default code of 0x000 to reduce jitter, skew, and power dissipation.

Figure 12. Block Diagram of DLL Timing Adjustment

Figure 13. Delaying the Clock with Respect to Data

Figure 14. Delaying Data with Respect to the Clock

## HiSPi Protocol Layer

The HiSPi protocol is described the HiSPi Protocol Specification document.

## **Serial Configuration**

The serial format should be configured using R0x31AC. Refer to the AR0331 Register Reference document for more detail regarding this register. The serial\_format register (R0x31AE) controls which serial format is in use when the serial interface is enabled (reset\_register[12] = 0). The following serial formats are supported:

- 0x0304 Sensor supports quad-lane HiSPi operation

- 0x0302 Sensor supports dual-lane HiSPi operation

- 0x0301 Sensor supports single-lane HiSPi operation

## PIXEL SENSITIVITY

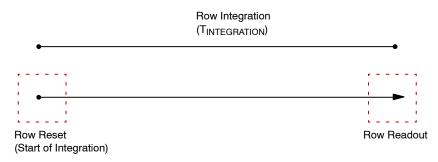

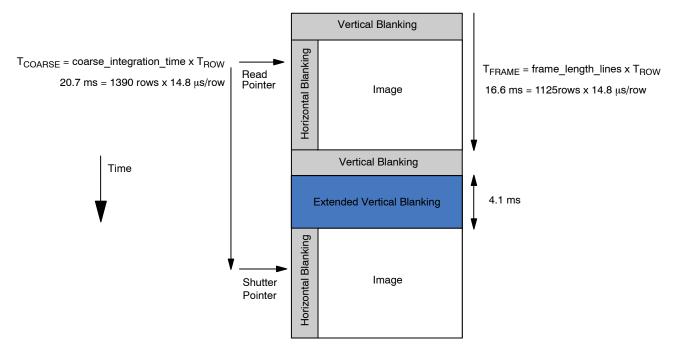

## Figure 15. Integration Control in ERS Readout

A pixel's integration time is defined by the number of clock periods between a row's reset and read operation. Both the read followed by the reset operations occur within a row period ( $T_{ROW}$ ) where the read and reset may be applied to different rows. The read and reset operations will be applied to the rows of the pixel array in a consecutive order.

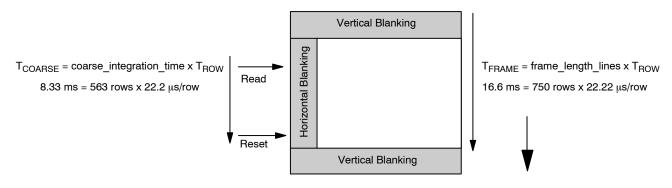

The coarse integration time is defined by the number of row periods ( $T_{ROW}$ ) between a row's reset and the row read. The row period is defined as the time between row read operations (see Sensor Frame Rate).

$$T_{COARSE} = T_{ROW} \times coarse_integration_time$$

(eq. 1)

Figure 16. Example of 8.33 ms Integration in 16.6 ms Frame

Figure 17. The Row Integration Time is Greater Than the Frame Readout Time

The minimum frame-time is defined by the number of row periods per frame and the row period. The sensor frame-time will increase if the coarse\_integration\_time is set to a value equal to or greater than the frame length lines. variable ADC reference. The sensor will apply the same analog gain to each color channel. Digital gain can be configured to separate levels for each color channel.

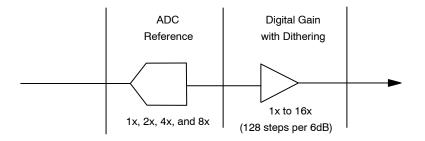

## **GAIN STAGES**

The analog gain stages of the AR0331 sensor are shown in Figure 18. The sensor analog gain stage consists of a

Figure 18. Gain Stages in AR0331 Sensor

The level of analog gain applied is controlled by the coarse\_gain register. The recommended analog gain settings are listed in Table 8. A minimum analog gain of 1.23x is

recommended. Changes to these registers should be done prior to streaming images.

#### Table 8. RECOMMENDED SENSOR GAIN

| coarse_gain(0x3060[5:4])/<br>coarse_gain_cb (0x3060[13:12]) | fine_gain (0x3060[3:0])/<br>fine_gain_cb (0x3060[11:8]) | ADC Gain |

|-------------------------------------------------------------|---------------------------------------------------------|----------|

| 0                                                           | 6                                                       | 1.23     |

| 0                                                           | 7                                                       | 1.28     |

| 0                                                           | 8                                                       | 1.34     |

| 0                                                           | 9                                                       | 1.39     |

| coarse_gain(0x3060[5:4])/<br>coarse_gain_cb (0x3060[13:12]) | fine_gain (0x3060[3:0])/<br>fine_gain_cb (0x3060[11:8]) | ADC Gain |

|-------------------------------------------------------------|---------------------------------------------------------|----------|

| 0                                                           | 10                                                      | 1.45     |

| 0                                                           | 11                                                      | 1.52     |

| 0                                                           | 12                                                      | 1.60     |

| 0                                                           | 13                                                      | 1.69     |

| 0                                                           | 14                                                      | 1.78     |

| 0                                                           | 15                                                      | 1.88     |

| 1                                                           | 0                                                       | 2.00     |

| 1                                                           | 2                                                       | 2.14     |

| 1                                                           | 4                                                       | 2.28     |

| 1                                                           | 6                                                       | 2.47     |

| 1                                                           | 8                                                       | 2.67     |

| 1                                                           | 10                                                      | 2.91     |

| 1                                                           | 12                                                      | 3.20     |

| 1                                                           | 14                                                      | 3.56     |

| 2                                                           | 0                                                       | 4        |

| 2                                                           | 4                                                       | 4.56     |

| 2                                                           | 8                                                       | 5.34     |

| 2                                                           | 12                                                      | 6.41     |

| 3                                                           | 0                                                       | 8        |

#### Table 8. RECOMMENDED SENSOR GAIN (continued)

Each digital gain can be configured from a gain of 0 to 15.992. The digital gain supports 128 gain steps per 6dB of gain. The format of each digital gain register is "xxxx.yyyyyy" where "xxxx" refers an integer gain of 1 to 15 and "yyyyyy" is a fractional gain ranging from 0/128 to 127/128.

The sensor includes a digital dithering feature to reduce quantization noise resulting from using digital gain. It can be disabled by setting R0x30BA[5] to 0. The default value is 1.

#### PEDESTALS

There are two types of constant offset pedestals that may be adjusted at the end of the datapath.

The data pedestal is a constant offset that is added to pixel values at the end of the datapath. The default offset when ALTM is disabled is 168 and is a 12-bit offset. This offset matches the maximum range used by the corrections in the digital readout path. The purpose of the data pedestal is to convert negative values generated by the digital datapath into positive output data. It is recommended that the data pedestal be set to 16 when ALTM is enabled.

The data pedestal value can be changed from its default value by adjusting register R0x301E.

The ALTM pedestal (R0x2450) is also located at the end of the datapath. The ALTM pedestal default offset is 0.

## **HIGH DYNAMIC RANGE MODE**

By default, the sensor powers up in HDR Mode. The HDR scheme used is multi–exposure HDR. This allows the sensor to handle up to 100 dB of dynamic range. In HDR mode, the sensor sequentially captures two exposures by maintaining two separate read and reset pointers that are interleaved within the rolling shutter readout. The intermediate pixel values are stored in line buffers while waiting for the two exposure values to be present. As soon as a pixel's two exposure values are available, they are combined to create a linearized 16–bit value for each pixel's response. Depending on whether HiSPi or Parallel mode is selected, the full 16 bit value may be output, it can be compressed to 12 bits using Adaptive Local Tone Mapping (ALTM), or companded to 12 or 14 bits.

#### **Adaptive Local Tone Mapping**

Real– world scenes often have a very high dynamic range (HDR) that far exceeds the electrical dynamic range of the imager. Dynamic range is defined as the luminance ratio between the brightest and the darkest objects in a scene. Even though the AR0331 can capture full dynamic range images, the images are still limited by the low dynamic range of display devices. Today's typical LCD monitor has a contrast ratio around 1000:1 while it is not atypical for an

HDR image having a contrast ratio of around 250000:1. Therefore, in order to reproduce HDR images on a low dynamic range display device, the captured high dynamic range must be compressed to the available range of the display device. This is commonly called tone mapping. The AR0331 has implemented an adaptive local tone mapping (ALTM) feature to reproduce visually appealing images that increase the local contrast and the visibility of the images. When ALTM is enabled, the gamma in the backend ISP should be set to 1 for proper display. See the AR0331 Developer Guide for more information on ALTM.

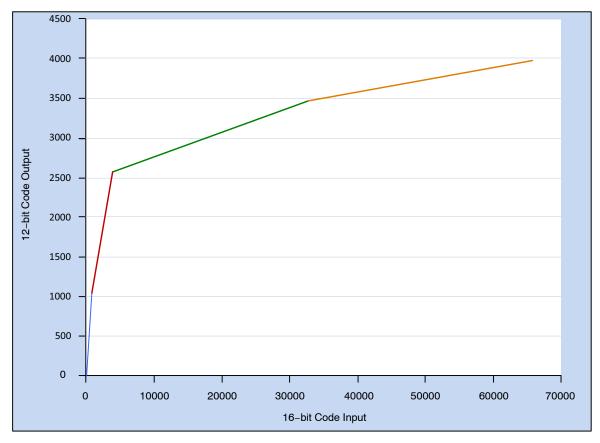

## Companding

The 16-bit linearized HDR image may be compressed to 12 bits using on-chip companding. Figure 19 illustrates the compression from 16- to 12-bits. Companding is enabled by setting R0x31D0. Table 10 shows the knee points for the different modes.

Figure 19. HDR Data Compression

## Table 9. COMPANDING TABLE

|                         | Segment 1                          | Segment 2                            | Segment 3                                             | Segment 4                                              |

|-------------------------|------------------------------------|--------------------------------------|-------------------------------------------------------|--------------------------------------------------------|

| Input Code Range        | 0 to 1023                          | 1024 to 4095                         | 4096 to 32767                                         | 32768 to 65535                                         |

| Output Code<br>Range    | 0 to 1023                          | 1024 to 2559                         | 2560 to 3455                                          | 3456 to 3967                                           |

| Companding<br>Formula   | P <sub>out</sub> = P <sub>in</sub> | $P_{out} = (P_{in} - 1024)/2 + 1024$ | $P_{out} = (P_{in} - 4096)/32 + 2560$                 | P <sub>out</sub> = (P <sub>in</sub> - 32768)/64 + 3456 |

| Decompanding<br>Formula | P <sub>out</sub> = P <sub>in</sub> | $P_{out} = (P_{in} - 1024)*2 + 1024$ | P <sub>out</sub> = (P <sub>in</sub> – 2560)*32 + 4096 | P <sub>out</sub> = (P <sub>in</sub> - 3456)*64 + 32768 |

Table 9 illustrates the input and output codes as well as companding and decompanding formulas for each of the four colored segments in Figure 19.

| T1/T2<br>Exposure Ratio<br>(R1)<br>R0x3082[3:2] | P1              | Роит1<br>= P1 | P2              | Роит2=<br>(P2 – P1)/2 + 1024 | P3              | Роит3=<br>(Р3 – Р2)/32 + 2560 | РМАХ            | РоитМАХ =<br>(PMAX – P3)/64 + 3456 |

|-------------------------------------------------|-----------------|---------------|-----------------|------------------------------|-----------------|-------------------------------|-----------------|------------------------------------|

| 4x, 8x, 16x, 32x                                | 2 <sup>10</sup> | 1024          | 2 <sup>12</sup> | 2560                         | 2 <sup>15</sup> | 3456                          | 2 <sup>16</sup> | 3968                               |

As described in Table 10, the AR0331 companding block operates on 16-bit input only. For the exposure ratios that do not result in 16-bits, bit shifting occurs before the data enters the companding block. As a result of the bit shift, data needs

to be unshifted after linearization in order to obtain the proper image. Table 11 provides the bit operation that should occur to the data after linearization.

| Table 11. BI | <b>FOPERATION AFTI</b> | ER LINEARIZATION |

|--------------|------------------------|------------------|

|--------------|------------------------|------------------|

| ratio_t1_t2 (R0x3082[3:2])/ratio_t1_t2_cb (R0x3084[3:2]) | Bit Shift Operation after Linearization |

|----------------------------------------------------------|-----------------------------------------|

| 4x                                                       | Right Shift 2 Bits                      |

| 8x                                                       | Right Shift 1 Bit                       |

| 16x                                                      | No Shift                                |

| 32x                                                      | Left Shift 1 Bit                        |

## HDR-Specific Exposure Settings

In HDR mode, pixel values are stored in line buffers while waiting for both exposures to be available for final pixel data combination. There are 70 line buffers used to store intermediate T1 data. Due to this limitation, the maximum coarse integration time possible for a given exposure ratio is equal to 70\*T1/T2 lines.

For example, if R0x3082[3:2] = 2, the sensor is set to have T1/T2 ratio = 16x. Therefore the maximum number of integration lines is 70\*16 = 1120 lines. If coarse integration time is greater than this, the T2 integration time will stay at 70. The sensor will calculate the ratio internally, enabling the linearization to be performed. If companding is being used,

then relinearization would still follow the programmed ratio. For example if the T1/T2 ratio was programmed to 16x but coarse integration was increased beyond 1120 then one would still use the 16x relinearization formulas.

An additional limitation is the maximum number of exposure lines in relation to the frame\_length\_lines register. In linear mode, maximum coarse\_integration\_time = frame\_length\_lines – 1. However in HDR mode, since the coarse integration time register controls T1, the max coarse integration time is frame\_length\_lines – 71.

Putting the two criteria listed above together, the formula is as follows:

maximum coarse\_integration\_time = minimum(70

$$\times \frac{T_1}{T_2}$$

, frame\_length\_lines-71) (eq. 2)

There is a limitation of the minimum number of exposure lines, which is one row time for linear mode. In HDR mode, the minimum number of rows required is half of the ratio T1/T2.

## **Motion Compensation**

In typical multi-exposure HDR systems, motion artifacts can be created when objects move during the T1 or T2 integration time. When this happens, edge artifacts can potentially be visible and might look like a ghosting effect.

To correct this, the AR0331 has special 2D motion compensation circuitry that detects motion artifacts and corrects the image.

The motion compensation feature can be enabled by setting R0x318C[14] = 1. Additional parameters are available to control the extent of motion detection and correction as per the requirements of the specific

application. For more information, refer to the AR0331 Register Reference document and the AR0331 Developer Guide.

## RESET

The AR0331 may be reset by the RESET\_BAR pin (active LOW) or the reset register.

## Hard Reset of Logic

The RESET\_BAR pin can be connected to an external RC circuit for simplicity. The recommended RC circuit uses a 10 k $\Omega$  resistor and a 0.1  $\mu$ F capacitor. The rise time for the RC circuit is 1  $\mu$ s maximum.

## Soft Reset of Logic

Soft reset of logic is controlled by the R0x301A Reset register. Bit 0 is used to reset the digital logic of the sensor.

Furthermore, by asserting the soft reset, the sensor aborts the current frame it is processing and starts a new frame. This bit

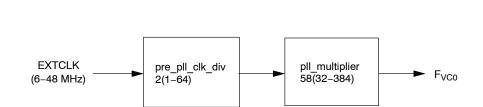

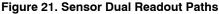

#### SENSOR PLL

#### VCO

Figure 20. PLL Dividers Affecting VCO Frequency

The sensor contains a phase–locked loop (PLL) that is used for timing generation and control. The required VCO clock frequency is attained through the use of a pre–PLL clock divider followed by a multiplier. The PLL multiplier should be an even integer. If an odd integer (M) is programmed, the PLL will default to the lower (M–1) value to maintain an even multiplier value. The multiplier is followed by a set of dividers used to generate the output clocks required for the sensor array, the pixel analog and digital readout paths, and the output parallel and serial interfaces. Use of the PLL is required when using the HiSPi interface.

is a self-resetting bit and also returns to "0" during two-wire

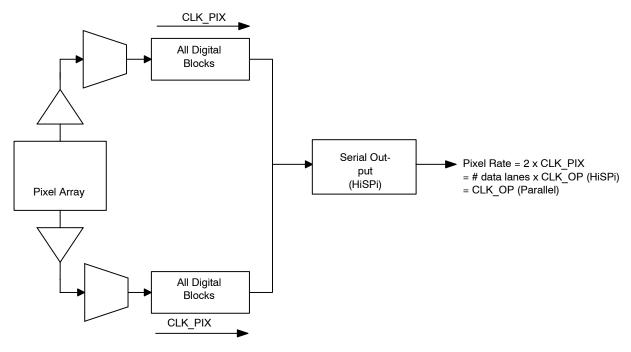

#### **Dual Readout Paths**

serial interface reads.

There are two readout paths within the sensor digital block. The sensor PLL should be configured such that the total pixel rate across both readout paths is equal to the output pixel rate. For example, if CLK\_PIX is 74.25 MHz in a 4-lane HiSPi configuration, the CLK\_OP should be equal to 37.125 MHz.

The sensor row timing calculation refers to each data-path individually. For example, the sensor default configuration uses 1100 clocks per row (line\_length\_pck) to output 1928 active pixels per row. The aggregate clocks per row seen by the receiver will be 2200 clocks (1100 x 2 readout paths).

## Parallel PLL Configuration

Figure 22. PLL for the Parallel Interface

The maximum output of the parallel interface is 74.25 MPixel/s. This will limit the readout clock (CLK\_PIX) to 37.125 MPixel/s. The sensor will not use the  $F_{SERIAL}$ ,

$F_{\mbox{SERIAL\_CLK}},$  or CLK\_OP when configured to use the parallel interface.

## Table 12. PLL PARAMETERS FOR THE PARALLEL INTERFACE

| Parameter      | Symbol           | Min | Мах    | Unit     |

|----------------|------------------|-----|--------|----------|

| External Clock | EXTCLK           | 6   | 48     | MHz      |

| VCO Clock      | F <sub>VCO</sub> | 384 | 768    | MHz      |

| Readout Clock  | CLK_PIX          |     | 37.125 | Mpixel/s |

| Output Clock   | CLK_OP           |     | 74.25  | Mpixel/s |

## Table 13. EXAMPLE PLL CONFIGURATION FOR THE PARALLEL INTERFACE

| Parameter         | Value | Output                             |

|-------------------|-------|------------------------------------|

| F <sub>VCO</sub>  |       | 445.5 MHz (Max)                    |

| vt_sys_clk_div    | 1     |                                    |

| vt_pix_clk_div    | 6     |                                    |

| CLK_PIX           |       | 37.125 MPixel/s (= 445.5 MHz / 12) |

| CLK_OP            |       | 74.25 MPixel/s (= 445.5 MHz / 6)   |

| Output pixel rate |       | 74.25 MPixel/s                     |

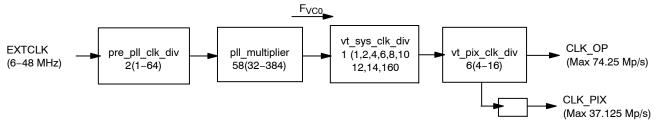

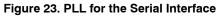

#### **Serial PLL Configuration**

The PLL must be enabled when HiSPi mode is selected. The sensor will use op\_sys\_clk\_div and op\_pix\_clk\_div to configure the output clock per lane (CLK\_OP). The configuration will depend on the number of active lanes (1, 2, or 4) configured. To configure the sensor protocol and number of lanes, refer to "Serial Configuration".

| Table 14. PLL PARAMETERS FOR THE SERIAL INTERFACE |

|---------------------------------------------------|

|---------------------------------------------------|

| Parameter                             | Symbol                  | Min         | Мах         | Unit     |

|---------------------------------------|-------------------------|-------------|-------------|----------|

| External Clock                        | EXTCLK                  | 6           | 48          | MHz      |

| External Clock                        | EXTCLK                  | 6           | 48          | MHz      |

| VCO Clock                             | F <sub>VCO</sub>        | 384         | 768         | MHz      |

| Readout Clock                         | CLK_PIX                 |             | 74.25       | Mpixel/s |

| Output Clock                          | CLK_OP                  |             | 37.125      | Mpixel/s |

| Output Serial Data Rate<br>Per Lane   | F <sub>SERIAL</sub>     | 300 (HiSPi) | 700 (HiSPi) | Mbps     |

| Output Serial Clock<br>Speed Per Lane | F <sub>SERIAL_CLK</sub> | 150 (HiSPi) | 350 (HiSPi) | MHz      |

Configure the serial output so that it adheres to the following rules:

- The maximum data-rate per lane (F<sub>SERIAL</sub>) is 700 Mbps/lane (HiSPi).

- Configure the output pixel rate per lane (CLK\_OP) so that the sensor output pixel rate matches the peak pixel rate (2 x CLK\_PIX).

- 4-lane: 4 x CLK\_OP = 2 x CLK\_PIX = Pixel Rate (max: 148.5 Mpixel/s)

- 2-lane: 2 x CLK\_OP = 2 x CLK\_PIX = Pixel Rate (max: 74.25 Mpixel/s)

- 1-lane: 1 x CLK\_OP = 2 x CLK\_PIX = Pixel Rate (max: 37.125 Mpixel/s)

|                         | 4-lane |         |        | 2-I    | ane    | 1-lane |        |          |

|-------------------------|--------|---------|--------|--------|--------|--------|--------|----------|

| Parameter               | 16-bit | 14-bit  | 12-bit | 10-bit | 12-bit | 10-bit | 10-bit | Units    |

| F <sub>VCO</sub>        | 594    | 519.75  | 445.5  | 742.5  | 445.5  | 742.5  | 742.5  | MHz      |

| vt_sys_clk_div          | 1      | 1       | 1      | 2      | 1      | 2      | 4      |          |

| vt_pix_clk_div          | 8      | 7       | 6      | 5      | 12     | 10     | 10     |          |

| op_sys_clk_div          | 1      | 1       | 1      | 2      | 1      | 2      | 2      |          |

| op_pix_clk_div          | 16     | 14      | 12     | 10     | 12     | 10     | 10     |          |

| F <sub>SERIAL</sub>     | 594    | 519.75  | 445.5  | 371.25 | 445.5  | 371.25 | 371.25 | MHz      |

| F <sub>SERIAL_CLK</sub> | 297    | 259.875 | 222.75 | 185.63 | 222.75 | 185.63 | 185.63 | MHz      |

| CLK_PIX                 | 74.25  | 74.25   | 74.25  | 74.25  | 37.125 | 37.125 | 18.563 | Mpixel/s |

| CLK_OP                  | 37.125 | 37.125  | 37.125 | 37.125 | 37.125 | 37.125 | 37.125 | Mpixel/s |

| Pixel Rate              | 148.5  | 148.5   | 148.5  | 148.5  | 74.25  | 74.25  | 37.125 | Mpixel/s |

## Table 15. EXAMPLE PLL CONFIGURATIONS FOR THE SERIAL INTERFACE

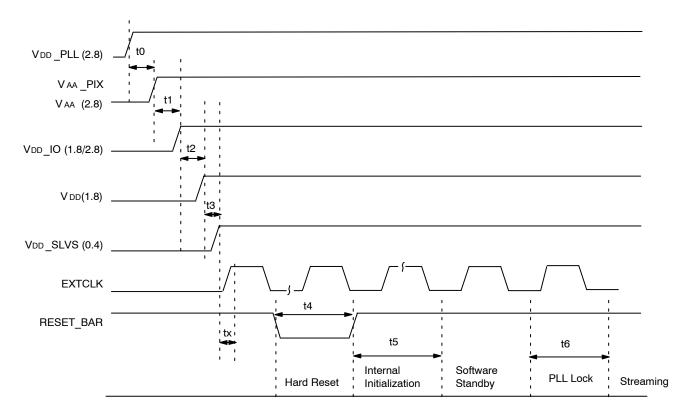

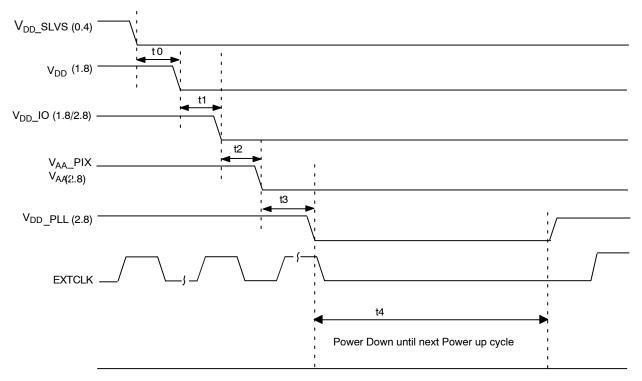

## Stream/Standby Control

The sensor supports a soft standby mode. In this mode, the external clock can be optionally disabled to further minimize power consumption. If this is done, then the "Power–Up Sequence" must be followed. When the external clock is disabled, the sensor will be unresponsive to register writes and other operations.

Soft Standby is a low-power state that is controlled through register R0x301A[2]. The sensor will go to Standby after completion of the current frame readout. When the sensor comes back from Soft Standby, previously written register settings are still maintained. Soft Standby will not occur if the Trigger pin is held high.

A specific sequence needs to be followed to enter and exit from Soft Standby.

Entering Soft Standby:

- 1. Set R0x301A[12] = 1 if serial mode was used

- 2. Set R0x301A[2] = 0 and drive Trigger pin low.

- 3. Turn off external clock to further minimize power consumption

## Exiting Soft Standby:

- 1. Enable external clock if it was turned off

- 2. Set R0x301A[2] = 1 or drive Trigger pin high.

- 3. Set R0x301A[12] = 0 if serial mode is used

## SENSOR READOUT

## Image Acquisition Modes

- The AR0331 supports two image acquisition modes:

- Electronic rolling shutter (ERS) mode: This is the normal mode of operation. When the AR0331 is streaming, it generates frames at a fixed rate, and each frame is integrated (exposed) using the ERS. When the ERS is in use, timing and control logic within the sensor sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and subsequently reading that row, the pixels in the row integrate incident light. The integration (exposure) time is controlled by varying the time between row reset and row readout. For each row in a frame, the time between row reset and row readout is the same, leading to a uniform integration time across the frame. When the integration time is changed (by using the two-wire serial interface to change register settings), the timing and control logic controls the transition from old to new integration time in such a way that the stream of output frames from the AR0331 switches cleanly from the old integration time

to the new while only generating frames with uniform integration. See "Changes to Integration Time" in the AR0331 Register Reference.

• Global reset mode:

This mode can be used to acquire a single image at the current resolution. In this mode, the end point of the pixel integration time is controlled by an external electromechanical shutter, and the AR0331 provides control signals to interface to that shutter.

The benefit of using an external electromechanical shutter is that it eliminates the visual artifacts associated with ERS operation. Visual artifacts arise in ERS operation, particularly at low frame rates, because an ERS image effectively integrates each row of the pixel array at a different point in time.

## Window Control

The sequencing of the pixel array is controlled by the x\_addr\_start, y\_addr\_start, x\_addr\_end, and y\_addr\_end registers.

## **Readout Modes**

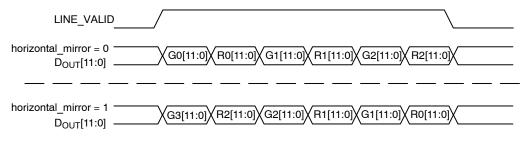

## Horizontal Mirror

When the horiz\_mirror bit (R0x3040[14]) is set in the read\_mode register, the order of pixel readout within a row is reversed, so that readout starts from x\_addr\_end + 1 and ends at x\_addr\_start. Figure 24 shows a sequence of 6 pixels being read out with R0x3040[14] = 0 and R0x3040[14] = 1.

Figure 24. Effect of Horizontal Mirror on Readout Order

## Vertical Flip

When the vert\_flip bit (R0x3040[15]) is set in the read\_mode register, the order in which pixel rows are read out is reversed, so that row readout starts from y\_addr\_end

and ends at y\_addr\_start. Figure 30 shows a sequence of 6 rows being read out with R0x3040[15] = 0 and R0x3040[15] = 1.

Figure 25. Effect of Vertical Flip on Readout Order

## SUBSAMPLING

The AR0331 supports subsampling. Subsampling allows the sensor to read out a smaller set of active pixels by either

skipping, binning, or summing pixels within the readout window. The following examples are configured to use either  $2 \times 2$  or  $3 \times 3$  subsampling.

Figure 26. Horizontal Binning in the AR0331 Sensor

Horizontal binning is achieved either in the pixel readout or the digital readout. The sensor will sample the combined 2x or 3x adjacent pixels within the same color plane.

Figure 27. Vertical Row Binning in the AR0331 Sensor

Vertical row binning is applied in the pixel readout. Row binning can be configured as 2x or 3x rows within the same color plane.

Pixel skipping can be configured up to 2x and 3x in both the x-direction and y-direction. Skipping pixels in the x-direction will not reduce the row time. Skipping pixels in the y-direction will reduce the number of rows from the sensor effectively reducing the frame time. Skipping will introduce image artifacts from aliasing. Refer to the AR0331 Developer Guide for details on configuring skipping, binning, and summing modes for color and monochrome operation.

## SENSOR FRAME RATE

The time required to read out an image frame ( $T_{FRAME}$ ) can be derived from the number of clocks required to output each image and the pixel clock.

The frame-rate is the inverse of the frame period.

$$fps = \frac{1}{T_{FRAME}}$$

(eq. 3)

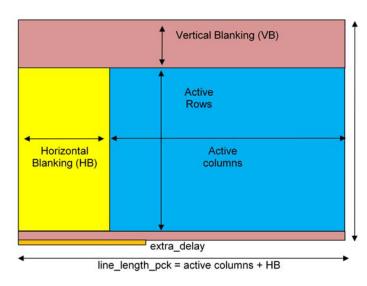

The number of clocks can be simplified further into the following parameters:

• The number of clocks required for each sensor row (line length pck)

This parameter also determines the sensor row period when referenced to the sensor readout clock. ( $T_{ROW}$  = line\_length\_pck x 1/CLK\_PIX)

- The number of row periods per frame (frame length lines)

- An extra delay between frames used to achieve a specific output frame period (extra delay)

$$T_{FRAME} = \frac{1}{(CLK_PIX)} \times [frame\_length\_lines \times line\_length\_pck + extra\_delay]$$

(eq. 4)

frame\_length\_lines = active rows + Vertical Blanking

$\frac{1}{2} \times \left[ \frac{x\_addr\_end\_x\_addr\_start + 1}{(x\_odd\_inc + 1) \times 0.5} \right] + 96 \quad (eq. 7)$

frame length lines determines the number of row periods

(T<sub>ROW</sub>) per frame. This includes both the active and

blanking rows. The minimum vertical blanking value is

defined by the number of OB rows read per frame, two

embedded data rows, and two blank rows. A minimum number of idle rows equal to the T2 integration time should

be added in HDR mode to allow for changes in integration

time by an auto exposure algorithm. For example, if the coarse integration time is 320 lines and the exposure ratio is

16x, then the minimum vertical blanking would be 8 + 2 + 2 + 20 = 32 rows. The minimum (default) number of idle

#### Figure 28. Frame Period Measured in Clocks

**Output Interface Limitations:**

**Row Periods Per Frame**

#### Row Period (T<sub>ROW</sub>)

line\_length\_pck will determine the number of clock periods per row and the row period ( $T_{ROW}$ ) when combined with the sensor readout clock. line\_length\_pck includes both the active pixels and the horizontal blanking time per row. The sensor utilizes two readout paths, as seen in Figure 21, allowing the sensor to output two pixels during each pixel clock.

The minimum line\_length\_pck is defined as the maximum of the following three equations:

#### ADC Readout Limitation:

line\_length\_pck

$$\geq$$

1100 (eq. 5)

**Digital Readout Limitation:**

$$\frac{1}{3} \times \left[ \frac{x\_addr\_end\_x\_addr\_start + 1}{(x\_odd\_inc + 1) \times 0.5} \right]$$

(eq. 6)

$$\begin{array}{c} (x\_odd\_inc + 1) \times 0.5 \end{array} \int (x\_odd\_inc + 1) \times 0.5 \end{array} \\ \begin{array}{c} (x\_odd\_end\_y\_addr\_start + 1] \\ (x\_odd\_inc + 1) \end{array} + min\_vertical\_blanking \end{array}$$

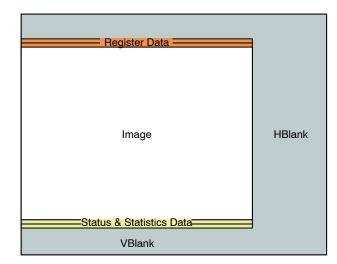

The sensor is configured to output frame information in two embedded data rows by setting R0x3064[8] to 1 (default). If R0x3064[8] is set to 0, the sensor will instead output two blank rows. The data configured in the two embedded rows is defined in "Embedded Data and Statistics".

(eq. 8)

#### Table 16. MINIMUM VERTICAL BLANKING CONFIGURATION

| R0x3180[7:4]  | OB Rows   | min_vertical_blanking (Note 1) |

|---------------|-----------|--------------------------------|

| 0x8 (Default) | 8 OB Rows | 8 OB + 8 = 16                  |

| 0x4           | 4 OB Rows | 4 OB + 8 = 12                  |

| 0x2           | 2 OB Rows | 2 OB + 8 = 10                  |

1. min\_vertical\_blanking includes the default number (4) of idle rows.

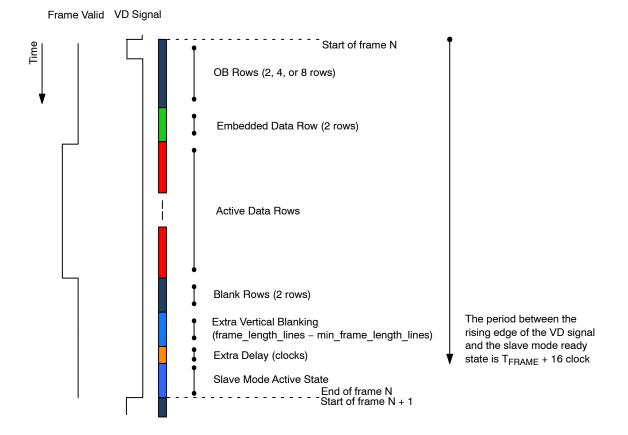

The locations of the OB rows, embedded rows, and blank rows within the frame readout are identified in Figure 29: "Slave Mode Active State and Vertical Blanking,".

## SLAVE MODE

The slave mode feature of the AR0331 supports triggering the start of a frame readout from a VD signal that is supplied

from an external ASIC. The slave mode signal allows for precise control of frame rate and register change updates.

The VD signal is an edge triggered input to the trigger pin and must be at least 3 PIXCLK cycles wide.

Figure 29. Slave Mode Active State and Vertical Blanking

If the slave mode is disabled, the new frame will begin after the extra delay period is finished.

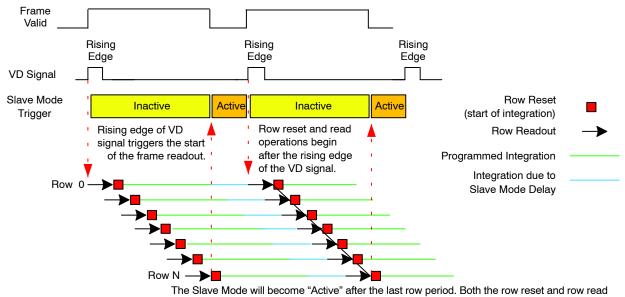

The slave mode will react to the rising edge of the input VD signal if it is in an active state. When the VD signal is received, the sensor will begin the frame readout and the

slave mode will remain inactive for the period of one frame time plus 16 clock periods ( $T_{FRAME}$  + (16 / CLK\_PIX)). After this period, the slave mode will re-enter the active state and will respond to the VD signal.

operations will wait until the rising edge of the VD signal. .

Note: The integration of the last row is started before the end of the programmed integration for the first row.

#### Figure 30. Slave Mode Example with Equal Integration and Frame Readout Periods

The row shutter and read operations will stop when the slave mode becomes active and is waiting for the VD signal. The following should be considered when configuring the sensor to use the slave mode:

- The frame period (T<sub>FRAME</sub>) should be configured to be less than the period of the input VD signal. The sensor will disregard the input VD signal if it appears before the frame readout is finished.

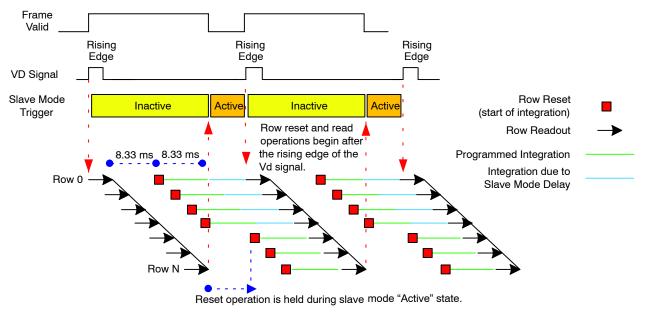

- 2. If the sensor integration time is configured to be less than the frame period, then the sensor will not have reset all of the sensor rows before it begins waiting for the input VD signal. This error can be minimized by configuring the frame period to be as close as possible to the desired frame rate (period between VD signals).

Note: The sensor read pointer will have paused at row 0 while the shutter pointer pauses at row N/2. The extra integration caused by the slave mode delay will only be seen by rows 0 to N/2. The example below is for a frame readout period of 16.6 ms while the integration time is configured to 8.33 ms.

#### Figure 31. Slave Mode Example Where the Integration Period is Half of the Frame Readout Period

When the slave mode becomes active, the sensor will pause both row read and row reset operations. (Note: The row integration period is defined as the period from row reset to row read.) The frame-time should therefore be configured so that the slave mode "wait period" is as short as possible. In the case where the sensor integration time is shorter than the frame time, the "wait period" will only increase the integration of the rows that have been reset following the last VD pulse.

The period between slave mode pulses must also be greater than the frame period. If the rising edge of the VD pulse arrives while the slave mode is inactive, the VD pulse will be ignored and will wait until the next VD pulse has arrived.

To enter slave mode:

- 1. While in soft-standby, set R0x30CE[4] = 1 to enter slave mode

- 2. Enable the input pins (TRIGGER) by setting R0x301A[8] = 1

- 3. Enable streaming by setting R0x301A[2] = 1

- 4. Apply sync-pulses to the TRIGGER input

## **FRAME READOUT**

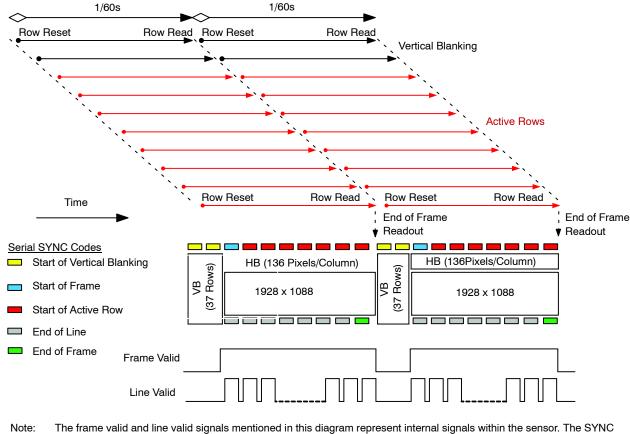

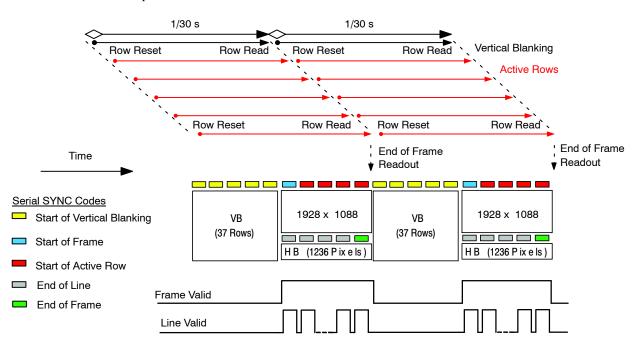

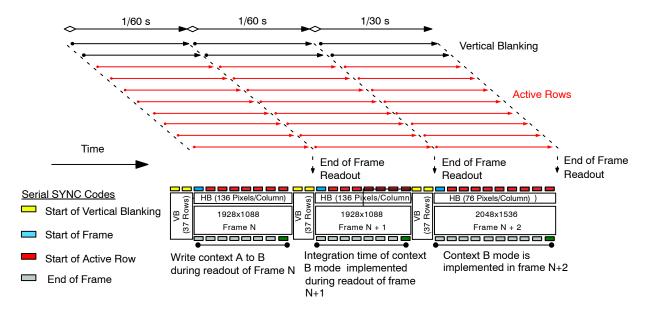

The sensor readout begins with vertical blanking rows followed by the active rows. The frame readout period can be defined by the number of row periods within a frame (frame\_length\_lines) and the row period (*line\_length\_pck/clk\_pix*). The sensor will read the first vertical blanking row at the beginning of the frame period and the last active row at the end of the row period.

codes represented in this diagram represent the HiSPi Streaming-SP protocol.

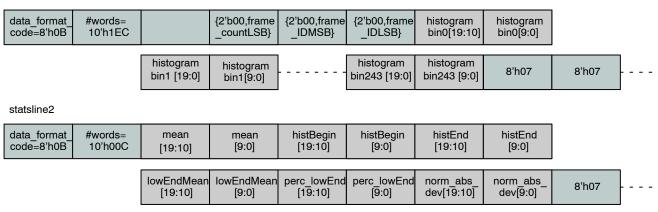

## Figure 32. Example of the Sensor Output of a 1928 x 1088 Frame at 60 fps

Figure 32 aligns the frame integration and readout operation to the sensor output. It also shows the sensor

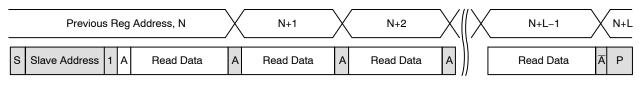

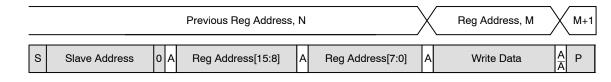

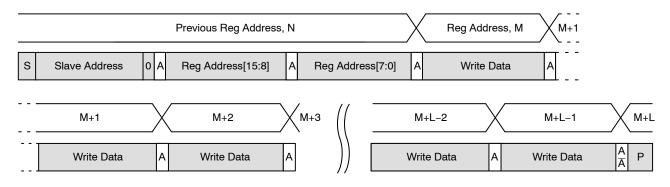

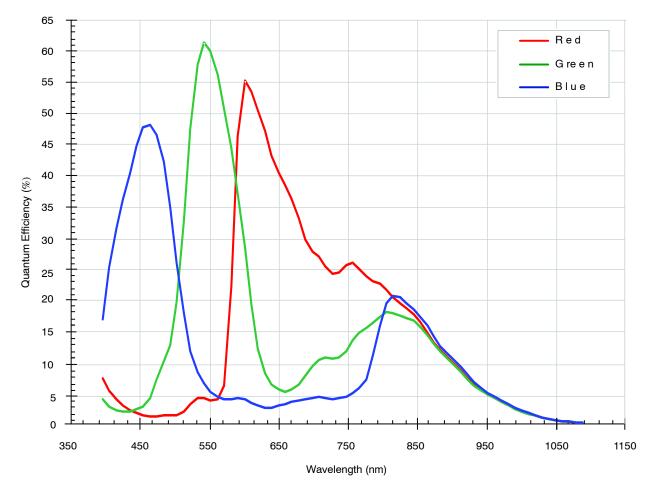

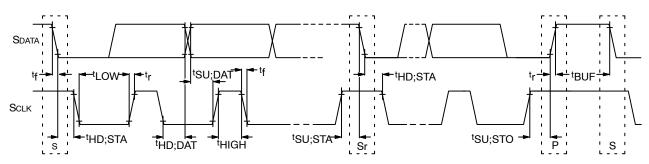

output using the HiSPi Streaming–SP protocol. Different sensor protocols will list different SYNC codes.