# Revision History 8Gbit DDR3L SDRAM

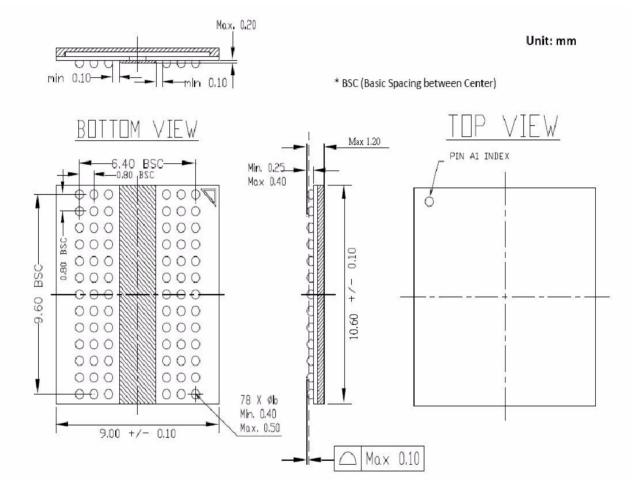

8 BANKS X 128Mbit X 8 - Dual Die Package (DDP) 78ball FBGA Package

| Revision | Details               | Date      |

|----------|-----------------------|-----------|

| Rev 1.0  | Preliminary datasheet | Feb. 2019 |

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 610-6800 FAX: (650) 620-9211 Alliance Memory Inc. reserves the right to change products or specification without notice

#### Specifications

- Density : 8G bits

- Organization :

- 128M words x 8 bits x 8 banks

- Package :

- 78-ball FBGA

- Two 1Gbit x 4 dies stacked (DDP)

- Lead-free (RoHS compliant) and Halogen-free

- Power supply : VDD, VDDQ = 1.35V (1.283V to 1.45V)

- Backward compatible to VDD, VDDQ = 1.5V ± 0.075V

- Data rate : 1866Mbps

- 2KB page size

- Row address: A0 to A15

- Column address: A0 to A9, A11

- Eight internal banks for concurrent operation

- Burst lengths (BL) : 8 and 4 with Burst Chop (BC)

- Burst type (BT) :

- Sequential (8, 4 with BC)

- Interleave (8, 4 with BC)

- <u>CAS</u> Latency (CL) : 5, 6, 7, 8, 9, 10, 11, 13

- CAS Write Latency (CWL) : 5, 6, 7, 8,9

- Precharge : auto precharge option for each burst access

- Driver strength : RZQ/7, RZQ/6 (RZQ = 240  $\Omega$ )

- Refresh : auto-refresh, self-refresh

- Refresh cycles :

- Average refresh period

- 7.8 μs at -40°C ≤ Tc ≤ +85°C

- 3.9 μs at +85°C < Tc ≤ +105°C

- Operating case temperature range

- Commercial Tc = 0°C to +95°C

**Table 1. Ordering Information**

- Industrial Tc =  $-40^{\circ}$ C to  $+95^{\circ}$ C

- Automotive Tc =  $-40^{\circ}$ C to  $+105^{\circ}$ C

### Features

- Double-data-rate architecture; two data transfers per clock cycle

- The high-speed data transfer is realized by the 8 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and DQS) is transmitted/ received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; center-aligned with data for WRITEs

- Differential clock inputs (CK and CK)

- DLL aligns DQ and DQS transitions with CK transitions

- Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS

- Data mask (DM) for write data

- Posted CAS by programmable additive latency for better command and data bus efficiency

- On-Die Termination (ODT) for better signal quality - Svnchronous ODT

- Synchronous C

- Dynamic ODT

- Asynchronous ODT

- Multi Purpose Register (MPR) for pre-defined pattern read out

- ZQ calibration for DQ drive and ODT

- RESET pin for Power-up sequence and reset function

- SRT range : Normal/extended

- Programmable Output driver impedance control

| Product part No   | Org    | Temperature               | Max Clock (MHz) | Package      |

|-------------------|--------|---------------------------|-----------------|--------------|

| AS4C1G8D3LA-10BCN | 1G x 8 | Commercial 0°C to 95°C    | 933             | 78-ball FBGA |

| AS4C1G8D3LA-10BIN | 1G x 8 | Industrial -40°C to 95°C  | 933             | 78-ball FBGA |

| AS4C1G8D3LA-10BAN | 1G x 8 | Automotive -40°C to 105°C | 933             | 78-ball FBGA |

# Table 2. Speed Grade Information

| Speed Grade | Clock Frequency | CAS Latency | tRCD(ns) | tRP(ns) |

|-------------|-----------------|-------------|----------|---------|

| DDR3-1866   | 933 MHz         | 13          | 13.91    | 13.91   |

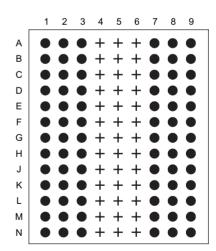

# Pin Configurations

|   |                    | •                                   |     |

|---|--------------------|-------------------------------------|-----|

|   | 1                  | 2                                   | 3   |

| Α | V <sub>SS</sub>    | V <sub>DD</sub>                     | NC  |

| в | V <sub>SS</sub>    | V <sub>SSQ</sub>                    | DQ0 |

| С | V <sub>DDQ</sub>   | DQ2                                 | DQS |

| D | V <sub>SSQ</sub>   | DQ6                                 | DQS |

| Е | V <sub>REFDQ</sub> | V <sub>REFDQ</sub> V <sub>DDQ</sub> |     |

| F | NC                 | V <sub>SS</sub>                     | RAS |

| G | ODT                | V <sub>DD</sub>                     | CAS |

| н | NC                 | CS                                  | WE  |

| J | V <sub>SS</sub>    | BA0                                 | BA2 |

| κ | V <sub>DD</sub>    | A3                                  | A0  |

| L | V <sub>SS</sub>    | A5                                  | A2  |

| м | V <sub>DD</sub>    | A7                                  | A9  |

| Ν | V <sub>SS</sub>    | RESET                               | A13 |

# 78-ball FBGA (x8 configuration)

| 4 | 5 | 6 | 7               | 8                  | 9                |   |

|---|---|---|-----------------|--------------------|------------------|---|

|   |   |   | NC              | V <sub>SS</sub>    | V <sub>DD</sub>  | Α |

|   |   |   | DM              | V <sub>SSQ</sub>   | V <sub>DDQ</sub> | в |

|   |   |   | DQ1             | DQ3                | V <sub>SSQ</sub> | С |

|   |   |   | V <sub>DD</sub> | V <sub>SS</sub>    | V <sub>SSQ</sub> | D |

|   |   |   | DQ7             | DQ5                | V <sub>DDQ</sub> | Е |

|   |   |   | СК              | V <sub>SS</sub>    | NC               | F |

|   |   |   | СК              | V <sub>DD</sub>    | CKE              | G |

|   |   |   | A10/AP          | ZQ                 | NC               | н |

|   |   |   | A15             | V <sub>REFCA</sub> | V <sub>SS</sub>  | J |

|   |   |   | A12/BC          | BA1                | V <sub>DD</sub>  | к |

|   |   |   | A1              | A4                 | V <sub>SS</sub>  | L |

|   |   |   | A11             | A6                 | V <sub>DD</sub>  | м |

|   |   |   | A14             | A8                 | V <sub>SS</sub>  | Ν |

# Ball Locations (x8)

- Populated ball

- + Ball not populated

# Top view

(See the balls through the package)

# Signal Pin Description

| Pin          | Туре             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ск, ск       | Input            | <b>Clock</b> : CK and $\overline{CK}$ are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of $\overline{CK}$ . Output (read) data is referenced to the crossings of CK and $\overline{CK}$                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CKE          | Input            | <b>Clock Enable</b> : CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self Refresh operation (all banks idle), or Active Power-Down (Row Active in any bank). CKE is asynchronous for self refresh exit. After $V_{REFCA}$ has become stable during the power on and initialization sequence, it must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, $\overline{CK}$ , ODT and CKE are disabled during power-down. Input buffers, excluding CKE, are disabled during Self-Refresh. |

| CS           | Input            | <b>Chip Select :</b> All commands are masked when $\overline{CS}$ is registered HIGH. $\overline{CS}$ provides for external Rank selection on systems with multiple Ranks. $\overline{CS}$ is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ODT          | Input            | <b>On Die Termination :</b> ODT (registered HIGH) enables termination resistance internal to the DDR3 SDRAM. When enabled, ODT is only applied to each DQ, DQS, DQS and DM. The ODT pin will be ignored if the Mode Register (MR1) is programmed to disable ODT.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RAS, CAS, WE | Input            | <b>Command Inputs</b> : $\overline{RAS}$ , $\overline{CAS}$ and $\overline{WE}$ (along with $\overline{CS}$ ) define the command being entered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DM           | Input            | <b>Input Data Mask :</b> DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BA0 - BA2    | Input            | <b>Bank Address Inputs :</b> BA0 - BA2 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines which mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A0 - A15     | Input            | Address Inputs : Provided the row address for Active commands and the column address for Read /<br>Write commands to select one location out of the memory array in the respective bank. (A10/AP and<br>A12/BC have additional functions, see below)<br>The address inputs also provide the op-code during Mode Register Set commands.                                                                                                                                                                                                                                                                                                                                                                           |

| A10 / AP     | Input            | <b>Autoprecharge</b> : A10 is sampled during Read/Write commands to determine whether Autoprecharge should be per-formed to the accessed bank after the Read/Write operation. (HIGH:Autoprecharge; LOW: No Autoprecharge)A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). if only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                                                                                                                                                       |

| A12 / BC     | Input            | <b>Burst Chop</b> : A12 is sampled during Read and Write commands to determine if burst chop(on-the-fly) will be per-formed. (HIGH : no burst chop, LOW : burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RESET        | Input            | Active Low Asynchronous Reset : Reset is active when RESET is LOW, and inactive when RESET is HIGH. RESET must be HIGH during normal operation. RESET is a CMOS rail to rail signal with DC high and low at 80% and 20% of VDD, i.e. 1.20V for DC high and 0.30V for DC low.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DQ           | Input/<br>Output | Data Input/ Output : Bi-directional data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| DQS, DQS     | Input/<br>Output | <b>Data Strobe :</b> Output with read data, input with write data. Edge-aligned with read data, centered in write data. The data strobe DQS is paired with differential signals DQS, respectively, to provide differential pair signaling to the system during reads and writes. DDR3 SDRAM supports differential data strobe only and does not support single-ended.                                                                                                                                                                                                                                                                                                                                            |

| NC           |                  | No Connect: No internal electrical connection is present.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pin    | Туре   | Function                                                                                   |

|--------|--------|--------------------------------------------------------------------------------------------|

| VDDQ   | Supply | DQ power supply: 1.35V ,1.283 - 1.45V operational; compatible to 1.5V +/- 0.075V operation |

| VSSQ   | Supply | DQ Ground                                                                                  |

| VDD    | Supply | Power Supply: 1.35V ,1.283 - 1.45V operational; compatible to 1.5V +/- 0.075V operation    |

| VSS    | Supply | Ground                                                                                     |

| VREFDQ | Supply | Reference Voltage for DQ                                                                   |

| VREFCA | Supply | Reference Voltage for CA                                                                   |

| ZQ     | Supply | Reference Pin for ZQ calibration                                                           |

NOTE : Input only pins ( BA0-BA2, A0-A15, RAS, CAS, WE, CS, CKE, ODT and RESET ) do not supply termination.

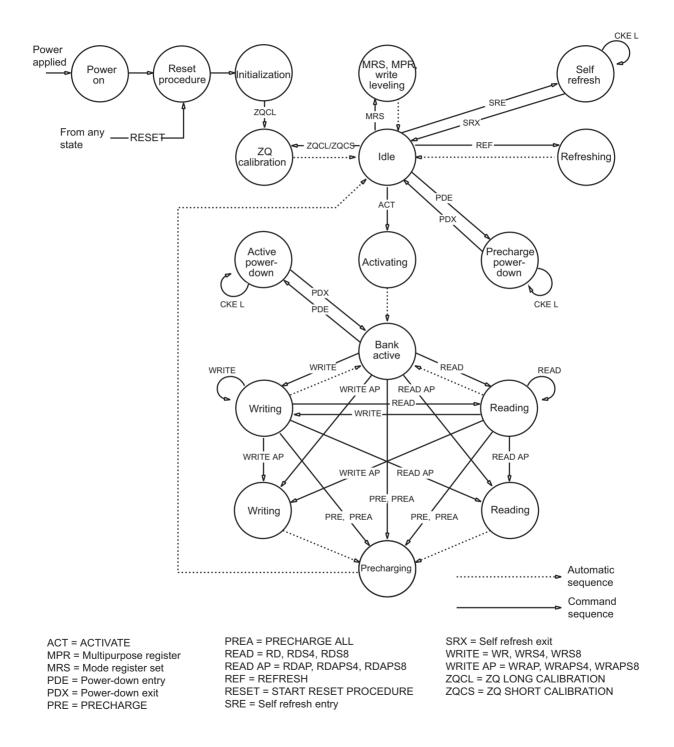

# Simplified State Diagram

### **Basic Functionality**

Read and write operation to the DDR3 SDRAM are burst oriented, start at a selected location, and continue for a burst length of four or eight in a programmed sequence. Operation begins with the registration of an Active command, which is then followed by a Read or Write command. The address bits registered coincident with the Active command are used to select the bank and row to be accessed (BA0-BA2 select the bank; A0-A15 select the row). The address bits registered coincident with the Read or Write command are used to select the starting column location for the burst operation, determine if the auto precharge command is to be issued (via A10/AP), and the select BC4 or BL8 mode "on the fly" (via A12) if enabled in the mode register.

Prior to normal operation, the DDR3 SDRAM must be powered up and initialized in a predefined manner. The following sections provide detailed information covering device reset and initialization, register definition, command descriptions and device operation.

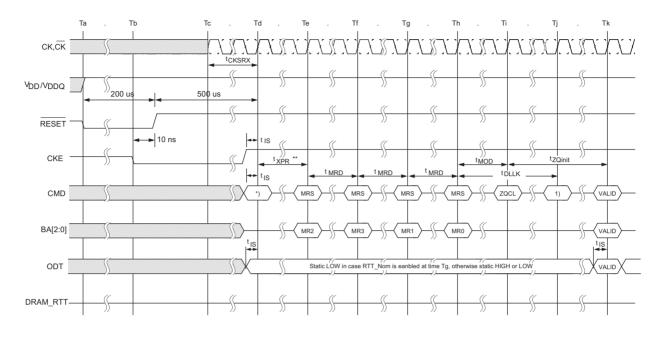

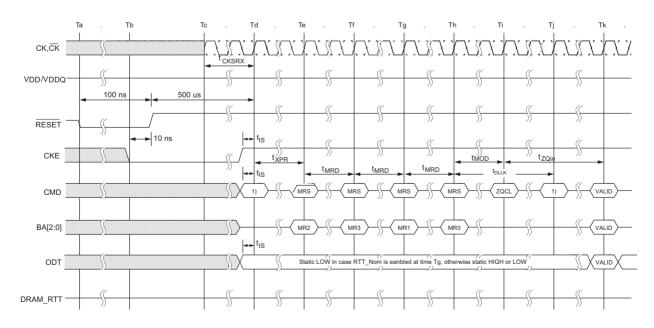

### Power-up and Initialization Sequence

The following sequence is required for POWER UP and Initialization.

- Apply power and attempt to maintain RESET below 0.2 x VDD (all other inputs may be undefined). RESET needs to be maintained for minimum 200μs with stable power. CKE is pulled "Low" anytime before RESET being de-asserted (min. time 10ns). The power voltage ramp time between 300mV to VDD min must be no longer than 200ms; and during the ramp, VDD > VDDQ and VDD - VDDQ < 0.3 volts.</li>

- VDD and VDDQ are driven from a single power converter output, AND

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side. In addition, VTT is limited to 0.95V max once power ramp is finished, AND

- Vref tracks VDDQ/2.

- or

- Apply VDD without any slope reversal before or at the same time as VDDQ.

- Apply VDDQ without any slope reversal before or at the same time as VTT & Vref.

- The voltage levels on all pins other than VDD, VDDQ, VSS, VSSQ must be less than or equal to VDDQ and VDD on one side and must be larger than or equal to VSSQ and VSS on the other side.

- 2. After RESET is de-asserted, wait for another 500us until CKE becomes active. During this time, the DRAM will start internal initialization; this will bedone independently of external clocks.

- 3. Clocks (CK, CK) need to be started and stabilized for at least 10ns or 5tCK (which is larger) before CKE goes active. Since CKE is a synchronous signal, the corresponding setup time to clock (tIS) must be met. Also a NOP or Deselect command must be registered (with tIS set up time to clock) before CKE goes active. Once the CKE registered "High" after Reset, CKE needs to be continuously registered "High" until the initialization sequence finished, including expiration of tDLLK and tZQinit.

- 4. The DDR3 SDRAM keeps its on-die termination in high-impedance state as long as RESET is asserted. Further, the SDRAM keeps its on-die termination in high impedance state after RESET deassertion until CKE is registered HIGH. The ODT input signal may be in undefined state until tIS before CKE is registered HIGH. When CKE is registered HIGH, the ODT input signal may be statically held at either LOW or HIGH. If RTT\_NOM is to be enabled in MR1 and the on-die termination is required to remain in the high impedance state, the ODT input signal must be statically held LOW. In all cases, the ODT input signal remains static until the power up initialization sequence is finished, including the expiration of tDLLK and tZQinit.

- 5. After CKE is registered high, wait minimum of Reset CKE Exit time, tXPR, before issuing the first MRS command to load mode register.(tXPR=Max(tXS, 5tCK)]

- 6. Issue MRS Command to load MR2 with all application settings. (To issue MRS command for MR2, provide "Low" to BA0 and BA2, "High" to BA1.)

- 7. Issue MRS Command to load MR3 with all application settings. (To issue MRS command for MR3, provide "Low" to BA2, "High" to BA0 and BA1.)

- 8. Issue MRS Command to load MR1 with all application settings and DLL enabled. (To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low" to BA1-BA2)

- 9. Issue MRS Command to load MR0 with all application settings and "DLL reset". (To issue DLL reset command, provide "High" to A8 and "Low" to BA0-2).

- 10. Issue ZQCL command to starting ZQ calibration.

- 11. Wait for both tDLLK and tZQ init completed.

- 12. The DDR3 SDRAM is now ready for normal operation.

1) From time point 'Td' until 'Tk', NOP or DES commands must be applied between MRS and ZQCL commands

### Reset and Initialization with Stable Power

The following sequence is required for /RESET at no power interruption initialization.

- Assert /RESET below 0.2 x VDD anytime when reset is needed (all other inputs may be undefined). /RESET needs to be maintained for minimum 100ns. CKE is pulled low before /RESET being de-asserted (minimum time 10ns).

Follow Power Up Initialization Sequence store 2 to 11

- 2. Follow Power-Up Initialization Sequence steps 2 to 11.

- 3. The reset sequence is now completed; DDR3 SDRAM is ready for normal operation.

1) From time point 'Td' until 'Tk', NOP or DES commands must be applied between MRS and ZQCL commands

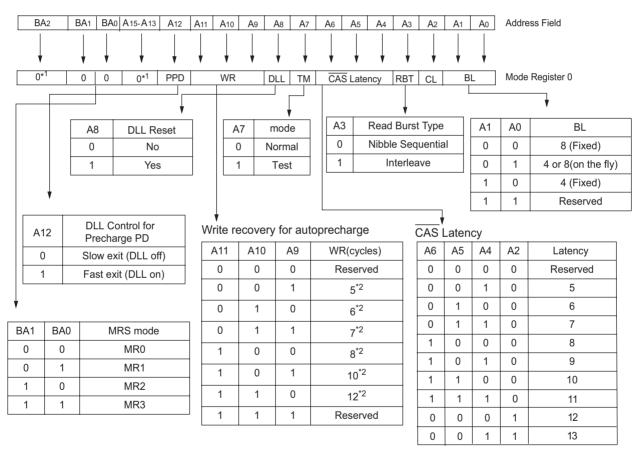

The Mode Register MR0 stores the data for controlling various operating modes of DDR3 SDRAM. It controls burst length, read burst type, CAS latency, test mode, DLL reset, WR and DLL control for precharge power-down, which include various vendor specific options to make DDR3 SDRAM useful for various applications. The mode register is written by asserting low on CS, RAS, CAS, WE, BA0, BA1 and BA2, while controlling the states of address pins according to the table below.

\*1 : BA2, A13, A14 and A15 are reserved for future use and must be programmed to 0 during MRS.

\*2 : WR(write recovery for autoprecharge)min in clock cycles is calculated by dividing tWR(in ns) by tCK(in ns) and rounding up to the next integer: WRmin[cycles] = Roundup(tWR[ns]/tCK[ns]). The WR value in the mode register must be programmed to be equal or larger than WRmin. The programmed WR value is used with tRP to determine tDAL.

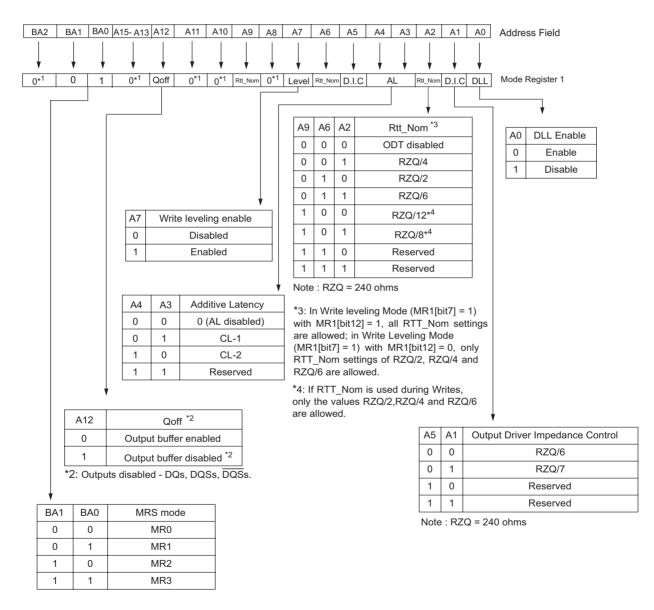

The Mode Register MR1 stores the data for enabling or disabling the DLL, output driver strength, RTT\_Nom impedance, additive latency, write leveling enable and Qoff.

The Mode Register 1 is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$ , high on BA0, low on BA1 and BA2, while controlling the states of address pins according to the table below.

\* 1 : BA2, A8, A10, A11, A13, A14 and A15 are reserved for future use (RFU) and must be programmed to 0 during MRS.

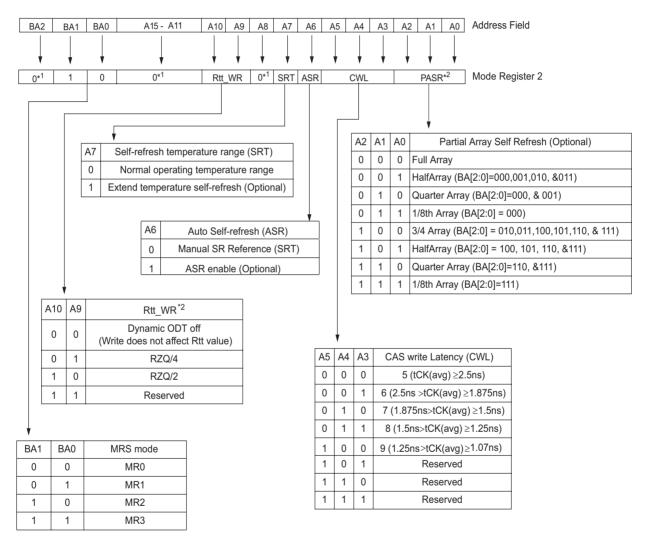

The Mode Register MR2 stores the data for controlling refresh related features, RTT\_WR impedance and CAS write latency (CWL). The Mode Register 2 is written by asserting low on CS, RAS, CAS, WE, high on BA1, low on BA0 and BA2, while controlling the states of address pins according to the table below.

\* 1 : BA2, A8, A11 ~ A15 are RFU and must be programmed to 0 during MRS.

\* 2 : The Rtt\_WR value can be applied during writes even when Rtt\_Nom is disabled.

During write leveling, Dynamic ODT is not available.

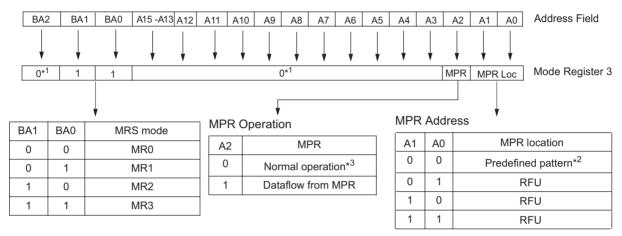

The Mode Register MR3 controls Multi Purpose Registers (MPR). The Mode Register 3 is written by asserting low on CS, RAS, CAS, WE, high on BA1 and BA0, and low on BA2 while controlling the states of address pins according to the table below.

\* 1 : BA2, A3 - A15 are reserved for future use (RFU) and must be programmed to 0 during MRS.

\* 2 : The predefined pattern will be used for read synchronization.

\* 3 : When MPR control is set for normal operation, MR3 A[2] = 0, MR3 A[1:0] will be ignored

# Burst Length (MR0)

Read and write accesses to the DDR3 are burst oriented, with the burst length being programmable, as shown in the figure MR0 Programming. The burst length determines the maximum number of column locations that can be accessed for a given read or write command. Burst length options include fixed BC4, fixed BL8, and on the fly which allows BC4 or BL8 to be selected coincident with the registration of a read on write command Via A12 (BC). Reserved states should not be used, as unknown operation or incompatibility with future versions may result.

# Burst Chop

In case of burst length being fixed to 4 by MR0 setting, the internal write operation starts two clock cycles earlier than for the BL8 mode. This means that the starting point for tWR and tWTR will be pulled in by two clocks. In case of burst length being selected on the fly via  $A12(\overline{BC})$ , the internal write operation starts at the same point in time like a burst of 8 write operation. This means that during on-the-fly control, the starting point for tWR and tWTR will not be pulled in by two clocks.

# Burst Type (MR0)

### [Burst Length and Sequence]

| Burst length   | Operation | Starting address | Sequential addressing  | Interleave addressing  |

|----------------|-----------|------------------|------------------------|------------------------|

|                |           | (A2, A1, A0)     | (decimal)              | (decimal)              |

| 4 (Burst chop) | READ      | 000              | 0, 1, 2, 3, T, T, T, T | 0, 1, 2, 3, T, T, T, T |

|                |           | 001              | 1, 2, 3, 0, T, T, T, T | 1, 0, 3, 2, T, T, T, T |

|                |           | 010              | 2, 3, 0, 1, T, T, T, T | 2, 3, 0, 1, T, T, T, T |

|                |           | 011              | 3, 0, 1, 2, T, T, T, T | 3, 2, 1, 0, T, T, T, T |

|                |           | 100              | 4, 5, 6, 7, T, T, T, T | 4, 5, 6, 7, T, T, T, T |

|                |           | 101              | 5, 6, 7, 4, T, T, T, T | 5, 4, 7, 6, T, T, T, T |

|                |           | 110              | 6, 7, 4, 5, T, T, T, T | 6, 7, 4, 5, T, T, T, T |

|                |           | 111              | 7, 4, 5, 6, T, T, T, T | 7, 6, 5, 4, T, T, T, T |

|                | WRITE     | 0VV              | 0, 1, 2, 3, X, X, X, X | 0, 1, 2, 3, X, X, X, X |

|                |           | 1VV              | 4, 5, 6, 7, X, X, X, X | 4, 5, 6, 7, X, X, X, X |

| 8              | READ      | 000              | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |

|                |           | 001              | 1, 2, 3, 0, 5, 6, 7, 4 | 1, 0, 3, 2, 5, 4, 7, 6 |

|                |           | 010              | 2, 3, 0, 1, 6, 7, 4, 5 | 2, 3, 0, 1, 6, 7, 4, 5 |

|                |           | 011              | 3, 0, 1, 2, 7, 4, 5, 6 | 3, 2, 1, 0, 7, 6, 5, 4 |

|                |           | 100              | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |

|                |           | 101              | 5, 6, 7, 4, 1, 2, 3, 0 | 5, 4, 7, 6, 1, 0, 3, 2 |

|                |           | 110              | 6, 7, 4, 5, 2, 3, 0, 1 | 6, 7, 4, 5, 2, 3, 0, 1 |

|                |           | 111              | 7, 4, 5, 6, 3, 0, 1, 2 | 7, 6, 5, 4, 3, 2, 1, 0 |

|                | WRITE     | VVV              | 0, 1, 2, 3, 4, 5, 6, 7 | 0, 1, 2, 3, 4, 5, 6, 7 |

Remark: T: Output driver for data and strobes are in high impedance.

V: A valid logic level (0 or 1), but respective buffer input ignores level on input pins.

X: Don't Care.

Notes: 1. Page length is a function of I/O organization and column addressing

2. 0...7 bit number is value of CA [2:0] that causes this bit to be the first read during a burst.

### Command Truth Table

(a) Note 1,2,3,4 apply to the entire Command truth table

(b) Note 5 applies to all Read/Write commands.

[BA=Bank Address, RA=Row Address, CA=Column Address, BC=Burst Chop, X=Don't care, V=Valid]

|                                                 |              | CI       | <Ε      |    |     |     |    | BA0 | A13 | A12    | A10    | A0     |          |

|-------------------------------------------------|--------------|----------|---------|----|-----|-----|----|-----|-----|--------|--------|--------|----------|

| Function                                        | Abbreviation | Previous | Current | CS | RAS | CAS | WE | -   | -   | /      | /      | -      | Notes    |

|                                                 |              | Cycle    | Cycle   |    |     |     |    | BA2 | A15 | BC     | AP     | A9,A11 |          |

| Mode Register Set                               | MRS          | н        | Н       | L  | L   | L   | L  | BA  |     | OF     | Code   |        |          |

| Refresh                                         | REF          | Н        | Н       | L  | L   | L   | Н  | V   | V   | V      | V      | V      |          |

| Self Refresh Entry                              | SRE          | Н        | L       | L  | L   | L   | Н  | V   | V   | V      | V      | V      | 7,9,12   |

| Self Refresh Exit                               | SRX          | L        | н       | Н  | Х   | Х   | Х  | Х   | Х   | Х      | Х      | Х      | 7,8,9,12 |

|                                                 | 0100         | L        |         | L  | н   | Н   | н  | V   | V   | V      | V      | V      | 7,0,3,12 |

| Single Bank Precharge                           | PRE          | Н        | Н       | L  | L   | Н   | L  | BA  | V   | V      | L      | V      |          |

| Precharge all Banks                             | PREA         | Н        | Н       | L  | L   | Н   | L  | V   | V   | V      | Н      | V      |          |

| Bank Activate                                   | ACT          | Н        | Н       | L  | L   | Н   | Н  | BA  |     | Row Ad | ddress | (RA)   |          |

| Write (Fixed BL8 or BL4)                        | WR           | Н        | Н       | L  | Н   | L   | L  | BA  | RFU | V      | L      | CA     |          |

| Write (BL4, on the Fly)                         | WRS4         | Н        | Н       | L  | Н   | L   | L  | BA  | RFU | L      | L      | CA     |          |

| Write (BL8, on the Fly)                         | WRS8         | Н        | Н       | L  | Н   | L   | L  | BA  | RFU | Н      | L      | CA     |          |

| Write with Auto Precharge<br>(Fixed BL8 or BL4) | WRA          | н        | Н       | L  | н   | L   | L  | BA  | RFU | V      | Н      | CA     |          |

| Write with Auto Precharge<br>(BL4, on the Fly)  | WRAS4        | н        | н       | L  | н   | L   | L  | ВА  | RFU | L      | н      | CA     |          |

| Write with Auto Precharge<br>(BL8, on the Fly)  | WRAS8        | н        | Н       | L  | н   | L   | L  | BA  | RFU | н      | н      | CA     |          |

| Read (Fixed BL8 or BL4)                         | RD           | н        | Н       | L  | н   | L   | Н  | BA  | RFU | V      | L      | CA     |          |

| Read (BL4, on the Fly)                          | RDS4         | н        | Н       | L  | н   | L   | Н  | BA  | RFU | L      | L      | CA     |          |

| Read (BL8, on the Fly)                          | RDS8         | Н        | Н       | L  | н   | L   | Н  | BA  | RFU | Н      | L      | CA     |          |

| Read with Auto Precharge<br>(Fixed BL8 or BL4)  | RDA          | н        | н       | L  | н   | L   | н  | ВА  | RFU | V      | н      | CA     |          |

| Read with Auto Precharge<br>(BL4, on the Fly)   | RDAS4        | н        | н       | L  | н   | L   | н  | ВА  | RFU | L      | н      | CA     |          |

| Read with Auto Precharge<br>(BL8, on the Fly)   | RDAS8        | н        | н       | L  | н   | L   | н  | ВА  | RFU | н      | н      | CA     |          |

| No Operation                                    | NOP          | н        | Н       | L  | н   | Н   | н  | V   | V   | V      | V      | V      | 10       |

| Device Deselected                               | DES          | н        | Н       | н  | X   | Х   | Х  | Х   | Х   | Х      | Х      | Х      | 11       |

| ZQ calibration Long                             | ZQCL         | Н        | Н       | L  | н   | Н   | L  | Х   | Х   | Х      | Н      | Х      |          |

| ZQ calibration Short                            | ZQCS         | Н        | Н       | L  | н   | Н   | L  | Х   | Х   | Х      | L      | Х      |          |

|                                                 | PDE          |          |         | L  | н   | Н   | Н  | V   | V   | V      | V      | V      | 6.10     |

| Power Down Entry                                | PDE          | Н        | L       | Н  | Х   | Х   | Х  | Х   | Х   | Х      | Х      | Х      | 6,12     |

| Power Down Exit                                 | PDX          | L        | н       | L  | Н   | Н   | Н  | V   | V   | V      | V      | V      | 6,12     |

|                                                 | FUA          |          | п       | Н  | Х   | Х   | Х  | Х   | Х   | Х      | Х      | Х      | 0,12     |

Note :

1. All DDR3 SDRAM commands are defined by states of CS, RAS, CAS, WE and CKE at the rising edge of the clock. The MSB of BA, RA, and CA are device density and configuration dependent

2. RESET is Low enable command which will be used only for asynchronous reset so must be maintained HIGH during any function.

3. Bank addresses (BA) determine which bank is to be operated upon. For (E)MRS BA selects an (Extended) Mode Register

4. "V" means "H or L (but a defined logic level)" and "X" means either "defined or undefined (like floating) logic level"

5. Burst reads or writes cannot be terminated or interrupted and Fixed/on the fly BL will be defined by MRS

6. The Power Down Mode does not perform any refresh operations.

7. The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh.

8. Self refresh exit is asynchronous.

9.  $V_{\text{REF}}(\text{Both } V_{\text{REFDQ}} \text{ and } V_{\text{REFCA}})$  must be maintained during Self Refresh operation.

10. The No Operation command (NOP) should be used in cases when the DDR3 SDRAM is in an idle or a wait state. The purpose of the No Operation command (NOP) is to prevent the DDR3 SDRAM from registering any unwanted commands between operations. A No Operation command will not terminate a previous operation that is still executing, such as a burst read or write cycle.

11. The Deselect command performs the same function as a No Operation command.

12. Refer to the CKE Truth Table for more detail with CKE transition

### CKE Truth Table

(a) Note 1~7 apply to the entire Command truth table

(b) CKE low is allowed only if tMRD and tMOD are satisfied

|                            | CKE                                                                           |                                   | Command (N) <sup>3</sup> |                            |                |  |  |

|----------------------------|-------------------------------------------------------------------------------|-----------------------------------|--------------------------|----------------------------|----------------|--|--|

| Current State <sup>2</sup> | Previous Cycle <sup>1</sup><br>(N-1)                                          | Current Cycle <sup>1</sup><br>(N) | RAS, CAS, WE, CS         | Action (N) <sup>3</sup>    | Notes          |  |  |

| Power Down                 | L                                                                             | L                                 | Х                        | Maintain Power-Down        | 14, 15         |  |  |

| Fower Down                 | L                                                                             | Н                                 | DESELECT or NOP          | Power Down Exit            | 11, 14         |  |  |

| Self Refresh               | L                                                                             | L                                 | Х                        | Maintain Self Refresh      | 15, 16         |  |  |

| Sell Reliesh               | L                                                                             | Н                                 | DESELECT or NOP          | Self Refresh Exit          | 8, 12, 16      |  |  |

| Bank(s) Active             | Н                                                                             | L                                 | DESELECT or NOP          | Active Power Down Entry    | 11, 13, 14     |  |  |

| Reading                    | Н                                                                             | L                                 | DESELECT or NOP          | Power Down Entry           | 11, 13, 14, 17 |  |  |

| Writing                    | Н                                                                             | L                                 | DESELECT or NOP          | Power Down Entry           | 11, 13, 14, 17 |  |  |

| Precharging                | Н                                                                             | L                                 | DESELECT or NOP          | Power Down Entry           | 11, 13, 14, 17 |  |  |

| Refreshing                 | Н                                                                             | L                                 | DESELECT or NOP          | Precharge Power Down Entry | 11             |  |  |

| All Ponko Idio             | Н                                                                             | L                                 | DESELECT or NOP          | Precharge Power Down Entry | 11,13, 14, 18  |  |  |

| All Banks Idle             | Н                                                                             | L                                 | REFRESH                  | Self Refresh Entry         | 9, 13, 18      |  |  |

|                            | For more details with all signals See "Command Truth Table," on previous page |                                   |                          |                            |                |  |  |

Notes:

- 1. CKE (N) is the logic state of CKE at clock edge N; CKE (N–1) was the state of CKE at the previous clock edge.

- 2. Current state is defined as the state of the DDR3 SDRAM immediately prior to clock edge N

- 3. COMMAND (N) is the command registered at clock edge N, and ACTION (N) is a result of COMMAND (N), ODT is not included here

- 4. All states and sequences not shown are illegal or reserved unless explicitly described elsewhere in this document

- 5. The state of ODT does not affect the states described in this table. The ODT function is not available during Self Refresh

- 6. CKE must be registered with the same value on tCKEmin consecutive positive clock edges. CKE must remain at the valid input level the entire time it takes to achieve the tCKEmin clocks of registeration. Thus, after any CKE transition, CKE may not transition from its valid level during the time period of tIS + tCKEmin + tIH.

- 7. DESELECT and NOP are defined in the Command truth table

- 8. On Self Refresh Exit DESELECT or NOP commands must be issued on every clock edge occurring during the tXS period. Read or ODT commands may be issued only after tXSDLL is satisfied.

- 9. Self Refresh mode can only be entered from the All Banks Idle state.

- 10. Must be a legal command as defined in the Command Truth Table.

- 11. Valid commands for Power Down Entry and Exit are NOP and DESELECT only.

- 12. Valid commands for Self Refresh Exit are NOP and DESELECT only.

- 13. Self Refresh can not be entered while Read or Write operations. See 'Self-Refresh Operation" and 'Power-Down Modes" on later section for a detailed list of restrictions.

- 14. The Power Down does not perform any refresh operations.

- 15. "X" means "don't care (including floating around V<sub>REF</sub>)" in Self Refresh and Power Down. It also applies to Address pins

- 16. V<sub>REF</sub> (Both V<sub>REFDQ</sub> and V<sub>REFCA</sub>) must be maintained during Self Refresh operation.

- 17. If all banks are closed at the conclusion of the read, write or precharge command, then Precharge Power Down is entered, otherwise Active Power Down is entered

- 18. 'Idle state' means that all banks are closed(tRP,tDAL,etc. satisfied) and CKE is high and all timings from previous operations are satisfied (tMRD,tMOD,tRFC,tZQinit,tZQOper,tZQCS,etc) as well as all SRF exit and Power Down exit parameters are satisfied (tXS,tXP,tXPDLL,etc)

### Absolute Maximum DC Ratings

| Symbol           | Parameter                           | Rating         | Units | Notes |

|------------------|-------------------------------------|----------------|-------|-------|

| VDD              | Voltage on VDD pin relative to Vss  | -0.4 V ~ 1.8 V | V     | 1,3   |

| VDDQ             | Voltage on VDDQ pin relative to Vss | -0.4 V ~ 1.8 V | V     | 1,3   |

| Vin, Vout        | Voltage on any pin relative to Vss  | -0.4 V ~ 1.8V  | V     | 1     |

| T <sub>STG</sub> | Storage Temperature                 | -55 to +150    | °C    | 1,2   |

NOTE :

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 3. VDD and VDDQ must be within 300mV of each other at all times;and VREF must be not greater than 0.6 x VDDQ, When VDD and VDDQ are less than 500mV; VREF may be equal to or less than 300mV.

### **Operating Temperature Condition**

| Symbol         | Parameter                               | Rating      | Units | Notes |

|----------------|-----------------------------------------|-------------|-------|-------|

| T <sub>C</sub> | Operating case temperature - Commercial | 0 to +95    | °C    | 1,2,3 |

| T <sub>C</sub> | Operating case temperature - Industrial | -40 to +95  | °C    | 1,2,3 |

| T <sub>C</sub> | Operating case temperature - Automotive | -40 to +105 | °C    | 1,2,3 |

NOTE :

- 1. Operating temperature is the case surface temperature on the center/top side of the DRAM.

- 2. The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be maintained between 0°C to +85°C under all operating conditions.

- 3. Some applications require operation of the DRAM in the Extended Temperature Range between +85°C and +95°C case temperature. Full specifications are guaranteed in this range, but the following additional conditions apply:

- a) Refresh commands must be doubled in frequency, therefore reducing the refresh interval tREFI to  $3.9\mu s$ . (This double refresh requirement may not apply for some devices.)

- b) If Self-refresh operation is required in the Extended Temperature Range, then it is mandatory to either use the Manual Self-Refresh mode with Extended Temperature Range capability (MR2 bit [A6, A7] = [0, 1]) or enable the optional Auto Self-Refresh mode (MR2 bit [A6, A7] = [1, 0]).

### **Recommended DC Operating Conditions**

|        |                           | Rating |      |      |       |       |

|--------|---------------------------|--------|------|------|-------|-------|

| Symbol | Parameter                 | Min.   | Тур. | Max. | Units | Notes |

| VDD    | Supply voltage            | 1.283  | 1.35 | 1.45 | V     | 1,2,3 |

| VDDQ   | Supply voltage for Output | 1.283  | 1.35 | 1.45 | V     | 1,2,3 |

NOTE :

1. Under all conditions VDDQ must be less than or equal to VDD.

2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together.

3. Under 1.5V operation, this DDR3L device operates in accordance with the DDR3 specifications under the same speed timings as defined for this device.

# AC and DC Input Measurement Levels

# Single-Ended AC and DC Input Levels for Command and Address(1.35V)

| Symbol        | Parameter                                | Min.         | Min. Max.    |   | Notes |

|---------------|------------------------------------------|--------------|--------------|---|-------|

| VIHCA (DC90)  | DC input logic high                      | VREF + 0.090 | VDD          | V | 1     |

| VILCA (DC90)  | DC input logic low                       | VSS          | VREF - 0.090 | V | 1     |

| VIHCA (AC160) | AC input logic high                      | -            | -            | V | 1,2   |

| VILCA (AC160) | AC input logic low                       | -            | -            | V | 1,2   |

| VIHCA (AC135) | AC input logic high                      | -            | -            | V | 1,2   |

| VILCA (AC135) | AC input logic low                       | -            | -            | V | 1,2   |

| VIHCA (AC125) | AC input logic high                      | VREF + 0.125 | -            | V | 1,2   |

| VILCA (AC125) | AC input logic low                       | -            | VREF - 0.125 | V | 1,2   |

| VREFCA (DC)   | Reference voltage for<br>ADD, CMD inputs | 0.49 * VDD   | 0.51 * VDD   | V | 3,4   |

NOTE :

- 1. For input only pins except /RESET : VREF = VREFCA (DC).

- 2. See Overshoot and Undershoot Specifications section.

- 3. The AC peak noise on VREF may not allow VREF to deviate from VREFCA (DC) by more than ±1% VDD (for reference : approx. ±15 mV).

- 4. For reference : approx. VDD/2 ±15 mV.

# Single-Ended AC and DC Input Levels for DQ and DM(1.35V)

| Symbol        | Parameter                              | Min. Max.    |              | Units | Notes |

|---------------|----------------------------------------|--------------|--------------|-------|-------|

| VIHDQ (DC90)  | DC input logic high                    | VREF + 0.090 | VDD          | V     | 1     |

| VILDQ (DC90)  | DC input logic low                     | VSS          | VREF - 0.090 | V     | 1     |

| VIHDQ (AC160) | AC input logic high                    | -            | -            | V     | 1,2   |

| VILDQ (AC160) | AC input logic low                     |              |              | V     | 1,2   |

| VIHDQ (AC135) | AC input logic high                    | -            | -            | V     | 1,2   |

| VILDQ (AC135) | AC input logic low                     | -            | -            | V     | 1,2   |

| VIHDQ (AC130) | AC input logic high                    | VREF + 0.130 | -            | V     | 1,2   |

| VILDQ (AC130) | AC input logic low                     | -            | VREF - 0.130 | V     | 1,2   |

| VREFDQ (DC)   | Reference voltage for<br>DQ, DM inputs | 0.49 * VDD   | 0.51 * VDD   | V     | 3,4   |

NOTE :

1. For DQ and DM : VREF = VREFDQ (DC).

2. See Overshoot and Undershoot Specifications section.

3. The AC peak noise on VREF may not allow VREF to deviate from VREFDQ (DC) by more than ±1% VDD (for reference: approx. ±15 mV).

4. For reference: approx. VDD/2 ±15 mV.

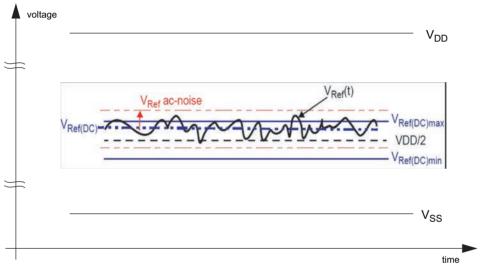

### VREF Tolerances

The dc-tolerance limits and ac-noise limits for the reference voltages VREFCA and VREFDQ are illustrated in figure VREF(DC) tolerance and VREF AC-Noise limits. It shows a valid reference voltage VREF(t) as a function of time. (VREF stands for VREFCA and VREFDQ likewise).

VREF(DC) is the linear average of VREF(t) over a very long period of time (e.g. 1 sec). This average has to meet the min/max requirement in Table of "Single-Ended AC and DC Input Levels for Command and Address". Furthermore VREF(t) may temporarily deviate from VREF(DC) by no more than +/- 1% VDD.

VREF(DC) tolerance and VREF AC-Noise limits

The voltage levels for setup and hold time measurements VIH(AC), VIH(DC), VIL(AC) and VIL(DC) are dependent on VREF.

"VREF" shall be understood as VREF(DC), as defined in figure above, VREF(DC) tolerance and VREF AC-Noise limits.

This clarifies, that DC-variations of VREF affect the absolute voltage a signal has to reach to achieve a valid high or low level and therefore the time to which setup and hold is measured. System timing and voltage budgets need to account for VREF(DC) deviations from the optimum position within the data-eye of the input signals.

This also clarifies that the DRAM setup/hold specification and derating values need to include time and voltage associated with VREF AC-noise. Timing and voltage effects due to AC-noise on VREF up to the specified limit (+/- 1% of VDD) are included in DRAM timings and their associated deratings.

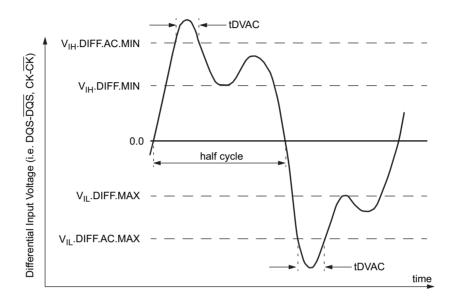

### AC and DC Logic Input Levels for Differential Signals

### Differential signals definition

Definition of differential ac-swing and "time above ac level" tDVAC

# Differential swing requirement for clock (CK - $\overline{CK}$ ) and strobe (DQS - $\overline{DQS}$ )

#### Differential AC and DC Input Levels

| Symbol      | Parameter                  | Min.                        | Min. Max.            |   | Notes |

|-------------|----------------------------|-----------------------------|----------------------|---|-------|

| VIHdiff     | Differential input high    | +0.18                       | NOTE 3               | V | 1     |

| VILdiff     | Differential input low     | tial input low NOTE 3 -0.18 |                      | V | 1     |

| VIHdiff(AC) | Differential input high AC | 2 x (VIH(AC) - VREF)        | NOTE 3               | V | 2     |

| VILdiff(AC) | Differential input low AC  | NOTE 3                      | 2 x (VIL(AC) - VREF) | V | 2     |

NOTE :

1. Used to define a differential signal slew-rate.

- 2. for CK CK use VIH/VIL(AC) of address/command and VREFCA; for strobes (DQS, DQS) use VIH/VIL(AC) of DQs and VREFDQ; if a reduced ac-high or ac-low level is used for a signal group, then the reduced level applies also here.

- 3. These values are not defined, however the single-ended signals CK, CK, DQS, DQS need to be within the respective limits (VIH(DC) max, VIL(DC)min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot specification".

| Slow Poto N/mol  | tDVAC [ps] @  VIH | l/Ldiff(AC)  = 320mV | tDVAC [ps] @  VIH/Ldiff(AC)  = 270 |      |  |

|------------------|-------------------|----------------------|------------------------------------|------|--|

| Slew Rate [V/ns] | Min.              | Max.                 | Min.                               | Max. |  |

| > 4.0            | 189               | -                    | 201                                | -    |  |

| 4.0              | 189               | -                    | 201                                | -    |  |

| 3.0              | 162               | -                    | 179                                | -    |  |

| 2.0              | 109               | -                    | 134                                | -    |  |

| 1.8              | 91                | -                    | 119                                | -    |  |

| 1.6              | 69                | -                    | 100                                | -    |  |

| 1.4              | 40                | -                    | 76                                 | -    |  |

| 1.2              | -                 | -                    | 44                                 | -    |  |

| 1.0              | -                 | -                    | -                                  | -    |  |

| < 1.0            | -                 | -                    | -                                  | -    |  |

# Allowed time before ringback (tDVAC) for CK - CK and DQS - DQS

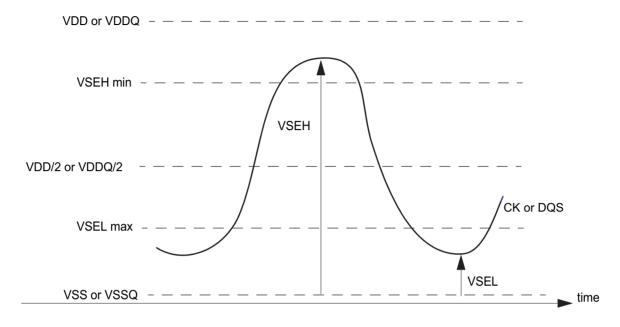

### Single-ended requirements for differential signals

Each individual component of a differential signal (CK, DQS,  $\overline{CK}$ ,  $\overline{DQS}$ ) has also to comply with certain requirements for single-ended signals.

CK and  $\overline{CK}$  have to approximately reach VSEH min / VSEL max [ approximately equal to the AC-levels (VIH(AC) / VIL(AC) ) for Address/command signals ] in every half-cycle.

DQS, DQS have to reach VSEH min / VSEL max [ approximately the ac-levels ( VIH(AC) / VIL(AC) ) for DQ signals ] in every half-cycle proceeding and following a valid transition.

Note that the applicable AC-levels for Address/command and DQ's might be different per speed-bin etc. E.g. if VIH150(AC) / VIL150(AC) is used for Address/command signals, then these AC-levels apply also for the single-ended components of differential CK and CK.

Single-ended requirement for differential signals

Note that while Address/command and DQ signal requirements are with respect to VREF, the single-ended components of differential signals have a requirement with respect to VDD/2; this is nominally the same. The transition of single-ended signals through the AC-levels is used to measure setup time. For single-ended components of differential signals the requirement to reach VSEL max, VSEH min has no bearing on timing, but adds a restriction on the common mode characteristics of these signals.

| Symbol | Parameter                                             | Min.            | Max.            | Units | Notes |

|--------|-------------------------------------------------------|-----------------|-----------------|-------|-------|

| VSEH   | Single-ended high-level for strobes                   | (VDD/2) + 0.175 | NOTE 3          | V     | 1,2   |

| VSEH   | Single-ended high-level for CK, $\overline{CK}$       | (VDD/2) + 0.175 | NOTE 3          | V     | 1,2   |

| VSEI   | Single-ended low-level for strobes                    | NOTE 3          | (VDD/2) - 0.175 | V     | 1,2   |

| VSEL   | Single-ended low-level for CK, $\overline{\text{CK}}$ | NOTE 3          | (VDD/2) - 0.175 | V     | 1,2   |

# Single-ended levels for CK, DQS, $\overline{CK}$ , $\overline{DQS}$

NOTE :

1. For CK, CK use VIH/VIL(AC) of address/command; for strobes (DQS, DQS) use VIH/VIL(AC) of DQs.

- 2. VIH(AC)/VIL(AC) for DQs is based on VREFDQ; VIH(AC)/VIL(AC) for address/command is based on VREFCA; if a reduced AC-high or AC-low level is used for a signal group, then the reduced level applies also here.

- 3. These values are not defined, however the single-ended components of differential signals CK, CK, DQS, DQS need to be within the respective limits (VIH(DC) max, VIL(DC) min) for single-ended signals as well as the limitations for overshoot and undershoot. Refer to "Overshoot and Undershoot specifications".

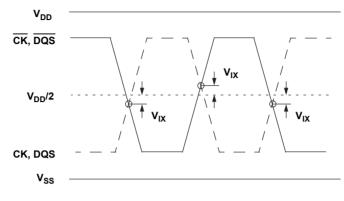

To guarantee tight setup and hold times as well as output skew parameters with respect to clock and strobe, each cross point voltage of differential input signals (CK, CK and DQS, DQS) must meet the requirements in below table. The differential input cross point voltage VIX is measured from the actual cross point of true and complement signal to the mid level between of VDD and VSS.

VIX Definition

### Cross point voltage for differential input signals ( CK, DQS )

| Symbol                             | Parameter                                                               |      | Max. | Units | Notes |

|------------------------------------|-------------------------------------------------------------------------|------|------|-------|-------|

| VIX                                | VIX Differential Input Cross Point Voltage relative to VDD/2 for CK, CK |      | 150  | mV    |       |

| VIX Differential input Cross Point | Differential input cross Foint voltage relative to VDD/2 for CK, CK     | -175 | 175  | mV    | 1     |

| VIX                                | Differential Input Cross Point Voltage relative to VDD/2 for DQS, DQS   |      | 150  | mV    |       |

NOTE :1. Extended range for VIX is only allowed for clock and if single-ended clock input signals CKand CK are monotonic, have a single-ended swing VSEL / VSEH of at least VDD/2 +/- 250 mV, and the differential slew rate of CK-CK is larger than 3 V/ ns. Refer to the table of Cross point voltage for differential input signals (CK, DQS) for VSEL and VSEH standard values.

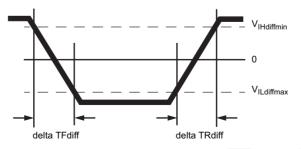

### Differential input slew rate definition

| Description                                                                                                                 | Meas          | sured         | Defined by                                           |

|-----------------------------------------------------------------------------------------------------------------------------|---------------|---------------|------------------------------------------------------|

| Description                                                                                                                 | From          | То            | Denned by                                            |

| Differential input slew rate for rising edge ( CK- $\overline{\text{CK}}$ and DQS- $\overline{\text{DQS}}$ )                | VILdiff (max) | VIHdiff (min) | <u>VIHdiff (min) - VILdiff (max)</u><br>Delta TRdiff |

| Differential input slew rate for falling edge ( $CK\operatorname{-}\overline{CK}$ and $DQS\operatorname{-}\overline{DQS}$ ) | VIHdiff (min) | VILdiff (max) | <u>VIHdiff (min) - VILdiff (max)</u><br>Delta TFdiff |

NOTE : The differential signal (i.e. CK -  $\overline{CK}$  and DQS -  $\overline{DQS}$ ) must be linear between these thresholds.

Differential Input Slew Rate definition for DQS, DQS, and CK, CK

# AC and DC Output Measurement Levels

#### Single-ended AC & DC Output Levels

| Symbol  | Parameter                                                 | DDR3-1866        | Units | Notes |

|---------|-----------------------------------------------------------|------------------|-------|-------|

| VOH(DC) | DC output high measurement level (for IV curve linearity) | 0.8 x VDDQ       | V     |       |

| VOM(DC) | DC output mid measurement level (for IV curve linearity)  | 0.5 x VDDQ       | V     |       |

| VOL(DC) | DC output low measurement level (for IV curve linearity)  | 0.2 x VDDQ       | V     |       |

| VOH(AC) | AC output high measurement level (for output SR)          | VTT + 0.1 x VDDQ | V     | 1     |

| VOL(AC) | AC output low measurement level (for output SR)           | VTT - 0.1 x VDDQ | V     | 1     |

NOTE : 1. The swing of +/-0.1 x VDDQ is based on approximately 50% of the static single ended output high or low swing with a driver impedance of  $40\Omega$  and an effective test load of  $25\Omega$  to VTT=VDDQ/2.

#### **Differential AC & DC Output Levels**

| Symbol      | Parameter                                                    | DDR3-1866   | Units | Notes |

|-------------|--------------------------------------------------------------|-------------|-------|-------|

| VOHdiff(AC) | AC differential output high measurement level (for outputSR) | +0.2 x VDDQ | V     | 1     |

| VOLdiff(AC) | AC differential output low measurement level (for output SR) | -0.2 x VDDQ | V     | 1     |

NOTE : 1. The swing of +/-0.2xVDDQ is based on approximately 50% of the static single ended output high or low swing with a driver impedance of  $40\Omega$  and an effective test load of  $25\Omega$  to VTT=VDDQ/2 at each of the differential outputs.

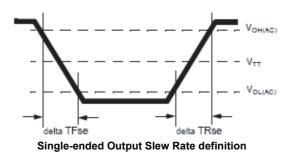

#### Single-ended Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOL(AC) and VOH(AC) for single ended signals.

|                                                | Meas    | sured   |                                      |

|------------------------------------------------|---------|---------|--------------------------------------|

| Description                                    | From    | То      | Defined by                           |

| Single ended output slew rate for rising edge  | VOL(AC) | VOH(AC) | <u>VOH(AC)-VOL(AC)</u><br>Delta TRse |

| Single ended output slew rate for falling edge | VOH(AC) | VOL(AC) | <u>VOH(AC)-VOL(AC)</u><br>Delta TRse |

NOTE : Output slew rate is verified by design and characterization, and may not be subject to production test.

| Parameter                        | Symbol | DDR3 | Units |       |

|----------------------------------|--------|------|-------|-------|

|                                  |        | Min  | Max   | Units |

| Single ended output<br>slew rate | SRQse  | TBD  | TBD   | V/ns  |

Description : SR : Slew Rate

Q : Query Output (like in DQ, which stands for Data-in, Query-Output)

se : Single-ended Signals For Ron = RZQ/7 setting

NOTE : (1) In two cased, a maximum slew rate of 6V/ns applies for a single DQ signal within a byte lane.

- Case\_1 is defined for a single DQ signal within a byte lane which is switching into a certain direction (either from high to low of low to high) while all remaining DQ signals in the same byte lane are static (i.e they stay at either high or low).

- Case\_2 is defined for a single DQ signals in the same byte lane are switching into the opposite direction (i.e. from low to high or high to low respectively). For the remaining DQ signal switching into the opposite direction, the regular maximum limit of 5 V/ns applies.

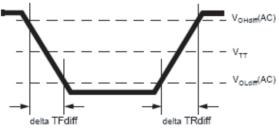

#### Differential Output Slew Rate

With the reference load for timing measurements, output slew rate for falling and rising edges is defined and measured between VOLdiff(AC) and VOH-diff(AC) for differential signals.

| Description                                    | Meas        | sured       | Defined by                                      |

|------------------------------------------------|-------------|-------------|-------------------------------------------------|

| Description                                    | From        | То          | Denned by                                       |

| Differential output slew rate for rising edge  | VOLdiff(AC) | VOHdiff(AC) | <u>VOHdiff(AC)-VOLdiff(AC)</u><br>Delta TRdiff  |

| Differential output slew rate for falling edge | VOHdiff(AC) | VOLdiff(AC) | <u>VOHdiff(AC)-VOLdiff(AC))</u><br>Delta TFdiff |

NOTE : Output slew rate is verified by design and characterization, and may not be subject to production test.

**Differential Output Slew Rate definition**

|                               |         | DDR3-1866 |     | Units |

|-------------------------------|---------|-----------|-----|-------|

| Parameter                     | Symbol  | Min       | Мах | Units |

| Differential output slew rate | SRQdiff | TBD       | TBD | V/ns  |

Description : SR : Slew Rate

Q : Query Output (like in DQ, which stands for Data-in, Query-Output) diff : Differential Signals

For Ron = RZQ/7 setting

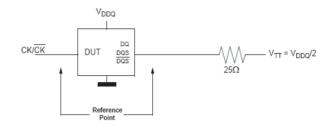

#### Reference Load for AC Timing and Output Slew Rate

Figure represents the effective reference load of 25 ohms used in defining the relevant AC timing parameters of the device as well as output slew rate measurements.

It is not intended as a precise representation of any particular system environment or a depiction of the actual load presented by a production tester. System designers should use IBIS or other simulation tools to correlate the timing reference load to a system environment. Manufacturers correlate to their production test conditions, generally one or more coaxial transmission lines terminated at the tester electronics.

Reference Load for AC Timing and Output Slew Rate

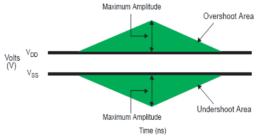

#### **Overshoot/Undershoot Specification**

#### Address and Control Overshoot and Undershoot specifications

| Parameter                                          | Specification | Unit |

|----------------------------------------------------|---------------|------|

| i arameter                                         | DDR3-1866     | onic |

| Maximum peak amplitude allowed for overshoot area  | 0.4V          | V    |

| Maximum peak amplitude allowed for undershoot area | 0.4V          | V    |

| Maximum overshoot area above VDD                   | 0.28V-ns      | V-ns |

| Maximum undershoot area below VSS                  | 0.28V-ns      | V-ns |

Address and Control Overshoot and Undershoot Definition

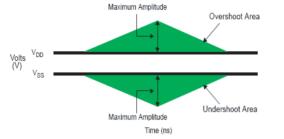

# Clock, Data, Strobe and Mask Overshoot and Undershoot Specifications

| Parameter                                          | Specification | Unit |

|----------------------------------------------------|---------------|------|

| i di dificici                                      | DDR3-1866     | Onit |

| Maximum peak amplitude allowed for overshoot area  | 0.4V          | V    |

| Maximum peak amplitude allowed for undershoot area | 0.4V          | V    |

| Maximum overshoot area above VDD                   | 0.11V-ns      | V-ns |

| Maximum undershoot area below VSS                  | 0.11V-ns      | V-ns |

Clock, Data, Strobe, Mask Overshoot and Undershoot Definition

# IDD Specification

# ( VDD = 1.35V±0.075V; VDDQ =1.35V±0.075V )

| Conditions                                                                                                                                                                                                                                                                                                                                                                                                              | Symbol | IDD max. | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|------|

| <b>Operating One Bank Active-Precharge Current;</b> CKE: High; External clock: On; tCK, nRC, nRAS, CL: see timing used table; BL: 8; AL: 0; $\overline{CS}$ : High between ACT and PRE; Command, Address: partially toggling; Data IO: FLOATING; DM:stable at 0; Bank Activity: Cycling with one bank active at a time; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                       | IDD0   | 96       | mA   |

| <b>Operating One Bank Active-Read-Precharge Current;</b> CKE: High; External clock: On;<br>tCK, nRC, nRAS, nRCD, CL: see timing used table; BL: 81; AL: 0; $\overline{CS}$ : High between ACT,<br>RD and PRE; Command, Address, Data IO: partially toggling; DM:stable at 0; Bank Activ-<br>ity: Cycling with one bank active at a time; Output Buffer and RTT: Enabled in Mode Reg-<br>isters; ODT Signal: stable at 0 | IDD1   | 125      | mA   |

| <b>Precharge Power-Down Current Slow Exit;</b> CKE: Low; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; $\overline{CS}$ : stable at 1; Command, Address: stable at 0; Data IO: FLOATING; DM: stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0; Pre-charge Power Down Mode: Slow Exit                                          | IDD2P0 | 16       | mA   |

| <b>Precharge Power-Down Current Fast Exit;</b> CKE: Low; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; $\overline{CS}$ : stable at 1; Command, Address: stable at 0; Data IO: FLOATING; DM:stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0; Pre-charge Power Down Mode: Fast Exit                                           | IDD2P1 | 30       | mA   |

| <b>Precharge Standby Current;</b> CKE: High; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; CS: stable at 1; Command, Address: partially toggling; Data IO: FLOATING; DM:stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                                                                                                     | IDD2N  | 50       | mA   |

| Precharge Standby ODT Current; CKE: High; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; CS: stable at 1; Command, Address: partially toggling; Data IO:<br>FLOATING; DM:stable at 0; Bank Activity: all banks closed; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: toggling                                                                                                        | IDD2NT | 58       | mA   |

| Precharge Quiet Standby Current; CKE: High; External clock: On; tCK, CL: see timing used table;                                                                                                                                                                                                                                                                                                                         | IDD2Q  | 50       | mA   |

| Active Power-Down Current; CKE: Low; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; CS: stable at 1; Command, Address: stable at 0; Data IO: FLOATING; DM: stable at 0; Bank Activity: all banks open; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                                                                                                                     | IDD3P  | 54       | mA   |

| Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Symbol | IDD max. | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|------|

| Active Standby Current; CKE: High; External clock: On; tCK, CL: see timing used table;<br>BL: 8; AL: 0; CS: stable at 1; Command, Address: partially toggling; Data IO: FLOATING;<br>DM: stable at 0; Bank Activity: all banks open; Output Buffer and RTT: Enabled in Mode<br>Registers; ODT Signal: stable at 0                                                                                                                                                                                                | IDD3N  | 62       | mA   |

| <b>Operating Burst Read Current;</b> CKE: High; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; $\overline{CS}$ : High between RD; Command, Address: par-tially toggling; Data IO: seamless read data burst with different data between one burst and the next one; DM: stable at 0; Bank Activity: all banks open, RD commands cycling through banks: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                                                 | IDD4R  | 200      | mA   |

| <b>Operating Burst Write Current;</b> CKE: High; External clock: On; tCK, CL: see timing used table; BL: 8; AL: 0; $\overline{CS}$ : High between WR; Command, Address: partially toggling; Data IO: seamless write data burst with different data between one burst and the next one; DM: stable at 0; Bank Activity: all banks open, WR commands cycling through banks: 0,0,1,1,2,2,; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at HIGH                                             | IDD4W  | 360      | mA   |

| <b>Burst Refresh Current;</b> CKE: High; External clock: On; tCK, CL, nRFC: see timing used table; BL: 8; AL: 0; CS: High between REF; Command, Address: partially toggling; Data IO: FLOATING; DM:stable at 0; Bank Activity: REF command every nRFC; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0                                                                                                                                                                                 | IDD5B  | 477      | mA   |

| Self Refresh Current: Normal Temperature Range; TCASE: 0- 85°C; Auto Self-Re-<br>fresh (ASR): Disabled; Self-Refresh Temperature Range (SRT): Normal; CKE: Low; Ex-<br>ternal clock: Off; CK and CK: LOW; CL: see timing used table; BL: 8; AL: 0; CS,<br>Command, Address, Data IO: FLOATING; DM: stable at 0; Bank Activity: Self-Refresh op-<br>eration; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: FLOATING                                                                               | IDD6   | 24       | mA   |

| Self Refresh Current: Extended Temperature Range; TCASE: 0- 95°C; Auto Self-<br>Re-<br>fresh (ASR): Disabled; Self-Refresh Temperature Range (SRT): Extended; CKE: Low; Ex-<br>ternal clock: Off; CK and CK: LOW; CL: see timing used table; BL: 8; AL: 0; CS,<br>Command, Address, Data IO: FLOATING; DM: stable at 0; Bank Activity: Extended Tem<br>perature Self-Refresh operation; Output Buffer and RTT: Enabled in Mode Registers;<br>ODT Signal: FLOATING                                                | IDD6ET | 32       | mA   |

| <b>Operating Bank Interleave Read Current;</b> CKE: High; External clock: On; tCK, nRC, nRAS, nRCD, nRRD, nFAW, CL: see timing used table; BL: 8; AL: CL-1; CS: High be-<br>tween ACT and RDA; Command, Address: partially toggling; Data IO: read data bursts with different data between one burst and the next one; DM: stable at 0; Bank Activity: two times interleaved cycling through banks (0, 1,7) with different addressing; Output Buffer and RTT: Enabled in Mode Registers; ODT Signal: stable at 0 | IDD7   | 270      | mA   |

| <b>RESET Low Current;</b> RESET: Low; External clock: off; CK and CK: LOW; CKE: FLOAT-<br>ING; CS, Command, Address, Data IO: FLOATING; ODT Signal : FLOATING                                                                                                                                                                                                                                                                                                                                                    | IDD8   | 20       | mA   |

#### NOTE :

1) Burst Length: BL8 fixed by MRS: set MR0 A[1,0]=00B

2) Output Buffer Enable: set MR1 A[12] = 0B; set MR1 A[5,1] = 01B; RTT\_Nom enable: set MR1 A[9,6,2] = 011B; RTT\_Wr enable: set MR2 A[10,9] = 10B