### **Datasheet**

DS000686

# **AS5116**

**On-Axis Magnetic Position Sensor with Analog Sine-Cosine Outputs**

v3-01 • 2021-May-07

## **Content Guide**

| 1          | General Description                      | . 3    |

|------------|------------------------------------------|--------|

| 1.1<br>1.2 | Key Benefits & FeaturesApplications      | 3      |

| 1.3        | Block Diagram                            | 4      |

| 2          | Ordering Information                     | . 5    |

| 3          | Pin Assignment                           | . 6    |

| 3.1<br>3.2 | Pin Diagram AS5116Pin Description AS5116 | 6<br>6 |

| 4          | Absolute Maximum Ratings                 | . 7    |

| 5          | Electrical Characteristics               | . 8    |

| 6          | Functional Description                   | 11     |

| 6.1<br>6.2 | IC Power ManagementGain Configuration    | 12     |

| 6.3        | Behavior of Sensor Outputs               | 13     |

| 7          | Digital Interface – UART                 | 15     |

| 7.1        | Register Description                     | 17     |

| 8          | Functional Safety2              | 21 |

|------------|---------------------------------|----|

| 8.1        | Safety Manual                   | 21 |

| 9          | Application Information         | 22 |

| 9.1<br>9.2 | Differential Mode               |    |

| 10         | Configuration and Programming 2 | 26 |

| 11         | Preconfigured Versions          | 27 |

| 11.1       | AS5116A                         | 27 |

| 12         | Package Drawings & Markings2    | 29 |

| 13         | Mechanical Data                 | 31 |

| 14         | Revision Information            | 32 |

| 15         | Legal Information               | 33 |

## 1 General Description

The AS5116 is a contactless magnetic position sensor for accurate angular measurement over a full mechanical turn of 360°.

Based on the Hall sensor technology, this device has a robust architecture that measures the orthogonal component of the flux density (Bz), over a full-turn rotation. To measure the angle, only a simple two-pole magnet rotating over the center of the package is required. The magnet can be placed above or below the device.

The absolute angle measurement provides an instant indication of the magnet's angular position. The angle information is provided by means of buffered differential sine and cosine voltages. The AS5116 operates at a supply voltage of 5 V or 3.3 V.

### 1.1 Key Benefits & Features

The benefits and features of AS5116, On-Axis Magnetic Position Sensor with Analog Sine-Cosine Outputs, are listed below:

Figure 1: Added Value of Using AS5116

| Benefits                                 | Features                                                   |

|------------------------------------------|------------------------------------------------------------|

| Highest reliability and durability       | Contactless angle measurement                              |

| Accurate angle measurement               | Low output noise                                           |

| Low system costs – no shielding required | Low inherent INL                                           |

| Enabler for safety critical applications | Magnetic stray field immunity overachieves ISO 11452-8     |

| High precision analog output             | Developed according to ISO26262                            |

| Small form factor                        | Fully differential buffered sine and cosine output signals |

| Fully automotive qualified               | AEC - Q100, Grade 0                                        |

### 1.2 Applications

- Rotor angle sensing of electric commutated motors

- Electric power steering systems

- Electric pumps

- Actuators in transmission systems

- Starter/Generator systems

- Other 360° angle measurement solutions

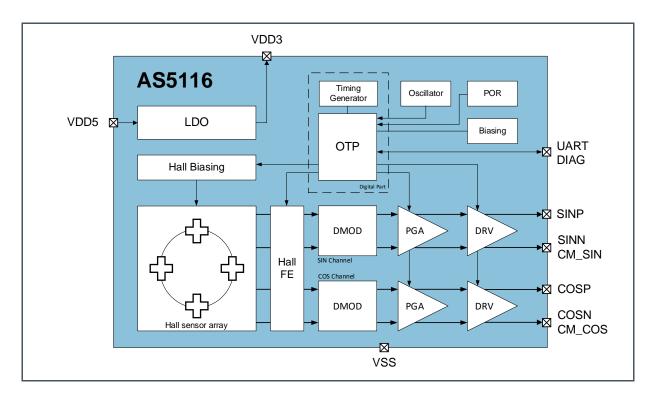

### 1.3 Block Diagram

Figure 2 shows the block diagram of the AS5116 sensor.

Figure 2: Functional Blocks of AS5116

# 2 Ordering Information

| Ordering Code | Package | Marking | Delivery Form   | Delivery Quantity |

|---------------|---------|---------|-----------------|-------------------|

| AS5116-HSOT   | SOIC8   | AS5116  | 13" Tape & Reel | 2500 pcs/reel     |

| AS5116-HSOM   | SOIC8   | AS5116  | 7" Tape & Reel  | 500 pcs/reel      |

| AS5116A-HSOT  | SOIC8   | AS5116A | 13" Tape & Reel | 2500 pcs/reel     |

| AS5116A-HSOM  | SOIC8   | AS5116A | 7" Tape & Reel  | 500 pcs/reel      |

# 3 Pin Assignment

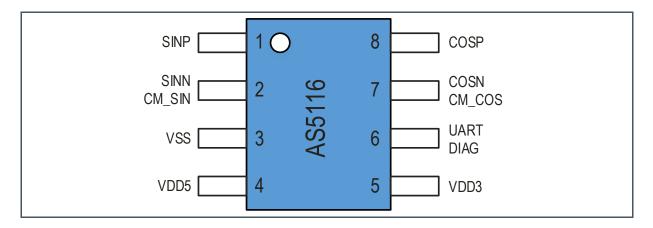

### 3.1 Pin Diagram AS5116

Figure 3: Pin Diagram of AS5116 in SOIC8 Package

### 3.2 Pin Description AS5116

Figure 4: Pin Description of AS5116 in SOIC8 Package

| 1 SINP Analog Out Buffered sine channel, positive output 2 SINN CM_SIN Analog Out Common mode level for sine channel (optional). 3 VSS Supply Common ground 4 VDD5 Supply Supply voltage 5 VDD3 Analog Out On chip low-dropout regulator output voltage. Requires an external 1 μF decoupling capacitor  UART Digital I/O Digital Out Diagnostic output for on-chip diagnostic functions. This pin always has to be tied to VDD5 with the pull up resistor R <sub>pu</sub> .  COSN CM_COS Analog Out Common mode level for cosine channel (optional).                                                   | Pin Number | Pin Name | Pin Type   | Description                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------|------------|--------------------------------------------------------------------------------------------------------------|

| CM_SIN  Analog Out Common mode level for sine channel (optional).  VSS Supply Common ground  VDD5 Supply Supply voltage  NDD3  Analog Out On chip low-dropout regulator output voltage. Requires an external 1 μF decoupling capacitor  UART DIGITAL Out Digital I/O Digital Out Diagnostic output for OTP programming (default). Diagnostic output for on-chip diagnostic functions. This pin always has to be tied to VDD5 with the pull up resistor R <sub>pu</sub> .  COSN CM_COS  Analog Out  Buffered cosine channel, inverted output (default). Common mode level for cosine channel (optional). | 1          | SINP     | Analog Out | Buffered sine channel, positive output                                                                       |

| 4 VDD5 Supply Supply voltage  5 VDD3 Analog Out On chip low-dropout regulator output voltage. Requires an external 1 μF decoupling capacitor  UART Digital I/O Digital Out Diagnostic output for on-chip diagnostic functions. This pin always has to be tied to VDD5 with the pull up resistor R <sub>pu</sub> .  COSN CM_COS Analog Out Common mode level for cosine channel (optional).                                                                                                                                                                                                              | 2          |          | Analog Out | • • • • • • • • • • • • • • • • • • • •                                                                      |

| 5 VDD3 Analog Out On chip low-dropout regulator output voltage. Requires an external 1 μF decoupling capacitor  UART DIGITAL Digital I/O Digital Out Diagnostic output for on-chip diagnostic functions. This pin always has to be tied to VDD5 with the pull up resistor R <sub>pu</sub> .  COSN CM_COS Analog Out Common mode level for cosine channel (optional).                                                                                                                                                                                                                                    | 3          | VSS      | Supply     | Common ground                                                                                                |

| an external 1 μF decoupling capacitor  UART Digital I/O Digital Out Diagnostic output for on-chip diagnostic functions.  This pin always has to be tied to VDD5 with the pull up resistor R <sub>pu</sub> .  COSN CM_COS Analog Out Common mode level for cosine channel (optional).                                                                                                                                                                                                                                                                                                                    | 4          | VDD5     | Supply     | Supply voltage                                                                                               |

| DIAG  Digital Out  Diagnostic output for on-chip diagnostic functions.  This pin always has to be tied to VDD5 with the pull up resistor R <sub>pu</sub> .  COSN  CM_COS  Analog Out  Common mode level for cosine channel (optional).                                                                                                                                                                                                                                                                                                                                                                  | 5          | VDD3     | Analog Out |                                                                                                              |

| 7 CM_COS Analog Out Common mode level for cosine channel (optional).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6          |          | · ·        | Diagnostic output for on-chip diagnostic functions.  This pin always has to be tied to VDD5 with the pull up |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7          |          | Analog Out |                                                                                                              |

| 8 COSP Analog Out Buffered cosine channel, positive output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8          | COSP     | Analog Out | Buffered cosine channel, positive output                                                                     |

## 4 Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5:

Absolute Maximum Ratings of AS5116

| Symbol              | Parameter                                     | Min  | Max        | Unit | Comments                                     |

|---------------------|-----------------------------------------------|------|------------|------|----------------------------------------------|

| Electrical P        | arameters                                     |      |            |      |                                              |

| VDD5                | DC Voltage at VDD5 pin                        | -0.3 | 7          | V    |                                              |

| VREG                | DC Voltage at VDD3 pin                        | -0.3 | 5          | V    |                                              |

| VSS                 | DC Voltage at VSS pin                         | -0.3 | 0.3        | V    |                                              |

| $V_{IN}$            | Input Pin Voltage to Ground                   | -0.3 | VDD5 + 0.3 | V    |                                              |

| I <sub>SCR</sub>    | Input Current (latch-up immunity)             | ±    | 100        | mA   | AEC-Q100-004                                 |

| Continuous          | Power Dissipation                             |      |            |      |                                              |

| P <sub>T</sub>      | Total Power Dissipation                       |      | 150        | mW   |                                              |

| Electrostati        | ic Discharge                                  |      |            |      |                                              |

| $ESD_HBM$           | Electrostatic Discharge HBM                   | ± 2  | ± 2000     |      | AEC-Q100-002                                 |

| ESD <sub>CDM</sub>  | Electrostatic Discharge CDM                   | ±    | 500        | V    | AEC-Q100-011                                 |

| Temperatui          | re Ranges and Storage Conditions              |      |            |      |                                              |

| T <sub>A</sub>      | Operating Ambient Temperature                 | -40  | 150        | °C   |                                              |

| TJ                  | Operating Junction Temperature                |      | 165        | °C   |                                              |

| T <sub>A_PROG</sub> | Ambient Temperature during OTP<br>Programming | 0    | 45         | °C   |                                              |

| T <sub>STRG</sub>   | Storage Temperature Range                     | - 55 | 150        | °C   |                                              |

| T <sub>BODY</sub>   | Package Body Temperature                      |      | 260        | °C   | IPC/JEDEC J-STD-020 (1)                      |

| RH <sub>NC</sub>    | Relative Humidity (non-condensing)            | 5    | 85         | %    |                                              |

| MSL                 | Moisture Sensitivity Level                    | 3    |            |      | Represents a maximum floor lifetime of 168 h |

| Temperatui          | re Soldering                                  |      |            |      |                                              |

| T <sub>PEAK</sub>   | Peak Temperature                              |      | 260        | °C   | IPC/JEDEC J-STD-020                          |

| t <sub>WELL</sub>   | Well Time above 217 °C                        | 30   | 45         | S    |                                              |

<sup>(1)</sup> The reflow peak soldering temperature (body temperature) is specified according to IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices." The lead finish for Pb-free leaded packages is "Matte Tin" (100 % Sn)

## **5** Electrical Characteristics

All limits are guaranteed over the operating temperature range (-40°C to 150°C) and lifetime, unless otherwise noticed. The parameters with Min and Max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6: Electrical Characteristics of AS5116

| Symbol                | Parameter                                 | Conditions                                               | Min           | Тур   | Max           | Unit |

|-----------------------|-------------------------------------------|----------------------------------------------------------|---------------|-------|---------------|------|

| Operating Condi       | tions                                     |                                                          |               |       |               |      |

| VDD5                  | Positive Supply Voltage                   | 5.0 V operation mode                                     | 4.5           | 5.0   | 5.5           | V    |

| VDD3                  | Positive Supply Voltage in 3V3 Mode       | 3.3 V operation mode,<br>LDO shorted                     | 3.0           | 3.3   | 3.6           | V    |

| VDDBURN               | Positive Supply Voltage                   | Supply voltage required for programming in 3V3 operation | 3.3           |       | 3.5           | V    |

| VREG                  | Regulated Voltage                         | Voltage at Vreg if sensor is in 5 V operation mode       | 3.2           | 3.4   | 3.6           | V    |

| VSS                   | Negative Supply Voltage                   |                                                          | 0             |       | 0             | V    |

| IDD                   | Supply Current                            | Depends on gain setting                                  |               |       | 17            | mA   |

| T <sub>POWER_ON</sub> | Power Up Time                             |                                                          |               |       | 10            | ms   |

| Input Parameter       |                                           |                                                          |               |       |               |      |

| BIN                   | Limit for Target Bz Peak<br>Field         | At the Hall element position inside the sensor           | 10            |       | 100           | mT   |

| VMAX                  | Maximum Rotation Speed                    |                                                          | -30000        |       | 30000         | RPM  |

| Output Paramete       | er                                        |                                                          |               |       |               |      |

| VOUT                  | Analog Output Voltage<br>Amplitude Limits |                                                          | GND +<br>0.25 |       | VDD –<br>0.5  | V    |

| VCM1                  | Output Common Mode Level                  | Default level                                            | 1.275         | 1.375 | 1.475         | V    |

| VCM2                  | Output Common Mode Level                  |                                                          | 1.975         | 2.125 | 2.275         | V    |

| IOUT                  | Analog Output Load Current                |                                                          | -1            |       | 1             | mA   |

| CLOAD                 | Analog Output Capacitive Load             |                                                          |               |       | 10            | nF   |

| Digital IO Paramo     | eter - DIAG                               |                                                          |               |       |               |      |

| V_IH                  | High Level Input Voltage                  | UART mode enabled (default)                              | 0.7 *<br>VDD5 |       |               | V    |

| V_IL                  | Low Level Input Voltage                   | UART mode enabled (default)                              |               |       | 0.3 *<br>VDD5 | V    |

| V_OH                  | High Level Output Voltage                 |                                                          | VDD5 -<br>0.5 |       |               | V    |

| V_OL                  | Low Level Output Voltage                  |                                                          |               |       | VSS +<br>0.4  | V    |

| C_L                   | Capacitive Load                           |                                                          |               |       | 50            | pF   |

| I_OUT_5V              | Output Current 5V Operation               |                                                          |               |       | 4             | mA   |

| Symbol             | Parameter                                                            | Conditions | Min | Тур | Max | Unit |

|--------------------|----------------------------------------------------------------------|------------|-----|-----|-----|------|

| I_OUT_3V           | Output Current 3V3<br>Operation                                      |            |     |     | 2   | mA   |

| External Component | ts                                                                   |            |     |     |     |      |

| R <sub>pu</sub>    | Pull up resistor in Figure 28 and Figure 29                          |            | 10  |     | 100 | kΩ   |

| C <sub>out</sub>   | Output capacitors C1, C2,<br>C3 and C4 in Figure 28 and<br>Figure 29 |            | 0.5 |     | 10  | nF   |

Figure 7: Key Performance Parameters

| Symbol                        | Parameter                                                                                             | Conditions                                                                                            | Min    | Тур   | Max  | Unit   |

|-------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|-------|------|--------|

| INL_error (1)                 | Based on Sensor<br>Internal Imperfections                                                             | -40 °C to 150 °C                                                                                      |        | 0.5   | 1    | degree |

| INL_error + Magnet (1)        | Non-Linearity @ Displacement of Magnet and Temperature -40 °C to 150 °C                               | Assuming N35H  Magnet (D=8 mm, H=3 mm) 500 µm displacement in x and y.  Package to magnet gap 1700 µm |        | 0.6   | 1.2  | degree |

| SINCOS_ORT_error (2)          | Orthogonality Error. Defines deviation of ideal phase shift of 90° between SIN and COS output signals | Based on maximum INL_error.                                                                           | -2     |       | 2    | degree |

| SINCOS_GAIN_error (2)         | Gain Mismatch between SIN and COS channel                                                             | Based on maximum INL_error                                                                            | -3.5   |       | 3.5  | %      |

| NOISE5V                       | Maximum RMS Noise. Depending on Gain Configuration (see Figure 10).                                   | VDD = 5 V (5 V operation)                                                                             |        |       | 2.47 | mVrms  |

| NOISE3V3                      | Maximum RMS Noise.<br>Depending on Gain<br>Configuration (see<br>Figure 10).                          | VDD = 3.3 V (3V3 operation)                                                                           |        |       | 2.61 | mVrms  |

| TD                            | Propagation Delay                                                                                     |                                                                                                       | 12     | 16    | 20   | μs     |

| M                             | Magnetic Sensitivity Differential Output Mode                                                         |                                                                                                       | 8      |       | 60   | mV/mT  |

| GV                            | Gain Variation at 25 °C                                                                               | Variation of selected absolute GAIN (Part to Part Variation)                                          | -16    |       | 16   | %      |

| GV_Temp_AS5116 <sup>(3)</sup> | Gain Variation Over<br>Temperature                                                                    | -40°C to 150°C<br>(Gain drift of one single<br>sensor)                                                | -0.105 | -0.05 | 0    | %/°C   |

| GV_Temp_AS5116A (4)           | Gain Variation Over<br>Temperature                                                                    | -40°C to 150°C<br>(Gain drift of one single<br>sensor)                                                | -0.075 | -0.03 | 0    | %/°C   |

| Symbol | Parameter   | Conditions                    | Min | Тур | Max | Unit |

|--------|-------------|-------------------------------|-----|-----|-----|------|

| HR     | Hall Radius | Radius of circular Hall array |     | 1.1 |     | mm   |

- (1) Valid for Differential Output Mode. Assuming a minimum Vout<sub>P2P</sub> voltage of 3000 mV. Differential consideration of output signals required.

- (2) Worst case linearity error is limited and guaranteed by INL\_max parameter.

- (3) Parameter guaranteed by design. Worst case figure, valid for Gain\_Code 24.

- (4) Parameter guaranteed by design. Worst case figure, valid for Gain\_Code 12.

## **6** Functional Description

The Hall-based magnetic position sensor, uses an array of planar sensors that convert the magnetic field component Bz perpendicular to the surface of the chip into a voltage. The signals coming from the Hall sensors are amplified, filtered and buffered before the information is available as sine and cosine voltages on the output. Gain respectively sensitivity of the complete signal path, can be defined by programming the Gain\_Code in CONFIG2 register. The sensor is as well programmable to provide a full differential or single ended signal on the output.

Settings are in system programmable through an UART single wire interface. For achieving a high ASIL in the application, the sensor is fully supporting the ISO26262 implementation process (Detailed information on request).

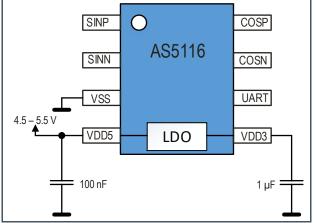

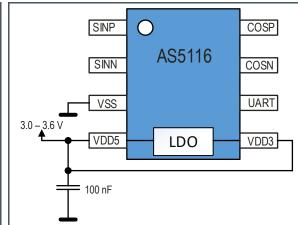

### 6.1 IC Power Management

The AS5116 can be either powered from a 5.0 V supply using the on-chip low-dropout regulator (LDO) or from a 3.3 V voltage supply. The LDO (low-dropout) regulator is not intended to power any other loads, and it needs a 1 µF capacitor to ground located close for decoupling as shown Figure 8.

In 3V3 operation, VDD and VREG tied together.

Figure 8: Pin Configuration in 5 V Operation Mode

Figure 9: Pin Configuration in 3V3 Operation Mode

### 6.2 Gain Configuration

The amplitudes of the output voltages are directly proportional to the Bz field of the magnet above the sensor. The user can select the appropriate Gain Setting out of 25 possible steps.

Figure 10: Gain Table<sup>(1)</sup>

| Gain_Code CONFIG2 Register 0x17 <1:5> | GAIN [mV/mT] 5V Operation Mode | Maximum RMS-<br>Noise [mV]<br>5V Operation Mode | GAIN [mV/mT] 3V3 Operation Mode | Maximum RMS-<br>Noise [mV]<br>3V3 Operation Mode |

|---------------------------------------|--------------------------------|-------------------------------------------------|---------------------------------|--------------------------------------------------|

| 0                                     | 8                              | 0.51                                            | 8                               | 0.51                                             |

| 1                                     | 10                             | 0.51                                            | 10                              | 0.68                                             |

| 2                                     | 12                             | 0.51                                            | 12                              | 0.72                                             |

| 3                                     | 13.5                           | 0.68                                            | 13                              | 1.53                                             |

| 4                                     | 16                             | 0.68                                            | 16                              | 0.96                                             |

| 5                                     | 18                             | 0.72                                            | 18                              | 1.08                                             |

| 6                                     | 20                             | 0.96                                            | 19.5                            | 1.14                                             |

| 7                                     | 22.5                           | 1.08                                            | 21.5                            | 1.35                                             |

| 8                                     | 24                             | 0.96                                            | 23                              | 1.35                                             |

| 9                                     | 26.5                           | 1.25                                            | 26                              | 1.53                                             |

| 10                                    | 26.5                           | 1.65                                            | 26.5                            | 1.65                                             |

| 11                                    | 29                             | 1.35                                            | 28.5                            | 1.65                                             |

| 12                                    | 31.5                           | 1.25                                            | 30                              | 1.74                                             |

| 13                                    | 32.5                           | 2.02                                            | 32.5                            | 2.02                                             |

| 14                                    | 35                             | 1.35                                            | 35                              | 2.02                                             |

| 15                                    | 35.5                           | 1.65                                            | 35.5                            | 2.20                                             |

| 16                                    | 39                             | 1.53                                            | 38                              | 2.20                                             |

| 17                                    | 40                             | 2.47                                            | 40                              | 2.47                                             |

| 18                                    | 42.5                           | 1.65                                            | 42.5                            | 2.47                                             |

| 19                                    | 45                             | 1.74                                            | 45                              | 2.61                                             |

| 20                                    | 47.5                           | 2.20                                            | 45                              | 2.61                                             |

| 21                                    | 52                             | 2.02                                            | 45                              | 2.61                                             |

| 22                                    | 53.5                           | 2.47                                            | 45                              | 2.61                                             |

| 23                                    | 57                             | 2.20                                            | 45                              | 2.61                                             |

| 24                                    | 60                             | 2.32                                            | 45                              | 2.61                                             |

<sup>(1)</sup> Gain table representing typical values, maximum Part-to-Part gain variation GV is separately specified.

### 6.3 Behavior of Sensor Outputs

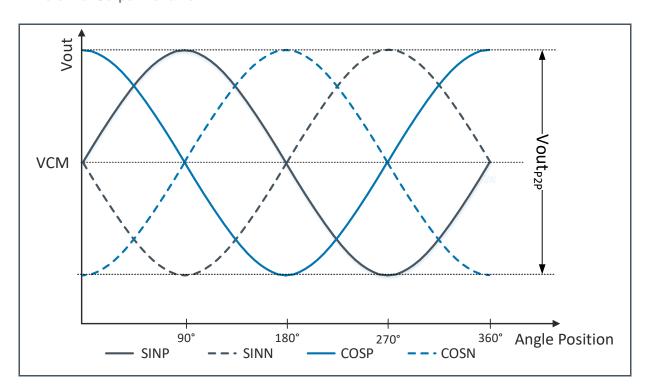

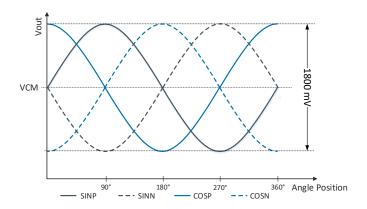

Following graphs show the behavior at different output settings over one mechanical 360° rotation.

#### 6.3.1 Differential Output Mode (Default Setting)

Positive SINP and COSP signals in combination with inverted SINN and COSN are provided via the output pins of the sensor. High immunity against common cause errors, evoked by the environment of the sensor, is given due to the differential signal transmission. Fully differential signal inputs are required to digitize the analog outputs. VCM is defined via OTP programming.

Figure 11: Differential Output Behavior

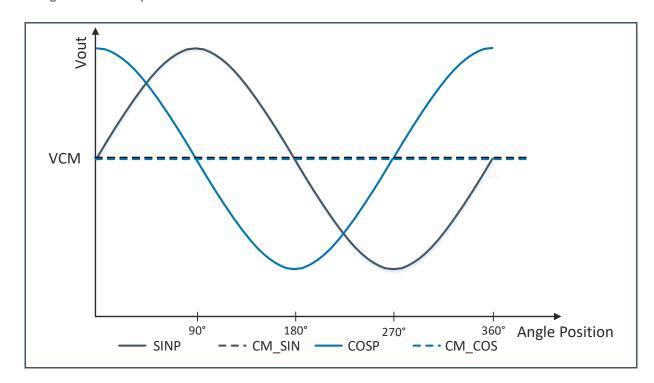

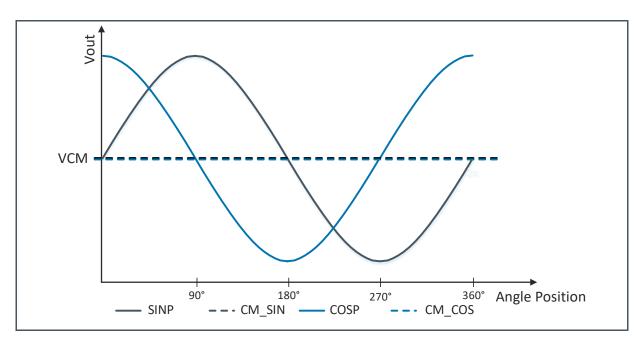

#### 6.3.2 Single-Ended Output Mode

Positive SINP and COSP signals in combination with the configured VCM level on CM\_SIN and CM\_COS are provided via the output pins of the sensor. To achieve best accuracy performance, fully differential signal inputs are recommended to digitize the analog outputs. As an alternative, single-ended measurement of all output signals with associated data processing (SINP - CM\_SIN, COSP - CM\_COS) is as well possible.

Figure 12: Single-Ended Output Behavior

## 7 Digital Interface – UART

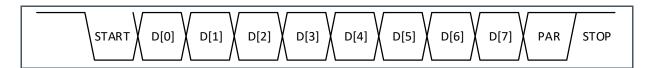

The AS5116 is equipped with an UART interface, which allows reading and writing the registers as well as permanently programming the non-volatile memory (OTP). By default (Diag\_EN = 0) the AS5116 is in the so-called Communication Mode and the UART is connected to pin 6. In this mode, it is possible to configure the register settings.

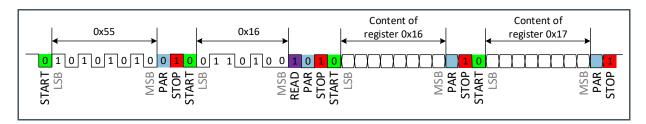

The UART interface allows reading and writing two consecutive addresses. The standard UART sequence consists of four frames. Each frame begins with a start bit (START), which is followed by 8 data bits (D[0:7]), one parity bit (PAR), and a stop bit (STOP), as shown in Figure 13.

Figure 13: UART Frame

The PAR bit is and Even Parity, calculated over the data bits (D[0:7]). Each frame is transferred LSB first.

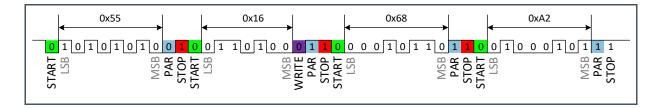

Figure 14: Standard UART Sequence

| Frame Number | D[7] | D[6] | D[5]    | D[4] | D[3] | D[2] | D[1] | D[0] |

|--------------|------|------|---------|------|------|------|------|------|

| 1            |      |      |         |      | 0x55 |      |      |      |

| 2            | R/W  |      | ADDRESS |      |      |      |      |      |

| 3            |      |      | DATA1   |      |      |      |      |      |

| 4            |      |      | DATA2   |      |      |      |      |      |

The first frame is the synchronization frame and consists of D[0:7] = 0x55 followed by the parity bit (PAR = 0) and the stop bit. This frame synchronizes the baud rate between the AS5116 and the UART Master. The UART baud rate have to stay in a range of 1.1 – 70 kbit/s.

The second frame contains the read/write command (Write: D[7] = 0; Read: D[7] = 1) and the address of the register (ADDRESS: D[0:6]).

The content of the third and fourth frames (DATA1 and DATA2) will be written to or read from the location specified by ADDRESS and ADDRESS+1.

Figure 15 and Figure 16 show examples of Read and Write UART frame.

Figure 15: UART – Write Example

In this UART – Write example the UART Master writes to CONFIG1 register 0x16 - 0x68 and to CONFIG2 register 0x17 - 0xA2.

Figure 16: UART – Read Example

In this UART – Read example the UART Master reads from CONFIG1 register 0x16 and CONFIG2 register 0x17.

### 7.1 Register Description

The table below shows all accessible digital registers implemented in the AS5116 sensor.

Figure 17: Register Overview

| Address | Name          | Function | Default | Description                                               |

|---------|---------------|----------|---------|-----------------------------------------------------------|

| 0x01    | UART_ERROR    | R        | 0x00    | Indication of framing and parity errors                   |

| 0x03    | P2RAM_CONTROL | R/W      | 0x00    | P2RAM handling                                            |

| 0x16    | CONFIG1       | R/W/P    | 0x00    | Configuration of output setting                           |

| 0x17    | CONFIG2       | R/W/P    | 0x00    | Configuration of gain and diagnostic mode                 |

| 0x18    | CUST_CHIP_ID1 | R/W/P    | 0x00    | Spare bits for custom chip ID                             |

| 0x19    | CUST_CHIP_ID2 | R/W/P    | 0x00    | Spare bits for custom chip ID                             |

| 0x1A    | CUST_CHIP_ID3 | R/W/P    | 0x00    | Spare bits for custom chip ID                             |

| 0x1B    | ECC           | R/W/P    | 0x00    | Configuration of ECC function                             |

| 0x50    | ECC_CHECKSUM  | R        | 0x00    | Calculated ECC checksum based on actual register settings |

| 0x51    | ECC_STATUS    | R        | 0x00    | Indicates actual ECC status if ECC function is enabled    |

#### 7.1.1 UART\_ERROR Register – 0x01

In the UART\_ERROR Register problems during UART communication are indicated. Error bits are sticky and clear on read.

UART\_SYNC Bit indicates a problem with the synchronization frame. This is usually the case if the Baudrate was not defined correctly. Baudrate window is defined from 1.1 kbit/s to 70 kbit/s.

UART\_PARITY bit indicates a parity error during a UART-Write command. UART\_FRAME bit indicates an error, if after synchronization the UART line stays low for more than twice the usual expected time (too long frame).

Figure 18: UART\_ERROR Register – 0x01

| Bit Position | Bit Name    | Default | Description                |

|--------------|-------------|---------|----------------------------|

| 0            | UART_SYNC   | 0       | UART synchronization error |

| 1            | UART_PARITY | 0       | UART parity error          |

| 2            | UART_FRAME  | 0       | UART frame too long error  |

#### 7.1.2 P2RAM\_CONTROL Register – 0x03

The P2RAM\_CONTROL Register handles all processes in combination with the OTP memory.

Description of OTP related commands and definition of the programming flow chart is given in section Configuration and Programming.

Figure 19: P2RAM\_CONTROL Register

| Bit Position | Bit Name | Default | Description                                                 |

|--------------|----------|---------|-------------------------------------------------------------|

| 0:1          | State    | 0       | P2RAM state                                                 |

| 2            | LOAD     | 0       | Load latch from fuse array                                  |

| 3            | BURN     | 0       | Burn command to permanently store setting within OTP memory |

| 6            | GLOAD    |         | Enabled guard band mode to check burn quality               |

#### 7.1.3 CONFIG1 Register – 0x16

In CONFIG1 Register includes several possible configurations of the sensor outputs, like common mode level and pin configuration

Figure 20: CONFIG1 Register

| Bit Position | Bit Name  | Default | Description                                                     |

|--------------|-----------|---------|-----------------------------------------------------------------|

| 0:2          | n.a.      | 0       | Not applicable                                                  |

| 3            | VCM_Level | 0       | Output common mode level<br>(0: VCM = 1.375 V, 1: VCM =2.125 V) |

| 4            | n.a.      | 0       | Not applicable                                                  |

| 5            | CM_COS    | 0       | Defines the output function of pin 7 (0: COSN, 1: CM_COS)       |

| 6            | CM_SIN    | 0       | Defines the output function of pin 2 (0: SINN, 1: CM_SIN)       |

| 7            | INVERT_CH | 0       | Inverts the sign of the output channels                         |

#### 7.1.4 **CONFIG2** Register – 0x17

CONFIG 2 Register includes the sensitivity settings and a bit to enable the diagnostic mode.

Figure 21:

**CONFIG2** Register

| Bit Position | Bit Name  | Default | Description                                        |

|--------------|-----------|---------|----------------------------------------------------|

| 0            | Diag_EN   | 0       | Enables diagnostic mode when the bit is set to "1" |

| 1:5          | Gain_Code | 0       | Defines the sensitivity of the sensor              |

| 6:7          | n.a.      | 0       | Not applicable                                     |

#### 7.1.5 CUST\_CHIP\_ID1 Register – 0x18

Figure 22:

CUST\_CHIP\_ID1

| Bit Position | Bit Name      | Default | Description                                    |

|--------------|---------------|---------|------------------------------------------------|

| 0:7          | CUST_CHIP_ID1 | 0       | Spare bits for customized tracking information |

#### 7.1.6 CUST\_CHIP\_ID2 Register – 0x19

Figure 23:

CUST\_CHIP\_ID2

| Bit Position | Bit Name      | Default | Description                                    |

|--------------|---------------|---------|------------------------------------------------|

| 0:7          | CUST_CHIP_ID2 | 0       | Spare bits for customized tracking information |

#### 7.1.7 CUST\_CHIP\_ID3 Register – 0x1A

Figure 24:

CUST\_CHIP\_ID3

| Bit Position | Bit Name      | Default | Description                                    |

|--------------|---------------|---------|------------------------------------------------|

| 0:7          | CUST_CHIP_ID3 | 0       | Spare bits for customized tracking information |

#### 7.1.8 ECC Register – 0x1B

Within ECC (Error-Correction Code) register, the ECC function is configured and enabled.

Figure 25: ECC Register

| Bit Position | Bit Name  | Default | Description                     |

|--------------|-----------|---------|---------------------------------|

| 0:6          | ECC_Chsum | 0       | ECC checksum programmed by user |

| 7            | ECC_EN    | 0       | Enables ECC function            |

# Figure 26: ECC CHECKSUM

| Bit Position | Bit Name       | Default | Description                      |

|--------------|----------------|---------|----------------------------------|

| 0:6          | ECC_Chsum_calc | 0       | Internal calculated ECC checksum |

# Figure 27: ECC STATUS

| Bit Position | Bit Name           | Default | Description                                                                                                                                                                                                                                                                                |

|--------------|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | ECC_EN_after_check | 0       | ECC_EN after error correction                                                                                                                                                                                                                                                              |

| 1:2          | ECC_Error          | 0       | <ul> <li>ECC Error code:</li> <li>0: P2RAM bytes in customer area are correct (or ECC_EN = 0)</li> <li>1: Single bit error in P2RAM. P2RAM output corrected by ECC function</li> <li>2: Two or more bits are defect in P2RAM block. No correction possible - major system error</li> </ul> |

## 8 Functional Safety

AS5116 is fully supporting the ISO26262 and enables applications to fulfill Automotive Safety Integrity Levels up to ASIL C.

### 8.1 Safety Manual

The safety manual, available upon request, contains all the necessary information for the system integrator, to integrate AS5116 in a safety related item.

AS5116 is supporting the ISO26262 as Safety Element out of Context (SEooC).

The safety manual includes the following information:

- Product development lifecycle

- Description of the technical safety concept on system level

- Detailed information of Assumption of Use of the element with respect to its intended use, which includes

- System Safe State information

- Fault Tolerant Time Interval

- Coverage information

As part of the Safety Manual, the Verification and Safety Analysis Report includes following information:

- HW architectural metric results (Single Point Fault Metric)

- Description of verifications based on the ISO26262

- Detailed FMEDA

## 9 Application Information

Several wiring options and configurations of AS5116 are possible. The most likely used options are shown in the following section.

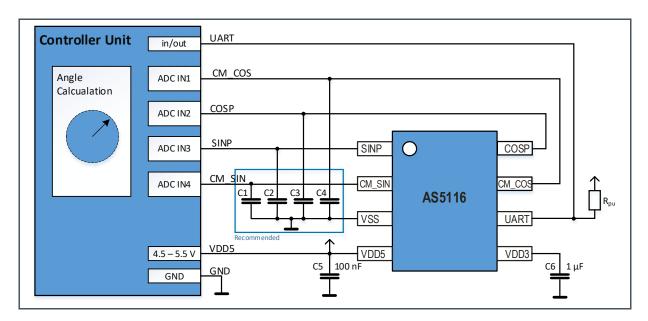

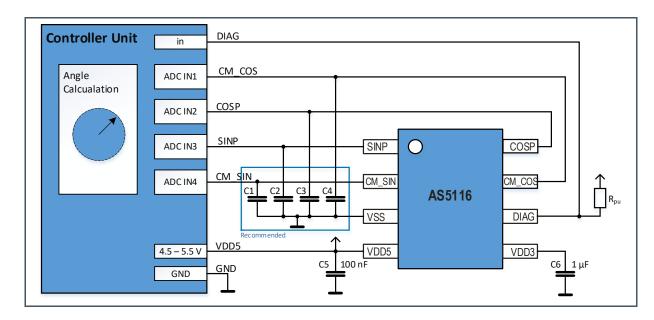

#### 9.1 Differential Mode

By default, the configuration of the sensor is in differential output mode. Positive SINP and COSP signals, as well as the inverted SINN and COSN signals are provided.

This is the recommended output configuration, due to the best common mode rejection. Fully differential inputs are required on controller side. To improve the angle accuracy, a one-time end of line calibration of offset and gain error is recommended before calculating the angle position.

#### 9.1.1 Minimum Wiring Diagram

Figure 28:

AS5116 Minimum Wiring Diagram, Differential Output Mode

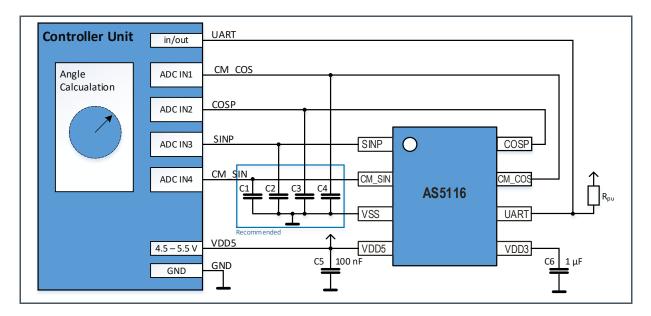

### 9.2 Single Ended Mode

In single-ended configuration, all voltage measurements are reverenced to VSS level. For safety reasons, it is recommended to check as well the levels of CM\_SIN and CM\_COS with separate analog inputs. The measured common mode voltages should be used to calculate the differential sine/cosine

values. Otherwise, the signal common mode level has to be determined in the controller based on one sine/cosine period. To improve the angle accuracy, a one-time end of line calibration of offset and gain error is recommended before calculating the angle position.

#### 9.2.1 Minimum Wiring Diagram

Figure 29: AS5116 Minimum Wiring Diagram, Single Ended Output Mode

#### 9.2.2 Output Amplitude Calculation

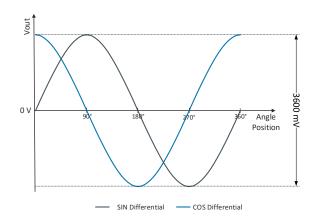

The output amplitude of sine and cosine signals are directly proportional to the selected GAIN setting and the Bz-Field of the available target magnet. Following equations explain how the calculation is done based on a typical example. Using that approach, a very convenient estimation of the output amplitudes is possible.

# Equation 1: Vout Peak to Peak – Single Ended Input

# Equation 2: Vout Peak to Peak – Differential Input

$$Vout_{SE\ P2P} = 2 \cdot Bz_{max} \cdot GAIN$$

$$Vout_{DIF\_P2P} = 4 \cdot Bz_{max} \cdot GAIN$$

#### **Output Amplitude Calculation – Example**

Assumptions: Gain Setting = 30 mV/mT,  $Bz_{max} = 30 \text{ mT}$

#### **Equation 3:**

$$Vout_{SE\_P2P} = 2 \cdot 30 \cdot 30 = 1800 \text{ mV}$$

#### **Equation 4:**

$$Vout_{DIF\ P2P} = 4 \cdot 30 \cdot 30 = 3600 \ mV$$

#### 9.2.3 Diagnostic Mode

In default configuration, the sensor is in communication mode. Pin 6 acts as single wire UART interface connection and can be used to configure all relevant customer setting.

During the programming process, it is possible to enable the diagnostic function by programming the "Diag\_EN" bit in the CONFIG2 Register – 0x17. In that case, pin 6 is acting as diagnostic output after the next power on reset of the sensor.

The diagnostic function checks if the status of the OTP register is still valid and correct. It is directly linked to the ECC\_error status 1 and 2 (ECC\_STATUS Register – 0x51).

Figure 30: DIAG Output State Definition

| State of DIAG Pin 6 | Output Level | Description                                                                                                 |

|---------------------|--------------|-------------------------------------------------------------------------------------------------------------|

| 0                   | GND          | OTP status ok                                                                                               |

| 1                   | VDD          | OTP error One or more bits flipped in OTP section. As result unexpected behavior of the sensor could occur. |

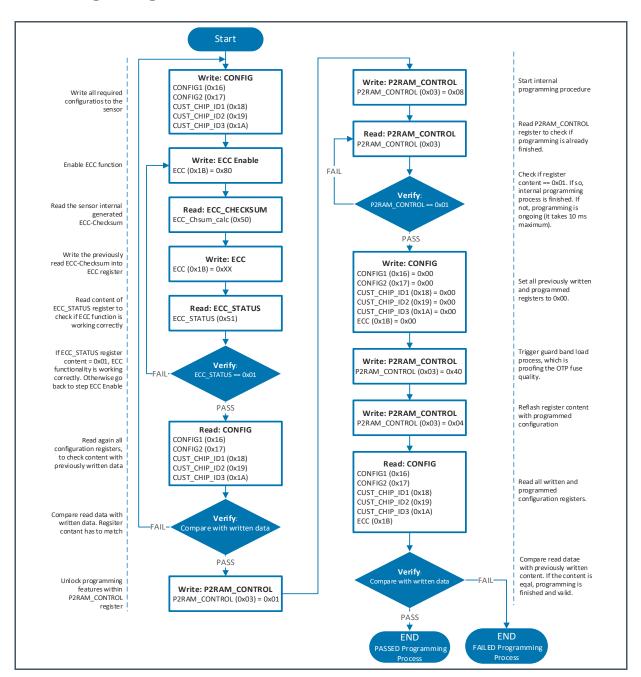

## 10 Configuration and Programming

The non-volatile memory is used to permanently program the configuration. To program the nonvolatile memory, the UART interface is used. The programming could be performed either in 5 V or in 3V3 operation mode operation. Tighter limits of the supply voltage in 3V3 operation has to be considered (VDDBURN).

Figure 31: AS5116 Programming Flow

# 11 Preconfigured Versions

Beside the fully flexible AS5116 version, further preconfigured variants with fixed CONFIG Register settings are available. By using an already programmed AS5116, no further OTP configuration of the sensor is possible.

#### 11.1 AS5116A

AS5116A is configured in Single-Ended mode. SINN and COSN outputs represent the common mode voltage. A fixed gain configuration of 31.5 mV/mT is chosen (Gain\_Code 12). OTP Diagnostic and internal ECC check are enabled and show the actual status on UART/DIAG pin.

Figure 32: AS5116A – Register Settings

| Gain_Code       | DIAG_EN     | VCM_Level   | CM_COS, CM_SIN | INVERT_CH   |

|-----------------|-------------|-------------|----------------|-------------|

| CONFIG2 <1:5>   | CONFIG2 <0> | CONFIG1 <3> | CONFIG1 <5:6>  | CONFIG1 <7> |

| 12 – 31.5 mV/mT | Enabled     | 2.125 V     | Enabled        | Disabled    |

Figure 33: AS5116A – Output Behavior

Figure 34:

AS5116A – Wiring Diagram, Single Ended Output Mode

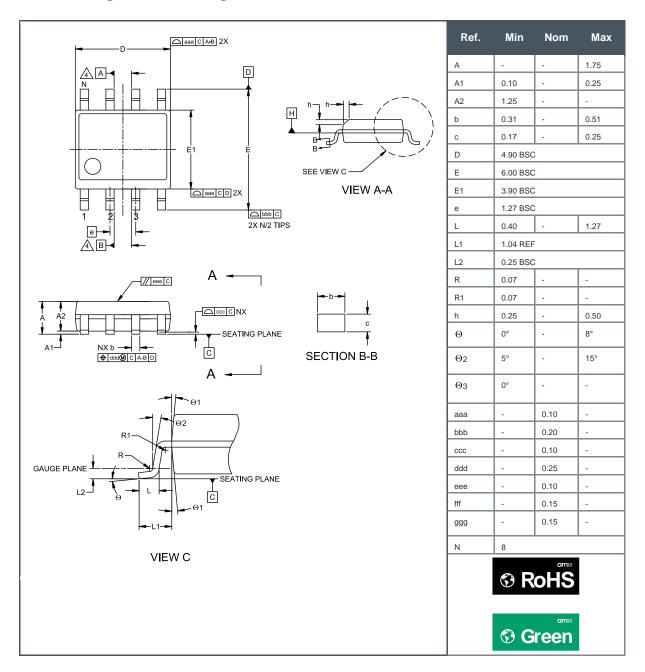

## 12 Package Drawings & Markings

Figure 35: SOIC 8 Package Outline Drawing

- (1) All dimensions are in millimeters (angles in degrees).

- (2) Dimensioning and tolerances conform to ASME Y14.5M-1994.

- (3) N is the total number of terminals.

- (4) Datum A&B to be determined by datum H.

- (5) This package contains no lead (Pb).

- (6) This drawing is subject to change without notice.

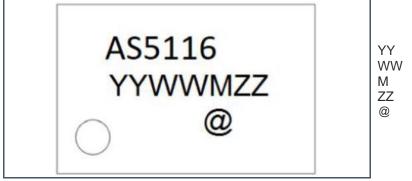

Figure 36: SOIC 8 Package Marking/Code for AS5116

Manufacturing Year

Manufacturing Week

Assembly Plant Identifier

Assembly Traceability Code

Sublot Identifier

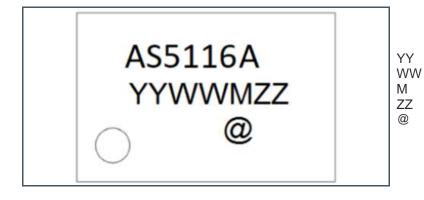

Figure 37: SOIC 8 Package Marking/Code for AS5116A

Manufacturing Year Manufacturing Week Assembly Plant Identifier Assembly Traceability Code Sublot Identifier

## 13 Mechanical Data

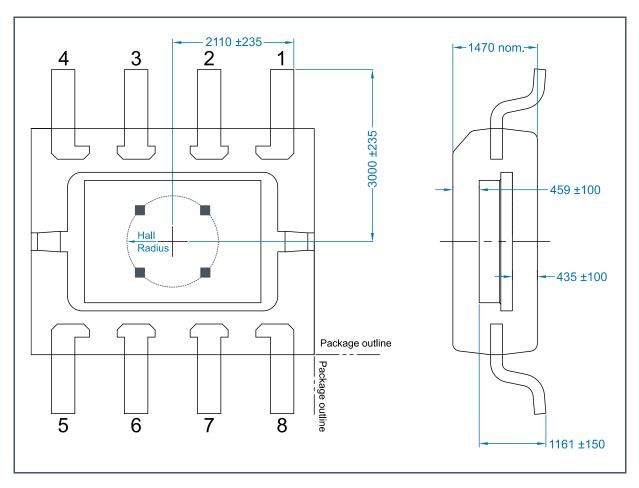

Figure 38: SOIC 8 Die Placement and Hall Array Position

- (1) All dimensions in micrometers

- (2) The Hall array center is located in the center of the IC package. Hall array radius is 1.1 mm.

- (3) Die thickness is 356 μm nominal

- (4) Adhesive thickness  $20 \pm 10 \mu m$

- (5) Leadframe downset 200  $\pm$  25  $\mu$ m

- (6) Leadframe thickness 200 ± 8 μm

## 14 Revision Information

| Changes from previous version to current revision v3-01 | Page |

|---------------------------------------------------------|------|

| Figure 4 changed                                        | 6    |

| Figure 6 changed                                        | 8    |

| Figure 21 changed                                       | 19   |

| Figure 28 changed                                       | 22   |

| Figure 29 changed                                       | 23   |

| Updated text under section 9.2.3                        | 25   |

| Updated Figure 30                                       | 25   |

| Updated Figure 32                                       | 27   |

| Figure 34 added                                         | 28   |

|                                                         |      |

|                                                         |      |

|                                                         |      |

Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

Correction of typographical errors is not explicitly mentioned.