# AS5172E/AS5172F

High-Resolution On-Axis Magnetic Angular Position Sensor with PSI5 Output

### **General Description**

The AS5172E/F is a magnetic position sensor with a high resolution 12-bit PSI5 output according PSI5 specification Version 1.3 and 2.1.

Based on a Hall sensor technology, this device measures the orthogonal component of the flux density (Bz) over a full-turn rotation and compensates for external stray magnetic fields with a robust architecture based on a 14-bit sensor array and analog front-end (AFE). A sub-range can programmed to achieve the best resolution for the application. To measure the angle, only a simple two-pole magnet rotating over the center of the package is required. The magnet may be placed above or below the device. The absolute angle measurement provides an instant indication of the magnet's angular position. The AS5172E/F operates up to a voltage of 16.5V and is protected against overvoltage up to +20V. In addition, the supply pins are protected against reverse polarity up to –18V.

Programmability over the VDD pin reduces the number of pins on the application connector.

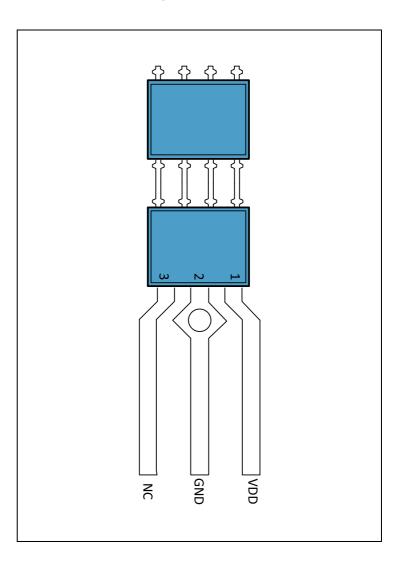

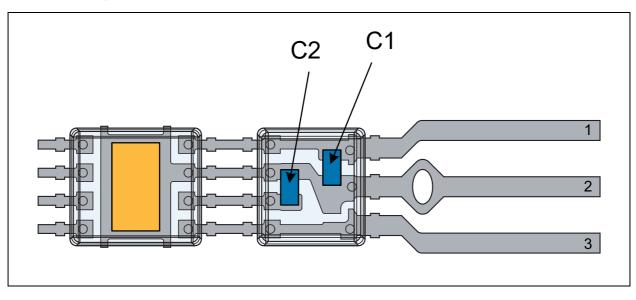

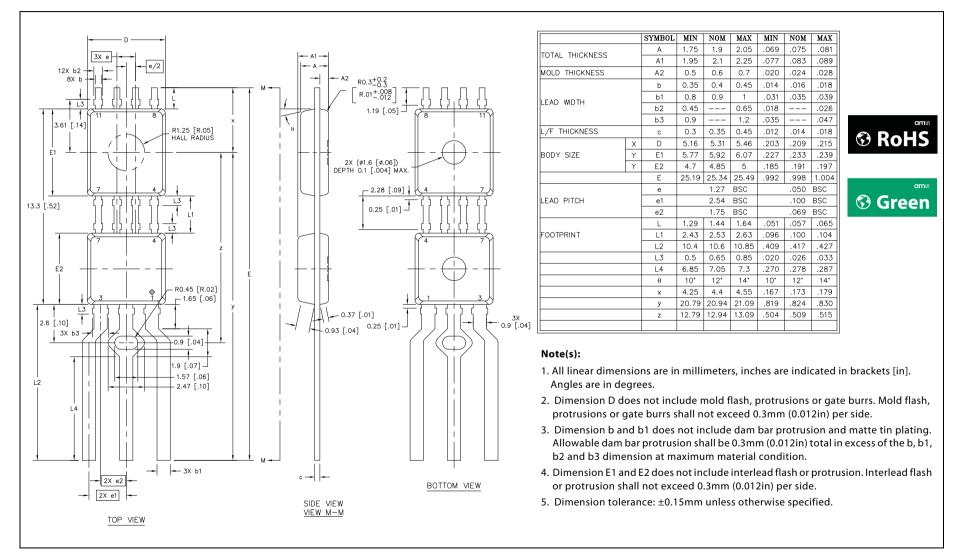

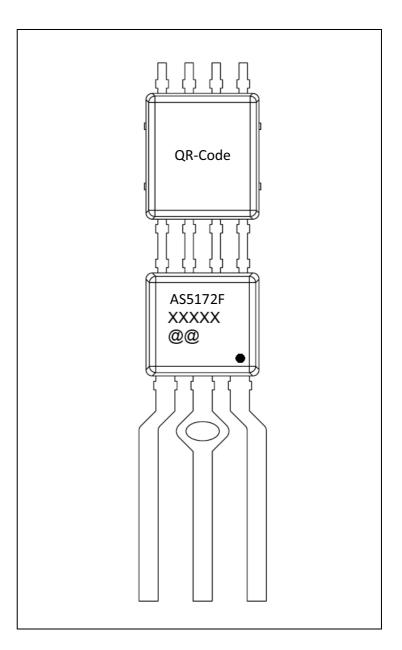

The AS5172E/F is available in a TSSOP14 package and in a SIP package.

The SIP package (System in Package) has integrated the AS5172E/F sensor die together with the decoupling capacitors necessary to pass system level ESD and EMC requirements. No additional components and PCB on the sensor side are needed.

The product is defined as SEooC (Safety Element out of Context) according ISO26262.

The product is fully system level EMC and ESD tested according OEM standards.

Ordering Information and Content Guide appear at end of datasheet.

### **Key Benefits and Features**

The benefits and features of this device are listed below:

Figure 1: Added Value of Using AS5172E/F

| Benefits                                                    | Features                                                                                    |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Resolve small angular excursion with high accuracy          | • 12-bit resolution @90° minimum arc                                                        |

| Accurate angle measurement                                  | Low output noise, low inherent INL                                                          |

| Higher durability and lower system costs (no shield needed) | Magnetic stray field immunity                                                               |

| Enabler for safety critical applications                    | Functional safety, diagnostics                                                              |

| Suitable for automotive applications                        | AEC-Q100 Grade 1 qualified                                                                  |

| SIP Package                                                 | <ul> <li>System cost reduction – no PCB and additional<br/>components are needed</li> </ul> |

### Applications

The AS5172E/F is ideal for automotive applications like brake and gas pedals, throttle valve and tumble flaps, steering angle sensors, chassis ride, EGR, fuel-level measurement systems, 2/4WD switch, and contactless potentiometers.

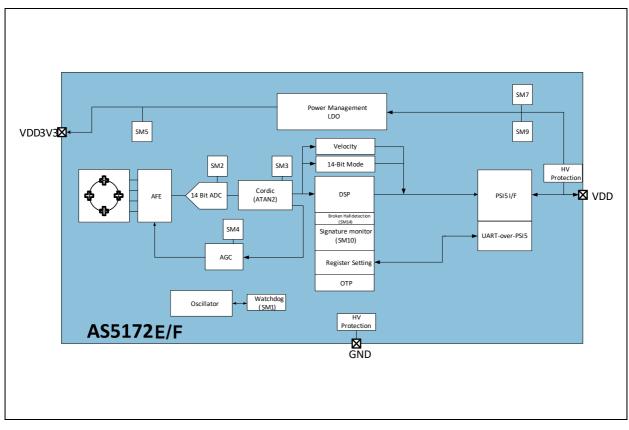

### **Block Diagram**

The functional blocks of this device are shown below:

#### Note(s):

1. Detailed safety mechanism information can be found in chapter Diagnostic.

### **Pin Assignments**

### Pin Diagram

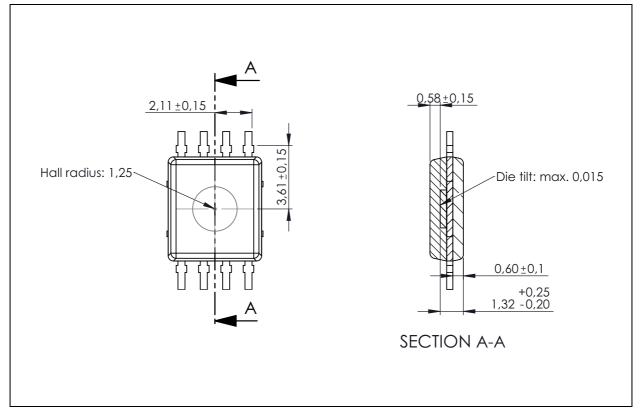

Figure 3: AS5172E/F in SIP Package

Figure 4: AS5172E/F Pin Description

| Pin Number | Name | Туре          | Description                                      |

|------------|------|---------------|--------------------------------------------------|

| 1          | VDD  | Supply        | Supply/PSI5 interface/UART-over-PSI5 programming |

| 2          | GND  | Supply        | Ground                                           |

| 3          | NC   | Not connected | Left open in application                         |

### Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Operating Conditions is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 5: Absolute Maximum Ratings

| Symbol                    | Parameter                            | Min                | Max                     | Units                 | Comments        |  |  |  |  |

|---------------------------|--------------------------------------|--------------------|-------------------------|-----------------------|-----------------|--|--|--|--|

| Electrical Parameters     |                                      |                    |                         |                       |                 |  |  |  |  |

| VDD                       | DC Supply Voltage at VDD pin         | -18                | 20                      | V                     | Not operational |  |  |  |  |

| VREGOUT                   | DC Voltage at the VDD3V3 pin         | -0.3               | 5                       | V                     |                 |  |  |  |  |

| ISCR                      | Input Current (latch-up<br>immunity) | ±100               |                         | mA                    | AEC-Q100-004    |  |  |  |  |

|                           | Continuous Pe                        | ower Diss          | ipation (T <sub>A</sub> | <sub>MB</sub> = 70°C) |                 |  |  |  |  |

| P <sub>T_Tssop</sub>      | Continuous Power<br>Dissipation      |                    | 377                     | mW                    |                 |  |  |  |  |

| P <sub>T_SIP</sub>        | Continuous Power<br>Dissipation      |                    | 377                     | mW                    |                 |  |  |  |  |

|                           | Ele                                  | ctrostatic         | Discharge               |                       |                 |  |  |  |  |

| ESD <sub>HBM on all</sub> | Electrostatic Discharge<br>HBM       | ±2 kV AEC-Q100-002 |                         |                       | AEC-Q100-002    |  |  |  |  |

| ESD <sub>HBM on SIP</sub> | On VDD and GND                       | :                  | ±8                      | kV                    | AEC-Q100-002    |  |  |  |  |

| Symbol                                    | Parameter                             | Min | Max | Units | Comments                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------------------------------|---------------------------------------|-----|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Temperature Ranges and Storage Conditions |                                       |     |     |       |                                                                                                                                                                                                                                                                                                               |  |  |  |

| T <sub>AMB</sub>                          | Operating Temperature<br>Range        | -40 | 125 | °C    | AS5172E/F ambient<br>temperature                                                                                                                                                                                                                                                                              |  |  |  |

| T <sub>aProg</sub>                        | Programming Temperature               | 5   | 45  | °C    | Programming@ room<br>temperature (25°C ± 20°C)                                                                                                                                                                                                                                                                |  |  |  |

| T <sub>STRG</sub>                         | Storage Temperature<br>Range          | -55 | 125 | °C    |                                                                                                                                                                                                                                                                                                               |  |  |  |

| Т <sub>воду</sub>                         | Package Body Temperature              |     | 260 | °C    | The reflow peak soldering<br>temperature (body<br>temperature) is specified<br>according to IPC/JEDEC<br>J-STD-020<br>"Moisture/Reflow<br>Sensitivity Classification for<br>Non-hermetic Solid State<br>Surface Mount Devices."<br>The lead finish for Pb-free<br>leaded packages is "Matte<br>Tin" (100% Sn) |  |  |  |

| RH <sub>NC</sub>                          | Relative Humidity<br>(non-condensing) | 5   | 85  | %     |                                                                                                                                                                                                                                                                                                               |  |  |  |

| MSL                                       | Moisture Sensitivity Level            |     | 3   |       | Represents a maximum<br>floor life time of 168 hours                                                                                                                                                                                                                                                          |  |  |  |

### System Electrical and Timing Characteristics

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

All in this datasheet defined tolerances for external components need to be assured over the whole operation conditions range and also over lifetime.

#### **Overall Condition:**

T<sub>AMB</sub>= -40°C to 125°C for AS5172E/F; Components spec; unless otherwise noted

### Figure 6: Operating Conditions

| Symbol               | Parameter                                                                            | Conditions                                                                                                                                                   | Min | Тур  | Max  | Unit |

|----------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| VDD                  | Positive Supply Voltage                                                              | Static condition                                                                                                                                             | 4   |      | 12   | V    |

| VDD_Rx               | Positive Supply Voltage                                                              | Dynamic condition                                                                                                                                            | 4   |      | 16.5 | V    |

| VDD3                 | Regulator Voltage                                                                    |                                                                                                                                                              | 3.3 | 3.45 | 3.6  | V    |

| IDD                  | Current Consumption                                                                  | No programming and no<br>PSI5 communication                                                                                                                  | 11  | 15   | 19   | mA   |

| IDDProg              | Current Consumption                                                                  | During programming                                                                                                                                           |     | 80   |      | mA   |

| IDDProgUN            | Current Consumption<br>of Unprogrammed<br>Device                                     | Unprogrammed device @<br>T <sub>AMB</sub> = 25°C ± 10°C                                                                                                      |     |      | 49   | mA   |

| IDD max              | Current Consumption                                                                  | IDD + IS_Common                                                                                                                                              |     |      | 49   | mA   |

| IS_Common            | Sink Current (common<br>mode)                                                        |                                                                                                                                                              | 22  | 26   | 30   | mA   |

| IS_low power<br>mode |                                                                                      | Sink current (low power mode)                                                                                                                                | 11  | 13   | 15   | mA   |

| IDD_D                | Current Drift of IS in<br>Low Power Mode                                             |                                                                                                                                                              | -4  |      | 4    | mA   |

| IDD_DRate            | Current Drift Rate                                                                   | Not tested                                                                                                                                                   |     |      | 1    | mA/s |

| TSUP                 | Start-Up Time, With<br>±2mA Tolerance in<br>Respect to the Trimmed<br>ILO Value (IL) | Functional mode                                                                                                                                              |     |      | 5    | ms   |

| PSI5_T               | Fall/Rise Time of the<br>Current Slope                                               | Programmed in production                                                                                                                                     | 300 | 500  | 700  | ns   |

| PSI5_TBITL           | Bit Time 125kbit/s<br>Mode                                                           | Not tested - Guaranteed by<br>Design                                                                                                                         | 7.6 | 8.0  | 8.4  | μs   |

| PSI5_TBITH           | Bit Time 189kbit/s<br>Mode                                                           | Not tested - Guaranteed by<br>Design                                                                                                                         | 5.0 | 5.3  | 5.6  | μs   |

| PSI5_MSR             | Mark/Space Ratio                                                                     | (t <sub>fall,80%</sub> - t <sub>rise, 20%</sub> )/PSI5_TBIT<br>or<br>(t <sub>fall,20%</sub> - t <sub>rise, 80%</sub> )/PSI5_TBIT<br>Programmed in production | 47  | 50   | 53   | %    |

### **Electrical System Characteristics**

$T_{AMB}$ = -40°C to 125°C for AS5172E/F;

VDD = 4V – 12V (sync pulse voltage not included); Magnetic Characterization; unless otherwise noted

Figure 7: Electrical System Characteristics

| Symbol      | Parameter                           | Conditions                                                                                                 | Min  | Тур | Max | Unit |

|-------------|-------------------------------------|------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| CRES        | Core Resolution                     |                                                                                                            |      | 14  |     | bit  |

| OutputRes   |                                     | ≥90° slope                                                                                                 |      |     | 12  | bit  |

| INLopt      | Integral Non-Linearity<br>(optimum) | Best aligned reference magnet <sup>(1)</sup><br>at 25°C over full turn 360°                                | -0.5 |     | 0.5 | deg  |

| INLtemp     | Integral Non-Linearity<br>(optimum) | Best aligned reference magnet <sup>(1)</sup><br>over temperature -40°C to 150°C<br>over full turn 360°     | -0.9 |     | 0.9 | deg  |

| INL         | Integral Non-Linearity              | Reference magnet <sup>(1)</sup> over<br>temperature -40°C to 150°C over<br>full turn 360° and displacement | -1.4 |     | 1.4 | deg  |

| ST          | Sampling Time                       |                                                                                                            |      | 128 |     | μs   |

| SPDF        | System Propagation<br>Delay Fast    | Depending on the PSI5 standard                                                                             | 200  |     | 500 | μs   |

| CoreClk     | Core Clock                          |                                                                                                            |      | 16  |     | MHz  |

| Coreclk tol | Tolerance of the Core<br>Clock      |                                                                                                            | -3.5 |     | 3.5 | %    |

| ON          | Output Noise Peak to<br>Peak        | Related to 12-bit<br>Not tested                                                                            |      |     | 4   | LSB  |

#### Note(s):

1. Reference magnet: NdFeB, 8mm diameter, 2.5mm thickness.

#### Figure 8: Power Management – Supply Monitor - Timing

| Symbol      | Parameter                           | Conditions                                                                                                    | Min  | Тур  | Мах  | Unit |

|-------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VDDUVTH     | VDD Undervoltage<br>Upper Threshold |                                                                                                               | 3.6  | 3.8  | 4.0  | V    |

| VDDUVTL     | VDD Undervoltage<br>Lower Threshold |                                                                                                               | 3.4  | 3.6  | 3.8  | V    |

| VDDUH       | VDD Undervoltage<br>Hysteresis      | Info parameter                                                                                                | 150  | 200  | 250  | mV   |

| UVDT        | VDD Undervoltage<br>Detection Time  |                                                                                                               | 10   | 50   | 250  | μs   |

| UVRT        | Undervoltage<br>Recovery Time       |                                                                                                               | 10   | 50   | 250  | μs   |

| VDDOVTH     | VDD Overvoltage<br>Upper Threshold  | If sensor in overvoltage<br>condition, ECU gets the Error<br>flag> overheating possible<br>in the application | 16.7 | 18   | 19.1 | V    |

| VDDOVTL     | VDD Overvoltage<br>Lower Threshold  |                                                                                                               | 14.5 | 15.5 | 16.5 | V    |

| OVDT        | VDD Overvoltage<br>Detection Time   | From the time VDD<br>exceeding 16.5V                                                                          |      | 1000 | 2000 | μs   |

| OVRT        | VDD Overvoltage<br>Recovery Time    | From the time VDD returning<br>from VDD > 16.5V to normal<br>operating voltage<br>(4V< VDD < 17V)             |      | 1000 | 2000 | μs   |

| VDD3V3UVTH  | VDD3V3 Reset Upper<br>Threshold     |                                                                                                               | 2.5  | 2.8  | 2.95 | V    |

| VDD3V3UVTL  | VDD3V3 Reset Lower<br>Threshold     |                                                                                                               | 2.4  | 2.6  | 2.72 | V    |

| VDD3V3UVHYS | VDD3V3 Reset<br>Hysteresis          | Info parameter                                                                                                | 105  | 175  | 245  | mV   |

| TDETWD      | WatchDog Error<br>Detection Time    |                                                                                                               |      |      | 12   | ms   |

#### **Magnetic Characteristics**

$T_{AMB}$ = -40°C to 125°C for AS5172E/F; VDD= 4V – 12V (sync pulse voltage not included); unless otherwise noted.

Two-pole cylindrical diametrically magnetized source:

Figure 9: Magnetic Characteristics

| Symbol              | Parameter                                               | Conditions                                                                                                                                    | Min | Тур | Max | Unit |

|---------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Bz                  | Orthogonal Magnetic<br>Field Strength                   | Required orthogonal<br>component of the magnetic<br>field strength measured at the<br>package surface along a circle<br>of 1.25 mm @= 0       | 30  |     | 70  | mT   |

| BzE                 | Orthogonal Magnetic<br>Field Strength –Extended<br>Mode | Required orthogonal<br>component of the magnetic<br>field strength measured at the<br>package surface along a circle<br>of 1.25mm<br>MFER = 1 | 10  |     | 90  | mT   |

| Disp <sup>(1)</sup> | Displacement Radius                                     | Offset between defined device<br>center and magnet axis.<br>Dependent on the selected<br>magnet.                                              |     | 0.5 |     | mm   |

#### Note(s):

1. Reference magnet: NdFeB, 8mm diameter, 2.5mm thickness.

# Electrical and Timing Characterization of the PSI5 Interface

This chapter describes the synchronization signal from the ECU according to the PSI5 specification V1.3 and V2.1. The parameters in this chapter are not reflecting the full specification range of the detection circuit for the synchronization signal.

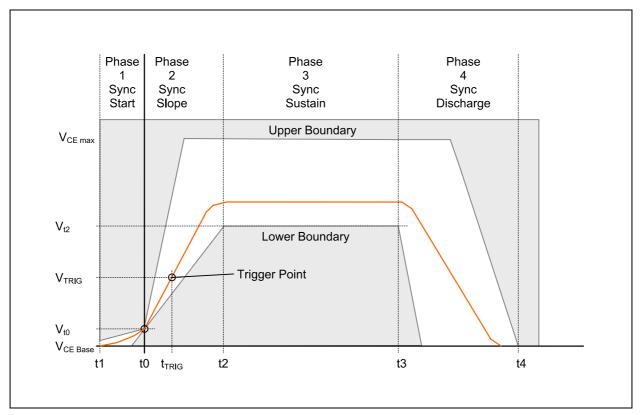

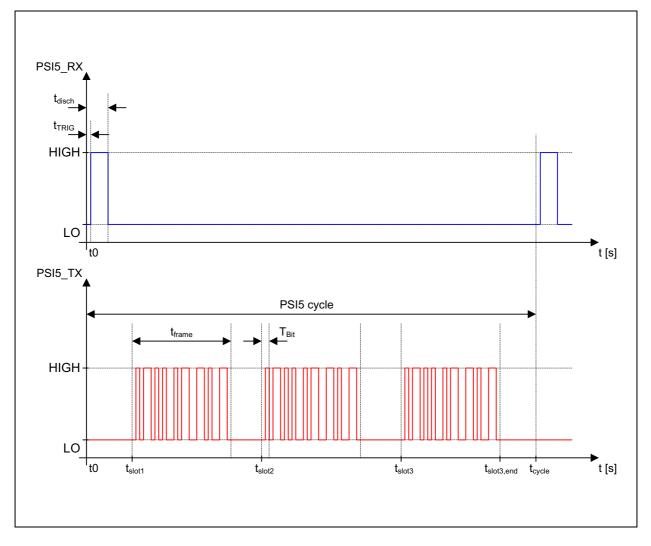

#### Synchronization Signal PSI5 V1.3

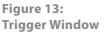

The synchronization signal start time t0 is defined as a crossing of the Vt0 value. In the "Sync Start" phase before this point, a "rounding in" of the voltage starting from VCE, Base to Vt0 is allowed for a maximum of t1. During the "Sync Slope" phase, the voltage rises within given slew rates to a value between the minimum sync signal voltage Vt2 and the maximum interface voltage VCE, max. After maintaining the voltage between this limits until a minimum of t3, the voltage decreases in the "Sync Discharge" phase until having reached the initial VCE, base value until latest t4.

#### Figure 11:

Synchronization Signal PSI5 V1.3 (1)

| Symbol  | Parameter                    | Conditions                                                       | Min   | Тур | Max  | Unit |

|---------|------------------------------|------------------------------------------------------------------|-------|-----|------|------|

| VBase   | Base Supply Voltage          | Voltage value at ECU                                             | 5.7   |     | 11   | V    |

| Vto     | Sync Slope Reference Voltage | Reference to VBase                                               |       | 0.5 |      | V    |

| Vt2     | Sync Signal Sustain Voltage  | Reference to VBase                                               | 3.5   |     |      | V    |

| Vce,max | Maximum Interface Voltage    |                                                                  |       |     | 16.5 | V    |

| t0      | Reference Time               | Reference time base; time<br>when the sync signal<br>crosses Vt0 |       | 0   |      | μs   |

| t1      | Sync Signal Earliest Start   | V=V <sub>CE</sub><br>Delta current less than<br>2mA              | -3    |     | 0    | μs   |

| t2      | Sync Signal Sustain Start    | @ Vt2                                                            |       | 7   |      | μs   |

|         | Sync Slope Rising Slew Rate  | Lower limit is valid for Vto<br>to Vt2                           | 0.43  | 1.0 | 1.5  | V/µs |

|         | Sync Slope Falling Slew Rate |                                                                  | -1.5  |     |      | V/µs |

| t3      | Sync Signal Sustain Time     |                                                                  |       | 16  |      | μs   |

| t4      | Discharge Time Limit         |                                                                  |       | 35  |      | μs   |

| Tslot1  | Start of Time Slot 1         |                                                                  | 44    | 51  | 59   | μs   |

| Tslot2  | Start of Time Slot 2         |                                                                  | 181.3 | 195 | 210  | μs   |

| Tslot3  | Start of Time Slot 3         |                                                                  | 328.9 | 350 | 373  | μs   |

#### Note(s):

1. The parameters in this table are just info parameters and therefore not production tested. The production related parameters are in the PSI5 Block Parameters table.

### Figure 12:

### Synchronization Signal PSI5 V2.1 <sup>(1)</sup>

| Symbol  | Parameter                    | Conditions                                                        | Min          | Тур | Max  | Unit |

|---------|------------------------------|-------------------------------------------------------------------|--------------|-----|------|------|

| VBase   | Base Supply Voltage          | Voltage value at ECU                                              | 5.7<br>(4.4) |     | 11   | V    |

| Vto     | Sync Slope Reference Voltage | Reference to VBase                                                |              | 0.5 |      | V    |

| Vt2     | Sync Signal Sustain Voltage  | Reference to VBase                                                | 3.5<br>(2.5) |     |      | V    |

| Vce,max | Maximum Interface Voltage    |                                                                   |              |     | 16.5 | V    |

| tO      | Reference Time               | Reference time base; time<br>when they sync signal<br>crosses Vt0 |              | 0   |      | μs   |

| t1      | Sync Signal Earliest Start   | V=V <sub>CE</sub><br>Delta current less than<br>2mA               | -3           |     | 0    | μs   |

| t2      | Sync Signal Sustain Start    | @ Vt2                                                             |              | 7   |      | μs   |

|         | Sync Slope Rising Slew Rate  | Lower limit is valid for Vt0<br>to Vt2                            | 0.43         |     | 1.5  | V/µs |

|         | Sync Slope Falling Slew Rate |                                                                   | -1.5         |     |      | V/µs |

| t3      | Sync Signal Sustain Time     |                                                                   |              | 16  |      | μs   |

| t4      | Discharge Time Limit         |                                                                   |              |     | 35   | μs   |

| Tslot1  | Start of Time Slot 1         |                                                                   | 44           |     |      | μs   |

#### Note(s):

1. The parameters in this table are just info parameters and therefore not production tested. The production related parameters are in the PSIS Block Parameters table.

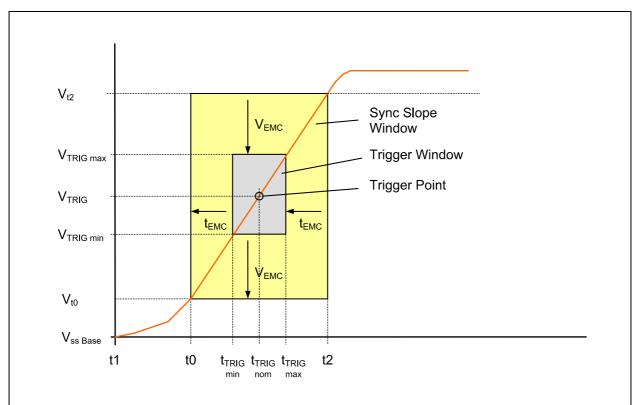

### **Synchronization Signal Detection**

The AS5172E/F has to detect the trigger within the "trigger window" during the rising slope of the synchronization signal at the trigger point with the trigger voltage  $V_{TRIG}$  and the trigger time  $t_{TRIG}$ .

In order to take into account voltage differences at different points of the interface lines, an additional safety margin for the trigger detection is defined by  $V_{EMC}$  and  $t_{EMC}$ .

The values are based on the PSI5 specification and shows the detection of the synchronization signal from the ECU according the PSI5 specification.

# Figure 14:

Synchronization Detection <sup>(1)</sup>

| Symbol      | Parameter                                                              | Conditions                                                                                                                         | Min  | Тур | Мах  | Unit |

|-------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| VEMC_C      | Margin for Voltage Variations                                          | Common power mode                                                                                                                  | -0.9 |     | 0.9  | V    |

| VEMC_LP     | Margin for Voltage Variations                                          | Low power mode                                                                                                                     | -0.7 |     | 0.7  | V    |

| VTrig_C     | Trigger Voltage Threshold                                              | Common power mode                                                                                                                  | 1.4  | 2.0 | 2.6  | V    |

| VTrig_LP    | Trigger Voltage Threshold                                              | Low power mode                                                                                                                     | 1.2  | 1.5 | 1.8  | V    |

| tTRIG       | Nominal Trigger Detection<br>Time                                      | @ V <sub>TRIG</sub> , @ AS5172E/F Pins;<br>Referenced to a straight<br>sync signal slope with<br>nominal slew rate of 0.43<br>V/μs | 2.1  | 3.5 | 4.9  | μs   |

| VCE,max     | Maximum Interface Voltage                                              |                                                                                                                                    |      |     | 16.5 | V    |

| tEMC        | Margin for Timing Variations<br>of the Signal on the Interface<br>Line | Relative to nominal trigger<br>window time                                                                                         | -2.1 |     | 2.1  | μs   |

| ttol detect | Tolerance of Internal Trigger<br>Detection Delay                       |                                                                                                                                    |      |     | 3    | μs   |

| TTRIG       | Trigger Detection Time                                                 | $T_{TRIG} = t_{TRIG} + t_{tol detect} + t_{EMC};$<br>Reference for AS5172E/F<br>time base                                          | 0    |     | 10   | μs   |

#### Note(s):

1. The parameters in this table are just info parameters and therefore not production tested. The production related parameters are in the PSI5 Block Parameters table.

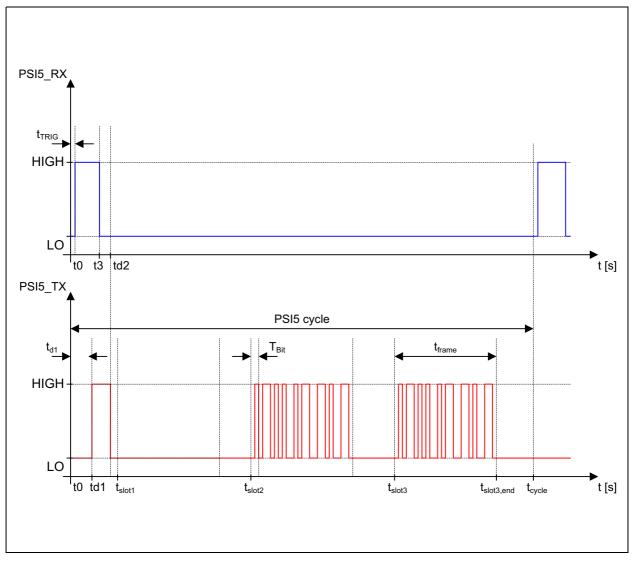

# Synchronization Signal with Discharge by AS5172E/F

This chapter describes the modifications required if the ECU uses a special transreceiver.

The parameters in this chapter are not reflecting the full specification range of the detection circuit for the synchronization signal.

Figure 15: Synchronization Signal from ECU with Discharge by the AS5172E/F

#### Figure 16:

Synchronization Signal from ECU with Discharge Parameter  $^{(1)}$

| Symbol                  | Parameter                                                              | Conditions                                                                                                                        | Min   | Тур   | Max  | Unit |

|-------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|

| V <sub>CE, BASE</sub>   | Base Supply Voltage                                                    | Mean voltage value at ECU                                                                                                         | 5.0   | 6.0   | 7.0  | V    |

| V <sub>CE, BASE_R</sub> | Base Supply Voltage<br>Including Ripple                                |                                                                                                                                   | 4.5   | 6.0   | 7.0  | V    |

| V <sub>t0</sub>         | Sync Slope Reference<br>Voltage                                        | Referenced to V <sub>CE, BASE</sub>                                                                                               |       | 0.5   |      | V    |

| V <sub>t2</sub>         | Sync Signal Sustain Voltage                                            | Referenced to V <sub>CE, BASE</sub>                                                                                               | +3.5  | +5.0  | +6.0 | V    |

| V <sub>CE,max</sub>     | Sync Signal Max. Voltage                                               |                                                                                                                                   | 10    | 11    | 14.5 | V    |

| V <sub>CE,max_R</sub>   | Sync Signal Max. Voltage<br>Including Ripple                           |                                                                                                                                   | 10    | 14    | 16.5 | V    |

| t0                      | Reference Time                                                         | Reference time base; time<br>when the synchronization<br>signal crosses V <sub>t0</sub>                                           |       | 0     |      | μs   |

| t1                      | Sync Signal Earliest Start                                             | V=V <sub>CE, BASE</sub>                                                                                                           | -3    |       | 0    | μs   |

| t2                      | Sync Signal Sustain Start                                              | @ V <sub>t2</sub>                                                                                                                 | 3     | 4     | 5    | μs   |

| S <sub>sync,r</sub>     | Sync Slope Rising Slew Rate                                            | 10% to 90% of V <sub>CE,max</sub>                                                                                                 | 0.7   | 1.0   | 1.6  | V/µs |

| S <sub>sync,f</sub>     | Sync Slope Falling Slew Rate                                           | 90% down to 10% of<br>V <sub>CE,max</sub>                                                                                         | -1.6  | -1.0  | -0.7 | V/µs |

| t3                      | Sync Signal Sustain Time                                               | V=V <sub>CE,sync</sub>                                                                                                            | 27.5  | 31    | 35.1 | μs   |

| td1                     | AS5172E/F Signals<br>Discharge                                         |                                                                                                                                   | 18.5  | 22.75 | 28   | μs   |

| td2                     | Discharge Stop Time                                                    |                                                                                                                                   | 38    | 43.25 | 50   | μs   |

| t4                      | Enable Pull Down to<br>V <sub>CE,BASE</sub> by ECU                     |                                                                                                                                   | 62.5  | 65    | 65.5 | μs   |

| t5                      | Receiver (ECU) Enable Start<br>Time                                    | Receiver (ECU) read for transmission                                                                                              | 63    | 66.2  | 65.5 | μs   |

| V <sub>TRIG</sub>       | Trigger Voltage Threshold                                              |                                                                                                                                   | 1.4   | 2.0   | 2.6  | V    |

| t <sub>TRIG</sub>       | Nominal Trigger Detection<br>Time                                      | @ V <sub>TRIG</sub> , @ AS5172E/F Pins;<br>Referenced to a straight<br>sync signal slope with<br>nominal slew rate of 0.7<br>V/μs | 1.25  | 2.15  | 3.05 | μs   |

| t <sub>EMC</sub>        | Margin for Timing Variations<br>of the Signal on the<br>Interface Line | Relative to nominal trigger<br>window time                                                                                        | -1.25 |       | 1.25 | μs   |

| Symbol                  | Parameter                                        | Conditions                                                                          | Min   | Тур | Max | Unit |

|-------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------|-------|-----|-----|------|

| t <sub>tol detect</sub> | Tolerance of Internal Trigger<br>Detection Delay |                                                                                     |       |     | 3   | μs   |

| T <sub>TRIG</sub>       | Trigger Detection Time                           | $T_{TRIG} = t_{TRIG} + t_{tol detect} + t_{EMC};$<br>Reference for sensor time base | 0     |     | 7.5 | μs   |

| t <sub>slot 1</sub>     | Start of Time Slot 1                             | Time slot 1 cannot be used<br>in this communication<br>mode                         | 44    | 51  | 59  | μs   |

| t <sub>slot2</sub>      | Start of Time Slot 2                             |                                                                                     | 181.3 | 195 | 210 | μs   |

| t <sub>slot3</sub>      | Start of Time Slot 3                             |                                                                                     | 328.9 | 350 | 373 | μs   |

#### Note(s):

1. The parameters in this table are just info parameters and therefore not production tested. The production related parameters are in the PSI5 Block Parameters table.

#### **PSI5 Block Parameters**

Figure 17: Block Parameters

| Symbol                   | Parameter                                                  | Conditions                                                                                        | Min   | Тур  | Max  | Unit |

|--------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------|------|------|------|

| V <sub>CE,BASE ECU</sub> | Base ECU Supply Voltage                                    | Voltage at ECU                                                                                    | 4.4   |      | 11   | V    |

| V <sub>CE,BASE</sub>     | Base Supply Voltage                                        | Voltage at the Sensor                                                                             | 4.0   |      | 11   | V    |

| V <sub>SUPPLY</sub>      | Low Supply Voltage                                         | Supply voltage for<br>comparator                                                                  | 3.3   | 3.45 | 3.6  | V    |

| V <sub>t0</sub>          | Sync Slope Reference                                       | Referred to V <sub>CE,BASE</sub>                                                                  |       | 0.5  |      | V    |

| V <sub>t2</sub>          | Minimum Sync Signal<br>Sustain Voltage (common<br>mode)    | Referred to V <sub>CE,BASE</sub>                                                                  | 3.5   |      |      | V    |

| V <sub>t2_L</sub>        | Minimum Sync Signal<br>Sustain Voltage (low power<br>mode) | Referred to V <sub>CE,BASE</sub>                                                                  | 2.5   |      |      | V    |

| V <sub>CE MAX</sub>      | Maximum Interface Voltage                                  |                                                                                                   |       |      | 16.5 | V    |

| t <sub>2</sub>           | Sync Signal Sustain Start                                  | Voltage @V <sub>t2</sub>                                                                          |       |      | 7    | μs   |

| SL <sub>RISE</sub>       | Rising Slope                                               |                                                                                                   | 0.43  |      | 1.6  | V/µs |

| SL <sub>FALL</sub>       | Falling Slope                                              | Depends on voltage and<br>discharge limit,<br>external load has to meet<br>these values           | -1.75 |      |      | V/µs |

| t <sub>3</sub>           | Sync Signal Sustain Time                                   | Info parameter:<br>Recommended ECU timing                                                         | 16    |      | 35.1 | μs   |

| t <sub>4</sub>           | Discharge Time Limit                                       | Info parameter:<br>Allowed variation of synch<br>pulse width for synch<br>pulse detection circuit | 17.67 |      | 62   | μs   |

| T <sub>SYNC</sub>        | Synchronization Period                                     | Info parameter:<br>To prevent shifts of<br>detection threshold                                    | 250   | 500  |      | μs   |

| V <sub>TRIG</sub>        | Trigger Voltage Threshold<br>(common mode)                 |                                                                                                   | 1.4   | 2.0  | 2.6  | V    |

| V <sub>TRIG_L</sub>      | Trigger Voltage Threshold<br>(low power mode)              |                                                                                                   | 1.2   | 1.5  | 1.8  | V    |

| Symbol                  | Parameter                                                                                                                                                                                               | Conditions                                                                                                                                                                  | Min  | Тур | Мах  | Unit |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| V <sub>TRIG EMC</sub>   | Trigger Voltage Threshold<br>Under EMC (common<br>mode)                                                                                                                                                 | At SL <sub>RISE</sub> = 0.43 V/μs;<br>For EMC<br>≤1V <sub>PEAK</sub><br>≥ 100kHz<br>Not tested - Guaranteed by<br>Design                                                    | 0.5  | 2.0 | 3.5  | v    |

| V <sub>TRIG EMC</sub>   | Trigger Voltage Threshold<br>Under EMC (low power<br>mode) At $SL_{RISE} = 0.43 \text{ V/}\mu\text{s}$ ;<br>For EMC<br>$\leq 1V_{PEAK}$<br>$\geq 100\text{kHz}$<br>Not tested - Guaranteed by<br>Design |                                                                                                                                                                             | 0.5  | 1.5 | 2.5  | v    |

| t <sub>tol detect</sub> | Tolerance of Internal<br>Trigger Detection Delay                                                                                                                                                        |                                                                                                                                                                             |      |     | 3    | μs   |

| t <sub>BLANK</sub>      | Output Signal Blanking<br>Time                                                                                                                                                                          | Blanking of trigger signal<br>in digital part after first<br>rising edge to avoid<br>multiple trigger signals<br>during EMC events.<br>Not tested - Guaranteed by<br>Design | 121  |     | 135  | μs   |

| V <sub>COM</sub>        | Comparator Input<br>Common Mode Voltage                                                                                                                                                                 |                                                                                                                                                                             |      | 1.5 |      | V    |

| RES <sub>div</sub>      | Resistor Divider Division<br>Factor                                                                                                                                                                     | Not tested - Guaranteed by<br>Design<br>2% mismatch                                                                                                                         | 7.84 | 8   | 8.16 | V/V  |

| f <sub>C_LP</sub>       | Low Pass Filter Cut-Off<br>Frequency                                                                                                                                                                    | Not tested - Guaranteed by<br>Design                                                                                                                                        | 2.5  | 5   | 7.5  | kHz  |

#### **Detailed Description**

The AS5172E/F is a Hall-based rotary magnetic position sensor using a CMOS technology. The lateral Hall sensor array converts the magnetic field component perpendicular to the surface of the chip into a voltage.

The signals coming from the Hall sensors are first amplified and filtered before being converted by the analog-to-digital converter (ADC). The output of the ADC is processed by the CORDIC block (Coordinate-Rotation Digital Computer) to compute the angle and magnitude of the magnetic field vector. The sensor and analog front-end (AFE) section works in a closed loop alongside an AGC to compensate for temperature and magnetic field variations. The calculated magnetic field strength (MAG), the automatic gain control (AGC) and the angle can be read through the UART-over-PSI5 protocol during programming.

The magnetic field coordinates provided by the CORDIC block are fed into a linearization block (DSP) which generates the transfer function.

The output of the AS5172E/F can be programmed to define a starting position (zero angle) and a stop position (maximum angle).

The AS5172E/F can be programmed through the VDD Pin with a special UART-over-PSI5 protocol which allows writing an on-chip non-volatile memory (One Time Programmable memory) where the specific settings are stored.

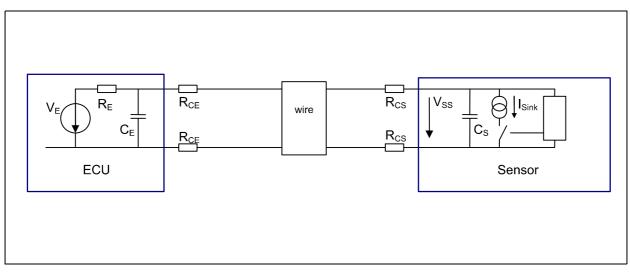

The AS5172E/F is equipped with a PSI5 Interface current driver and a PSI5 Interface receiver. The current driver drives the additional sink current to reach the I\_high level on the VDD. The receiver is comparing the voltage level at the VDD Pin with the internal voltage thresholds.

The Sensor to ECU communication is described in the chapters below and is based upon the PSI5 standard.

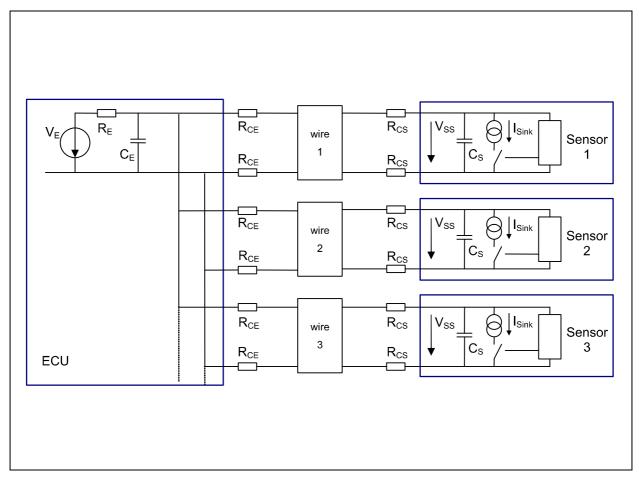

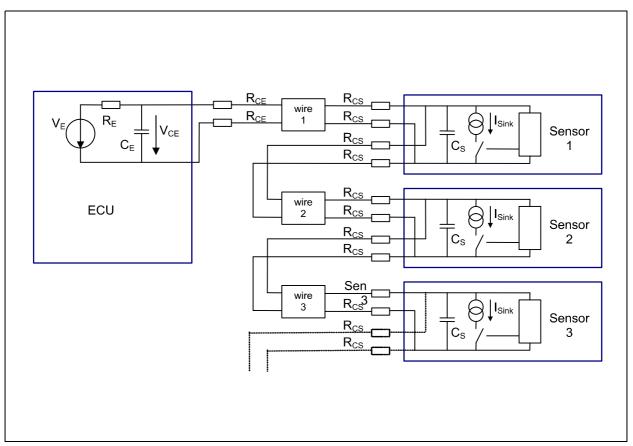

The AS5172E/F supports, according the PSI5 standard, the synchronous mode or in asynchronous mode.

In PSI5 V1.3 (10-bit mode), the asynchronous modes can only use one time slot per period. For a transmission of one 12/16 bit data word, two periods are necessary.

AS5172E/F supports the bus modes PSI5-U and PSI5-P. The daisy chain mode is not supported.

# **Register Description**

# OTP (non-volatile memory) Register Description

Figure 18:

OTP (non-volatile memory) Register Description

| Address | Bit Nr. | Symbol                       | Description                                                                |  |  |

|---------|---------|------------------------------|----------------------------------------------------------------------------|--|--|

|         | 0       | velocity_compatibility_range | Changes max velocity range to 4608 deg/s                                   |  |  |

|         | 1       | PSI516bitmode_noE            | PSI5 setting for 16-bit data frame without error bit                       |  |  |

|         | 2       | Direction                    | Changes direction in 14-bit mode                                           |  |  |

|         | 3       | PSI5_14bit_angle             | Enables 14-bit angle output                                                |  |  |

| 0x01    | 4       | PSI5_quad_info               | Enables quadrant information                                               |  |  |

|         | 5       | PSI5_16bit_frame             | Enables the PSI5 16-bit frame                                              |  |  |

|         | 6       | Velocity_extended_range      | 0 = 1250 deg/s<br>1 = 5000 deg/s                                           |  |  |

|         | 7       | Extended_init_phase          | 0 = 22 datablocks during Init phase<br>1 = 32 datablocks during Init phase |  |  |

| 0x02    | 0       | Factory settings             | ams factory settings                                                       |  |  |

| 0x02    | 7:1     | ams ID                       | ams ID (F9)                                                                |  |  |

| 0x03    | 7:0     | ams ID                       | ams ID (F9)                                                                |  |  |

| 0x04    | 5:0     | ams ID                       | ams ID (F9)                                                                |  |  |

| 0x04    | 7:6     | Factory settings             | ams factory settings                                                       |  |  |

| 0x05    | 7:0     |                              |                                                                            |  |  |

| 0x06    | 7:0     |                              |                                                                            |  |  |

| 0x07    | 7:0     |                              |                                                                            |  |  |

| 0x08    | 7:0     | Factory settings             | ams factory settings                                                       |  |  |

| 0x09    | 7:0     |                              |                                                                            |  |  |

| 0x0A    | 7:0     |                              |                                                                            |  |  |

| 0x0B    | 7:0     |                              |                                                                            |  |  |

| Address | Bit Nr. | Symbol       | Description                 |

|---------|---------|--------------|-----------------------------|

|         | 0       | Month[3]     |                             |

|         | 1       | Year[0]      |                             |

|         | 2       | Year[1]      |                             |

| 0x0C    | 3       | Year[2]      | Conser Duaduation Data (EQ) |

| UXUC    | 4       | Year[3]      | Sensor Production Date (F8) |

|         | 5       | Year[4]      |                             |

|         | 6       | Year[5]      |                             |

|         | 7       | Year[6]      |                             |

|         | 0       | Day[0]       |                             |

|         | 1       | Day[1]       |                             |

|         | 2       | Day[2]       |                             |

| 0x0D    | 3       | Day[3]       | Sensor Production Date (F8) |

| 0,000   | 4       | Day[4]       |                             |

|         | 5       | Month[0]     |                             |

|         | 6       | Month[1]     |                             |

|         | 7       | Month[2]     |                             |

|         | 0       | Type[0]      |                             |

|         | 1       | Type[1]      | Sensor Type (F4)            |

|         | 2       | Type[2]      |                             |

| 0x0E    | 3       | Type[3]      |                             |

| UXUE    | 4       | Parameter[4] |                             |

|         | 5       | Parameter[5] | Sensor Parameter (F5)       |

|         | 6       | Parameter[6] | י אבוואטו דמומווופובו (ו א) |

|         | 7       | Parameter[7] |                             |

| Address | Bit Nr. | Symbol                   | Description                                            |

|---------|---------|--------------------------|--------------------------------------------------------|

|         | 0       | Parameter[0]             |                                                        |

|         | 1       | Parameter[1]             | Sensor Parameter (F5)                                  |

| 0x0F    | 2       | Parameter[2]             |                                                        |

|         | 3       | Parameter[3]             |                                                        |

| UXUF    | 4       | Sensor_Code_Man[4]       |                                                        |

|         | 5       | Sensor_Code_Man[5]       | Sanaan Cada Manufasturan (EC)                          |

|         | 6       | Sensor_Code_Man[6]       | - Sensor Code Manufacturer (F6)                        |

|         | 7       | Sensor_Code_Man[7]       |                                                        |

|         | 0       | Sensor_Code_Man[0]       |                                                        |

|         | 1       | Sensor_Code_Man[1]       | Sanaan Cada Manufasturan (EC)                          |

| 0x10    | 2       | Sensor_Code_Man[2]       | - Sensor Code Manufacturer (F6)                        |

|         | 3       | Sensor_Code_Man[3]       |                                                        |

| 0x10    | 4       | Sensor_Code_Veh[3]       |                                                        |

|         | 5       | Sensor_Code_Veh[3]       | -<br>Concer Code Vehicle (F7)                          |

|         | 6       | Sensor_Code_Veh[3]       | - Sensor Code Vehicle (F7)                             |

|         | 7       | Sensor_Code_Veh[3]       |                                                        |

| 0x11    | 7:0     | PSI5Mode                 | PSI5 mode selection                                    |

|         | 0       | Sync_discharge           | Enables sync pulse discharging                         |

|         | 1       | Init_phase_repetition[0] | DCIE initialization whose constition factor (), times) |

|         | 2       | Init_phase_repetition[1] | PSI5 initialization phase repetition factor (k-times)  |

| 0.12    | 3       | PSI5_timeslot[0]         | DCIE timeslet far hus mode                             |

| 0x12    | 4       | PSI5_timeslot[1]         | PSI5 timeslot for bus mode                             |

|         | 5       | Init_phase_disable       | Disables the PSI5 initialization phase                 |

|         | 6       | Velocity_info            | Enables PSI5 velocity output                           |

|         | 7       | Psi5_4_timeslot          | Enables PSI5 with 4 timeslots (16-bit mode only)       |

| Address | Bit Nr. | Symbol               | Description                                             |

|---------|---------|----------------------|---------------------------------------------------------|

|         | 0       | Psi5_16_bit_new_init | Use different initialization frame for PSI5 16-bit mode |

|         | 1       | -                    | Not used                                                |

|         | 2       | -                    | Not used                                                |

| 0x13    | 3       | Quadrant[0]          | Quadrant calestian                                      |

|         | 4       | Quadrant[1]          | - Quadrant selection                                    |

|         | 5       | Velocity_filter[0]   |                                                         |

|         | 6       | Velocity_filter[1]   | Filter configuration for velocity measurement           |

|         | 7       | Velocity_filter[2]   |                                                         |

| 0x14    | 7:0     | CLH[7:0]             | Clamping level high                                     |

|         | 0       | CLH[8]               |                                                         |

|         | 1       | CLH[9]               |                                                         |

|         | 2       | CLH[10]              | - Clamping level high                                   |

| 0.15    | 3       | CLH[11]              |                                                         |

| 0x15    | 4       | CLL[0]               |                                                         |

|         | 5       | CLL[1]               |                                                         |

|         | 6       | CLL[2]               | - Clamping level low                                    |

|         | 7       | CLL[3]               |                                                         |

| 0x16    | 7:0     | CLL[11:4]            | Clamping level low                                      |

| 0x17    | 7:0     | Offset[7:0]          | Offset                                                  |

| 0x18    | 7:0     | Offset[15:8]         | Offset                                                  |

|         | 0       | Offset[16]           |                                                         |

|         | 1       | Offset[17]           | Offset                                                  |

|         | 2       | Offset[18]           | Onset                                                   |

| 0x19    | 3       | Offset[19]           |                                                         |

| UXIY    | 4       | Gain[0]              |                                                         |

|         | 5       | Gain[1]              | Cain                                                    |

|         | 6       | Gain[2]              | - Gain                                                  |

|         | 7       | Gain[3]              |                                                         |

| 0x1A    | 7:0     | Gain[11:4]           | Gain                                                    |

| Address | Bit Nr. | Symbol                 | Description                                                    |

|---------|---------|------------------------|----------------------------------------------------------------|

|         | 0       | Gain[12]               |                                                                |

|         | 1       | Gain[13]               |                                                                |

|         | 2       | Gain[14]               | Gain                                                           |

| 0x1B    | 3       | Gain[15]               |                                                                |

| UXID    | 4       | Gain[16]               |                                                                |

|         | 5       | BP[0]                  |                                                                |

|         | 6       | BP[1]                  | Breakpoint / 14-Bit Mode zero offset                           |

|         | 7       | BP[2]                  |                                                                |

| 0x1C    | 7:0     | BP[10:3]               | Breakpoint / 14-Bit Mode zero offset                           |

|         | 0       | BP[11]                 |                                                                |

|         | 1       | BP[12]                 | Breakpoint / 14-Bit Mode zero point offset                     |

|         | 2       | BP[13]                 |                                                                |

| 0x1D    | 3       | Extended_range_disable | Disables the extended range for magnetic input field           |

| UXID    | 4       | Reduced_angle_range    | Enables the reduced angle range for segments smaller 23 degree |

|         | 5       | -                      | Not used                                                       |

|         | 6       | -                      | Not used                                                       |

|         | 7       | Customer_lock          | Customer lock                                                  |

| 0x1E    | 7:0     | VendorID[7:0]          | Vendor ID (F3)                                                 |

| 0x1F    | 7:0     | Signature[7:0]         | Signature calculated across the full OTP                       |

### Volatile Memory Register Description

#### Figure 19: Volatile Memory Register Description

| Address | Bit Nr. | Symbol             | R/W | Description                                     |

|---------|---------|--------------------|-----|-------------------------------------------------|

|         | 4:0     | -                  |     | Not used                                        |

| 0x23    | 5       | DSP_reset          | R/W | Reset of the DSP (Digital Signal Processing)    |

|         | 6       | GLoad              | R/W | Enables GLoad                                   |

|         | 7       | -                  |     | Not used                                        |

| 0x32    | 7:0     | Angle_CORDIC[7:0]  | R   | 14-Bit Angle information (raw value without     |

| 0x33    | 5:0     | Angle_CORDIC[13:8] | R   | zero offset)                                    |

| 0,55    | 7:6     | -                  |     | Not used                                        |

| 0x34    | 7:0     | Magnitude          | R   | Magnitude at the CORDIC output                  |

| 0x35    | 7:0     | AGC                | R   | AGC (Automatic Gain Control)                    |

| 0x36    | 7:0     | Angle_DSP[7:0]     | R   | 12-Bit Angle information (with zero offset, and |

| 0x37    | 3:0     | Angle_DSP[11:8]    | R   | customer settings)                              |

| 0,37    | 7:4     | -                  |     | Not used                                        |

| 0x38    | 7:0     | Velocity[7:0]      | R   | Velocity output                                 |

| 0x39    | 3:0     | Velocity[11:8]     | R   | velocity output                                 |

| 0222    | 7:4     | -                  |     | Not used                                        |

| 0x3A    | 7:0     | FUSA[7:0]          | R   | FUSA output                                     |

| 0x3B    | 5:0     | FUSA[13:8]         | R   |                                                 |

### SFR Description

Figure 20: SFR Description

| Address | Bit Nr. | Symbol        | Description                               |  |  |

|---------|---------|---------------|-------------------------------------------|--|--|

| 0x60    | 7:0     | Pass2Function | Pass-to-function, see Programming chapter |  |  |

| 0x61    | 7:0     |               | rass to function, see riogramming enapter |  |  |

| 0x62    | 7:0     | BurnOTP       | BurnOTP, see Programming chapter          |  |  |

| 0x63    | 7:0     | builton       | bumon, see rogramming enapter             |  |  |

#### Programming

#### **UART-Over-PSI5**

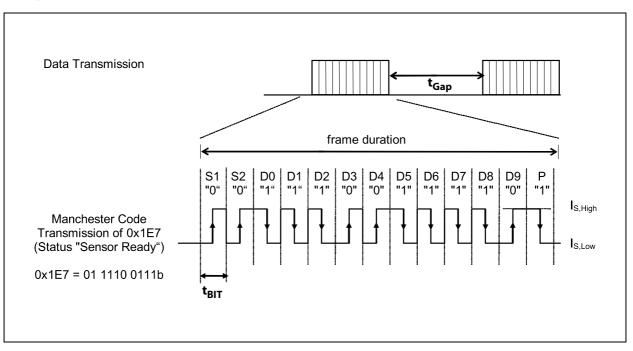

The AS5172E/F is equipped with a one wire UART-over-PSI5 interface based on a "Tooth Gap" similar method according PSI5 specification, which allows reading and writing the registers as well as permanent programming of the non-volatile OTP memory (One Time Programmable).

By default the AS5172E/F is in the so-called *Communication Mode*. In this mode, it is possible to configure the register settings.

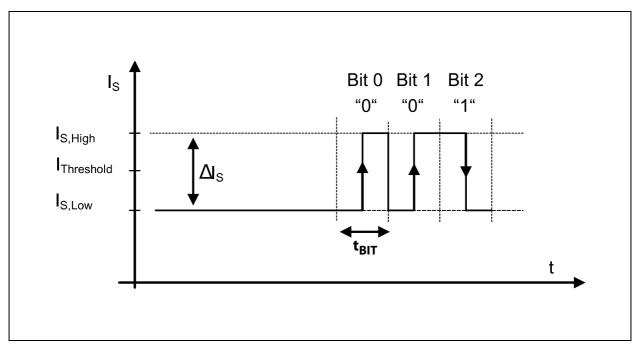

A voltage modulation on the supply lines (VDD and GND) is used to realize a Programmer-to-Sensor communication. The Sensor-to-Programmer communication is done with current modulation.

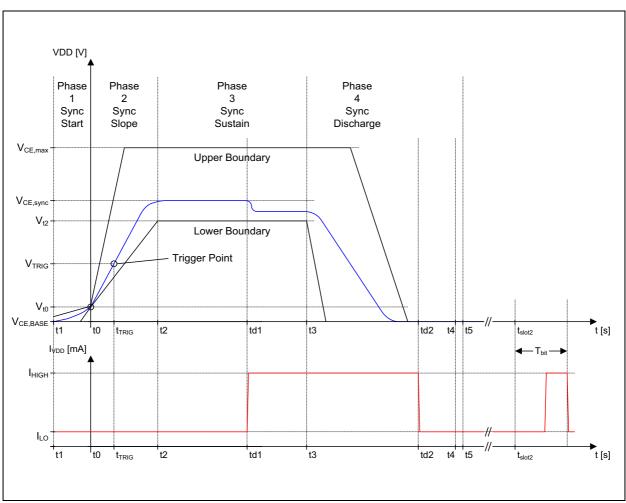

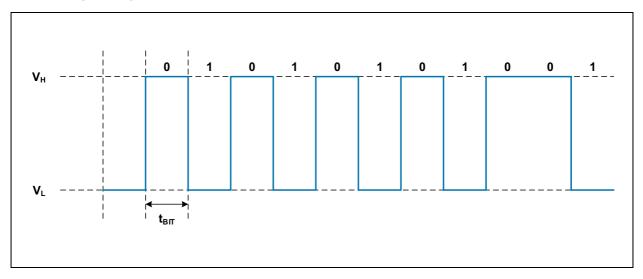

The physical layer of the two communication modes is shown in Figure 21 and Figure 22 below.

Figure 21: Bit Encoding of Programmer-to-Sensor Communication

A logical "0" is represented by a sync pulse (V<sub>H</sub>) on the VDD line for a duration of  $t_{BIT}$ . A logical "1" by the absence of the sync pulse (V<sub>L</sub>) for a duration of  $t_{BIT}$ .

#### Figure 22: Bit Encoding of Sensor-to-Programmer Communication

A logical "0" is represented by an increased sink current ( $I_H$ ) on the VDD line for a duration of  $t_{BIT.}$  A logical "1" by normal sink current ( $I_H$ ) for a duration of  $t_{BIT.}$

Figure 23: UART-Over-PSI5 Protocol

| Symbol           | Parameter               | Conditions    | Min   | Тур   | Мах   | Unit |

|------------------|-------------------------|---------------|-------|-------|-------|------|

| V <sub>H</sub>   | High Level Voltage      |               | 11    |       | 12    | V    |

| VL               | Low Level Voltage       |               | 5.5   |       | 6     | V    |

| I <sub>Н</sub>   | High Level Sink Current | Typical value |       | 49    |       | mA   |

| ١ <sub>L</sub>   | Low Level Sink Current  | Typical value |       | 19    |       | mA   |

| t <sub>BIT</sub> |                         |               | 25.6  | 26    | 26.5  | μs   |

| Baudrate         |                         |               | 37800 | 38400 | 39000 | Baud |

For further information please refer to application note AN\_AS5172\_Programming\_Procedure\_V1-00

**ams** also provides a programmer which supports the above-mentioned protocol. Please get in contact with the application engineering team.

### **UART Protocol**

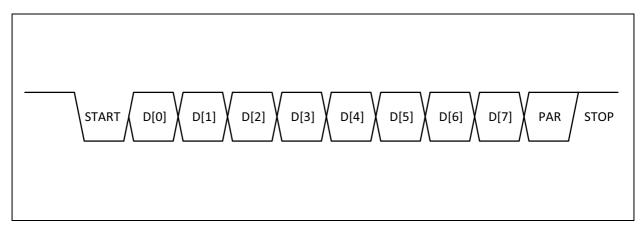

The UART interface allows reading and writing two consecutive addresses. The standard UART sequence consists of four frames. Each frame begins with a start bit (START), which is followed by 8 data bits (D[0:7]), one parity bit (PAR), and a stop bit (STOP), as shown in Figure 24.

Figure 24: UART Protocol Frame

The PAR bit is even parity calculated over the data bits (D[7:0]). Each frame is transferred from LSB to MSB.

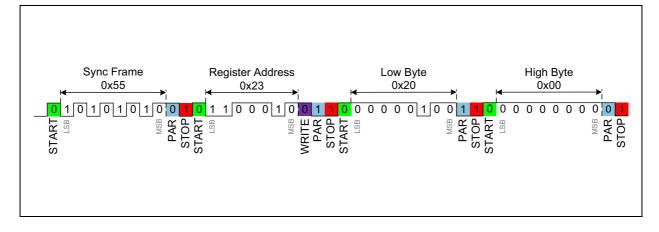

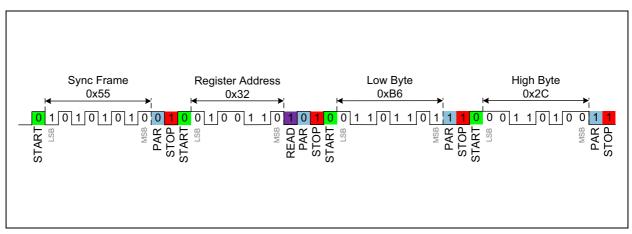

The first frame is the synchronization frame and consists D[7:0] = 0x55. This frame synchronizes the baud rate between the AS5172E/F and the programmer.

The second frame contains the register address (D[6:0] = ADDRESS) and the write/read command (WRITE: D[7]=0; READ: D[7]=1).

The third and fourth frame will be written/read to/from the location specified by ADDRESS and ADDRESS+1, respectively.

Figure 25 and Figure 26 show examples of a WRITE and READ sequence.

Figure 25: Example of WRITE (Reg[0x23] = 0x20 and Reg [0x24] = 0x00)

#### Figure 26: Example of READ (Reg[0x32] = 0xB6 and Reg [0x24] = 0x2C)

#### Reading of the 14-Bit Angle Information

To read the current position of the magnet (Angle) the following procedure is necessary:

- 1. Set the DSP\_reset bit in Reg(0x23) to 1. (WRITE Reg(0x23) = 0x20)

- 2. Read Angle\_CORDIC register (READ Reg(0x32) and Reg(0x33))

- 3. Set the DSP\_reset bit in Reg(0x23) to 0. (WRITE Reg(0x23) = 0x00)

The DSP\_reset bit resets the internal DSP. After a reset, the Angle\_CORDIC register is updated.

#### Reading the Magnitude and AGC

To read the current Magnitude and AGC value following procedure is necessary:

- Set the DSP\_reset bit in Reg(0x23) to 1. (WRITE Reg(0x23) = 0x20)

- 2. Read Magnitude and AGC register (READ Reg(0x34) and Reg(0x35))

- 3. Set the DSP\_reset bit in Reg(0x23) to 0. (WRITE Reg(0x23) = 0x00)

The DSP\_reset bit resets the internal DSP. After a reset, the Magnitude and AGC registers are updated.

#### Exiting the Communication Mode

To exit the *Communication Mode* and enter *Functional Mode* a special Pass-to-function command is necessary. Therefore a specific value has to be written into registers 0x60 and 0x61.

Pass2Function: WRITE Reg(0x60) = 0x70 and Reg(0x61) = 0x51

The device is temporarily set to operational mode until a sensor reset happens.

#### Burn the OTP Registers

To permanently program the device a special BurnOTP command is necessary. Therefore a specific value has to be written into registers 0x62 and 0x63.

BurnOTP: WRITE Reg(0x62) = 0x70 and Reg(0x63) = 0x51

This commands permanently burns the OTP memory based on poly silicon fuses. After fusing a verification of the burn quality is mandatory to avoid bit-flips over temperature and lifetime. This can be done with the GLoad operation. For further information please refer to application note  $AN_AS5172\_Programming\_Procedure\_V1-00.$

### **AS5172E/F Transfer Function**

After programming the Customer\_lock in the OTP or by using the Pass-to-function command the AS5172E/F is working in the selected PSI5 mode over the VDD pin.

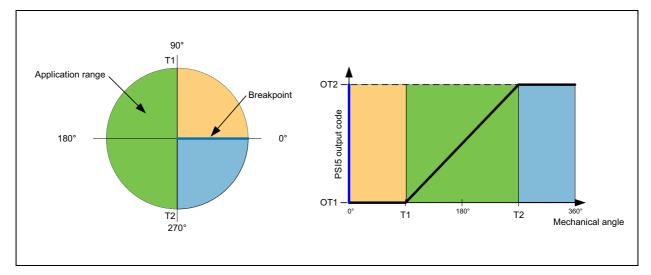

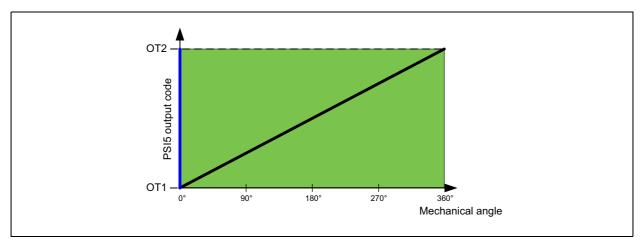

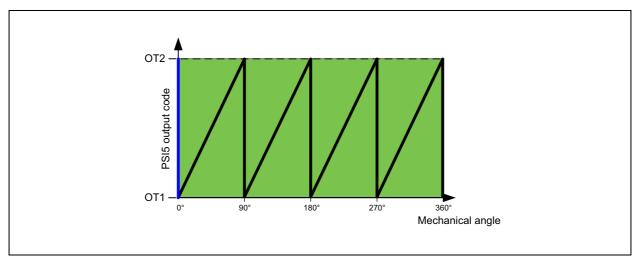

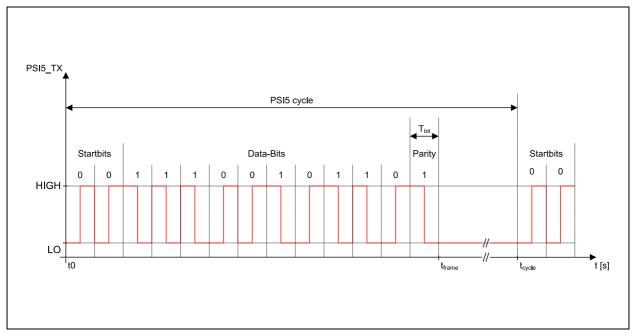

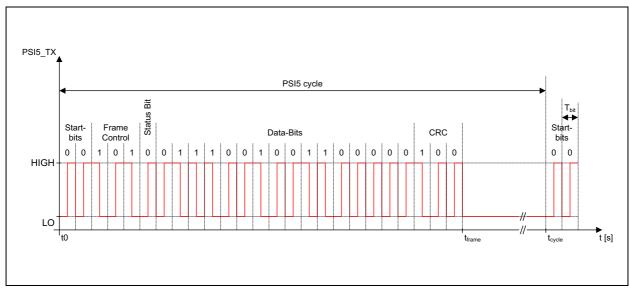

The DSP block generates a linear transfer function proportional to the angle of the rotating magnet which is fed into the PSI5 interface. The PSI5 interface works with 10-bit resolution in PSI5 V1.3 and 12-bit resolution in PSI5 V2.1. Figure 27 shows the transfer function in detail.

#### Figure 28: PSI5 Protocol Output Resolution

| Symbol   | Parameter                   | Conditions | Value | Unit |

|----------|-----------------------------|------------|-------|------|

| OTR_V1.3 | Output Resolution PSI5 V1.3 | PSI5 V1.3  | 10    | Bit  |

| OT1      |                             |            | -480  | LSB  |

| OT2      |                             |            | +480  | LSB  |

| OTR_V2.1 | Output Resolution PSI5 V2.1 | PSI5 V2.1  | 12    | Bit  |

| OT1      |                             |            | -2048 | LSB  |

| OT2      |                             |            | +2048 | LSB  |

The PSI5 output characteristic is programmable in the OTP memory. The parameters T1, T2 and BP define the linear transfer function. Figure 27 shows a simple example of a typical output function.

The mechanical starting point T1 and the mechanical end point T2 define the mechanical range. The BP (Breakpoint) defines the transition point between OT1 and OT2.

These parameters are input parameters. Using a DLL provided by **ams**, these parameters are converted into the final OTP parameters: CLH, CLL, Offset, Gain and BP.

For detailed information regarding the calculation DLL please get in contact with the application engineering team at **ams**.

### **Multiple Quadrants**

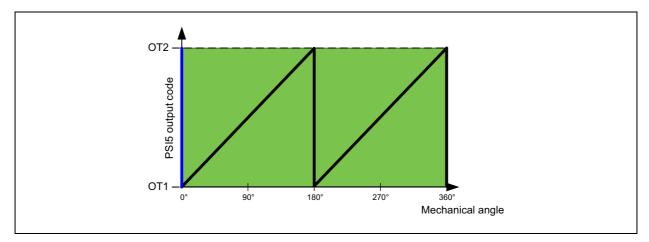

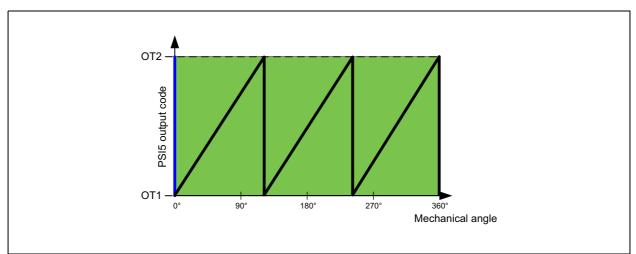

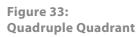

The multiple quadrant option allows repeating the same output slope up to four times over a full 360° rotation as shown in Figure 30, Figure 31, Figure 32 and Figure 33. The Quadrant bits in register (0x13) set the number of quadrant as shown in Figure 29. Additionally a built-in quadrant detection can indicate the currently active quadrant in a special PSI5 data frame. For more information please refer to chapter PSI5 Modes.

Figure 29: Quadrant Selection

| Quadrant | Number of Quadrants | Max. Mechanical Range |

|----------|---------------------|-----------------------|

| 00       | Single              | 360°                  |

| 01       | Dual                | 180°                  |

| 10       | Triple              | 120°                  |

| 11       | Quadruple           | 90°                   |

Figure 30: Single Quadrant

#### Figure 31: Dual Quadrant

Page 34 Document Feedback

#### Figure 32: Triple Quadrant

#### Extended Magnetic Input Range

By default the AS5172E/F operates in Extended Mode. This mode extends the magnetic input field range and allows increasing of the air gap between sensor and magnet. The extended range can be disabled with Extended\_range\_disable bit. For further information about the Extended Mode please refer to application note "AN\_AS5172\_ExtendedMode\_ V1-00.pdf".

#### **Rolling Counter**

The frame control bits in the PSI5 frame can be used as a rolling counter. This setting can be enabled in the OTP. If this setting is enabled the rolling counter starts incrementing from value 0x0 once the initialization is finished. When reaching a value of 0x7 the counter is reset at starts with 0x0 again.

In PSI5 16-bit frame mode, the rolling count enables a toggle bit in A14 of the frame.

#### Angular Velocity Measurement

The AS5172E/F features an average angular velocity calculation algorithm with 12-bit resolution. This angular velocity information can be used without further averaging in the ECU. The sensor calculates the velocity for each CORDIC cycle (typ. 128µs). Due to the PSI5 interface limitation the information can only be send every 500µs.

To optimize the signal-to-noise performance the cut off frequency is programmable via Velocity\_filter[2:0] bits in register 0x13. The velocity information is available in all P20CRC-500 and P16CRC-500 modes. Additionally the range of the velocity can be programmed by Velocity\_extended\_range bit in register 0x01.

Figure 34: Angular Velocity Measurement Parameter

| Symbol  | Parameter                                           | Min | Тур   | Max  | Unit    | Comments                                                                                                     |

|---------|-----------------------------------------------------|-----|-------|------|---------|--------------------------------------------------------------------------------------------------------------|

| VRes    | Velocity Signal<br>Resolution                       |     | 12    |      | Bit     |                                                                                                              |

| VRange  | Measurement Range<br>(default)                      |     | 1250  | 1374 | °/s     | Only typical value is guaranteed                                                                             |

| VRangeE | Measurement Range<br>(extended)                     |     | 5000  | 5496 | °/s     | Only typical value is guaranteed                                                                             |

| να      | Measurement Range<br>(compatibility)                |     | 4608  |      | °/s     | Only typical value is guaranteed,<br>valid only when velocity<br>compatibility range is<br>programmed in OTP |

| VSens   | Velocity Sensitivity<br>(default)                   |     | 0.671 |      | °/s/Bit | 12-bit resolution                                                                                            |

| VSensE  | Velocity Sensitivity<br>(extended)                  |     | 2.684 |      | °/s/Bit | 12-bit resolution, only in<br>Extended Mode                                                                  |

| VSensα  | Sensitivity for V $\alpha$<br>(compatibility range) |     | 2.4   |      | °/s/Bit | 12-bit resolution, valid only<br>when velocity compatibility<br>range is programmed in OTP                   |

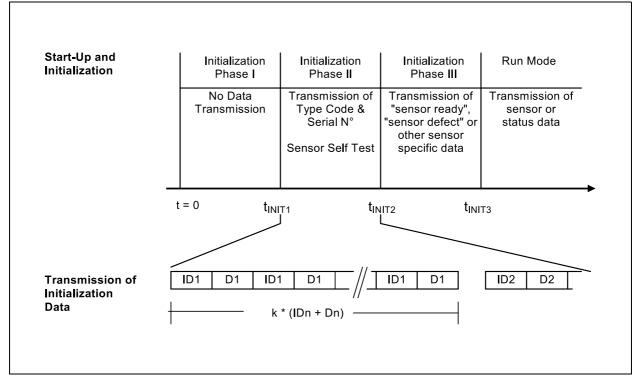

| FCutOff | Cut Off Frequency                                   | 19  | 77    | 260  | Hz      | Programmable with<br>Velocity_filter[2:0]                                                                    |