# AS5247

14-Bit Dual-Die On-Axis Magnetic Rotary Position Sensor with 11-Bit Binary Incremental Pulse Count

### **General Description**

The AS5247 is a high-resolution redundant rotary position sensor for fast absolute angle measurement over a full 360-degree range. This new position sensor is equipped with a revolutionary integrated dynamic angle error compensation (DAEC<sup>™</sup>) with almost 0 latency.

The robust design of the device suppresses the influence of any homogenous external stray magnetic field. A standard 4-wire SPI serial interface allows a host microcontroller to read 14-bit absolute angle position data from the AS5247 and to program non-volatile settings without a dedicated programmer.

Incremental movements are indicated on a set of ABI signals with a maximum resolution of 2048 steps / 512 pulses per revolution. The resolution of the ABI signal is programmable to 1024 steps / 256 pulses per revolution.

Brushless DC (BLDC) motors are controlled through a standard UVW commutation interface with a programmable number of pole pairs from 1 to 7. The absolute angle position is also provided as PWM-encoded output signal.

The AS5247 supports embedded self-diagnostics including magnetic field strength too high, magnetic field strength too low or lost magnet, and other related diagnostic features.

The AS5247 is available as a dual die in a compact MLF-40 7x7 package.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS5247, 14-bit Dual-Die On-Axis Magnetic Rotary Position Sensor with 11-bit Binary Incremental Pulse Count are listed below:

Figure 1: Added Value of Using the AS5247

| Benefits                                       | Features                                                                  |

|------------------------------------------------|---------------------------------------------------------------------------|

| Easy to use – saving costs on DSP              | <ul> <li>DAEC<sup>™</sup> Dynamic angle error compensation</li> </ul>     |

| Good resolution for motor and position control | 14-bit core resolution                                                    |

| Versatile choice of the interface              | <ul> <li>Independent output interfaces: SPI, ABI, UVW,<br/>PWM</li> </ul> |

| Benefits                               | Features                                  |

|----------------------------------------|-------------------------------------------|

| No programmer needed (via SPI command) | Zero position, configuration programmable |

| Supports safety-critical applications  | Self-Diagnostics and redundancy           |

| Lower system costs (no shielding)      | Immune to external stray field            |

## Applications

The AS5247 has been designed to support BLDC motor commutation for the most challenging and safety-critical automotive applications (AEC-Q100 grade 0 automotive qualified) such as electric power steering (EPS), transmission (gearbox, actuator), brake (actuator) and starter & alternator.

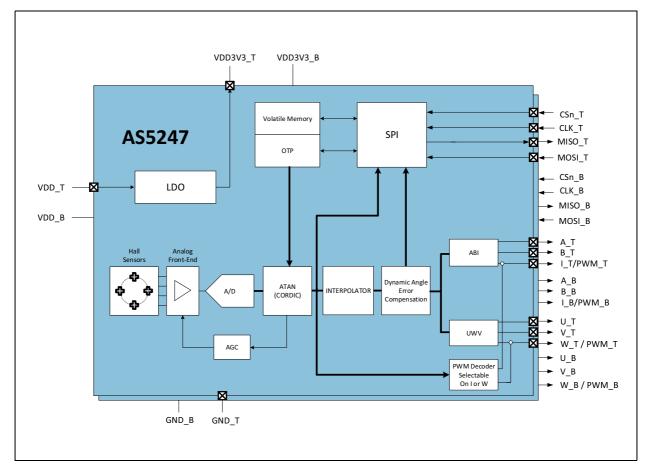

## **Block Diagram**

The functional blocks of this device are shown below:

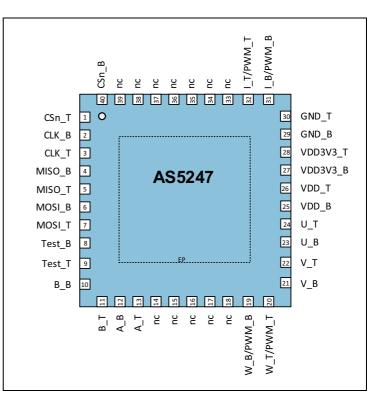

## **Pin Assignment**

Figure 3: **MLF 40 Pin Assignment**

The suffix on the signal name indicates which of the two internal chips is connected to the pin (T = top die, B = bottom die). The package contains two identical chips,

and no pins are shared by both chips.

#### Figure 4: **Pin Description**

| Pin Number | Pin Name | Pin Type       | Pin Description                     |

|------------|----------|----------------|-------------------------------------|

| 1          | CSn_T    | Digital Input  | SPI chip select (active low)        |

| 2          | CLK_B    | Digital Input  | SPI Clock                           |

| 3          | CLK_T    | Digital Input  | SPI Clock                           |

| 4          | MISO_B   | Digital Output | SPI master data input, slave output |

| 5          | MISO_T   | Digital Output | SPI master data input, slave output |

| 6          | MOSI_B   | Digital Input  | SPI master data output, slave input |

| 7          | MOSI_T   | Digital Input  | SPI master data output, slave input |

| 8          | Test_B   |                | Test pin. Connected to ground       |

| 9          | Test_T   |                | Test pin. Connected to ground       |

| 10         | B_B      | Digital Output | Incremental signal B                |

| 11         | B_T      | Digital Output | Incremental signal B                |

| 12         | A_B      | Digital Output | Incremental Signal A                |

om

| Pin Number | Pin Name  | Pin Type       | Pin Description                                                                           |

|------------|-----------|----------------|-------------------------------------------------------------------------------------------|

| 13         | A_T       | Digital Output | Incremental Signal A                                                                      |

| 14         | nc        |                | Not connected                                                                             |

| 15         | nc        |                | Not connected                                                                             |

| 16         | nc        |                | Not connected                                                                             |

| 17         | nc        |                | Not connected                                                                             |

| 18         | nc        |                | Not connected                                                                             |

| 19         | W_B/PWM_B | Digital Output | Commutation signal W or PWM encoded output                                                |

| 20         | W_T/PWM_T | Digital Output | Commutation signal W or PWM encoded output                                                |

| 21         | V_B       | Digital Output | Commutation signal V                                                                      |

| 22         | V_T       | Digital Output | Commutation signal V                                                                      |

| 23         | U_B       | Digital Output | Commutation signal U                                                                      |

| 24         | U_T       | Digital Output | Commutation signal U                                                                      |

| 25         | VDD_B     | Power Supply   | 5V power supply voltage for on-chip regulator                                             |

| 26         | VDD_T     | Power Supply   | 5V power supply voltage for on-chip regulator                                             |

| 27         | VDD3V3_B  | Power Supply   | 3.3V on-chip low-dropout (LDO) output.<br>Requires an external decoupling capacitor (1uF) |

| 28         | VDD3V3_T  | Power Supply   | 3.3V on-chip low-dropout (LDO) output.<br>Requires an external decoupling capacitor (1uF) |

| 29         | GND_B     | Power Supply   | Ground                                                                                    |

| 30         | GND_T     | Power Supply   | Ground                                                                                    |

| 31         | I_B/PWM_B | Digital Output | Index signal or PWM encoded output                                                        |

| 32         | I_T/PWM_T | Digital Output | Index signal or PWM encoded output                                                        |

| 33         | n.c       |                |                                                                                           |

| 34         | n.c       |                |                                                                                           |

| Pin Number | Pin Name | Pin Type | Pin Description              |

|------------|----------|----------|------------------------------|

| 35         | n.c      |          |                              |

| 36         | n.c      |          |                              |

| 37         | n.c      |          |                              |

| 38         | n.c      |          |                              |

| 39         | n.c      |          |                              |

| 40         | CSn_B    |          | SPI chip select (active low) |

#### Note(s) and/or Footnote(s):

1. Floating state of a digital input is not allowed.

2. If SPI is not used, a Pull up resistor on CSn is required.

3. If SPI is not used, a Pull down resistor on CLK and MOSI is required.

4. If SPI is not used, the pin MISO can be left open.

5. If ABI, UVW or PWM is not used, the pins can be left open.

## Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Parameters regarding normal operation of the sensor are listed in section Electrical Characteristics.

Figure 5:

Absolute Maximum Ratings

| Parameter                                          | Symbol           | Min  | Max     | Units | Note                                               |

|----------------------------------------------------|------------------|------|---------|-------|----------------------------------------------------|

| DC supply voltage at VDD pin                       | VDD5             | -0.3 | 7.0     | V     |                                                    |

| DC supply voltage at VDD3V3 pin                    | VDD3             | -0.3 | 5.0     | V     |                                                    |

| DC supply voltage at GND pin                       | VSS              | -0.3 | 0.3     | V     |                                                    |

| Input pin voltage                                  | Vin              |      | VDD+0.3 | V     |                                                    |

| Input current (latch-up immunity)                  | lscr             | -100 | 100     | mA    | Norm:<br>AEC-Q100-004                              |

| Electrostatic discharge                            | ESD              |      | ±2      | kV    | Norm:<br>AEC-Q100-002                              |

| Total power dissipation (all supplies and outputs) | Pt               |      | 150     | mW    |                                                    |

| Ambient temperature 5V0                            | Ta5V0            | -40  | 150     | °C    | In the 5.0V power supply mode only                 |

| Ambient temperature 3V3                            | Ta3V3            | -40  | 150     | °C    | In the 3.3V power<br>supply mode if<br>NOISESET=1  |

| Programming temperature                            | TaProg           | 5    | 45      | °C    | Programming @<br>room temperature<br>(25°C ± 20°C) |

| Storage temperature                                | T_strg           | -55  | 150     | °C    |                                                    |

| Package body temperature                           | T_body           |      | 260     | °C    | Norm: IPC/JEDEC<br>J-STD-020                       |

| Relative humidity non-condensing                   | RH <sub>NC</sub> | 5    | 85      | %     |                                                    |

| Moisture sensitivity level                         | MSL              |      | 3       |       | Represents a<br>maximum floor<br>lifetime of 168h  |

## **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

#### Figure 6: Electrical Characteristics

| Symbol     | Parameter                                     | Conditions                                                                       | Min           | Тур | Max              | Unit |

|------------|-----------------------------------------------|----------------------------------------------------------------------------------|---------------|-----|------------------|------|

| VDD        | Positive supply voltage                       | 5.0V operation mode                                                              | 4.5           | 5.0 | 5.5              | V    |

| VDD3V3     | Positive supply voltage                       | 3.3V operation mode;<br>only from -40°C to 125°C                                 | 3.0           | 3.3 | 3.6              | V    |

| VDD3V3_150 | Positive supply voltage                       | 3.3V operation mode;<br>only from -40°C to 150°C<br>(Noiseset Bit has to be set) | 3.0           | 3.3 | 3.6              | V    |

| VDD_Burn   | Positive supply voltage                       | Supply voltage required<br>for programming in 3.3V<br>operation                  | 3.3           |     | 3.5              | V    |

| VREG       | Regulated Voltage                             | Voltage at VDD3V3 pin if<br>VDD ≠ VDD3V3                                         | 3.2           | 3.4 | 3.6              | V    |

| IDD        | Supply current                                | Only for one die. Must be<br>multiplied by 2                                     |               |     | 15               | mA   |

| VIH        | High-level input<br>voltage                   |                                                                                  | 0.7 	imes VDD |     |                  | V    |

| VIL        | Low-level input<br>voltage                    |                                                                                  |               |     | $0.3 \times VDD$ | V    |

| VOH        | High-level output<br>voltage                  |                                                                                  | VDD - 0.5     |     |                  |      |

| VOL        | Low-level output<br>voltage                   |                                                                                  |               |     | VSS + 0.4        | V    |

| I_Out      | Current on digital<br>output A, B, I, U, V, W |                                                                                  |               |     | 1                | mA   |

| I_Out_MISO | Current on digital output MISO                |                                                                                  |               |     | 4                | mA   |

| C_L        | Capacitive load on<br>digital output          |                                                                                  |               |     | 50               | pF   |

## **Magnetic Characteristics**

Figure 7:

**Magnetic Specifications**

| Symbol | Parameter                                                       | Conditions                                                                                                                  | Min | Тур | Max | Unit |

|--------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Bz     | Orthogonal magnetic<br>field strength, normal<br>operating mode | Required orthogonal component of<br>the magnetic field strength measured<br>at the die's surface along a circle of<br>1.1mm | 35  |     | 70  | mT   |

#### Note(s) and/or Footnote(s):

1. It is possible to operate the AS5247 below 35mT with reduced noise performance.

## **System Characteristics**

Figure 8: System Specifications

| Symbol                    | Parameter                                                                         | Conditions                                                                                           | Min | Тур | Мах   | Units  |

|---------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|-----|-------|--------|

| RES                       | Core resolution                                                                   |                                                                                                      |     | 14  |       | bit    |

| RES_ABI                   | Resolution of the<br>ABI interface                                                | Programmable with<br>register setting<br>(ABIRES)                                                    | 10  |     | 11    | bit    |

| INL <sub>OPT</sub> @ 25°C | Non-linearity,<br>optimum placement<br>of the magnet                              |                                                                                                      |     |     | ±0.9  | degree |

| INL <sub>DIS+TEMP</sub>   | Non-linearity @<br>displacement of<br>magnet and<br>temperature -40°C<br>to 150°C | Assuming N35H<br>Magnet<br>(D=8mm, H=3mm)<br>500um displacement<br>in x and y<br>z-distance @ 2000um |     |     | ±1.4  | degree |

| ONL                       | RMS output noise<br>(1 sigma)                                                     | Orthogonal<br>component for the<br>magnetic field within<br>the specified range<br>(Bz), NOISESET= 0 |     |     | 0.068 | degree |

| ONH                       | RMS output noise<br>(1 sigma) on SPI, ABI<br>and UVW interfaces                   | Orthogonal<br>component for the<br>magnetic field within<br>the specified range<br>(Bz), NOISESET= 1 |     |     | 0.082 | degree |

| Symbol                      | Parameter                                                                      | Conditions                                                                              | Min | Тур | Max   | Units  |

|-----------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-------|--------|

| ON_PWM                      | RMS output noise<br>(1 sigma) on PWM<br>interface                              | Orthogonal<br>component for the<br>magnetic field within<br>the specified range<br>(Bz) |     |     | 0.068 | degree |

| t <sub>delay</sub>          | System propagation delay –core                                                 | Reading angle via SPI                                                                   | 90  |     | 110   | μs     |

| t <sub>delay_</sub><br>DAEC | System propagation<br>delay after dynamic<br>angle error<br>correction.        | At ABI and UVW<br>interfaces                                                            | 1.5 |     | 1.9   | μs     |

| t <sub>sampl</sub>          | Sampling rate                                                                  | Refresh rate at SPI                                                                     | 202 | 222 | 247   | ns     |

| DAE <sub>1700</sub>         | Dynamic angle error                                                            | At 1700 RPM constant speed                                                              |     |     | 0.02  | degree |

| DAE <sub>max</sub>          | Dynamic angle error                                                            | At 14500 RPM constant speed                                                             |     |     | 0.18  | degree |

| DAE <sub>acc</sub>          | Dynamic angle error<br>at constant<br>acceleration<br>(25krad/s <sup>2</sup> ) | 25k radians/s <sup>2</sup><br>constant acceleration                                     |     |     | 0.175 | degree |

| MS                          | Maximum speed                                                                  |                                                                                         |     |     | 14500 | RPM    |

Reference magnet: N35H, 8mm diameter; 3mm thickness

## **Timing Characteristics**

Figure 9: Timing Specifications

| Symbol           | Parameter     | Conditions                                                                                       | Min | Тур | Max | Units |

|------------------|---------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>pon</sub> | Power-on time | Not tested, guaranteed by<br>design. Time between<br>VDD > VDDmin and the<br>first valid outcome |     |     | 10  | ms    |

## **Detailed Description**

The AS5247 is a Hall-effect magnetic sensor using a CMOS lateral technology. The lateral Hall sensors convert the magnetic field component perpendicular to the surface of the chip into a voltage.

The signals from the Hall sensors are amplified and filtered by the analog front-end (AFE) before being converted by the analog-to-digital converter (ADC). The output of the ADC is processed by the hardwired CORDIC (coordinate rotating digital computer) block to compute the angle and magnitude of the magnetic vector. The intensity of the magnetic field (magnitude) is used by the automatic gain control (AGC) to adjust the amplification level for compensation of the temperature and magnetic field variations.

The internal 14-bit resolution is available by readout register via the SPI interface. The resolution on the ABI output can be programmed for 10 or 11bits.

The Dynamic Angle Error Compensation block corrects the calculated angle regarding latency, by using a linear prediction calculation algorithm. At constant rotation speed the latency time is internally compensated by the AS5247, reducing the dynamic angle error at the SPI, ABI and UVW outputs. The AS5247 allows selecting between a UVW / ABI output and a PWM-encoded interface on the W-pin or the I-pin.

At higher speeds, the interpolator fills in missing ABI pulses and generates the UVW signals with no loss of resolution. The non-volatile settings in the AS5247 can be programmed through the SPI interface without any dedicated programmer.

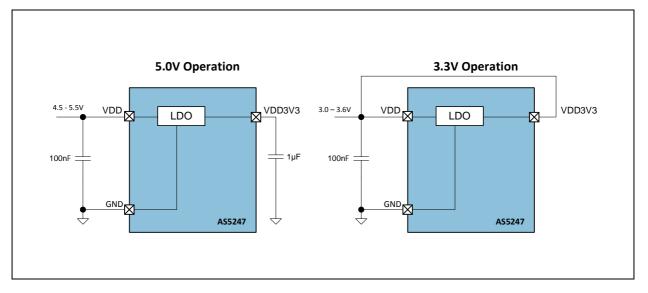

## **Power Management**

The AS5247 can be either powered from a 5.0V supply using the on-chip low-dropout regulator or from a 3.3V voltage supply. The LDO regulator is not intended to power any other loads, and it needs a 1  $\mu$ F capacitor to ground located close to the chip for decoupling as shown in Figure 11.

In 3.3V operation, VDD and VDD3V3 must be tied together. In this configuration, normal noise performance (ONL) is available at reduced maximum temperature (125°C) by clearing NOISESET to 0 (default configuration). When NOISESET is set to 1, the full temperature range is available with reduced noise performance (ONH).

| Figure 10:                   |                 |              |          |          |

|------------------------------|-----------------|--------------|----------|----------|

| <b>Temperature Range and</b> | <b>Output N</b> | loise in 3.3 | SV and 5 | .0V Mode |

| VDD (V) | NOISESET | Temperature Range (°C) | RMS Output Noise (degree) |

|---------|----------|------------------------|---------------------------|

| 5.0     | 0        | -40 ~ 150              | 0.068                     |

| 3.3     | 0        | -40 ~ 125              | 0.068                     |

| 3.3     | 1        | -40 ~ 150              | 0.082                     |

#### Figure 11: 5.0V and 3.3V Power Supply Options

After applying power to the chip, the power-on time (tpon) must elapse before the AS5247 provides the first valid data.

## **Dynamic Angle Error Compensation**

The AS5247 uses 4 integrated Hall sensors on Bottom Die and Top Die, which produce a voltage proportional to the orthogonal component of the magnetic field to the die. These voltage signals are amplified, filtered, and converted into the digital domain to allow the CORDIC digital block to calculate the angle of the magnetic vector. The propagation of these signals through the analog front-end and digital back-end generates a fixed delay between the time of measurement and the availability of the measured angle at the outputs. This latency generates a dynamic angle error, represented by the product of the angular speed  $\omega$  and the system propagation delay (tdelay):

#### (EQ1) $DAE = \omega x \text{ tdelay}$

The dynamic angle compensation block calculates the current magnet rotation speed ( $\omega$ ) and multiplies it with the system propagation delay (tdelay) to determine the correction angle to reduce this error. At constant speed, the residual system propagation delay is tdelay\_DAEC.

The angle represented on the PWM interface is not compensated by the Dynamic Angle Error Compensation algorithm. It is also possible to disable the Dynamic Angle Error Compensation with the DAECDIS setting. Disabling the Dynamic Angle Error Compensation gives a noise benefit of 0.016 degree rms. This setting can be advantageous for low speed ( under 100 RPM) respectively static positioning applications.

#### SPI Interface (slave)

The SPI interface is used by a host microcontroller (master) to read or write the volatile memory, as well as to program the non-volatile OTP registers. The AS5247 SPI only supports slave operation mode. It communicates at clock rates up to 10 MHz.

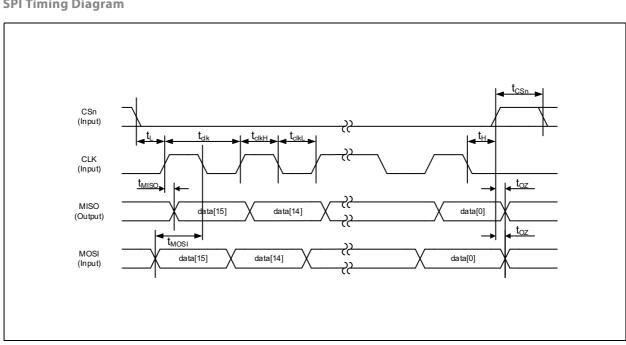

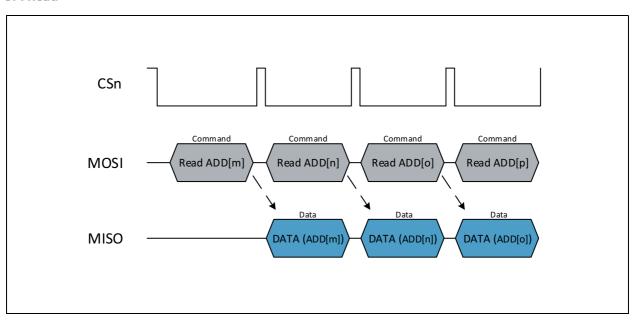

The AS5247 SPI uses mode=1 (CPOL=0, CPHA=1) to exchange data. As shown in Figure 12, a data transfer starts with the falling edge of CSn (CLK is low). The AS5247 samples MOSI data on the falling edge of CLK. SPI commands are executed at the end of the frame (rising edge of CSn). The bit order is MSB first. Data is protected by parity.

#### SPI Timing

The AS5247 SPI timing is shown in Figure 12.

Figure 12: SPI Timing Diagram

#### Figure 13: SPI Timing

| Parameter         | Description                                                  | Min    | Max | Units |

|-------------------|--------------------------------------------------------------|--------|-----|-------|

| tL                | Time between CSn falling edge and CLK rising edge            | 350    |     | ns    |

| t <sub>clk</sub>  | Serial clock period                                          | 100    |     | ns    |

| t <sub>clkL</sub> | Low period of serial clock                                   | 50     |     | ns    |

| t <sub>clkH</sub> | High period of serial clock                                  | 50     |     | ns    |

| t <sub>H</sub>    | Time between last falling edge of CLK and rising edge of CSn | tclk/2 |     | ns    |

| t <sub>CSn</sub>  | High time of CSn between two transmissions                   | 350    |     | ns    |

| t <sub>MOSI</sub> | Data input valid to falling clock edge                       | 20     |     | ns    |

| t <sub>MISO</sub> | CLK edge to data output valid                                |        | 51  | ns    |

| t <sub>OZ</sub>   | Release bus time after CS rising edge.                       |        | 10  | ns    |

#### **SPI Transaction**

An SPI transaction consists of a 16-bit command frame followed by a 16-bit data frame. Figure 14 shows the structure of the command frame.

| Bit  | Name | Description                                                        |

|------|------|--------------------------------------------------------------------|

| 15   | PARC | Parity bit (even) calculated on the lower 15 bits of command frame |

| 14   | R/W  | 0: Write<br>1: Read                                                |

| 13:0 | ADDR | Address to read or write                                           |

SPI Command Frame

Figure 14:

To increase the reliability of communication over the SPI, an even parity bit (PARC) must be generated and sent. A wrong setting of the parity bit causes an parity bit error which is shown the PARERR bit in the error flag register. The parity bit is calculated from the lower 15 bits of the command frame. The 16-bit command consists of a register address and read/write bit which indicates if the transaction is a read or write and the parity bit. Figure 15 shows the read data frame.

#### Figure 15: SPI Read Data Frame

| Bit  | Name | Description                                                              |

|------|------|--------------------------------------------------------------------------|

| 15   | PARD | Parity bit (even) calculated on the lower 15 bits of the read data frame |

| 14   | EF   | 0: No command frame error command occurred<br>1: Error occurred          |

| 13:0 | DATA | Data                                                                     |

The data is sent on the MISO pin. The parity bit PARD is calculated by the AS5247 of the lower 15 bits of data frame. If an error is detected in the previous SPI command frame, the EF bit is set high. The SPI read is sampled on the rising edge of CSn and the data is transmitted on MISO with the next read command, as shown in Figure 16.

#### Figure 16: SPI Read

#### Figure 17: SPI Write Data Frame

| Bit  | Name | Description       |

|------|------|-------------------|

| 15   | PARC | Parity bit (even) |

| 14   | 0    | Always low        |

| 13:0 | DATA | Data              |

The parity bit PARC is calculated from the lower 15 bits of data frame.

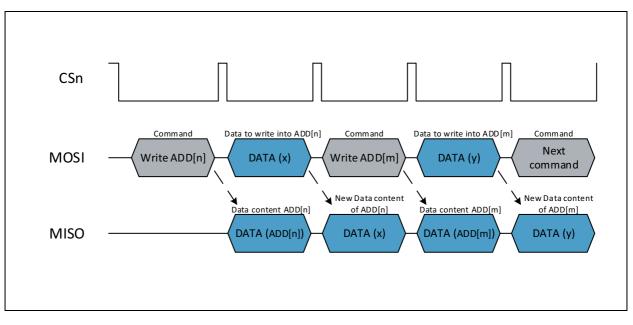

In a SPI write transaction, the write command frame is followed by a write data frame at MOSI. The write data frame consists of the new content of register which address is defined in the command frame.

During the new content is transmitted on MOSI by the write data frame, the old content is send on MISO. At the next command on MOSI the actual content of the register is transmitted on MISO, as shown in Figure 18.

## **Volatile Registers**

The volatile registers are shown in Figure 19. Each register has a 14-bit address.

| Figure 1 | 9:       |       |

|----------|----------|-------|

| Volatile | Register | Table |

| Address | Name     | Default | Description                                             |

|---------|----------|---------|---------------------------------------------------------|

| 0x0000  | NOP      | 0x0000  | No operation                                            |

| 0x0001  | ERRFL    | 0x0000  | Error register                                          |

| 0x0003  | PROG     | 0x0000  | Programming register                                    |

| 0x3FFC  | DIAAGC   | 0x0180  | Diagnostic and AGC                                      |

| 0x3FFD  | MAG      | 0x0000  | CORDIC magnitude                                        |

| 0x3FFE  | ANGLEUNC | 0x0000  | Measured angle without dynamic angle error compensation |

| 0x3FFF  | ANGLECOM | 0x0000  | Measured angle with dynamic angle error compensation    |

Reading the NOP register is equivalent to a nop (no operation) instruction for the AS5247.

Figure 20: ERRFL (0x0001)

| Name    | Read/Write | Bit Position | Description                                                                       |

|---------|------------|--------------|-----------------------------------------------------------------------------------|

| PARERR  | R          | 2            | Parity error                                                                      |

| INVCOMM | R          | 1            | Invalid command error: set to 1 by reading or writing an invalid register address |

| FRERR   | R          | 0            | Framing error: is set to 1 when a non-compliant SPI frame is detected             |

Reading the ERRFL register automatically clears its contents (ERRFL=0x0000).

#### Figure 21: PROG (0x0003)

| Name    | Read/Write | Bit Position | Description                                                                                 |

|---------|------------|--------------|---------------------------------------------------------------------------------------------|

| PROGVER | R/W        | 6            | Program verify: must be set to 1 for<br>verifying the correctness of the OTP<br>programming |

| PROGOTP | R/W        | 3            | Start OTP programming cycle                                                                 |

| OTPREF  | R/W        | 2            | Refreshes the non-volatile memory content with the OTP programmed content                   |

| PROGEN  | R/W        | 0            | Program OTP enable: enables programming the entire OTP memory                               |

The PROG register is used for programming the OTP memory. (See programming the zero position.)

Figure 22: DIAAGC (0x3FFC)

| Name | Read/Write | Bit Position | Description                                                                                                            |

|------|------------|--------------|------------------------------------------------------------------------------------------------------------------------|

| MAGL | R          | 11           | Diagnostic: Magnetic field strength too low;<br>AGC=0xFF                                                               |

| MAGH | R          | 10           | Diagnostic: Magnetic field strength too<br>high; AGC=0x00                                                              |

| COF  | R          | 9            | Diagnostic: CORDIC overflow                                                                                            |

| LF   | R          | 8            | Diagnostics: Loops Finished<br>LF=0:internal offset loops not ready<br>regulated<br>LF=1:internal offset loop finished |

| AGC  | R          | 7:0          | Automatic gain control value                                                                                           |

Figure 23: MAG (0x3FFD)

| Name | Read/Write | Bit Position | Description                  |

|------|------------|--------------|------------------------------|

| MAG  | R          | 13:0         | CORDIC magnitude information |

#### Figure 24: ANGLEUNC (0x3FFE)

| Name     | Read/Write | Bit Position | Description                                                |

|----------|------------|--------------|------------------------------------------------------------|

| ANGLEUNC | R          | 13:0         | Angle information without dynamic angle error compensation |

Figure 25: ANGLECOM (0x3FFF)

| Name     | Read/Write | Bit Position | Description                                              |

|----------|------------|--------------|----------------------------------------------------------|

| ANGLECOM | R          | 13:0         | Angle information with dynamic angle error compensation. |

## Non-Volatile Registers (OTP)

The OTP (One-Time Programmable) memory is used to store the absolute zero position of the sensor and the customer settings permanently in the sensor IC. SPI write/read access is possible several times for all Non-Volatile Registers (soft write). Soft written register content will be lost after a hardware reset. The programming itself can be done just once. Therefore the content of the Non-Volatile Registers is stored permanently in the sensor. The register content is still present after a hardware reset and cannot be overwritten. For a correct function of the sensor the OTP programming is not required. If no configuration or programming is done, the Non-Volatile Registers are in the default state 0x0000.

Figure 26: Non-Volatile Register Table

| Address | Name      | Default | Description                      |

|---------|-----------|---------|----------------------------------|

| 0x0016  | ZPOSM     | 0x0000  | Zero position MSB                |

| 0x0017  | ZPOSL     | 0x0000  | Zero position LSB/MAG diagnostic |

| 0x0018  | SETTINGS1 | 0x0000  | Custom setting register1         |

| 0x0019  | SETTINGS2 | 0x0000  | Custom setting register 2        |

| 0x001A  | RED       | 0x0000  | Redundancy register              |

Figure 27: ZPOSM (0x0016)

| Name  | Read/Write/Program | Bit Position | Description                                  |

|-------|--------------------|--------------|----------------------------------------------|

| ZPOSM | R/W/P              | 7:0          | 8 most significant bits of the zero position |

### Figure 28: ZPOSL (0x0017)

| Name            | Read/Write/Program | Bit Position | Description                                                                                          |

|-----------------|--------------------|--------------|------------------------------------------------------------------------------------------------------|

| ZPOSL           | R/W/P              | 5:0          | 6 least significant bits of the zero position                                                        |

| comp_l_error_en | R/W/P              | 6            | This bit enables the contribution of<br>MAGH (Magnetic field strength too high)<br>to the error flag |

| comp_h_error_en | R/W/P              | 7            | This bit enables the contribution of MAGL<br>(Magnetic field strength too low) to the<br>error flag  |

#### Figure 29: SETTINGS1 (0x0018)

| Name       | Read/Write/Program | Bit Position | Description                                                                                                                            |

|------------|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------|

| IWIDTH     | R/W/P              | 0            | Width of the index pulse I<br>(0 = 3LSB, 1 = 1LSB)                                                                                     |

| NOISESET   | R/W/P              | 1            | Noise setting                                                                                                                          |

| DIR        | R/W/P              | 2            | Rotation direction                                                                                                                     |

| UVW_ABI    | R/W/P              | 3            | Defines the PWM Output<br>(0 = ABI is operating, W is used as PWM<br>1 = UVW is operating, I is used as PWM)                           |

| DAECDIS    | R/W/P              | 4            | Disable Dynamic Angle Error<br>Compensation (0 = DAE compensation<br>on, 1 = DAE compensation off)                                     |

| Dataselect | R/W/P              | 6            | This bit defines which data can be read<br>form<br>address 16383dec (3FFFhex).<br>$0 \rightarrow ANGLECOM$<br>$1 \rightarrow ANGLEUNC$ |

| PWMon      | R/W/P              | 7            | enables PWM (setting of UVW_ABI Bit necessary)                                                                                         |

Figure 30: SETTINGS2 (0x0019)

| Name   | Read/Write/Program | Bit Position | Description                                                                                                                                                                |

|--------|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UVWPP  | R/W/P              | 2:0          | UVW number of pole pairs<br>(000=1,001=2,010=3,011=4,100=5,<br>101=6,110=7,111=7)                                                                                          |

| HYS    | R/W/P              | 4:3          | Hysteresis<br>for 11 Bit ABI Resolution: (00=3LSB, 01=<br>2LSB,10=1LSB,11=no hysteresis)<br>for 10 Bit ABI Resolution: (00=2LSB, 01=<br>1LSB,10=no Hysteresis LSB,11=3LSB) |

| ABIRES | R/W/P              | 5            | Resolution of ABI (0=11 bits, 1=10 bits)                                                                                                                                   |

The hysteresis is in terms of the chosen resolution (11 bits vs. 10bits) The ABIRES resolution does not affect the UVW signals.

Figure 31: RED(0x001A)

| Name | Read/Write/Program | Bit Position | Description                                                                                                                                                                                                                                      |

|------|--------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RED  | R/W/P              | 4:0          | Redundancy bits. This field enables<br>with force to high one bit of the<br>Non-Volatile register map after a<br>non-successful burning. For more<br>details please refer to the application<br>note "AS5147_ApplicationNote_<br>RedundancyBits" |

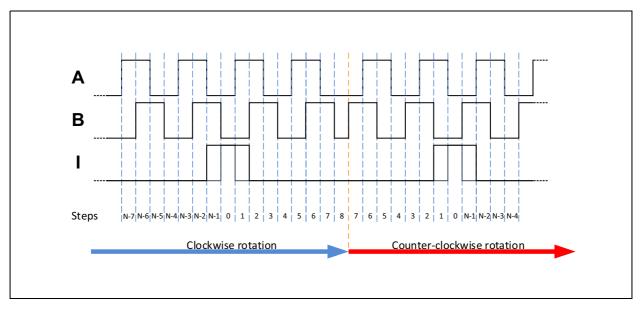

## **ABI Incremental Interface**

The AS5247 can send the angle position to the host microcontroller through an incremental interface. This interface is available simultaneously with the other interfaces. By default, the incremental interface is set to work at the highest resolution (11 bits), which corresponds to 2048 steps per revolution or 512 pulses per revolution (ppr). This resolution can be cut in half using the OTP bit ABIRES, which results in 1024 steps per revolution or 256 pulses per revolution.

The phase shift between the A and B signals indicates the rotation direction: clockwise (A leads, B follows) or counterclockwise (B leads, A follows). The DIR bit can be used to invert the sense of the rotation direction. During the power-on time, all three ABI signals are high.

The IWIDTH setting programs the width of the index pulse from 3 LSB (default) to 1 LSB.

#### Figure 32: ABI Signals at 11 Bit Resolution

#### Note(s) and/or Footnote(s):

1. N = 2048 for 11-bit resolution, and N = 1024 for 10-bit resolution.

2. Index pulse width 3 LSB and index pulse width 1 LSB (dashed line) are shown in the diagram.

The Figure 32 shows the ABI signal flow if the magnet rotates in clockwise direction and counter-clockwise direction (DIR=0). In case of clockwise rotation when the magnet is rotating to the right hand side, the angle value is increasing. Clockwise rotation direction is defined as shown in Figure 44.

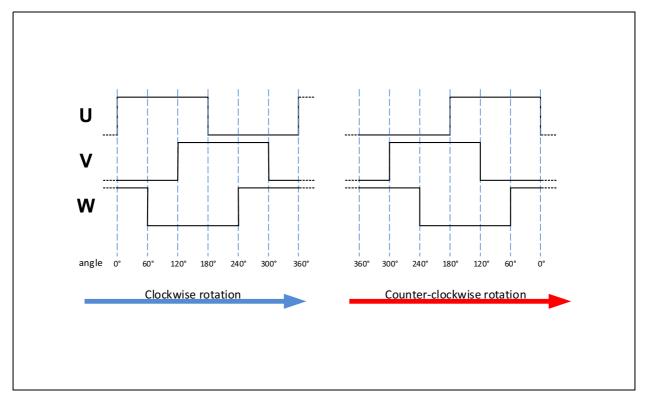

#### **UVW** Commutation Interface

The AS5247 can emulate the UVW signals generated by the three discrete Hall switches commonly used in BLDC motors.

The UVWPP field in the SETTINGS register selects the number of pole pairs of the motor (from 1 to 7 pole pairs). The UVW signals are generated with 14-bit resolution.

During the power-on time, the UVW signals are low.

Figure 33: UVW Signals

The Figure 33 shows the UVW signal flow if the magnet rotates in clockwise direction and counter-clockwise direction (DIR=0). In case of clockwise rotation when the magnet is rotating to the right hand side, the angle value is increasing. Clockwise rotation direction is defined as shown in Figure 44. With the bit DIR, it is possible to invert the rotation direction.

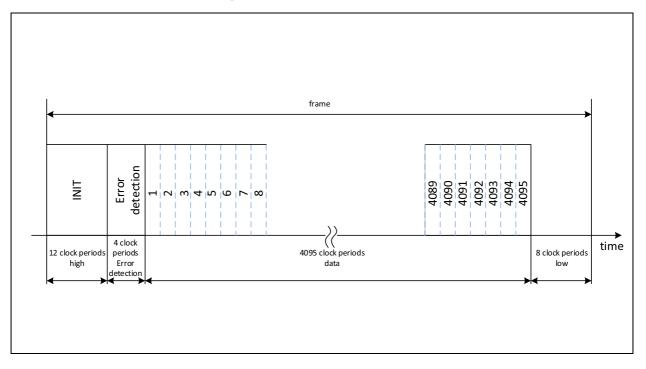

#### PWM

The PWM can be enabled with the bit setting PWMon. The PWM encoded signal is displayed on the pin W or the pin I. The bit setting UVW\_ABI defines which output is used as PWM. The PWM output consists of a frame of 4119 PWM clock periods, as

shown in Figure 34. The PWM frame has the following sections:

- 12 PWM Clocks for INIT

- 4 PWM Clocks for Error detection

- 4095 PWM clock periods of data

- 8 PWM clock periods low

The angle is represented in the data part of the frame with a 12-bit resolution. One PWM clock period represents 0.088 degree and has a typical duration of 444 ns.

If the embedded diagnostic of the AS5247 detects any error, the PWM interface displays only 12 clock periods high (0.3% duty-cycle). Respectively the 4 clocks for error detection are forced to low.

Figure 34: Pulse Width Modulation Encoded Signal

## Hysteresis

The width of the hysteresis can be programmed. Two HYS bits are available in the SETTINGS2 register for configuration. Figure 35 shows the available settings based on the selected ABI resolution (ABIRES).

Figure 35: Hysteresis Settings

| HYS | HYSTERESIS with 11 Bit ABI<br>Resolution | HYSTERESIS with 10 Bit ABI<br>Resolution |

|-----|------------------------------------------|------------------------------------------|

| 00  | 3                                        | 2                                        |

| 01  | 2                                        | 1                                        |

| 10  | 1                                        | 0                                        |

| 11  | 0                                        | 3                                        |

# Automatic Gain Control (AGC) and CORDIC Magnitude

The AS5247 uses AGC to compensate for variations in the magnetic field strength due to changes of temperature, air gap between the chip and the magnet, and demagnetization of the magnet. The automatic gain control value can be read in the AGC field of the DIAAGC register. Within the specified input magnetic field strength (Bz), the Automatic Gain Control works in a closed loop and keeps the CORDIC magnitude value (MAG) constant. Below the minimum input magnetic field strength, the CORDIC magnitude decreases and the MAGL bit is set.

#### **Diagnostic Features**

The AS5247 supports embedded self-diagnostics.

MAGH: Magnetic field strength too high, set if AGC = 0x00. This indicates the non-linearity error may be increased.

MAGL: Magnetic field strength too low, set high if AGC = 0xFF. This indicates the output noise of the measured angle may be increased.

COF: CORDIC overflow. This indicates the measured angle is not reliable.

LF: Offset compensation completed. At power-up, an internal offset compensation procedure is started, and this bit is set when the procedure is completed.

Full Redundancy for application with high safety requirements

#### LF Error / COF Error

In case of an LF or COF error, all outputs are changing into a safe state:

SPI Output: Information in the DIAAGC (0x3FFC) register. The angle information is still valid.

Error State PWM Output:

The PWM Clock Periods for Error Detection are forced to low. In addition the angle value is not valid (all 4096 Clock periods, showing the angle value, are forced to low). The PWM Error detection is shown at PWM Clock Period 13, 14, 15 and 16, see Figure 34.

Error State ABI Outputs:

ABI output is forced to high (111).

Error State UVW Outputs:

UVW output is forced to low (000).

#### MAGH Error / MAGL Error

Default diagnostic setting for MAGH error /MAGL error:

In case of a MAGH error or MAGL error, there is no safe state on the PWM, ABI or UVW outputs if comp\_h\_error\_en is 0 and comp\_l\_error\_en is 0.

The error flags can be read out with the DIAAGC (0x3FFC) register.

Enhanced diagnosis setting for MAGH error / MAGL error:

In case of a MAGH error or MAGL error, the PWM, ABI or UVW outputs are going into a safe state if comp\_h\_error\_en is 1 and comp\_l\_error\_en is 1.The device is operating with the performance as explained in chapter Diagnostic Features.

SPI Output: Information in the DIAAGC (0x3FFC) register. The angle information is still valid, if the MAGH or MAGL error flag is on.

Error State PWM Output:

The PWM Clock Periods for Error Detection are forced to low. In addition the angle value is not valid (all 4096 Clock periods, showing the angle value, are forced to low). The PWM Error detection is shown at PWM Clock Period 13, 14, 15 and 16, see Figure 34.

Error State ABI Outputs:

ABI output is forced to high (111).

Error State UVW Outputs:

UVW output is forced to low (000).

**Important:** When comp\_h\_error\_en and/or comp\_l\_error\_en is enabled, a marginal magnetic field input can cause toggling of MAGH or MAGL which will lead to toggling of the ABI/UVW outputs between operational mode and failure mode.

## **Application Information**

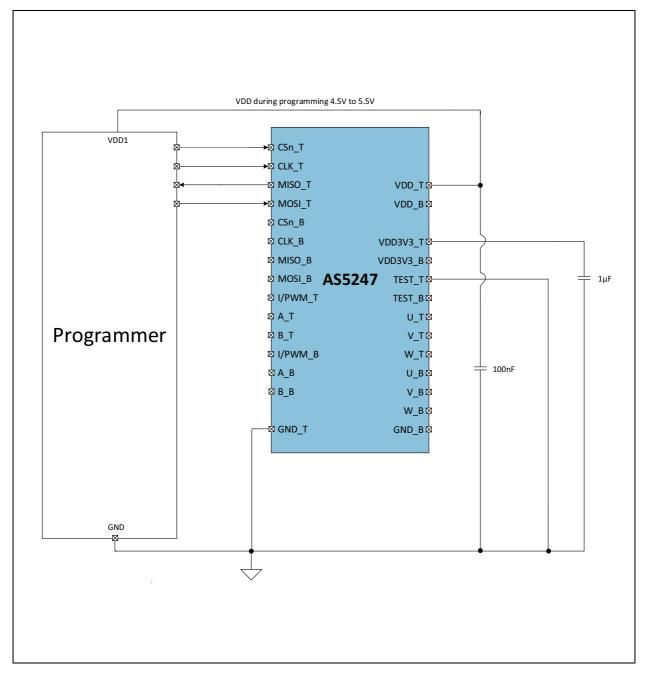

### Burn and Verification of the OTP Memory

Figure 36:

Minimum Programming Diagram for the AS5247 in 5V Operation

#### Note(s) and/or Footnote(s):

1. In terms of EMC and for remote application, additional circuits are necessary.

2. Diagram shows only the connection to Top Die of AS5247. For programming of Bottom Die the following pins have to be connected instead of the connection in the drawing:

CSn\_B, CLK\_B, MISO\_B, MOSI\_B,GND\_B,VDD\_B, VDD3V3\_B,TEST\_B

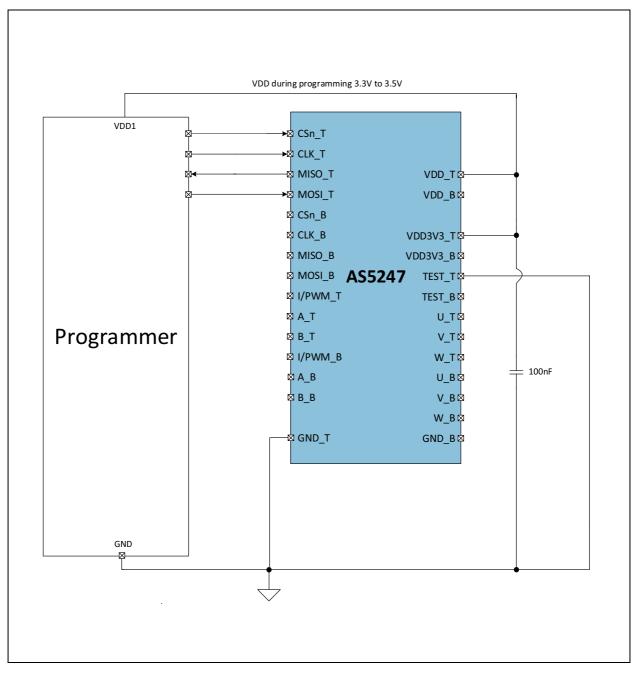

#### Figure 37: Minimum Programming Diagram for the AS5247 in 3.3V Operation

#### Note(s) and/or Footnote(s):

1. In terms of EMC and for remote application, additional circuits are necessary.

2. Diagram shows only the connection to Top Die of AS5247. For programming of Bottom Die the following pins have to be connected instead of the connection in the drawing:

CSn\_B, CLK\_B, MISO\_B, MOSI\_B, GND\_B, VDD\_B, VDD3V3\_B, TEST\_B

m

Figure 38: OTP Programming Parameters

| Symbol             | Parameter                  | Conditions                                             | Min | Тур | Max | Units |

|--------------------|----------------------------|--------------------------------------------------------|-----|-----|-----|-------|

| T <sub>aProg</sub> | Programming<br>temperature | Programming @ Room<br>Temperature (25°C ± 20°C)        | 5   |     | 45  | ۰C    |

| V <sub>DD</sub>    | Positive supply voltage    | 5V operation mode. Supply voltage during programming   | 4.5 | 5   | 5.5 | V     |

| V <sub>DD</sub>    | Positive supply voltage    | 3.3V operation mode. Supply voltage during programming | 3.3 |     | 3.5 | V     |

| I <sub>Prog</sub>  | Current for programming    | Max current during OTP burn procedure                  |     |     | 100 | mA    |

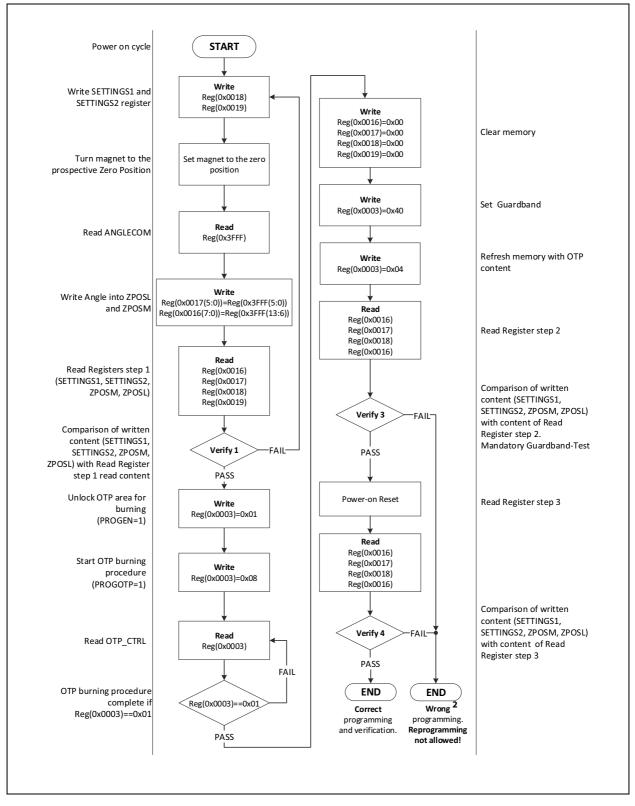

Step-by-step procedure to permanently program the non-volatile memory (OTP):

The programming can either be performed in 5V operation using the internal LDO (1 $\mu$ F on regulator output pin), or in 3V Operation but using a supply voltage between 3.3V and 3.5V.

- 1. Power on cycle

- 2. Write the SETTINGS1 and SETTINGS2 registers with the Custom settings for this application

- 3. Place the magnet at the desired zero position

- 4. Read out the measured angle from the ANGLECOM register

- 5. Write ANGLECOM [5:0] into the ZPOSL register and ANGLECOM [13:6] into the ZPOSM register

- 6. Read Reg(0x0016) to Reg(0x0019)  $\rightarrow$  Read register step1

- 7. Comparison of written content (settings and angle) with content of read register step1

- 8. If point 7 is correct, enable OTP read / write by setting PROGEN = 1 in the PROG register

- 9. Start the OTP burn procedure by setting PROGOTP = 1 in the PROG register

- 10. Read the PROG register until it reads 0x0001 (Programming procedure complete)

- 11. Clear the memory content by writing 0x00 in the whole non-volatile memory

- 12. Set the PROGVER = 1 to set the Guard band for the guard band test.<sup>1</sup>

- 13. Refresh the non-volatile memory content with the OTP content by setting OTPREF = 1

- 14. Read Reg(0x0016) to Reg(0x0019)  $\rightarrow$  Read register step2

- 15. Comparison of written content (settings and angle) with content of read register step2. If a deviation in the comparison occurs, the guard band test was not successful<sup>2</sup>. Reprogramming is not allowed! Mandatory: guard band test

- 16. New power on cycle.

- 17. Read Reg(0x0016) to Reg(0x0019)  $\rightarrow$  Read register step3

- 18. Comparison of written content (settings and angle) with content of read register step3. If a deviation in the comparison occurs, the power on test was not successful<sup>2</sup>. Reprogramming is not allowed!

- 19. If **point 18** is correct, the programming was successful.

- 20. Repeat **point 1** to **point 19** on the second die.

<sup>1.</sup> Guard band test:

<sup>-</sup> Restricted to temperature range: 25 °C  $\pm$  20 °C

<sup>-</sup> Right after the programming procedure (max. 1 hour with same

<sup>-</sup> Conditions 25°C ± 20 °C)

<sup>-</sup> Same VDD voltage

The guard band test is only for the verification of the burned OTP fuses during the programming sequence.

A use of the guard band in other cases is not allowed.

<sup>2.</sup> Typical programming yield of 99,9% is guaranteed.

#### Figure 39:

**OTP Memory Burn and Verification Flowchart**

#### Note(s) and/or Footnote(s):

- 1. This procedure has to be done twice, for the Top Die and for the Bottom Die.

- 2. Device with wrong programming must not be used. Scrapping mandatory.

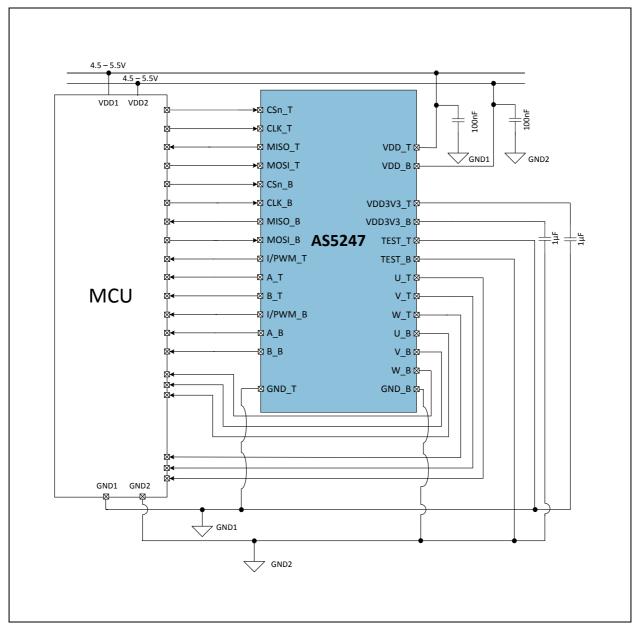

#### Figure 40: Minimum Circuit Diagram for the AS5247

#### Note(s) and/or Footnote(s):

1. This application block diagram is showing the AS5247 using in a full redundant application. Interms of EMC and for remote application, additional protection circuit is necessary.

om

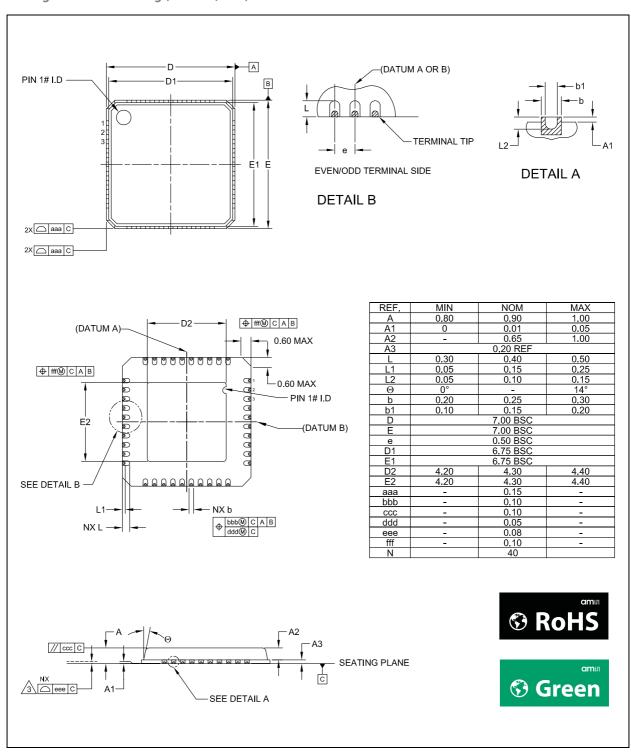

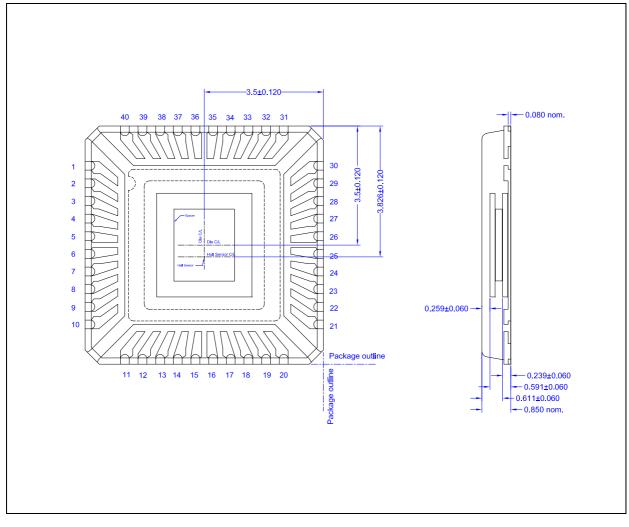

## Package Drawings & Markings

The axis of the magnet must be aligned over the center of the package.

Figure 41:

Package Outline Drawing (MLF-40, 7x7)

#### Note(s) and/or Footnote(s):

- 1. Dimensions & tolerancing conform to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters (angles in degrees).

- 3. Bilateral coplanarity zone applies to the exposed pad as well as the terminal.

- 4. Radius on terminal is optional.

- 5. N is the total number of terminals.

Figure 42: Package Marking

#### Figure 43: Packaging Code

| YY                                        | ww                 | V                | ZZ                                 | @                 |

|-------------------------------------------|--------------------|------------------|------------------------------------|-------------------|

| Last two digits of the manufacturing year | Manufacturing week | Plant identifier | Free choice /<br>traceability code | Sublot identifier |

## **Mechanical Data**

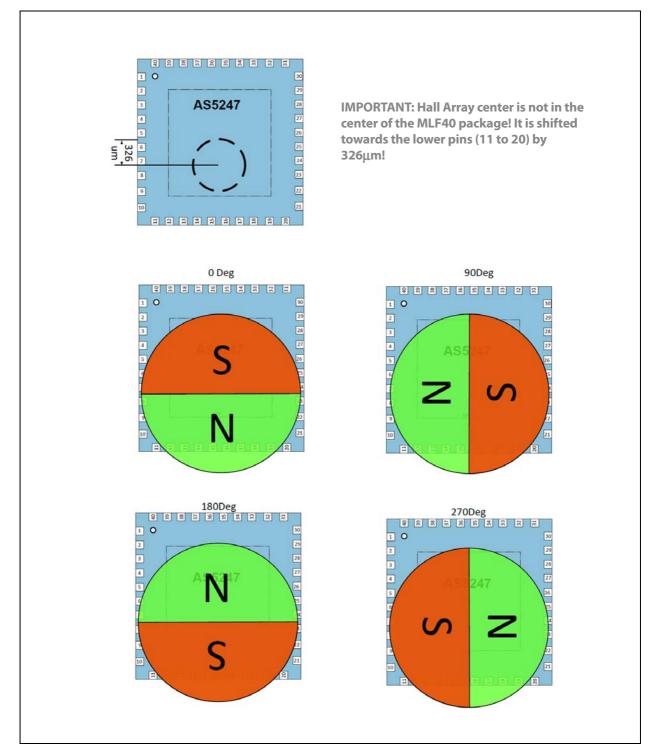

Figure 44: Angle Detection by Default (no zero position programmed)

#### Figure 45: Die Placement and Hall Array Position

#### Note(s) and/or Footnote(s):

- 1. All dimensions in mm.

- 2. Die thickness 150 $\mu$ m nom.

- 3. Adhesive thickness 12 $\mu$ m nom.

- 4. Spacer thickness: 178 $\mu$ m typ.

## **Ordering & Contact Information**

Figure 46: Ordering Information

| Ordering<br>Code | Package | Marking | Delivery Form               | Delivery<br>Quantity |

|------------------|---------|---------|-----------------------------|----------------------|

| AS5247-HMFM      | MLF-40  | AS5247  | 7" Tape & Reel in dry pack  | 1000 pcs/reel        |

| AS5247-HMFT      | MLF-40  | AS5247  | 13" Tape & Reel in dry pack | 4000 pcs/reel        |

Buy our products or get free samples online at: www.ams.com/ICdirect

Technical Support is available at: www.ams.com/Technical-Support

Provide feedback about this document at: www.ams.com/Document-Feedback

For further information and requests, e-mail us at: ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/contact

#### Headquarters

ams AG Tobelbader Strasse 30 8141 Premstaetten Austria, Europe

Tel: +43 (0) 3136 500 0

Website: www.ams.com

## RoHS Compliant & ams Green Statement

**RoHS:** The term RoHS compliant means that ams AG products fully comply with current RoHS directives. Our semiconductor products do not contain any chemicals for all 6 substance categories, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, RoHS compliant products are suitable for use in specified lead-free processes.

**ams Green (RoHS compliant and no Sb/Br):** ams Green defines that in addition to RoHS compliance, our products are free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material).

**Important Information:** The information provided in this statement represents ams AG knowledge and belief as of the date that it is provided. ams AG bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. ams AG has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. ams AG and ams AG suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

## Copyrights & Disclaimer

Copyright ams AG, Tobelbader Strasse 30, 8141 Premstaetten, Austria-Europe. Trademarks Registered. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing in its General Terms of Trade. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. This product is provided by ams AG "AS IS" and any express or implied warranties, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose are disclaimed.

ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

## **Document Status**

| Document Status          | Product Status  | Definition                                                                                                                                                                                                                                                                     |

|--------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview          | Pre-Development | Information in this datasheet is based on product ideas in<br>the planning phase of development. All specifications are<br>design goals without any warranty and are subject to<br>change without notice                                                                       |

| Preliminary Datasheet    | Pre-Production  | Information in this datasheet is based on products in the<br>design, validation or qualification phase of development.<br>The performance and parameters shown in this document<br>are preliminary without any warranty and are subject to<br>change without notice            |

| Datasheet                | Production      | Information in this datasheet is based on products in<br>ramp-up to full production or full production which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade                                |

| Datasheet (discontinued) | Discontinued    | Information in this datasheet is based on products which<br>conform to specifications in accordance with the terms of<br>ams AG standard warranty as given in the General Terms of<br>Trade, but these products have been superseded and<br>should not be used for new designs |

## **Revision Information**

| Changes from 1-09 (2015-Sep-24) to current revision 1-10 (2016-Dec-05) | Page |

|------------------------------------------------------------------------|------|

| Updated Figure 2                                                       | 2    |

| Updated text above Figure 5                                            | 6    |

| Updated text under Detailed Description                                | 10   |

| Updated Figure 14 and text under it                                    | 13   |

| Updated Figure 15 and text under it                                    | 14   |

| Updated Figure 16                                                      | 14   |

| Updated Figure 17 and text under it                                    | 15   |

| Updated Figure 18                                                      | 15   |

| Updated Figure 23                                                      | 17   |

| Updated Figure 24                                                      | 18   |

| Updated Figure 25                                                      | 18   |

| Updated Figure 28                                                      | 19   |

| Updated Figure 29                                                      | 19   |

| Updated text under ABI Incremental Interface                           | 20   |

| Updated Figure 31                                                      | 20   |

| Updated Figure 32 and text under it                                    | 21   |

| Updated Figure 33 and text under it                                    | 22   |

| Updated Figure 34                                                      | 23   |

| Updated text under Hysteresis                                          | 24   |

| Updated title of OCF Error/COF Error section to LF Error/COF Error     | 25   |

| Updated text under MAGH Error / MAGL Error                             | 25   |

| Updated text under Figure 38                                           | 28   |

| Updated Figure 39 and added notes under it                             | 30   |

#### Note(s) and/or Footnote(s):

1. Page and figure numbers for the previous version may differ from page and figure numbers in the current revision.

2. Correction of typographical errors is not explicitly mentioned.