# AS8510 Data Acquisition Device for Battery Sensors

# 1 General Description

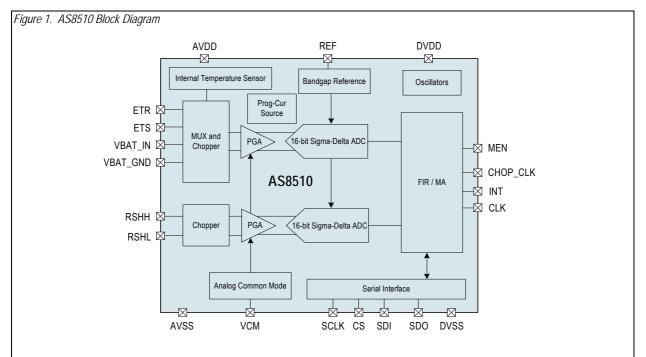

The AS8510 is a virtually offset free, low noise, two channel measurement device. It is tailored to accurately measure battery current from mA range up to kA range in conjunction with a 100  $\mu\Omega$  shunt resistor in series with the battery rail. Through the second measurement channel it enables capture of, either battery voltage synchronous with the current measurement, or, measure the analog output of an internal or external temperature sensor. Both channels are matched and can either measure small signals up to ±160 mV versus ground, through programmable gain amplifier or larger signals in the 0 to 1V range without the amplifier.

After analog to digital conversion and digital filtering, the resulting 16-bit digital words are accessible through 4-wire standard serial interface. The device includes a number of additional features explained in the next section.

# 2 Key Features

- 3.3V supply voltage

- Two High resolution 16 bit  $\Sigma$ – $\Delta$  A/D converters

- Programmable sampling to enable data throughputs from less than 1Hz to 8kHz

- Zero Offset for both channels

- Independent control of data rate on both channels

- Precision, low noise, programmable gain amplifiers for both channels with gains 5, 25, 40, 100 to support wide dynamic ranges.

- Option for multiplexing either one differential input, or two single ended inputs or the internal temperature sensor on one channel

- Programmable current source for external temperature sensor connectable to any of the inputs

- High precision and high stability 1.2V reference voltage source

- Digital signal processing with filter options for both channels

- Four operating modes providing

- Continuous data acquisition (or)

- Periodic single-shot acquisition, (or)

- Continuous acquisition on threshold crossing of programmed current levels (or)

- A combination of the above

- On chip high-precision 4MHz RC oscillator or option for external clock

- -40°C to +125°C ambient operation

- AEC Q100 automotive qualified

- Internal chip ID for full traceability

- SSOP-20 pin package

# 3 Applications

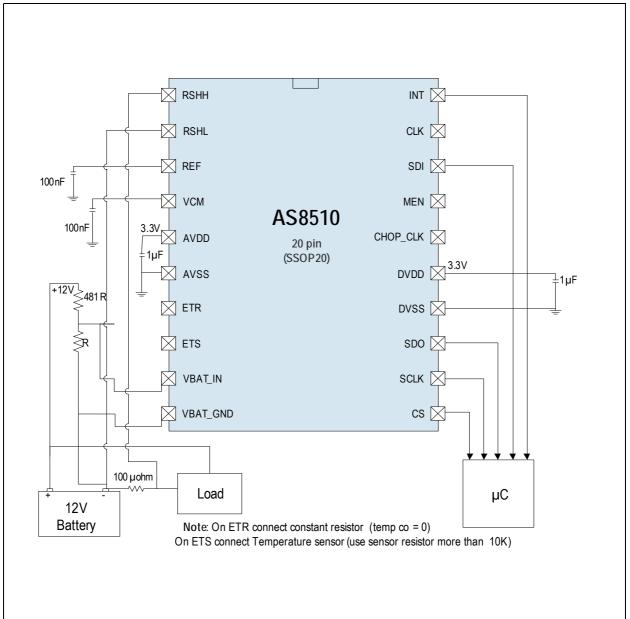

The AS8510 is ideal for shunt based batteries sensor. For high-side current sensing, the input signal may be conditioned using *ams* device AS8525 before applying to this device.

## Contents

| 1 | General Description                                                               | 1    |  |

|---|-----------------------------------------------------------------------------------|------|--|

| 2 | Key Features                                                                      | 1    |  |

| 3 | Applications                                                                      | 1    |  |

| 4 | Pin Assignments                                                                   | 4    |  |

|   | 4.1 Pin Descriptions                                                              | 4    |  |

| 5 | Absolute Maximum Ratings                                                          | 6    |  |

| 6 | Electrical Characteristics                                                        | 7    |  |

|   | 6.1 Operating Conditions                                                          | 7    |  |

|   | 6.2 DC/AC Characteristics for Digital Inputs and Outputs                          |      |  |

|   | 6.3 Detailed System and Block Specifications                                      |      |  |

|   | 6.3.1 Electrical System Specifications                                            |      |  |

|   | 6.4 Current Measurement Ranges (across 100µOhm shunt resistor)                    | 9    |  |

|   | 6.4.1 Differential Input Amplifier for Current Channel                            |      |  |

|   | 6.4.2 Differential Input Amplifier for Voltage Channel                            | .11  |  |

|   | 6.4.3 Sigma Delta Analog to Digital Converter                                     | . 12 |  |

|   | 6.4.4 Bandgap Reference Voltage                                                   |      |  |

|   | 6.4.5 Internal (Programmable) Current Source for External Temperature Measurement |      |  |

|   | 6.4.6 CMREF Circuit (VCM)                                                         |      |  |

|   | 6.4.7 Internal AVDD Power-on Reset                                                |      |  |

|   | 6.4.8 Internal DVDD Power-on Reset                                                |      |  |

|   | 6.4.10 High Speed Oscillator                                                      |      |  |

|   | 6.4.11 External Clock                                                             |      |  |

|   | 6.4.12 Internal Temperature Sensor                                                |      |  |

|   | 6.5 System Specifications                                                         |      |  |

| 7 | Detailed Description                                                              |      |  |

|   | 7.1 Current Measurement Channel                                                   |      |  |

|   | 7.2 Voltage/Temperature Measurement Channel                                       |      |  |

|   | 7.3 Digital Implementation of Measurement Path                                    |      |  |

|   | 7.4 Modes of Operation                                                            |      |  |

|   | 7.4.1 Normal Mode 1 (NOM1)                                                        |      |  |

|   | 7.4.2 Normal Mode 2 (NOM2)                                                        | .21  |  |

|   | 7.4.3 Standby Mode1 (SBM1)                                                        | . 22 |  |

|   | 7.4.4 Standby Mode2 (SBM2)                                                        | . 23 |  |

|   | 7.5 Reference-Voltage                                                             | . 23 |  |

|   | 7.6 Oscillators                                                                   | . 23 |  |

|   | 7.7 Power-On Reset                                                                | . 23 |  |

|   | 7.8 4-Wire Serial Port Interface                                                  | . 24 |  |

|   | 7.8.1 SPI Frame                                                                   |      |  |

|   | 7.8.2 Write Command                                                               |      |  |

|   | 7.8.3 Read Command                                                                |      |  |

|   | 7.8.4 Timing                                                                      |      |  |

|   | 7.8.5 SPI Interface Timing                                                        | . 28 |  |

| ě ě ě |       |      |

|-------|-------|------|

|       |       |      |

|       | ě ě ě |      |

|       |       |      |

|       |       |      |

|       |       |      |

|       |       |      |

|       |       |      |

|       |       | ēēē. |

|       |       | ěěě  |

|       |       |      |

|       |       |      |

|       |       |      |

| 7.9 Control Register                                                           | . 29 |

|--------------------------------------------------------------------------------|------|

| 7.9.1 Standby Mode - Power Consumption                                         | .40  |

| 7.9.2 Initialization Sequence at Power ON                                      | .40  |

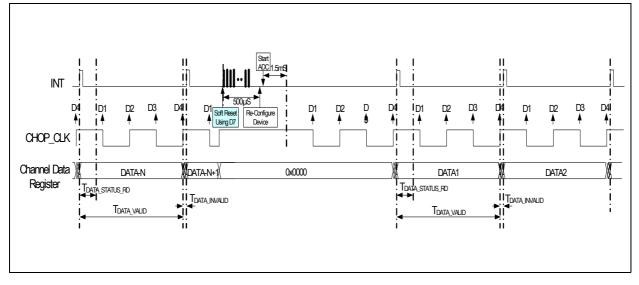

| 7.9.3 Soft-reset of Device Using Bit D[7] of Reset Register 0x09               | .41  |

| 7.9.4 Soft-reset of the Measurement Path Using Bit D[7] of Reset Register 0x09 | . 42 |

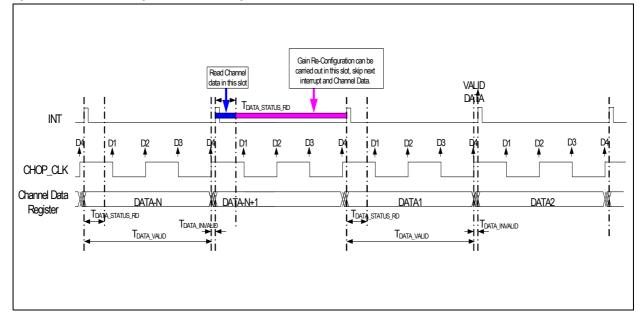

| 7.9.5 Reconfiguring Gain Setting of PGA                                        | . 42 |

| 7.9.6 Configuring the Device During Normal Mode                                | .43  |

| 7.10 Low Side Current Measurement Application                                  | . 43 |

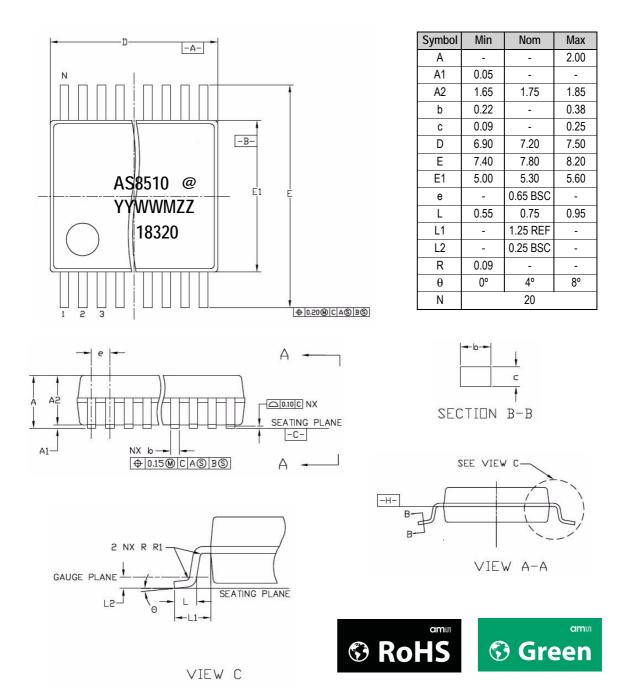

| 8 Package Drawings and Markings                                                | 44   |

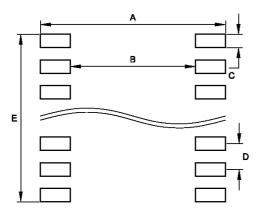

| 8.1 Recommended PCB Footprint                                                  | . 45 |

| 9 Ordering Information                                                         | 47   |

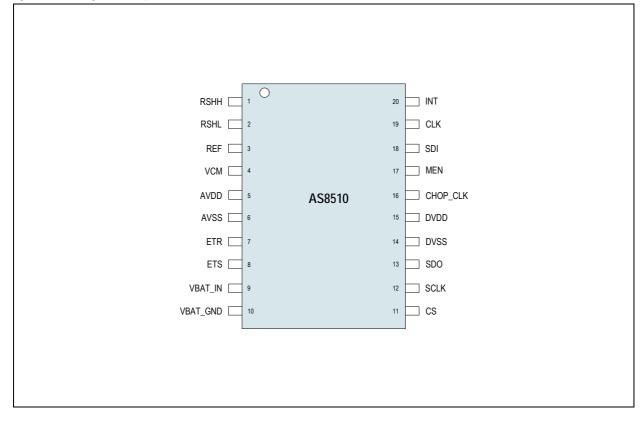

# 4 Pin Assignments

Figure 2. Pin Assignments (Top View)

## 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin Number | Pin Name | Pin Type                   | Description                                                                                |  |

|------------|----------|----------------------------|--------------------------------------------------------------------------------------------|--|

| 1          | RSHH     | Analog input               | Positive Differential input for current channel                                            |  |

| 2          | RSHL     | Analog input               | Negative differential input for current channel                                            |  |

| 3          | REF      |                            | Internal reference voltage to sigma-delta ADC; connect 100nF to AVSS from this pin.        |  |

| 4          | VCM      | Analog output              | Common Mode voltage to the internal measurement path; connect 100nF to AVSS from this pin. |  |

| 5          | AVDD     | Cumply and                 | +3.3V Analog Power-supply                                                                  |  |

| 6          | AVSS     | Supply pad                 | 0V Power-supply analog                                                                     |  |

| 7          | ETR      |                            | Voltage channel single ended input                                                         |  |

| 8          | ETS      |                            |                                                                                            |  |

| 9          | VBAT_IN  | Analog input               | Battery voltage (high) input                                                               |  |

| 10         | VBAT_GND |                            | Battery voltage (low) input                                                                |  |

| 11         | CS       | Digital input with pull-up | Chip select with an internal pull-up resistor (SPI Interface)                              |  |

| 12         | SCLK     | Digital input              | Clock signal (SPI Interface)                                                               |  |

| 13         | SDO      | Digital output             | Serial Data Input (SPI Interface)                                                          |  |

### Table 1. Pin Descriptions

| Pin Number | Pin Name | Pin Type          | Description                                                                                                                                                                                                                                                                              |

|------------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14         | DVSS     | Supply pod        | 0V Digital Ground                                                                                                                                                                                                                                                                        |

| 15         | DVDD     | Supply pad        | +3.3V Digital Supply                                                                                                                                                                                                                                                                     |

| 16         | CHOP_CLK | Divited as devide | Chop Clock used in High side measurements to synchronize external chopper.<br>(As an example, when AS8525 is used to condition the input signal to the input range of AS8510, the chop clock is used by AS8525.)                                                                         |

| 17         | MEN      | Digital output    | Digital output issued during the Standby Mode (SBM) to signal<br>the short duration of data sampling. This signal is useful in the<br>case of a High Side Measurement application.<br>(For example: This signal is used by AS8525 device to wake-up<br>and enable the measurement path.) |

| 18         | SDI      | Digital input     | Data signal (SPI Interface)                                                                                                                                                                                                                                                              |

| 19         | CLK      | Digital I/O       | By default this pin is the internal clock output which can be used<br>by a Microcontroller. The internal clock may also be disabled as<br>an output by programming Register 08. To use an external Clock,<br>Register 08 has to be programmed.                                           |

| 20         | INT      | Digital output    | Active High Interrupt to indicate data is ready                                                                                                                                                                                                                                          |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 7 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Tabla 2  | Abcoluto | Maximum       | Datinac  |

|----------|----------|---------------|----------|

| Table 2. | ADSUIULE | IVIAXIIIIUIII | Rallings |

| Parameter                                                      | Min  | Мах                      | Units | Notes                                                                                                           |

|----------------------------------------------------------------|------|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------|

| Electrical Parameters                                          |      | 1                        |       |                                                                                                                 |

| DC supply voltage (AVDD and DVDD)                              | -0.3 | 5                        | V     |                                                                                                                 |

| Input voltage (VIN)                                            | -0.3 | AVDD + 0.3<br>DVDD + 0.3 | V     |                                                                                                                 |

| Input current (latchup immunity)<br>(IscR)                     | -100 | 100                      | mA    | AEC - Q100 - 004                                                                                                |

| Electrostatic Discharge                                        | •    |                          |       |                                                                                                                 |

| Electrostatic discharge (ESD) all pins                         |      | ±2                       | kV    | AEC - Q100 - 002                                                                                                |

| Continuous Power Dissipation                                   | •    |                          |       |                                                                                                                 |

| Total power dissipation (all supplies and outputs) ( $P_{t}$ ) |      | 50                       | mW    | SSOP20 in still air, soldered on JEDEC<br>standard board @ 125° ambient, static<br>operation with no time limit |

| Temperature Ranges and Storage Condition                       | ns   |                          |       |                                                                                                                 |

| Storage temperature (T <sub>STRG</sub> )                       | -50  | 125                      | °C    |                                                                                                                 |

| Junction temperature (TJ)                                      |      | 130                      | °C    |                                                                                                                 |

| Thermal resistance (RthJC)                                     |      | 80                       | K/W   | JEDEC standard test board, 0 air velocity                                                                       |

| Package body temperature (T <sub>BODY</sub> )                  |      | 260                      | °C    | Norm: IPC/JEDEC J-STD-020 <sup>1</sup>                                                                          |

| Moisture Sensitive level (MSL)                                 |      | 3                        |       |                                                                                                                 |

| Humidity non-condensing                                        | 5    | 85                       | %     |                                                                                                                 |

1. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-hermetic Solid State Surface Mount Devices".

# 6 Electrical Characteristics

## 6.1 Operating Conditions

Table 3. Operating Conditions

| Symbol            | Parameter                                 | Conditions | Min  | Мах   | Units |

|-------------------|-------------------------------------------|------------|------|-------|-------|

| AVDD              | Positive analog supply voltage            |            | 3.0  | 3.6   | V     |

| AVSS              | 0V Ground                                 |            | 0    | 0     | V     |

| A - D             | Difference in analog and digital supplies |            |      | 0.1   | V     |

| DVDD              | Positive digital supply                   |            | 2.97 | 3.63  | V     |

| DVSS              | 0V Digital Ground                         |            | 0    | 0     | V     |

| T <sub>AMB</sub>  | Ambient temperature                       |            | -40  | 125   | °C    |

| I <sub>SUPP</sub> | Supply current                            |            |      | 5.5   | mA    |

| f <sub>CLK</sub>  | System clock frequency <sup>1</sup>       |            |      | 4.096 | MHz   |

1. Nominal clock frequency from external or internal oscillator.

## 6.2 DC/AC Characteristics for Digital Inputs and Outputs

All pull-up and pull-down have been implemented with active devices. SDO has been measured with 10pF load.

Table 4. INT

| Symbol            | Parameter                 | Conditions | Min | Тур | Max | Units |

|-------------------|---------------------------|------------|-----|-----|-----|-------|

| I <sub>LEAK</sub> | Tri-state leakage current |            | -1  |     | +1  | μA    |

| V <sub>OH</sub>   | High level output voltage |            | 2.5 |     |     | V     |

| V <sub>OL</sub>   | Low level output voltage  |            |     |     | 0.4 | V     |

| lo                | Output Current            |            |     |     | 4   | mA    |

Table 5. CS Input

| Symbol            | Parameter                | Conditions               | Min  | Тур | Max | Units |

|-------------------|--------------------------|--------------------------|------|-----|-----|-------|

| V <sub>IH</sub>   | High level input voltage |                          | 2.0  |     |     | V     |

| V <sub>IL</sub>   | Low level input voltage  |                          |      |     | 0.8 | V     |

| I <sub>LEAK</sub> | Input leakage current    |                          | -1   |     | +1  | μA    |

| lpu               | Pull up current          | CS pulled to DVDD = 3.3V | -150 |     | -15 | μA    |

Table 6. SDI

| Symbol            | Parameter                | Conditions | Min | Тур | Мах | Units |

|-------------------|--------------------------|------------|-----|-----|-----|-------|

| VIH               | High level input voltage |            | 2.0 |     |     | V     |

| V <sub>IL</sub>   | Low level input voltage  |            |     |     | 0.8 | V     |

| I <sub>LEAK</sub> | Input leakage current    |            | -1  |     | +1  | μA    |

Table 7. SDO Output

| Symbol          | Parameter                 | Conditions    | Min | Тур | Мах | Units |

|-----------------|---------------------------|---------------|-----|-----|-----|-------|

| V <sub>OH</sub> | High level output voltage | Isource = 8mA | 2.5 |     |     | V     |

| V <sub>OL</sub> | Low level output voltage  | Isink = 8mA   |     |     | 0.4 | V     |

| lo              | Output Current            |               |     |     | 8   | mA    |

Table 8. CHOP\_CLK Output

| Symbol          | Parameter                 | Conditions | Min | Тур | Max | Units |

|-----------------|---------------------------|------------|-----|-----|-----|-------|

| V <sub>OH</sub> | High level output voltage |            | 2.5 |     |     | V     |

| V <sub>OL</sub> | Low level output voltage  |            |     |     | 0.4 | V     |

| lo              | Output Current            |            |     |     | 4   | mA    |

Table 9. CLK I/O with Input Schmitt Trigger and Output Buffer

| Symbol            | Parameter                 | Conditions         | Min | Тур | Мах | Units |

|-------------------|---------------------------|--------------------|-----|-----|-----|-------|

| V <sub>IH</sub>   | High level input voltage  | DVdd = 3.3V        | 2.4 |     |     | V     |

| VIL               | Low level input voltage   | DVdd = 3.3V        |     |     | 1.0 | V     |

| I <sub>LEAK</sub> | Input leakage current     |                    | -1  |     | +1  | μA    |

| I <sub>PD</sub>   | Pull down current         | CLK pulled to DVSS | 10  |     | 100 | μA    |

| lo                | Output Current            |                    |     |     | 4   | mA    |

| V <sub>OH</sub>   | High level output voltage |                    | 2.5 |     |     | V     |

| V <sub>OL</sub>   | Low level output voltage  |                    |     |     | 0.4 | V     |

## Table 10. SCLK with Input Schmitt Trigger

| Symbol            | Parameter                | Conditions  | Min | Тур | Мах | Units |

|-------------------|--------------------------|-------------|-----|-----|-----|-------|

| VIH               | High level input voltage | DVdd = 3.3V | 2.4 |     |     | V     |

| VIL               | Low level input voltage  | DVdd = 3.3V |     |     | 1.0 | V     |

| I <sub>LEAK</sub> | Input leakage current    |             | -1  |     | +1  | μA    |

Table 11. MEN Output

| Symbol          | Parameter                 | Conditions | Min | Тур | Мах | Units |

|-----------------|---------------------------|------------|-----|-----|-----|-------|

| V <sub>OH</sub> | High level output voltage |            | 2.5 |     |     | V     |

| V <sub>OL</sub> | Low level output voltage  |            |     |     | 0.4 | V     |

| lo              | Output Current            |            |     |     | 2   | mA    |

## 6.3 Detailed System and Block Specifications

## 6.3.1 Electrical System Specifications

Table 12. Electrical System Specifications

| Symbol             | Parameter                        | Min | Тур | Max | Units | Notes                                                                                                    |

|--------------------|----------------------------------|-----|-----|-----|-------|----------------------------------------------------------------------------------------------------------|

| IDD <sub>NOM</sub> | Current consumption normal mode  |     | 3   | 5.5 | mA    |                                                                                                          |

| IDD <sub>SBM</sub> | Current consumption standby mode |     | 40  |     | μΑ    | Average of NORMAL Mode Power<br>consumption over a period of 10sec<br>when the device is in STANDBY Mode |

## 6.4 Current Measurement Ranges (across 100µOhm shunt resistor)

Table 13. Current Measurement Ranges

| Symbol | Parameter                           | I <sub>max</sub><br>[A] | V <sub>sh</sub><br>[mV] | PGA<br>Gain<br>Nominal | Data Rate<br>(f <sub>OUT</sub> ) | V <sub>INADC</sub> 1<br>[mV] | PSR <sup>2</sup><br>[dB] |

|--------|-------------------------------------|-------------------------|-------------------------|------------------------|----------------------------------|------------------------------|--------------------------|

| 170    | Input current range of 70A in NOM   | ±77                     | ±8.1                    | 100                    | @ 1 kHz                          | 890                          | 60                       |

| 1200   | Input current range of 200A in NOM  | ±235                    | ±24.7                   | 40                     | @ 1 kHz                          | 1088                         | 60                       |

| 1400   | Input current range of 400A in NOM  | ±400                    | ±42                     | 25                     | @ 1 kHz                          | 1137                         | 60                       |

| 11500  | Input current range of 1500A in NOM | +2076/-1523             | +218/-160               | 5                      | @ 1 kHz                          | 1204                         | 60                       |

1.  $V_{INADC} = V_{sh} *$  Gain, gain deviations to be considered according to Table 15 and Table 16.

2. AVDD, DVDD of 3.3V with  $\pm$ 5% variation.

The maximum current range can be calculated by the equation:

$I_{max} = (VREF_{min} - V_{OSDRIFT}*Gn*e)/(Gn *e*R_{SHUNT})$

Where

VREF<sub>min</sub> is minimum ADC reference voltage for the anticipated temperature range e.g.1220mV

VOSDRIFT is the maximum input referred PGA offset (e.g. 3 mV)

Gn is the nominal gain as selected (G1 to G4)

e is maximum gain tolerance (1,1)

$R_{\mbox{\scriptsize SHUNT}}$  is the maximum shunt resistance

Exceeding this maximum current range will lead first to non-linearity and finally to clamping.

**Note:** The Data Rate at the output can be calculated according to the formula:

fsout=2\*fchop /R2 (R2 is down sampling ratio taking values 1, 2, 4 up to 32768 as powers of 2)

Table 14. Valid Combinations of the Chopper Clock, Oversampling Clock and Decimation Ratios

| Over Sampling Frequency | Chopper Frequency | Decimation Ratio |

|-------------------------|-------------------|------------------|

| 1.024MHz                | 2kHz              | 64               |

| 2.048MHz                | 2kHz              | 64               |

| 2.048MHz                | 2kHz              | 128              |

| 2.048MHz                | 4kHz              | 64               |

## 6.4.1 Differential Input Amplifier for Current Channel

Table 15. Differential Input Amplifier for Current Channel

| Symbol               | Parameter                                 | Conditions                                                      | Min      | Тур          | Max      | Units  |

|----------------------|-------------------------------------------|-----------------------------------------------------------------|----------|--------------|----------|--------|

| VIN_AMP              | Input voltage range                       | RSHH and RSHL                                                   | -160     |              | +160     | mV     |

| I <sub>IN_</sub> AMP | Input current <sup>1, 11</sup>            | RSHH and RSHL@ +160mV input<br>voltage at 125℃ with PGA         | -50      | 2            | 50       | nA     |

| ICM                  | Absolute input voltage range <sup>2</sup> |                                                                 |          | -160<br>+300 |          | mV     |

| G = G1               | Gain1 <sup>3, 4, 9</sup>                  | 110                                                             |          | 100          |          |        |

| G = G2               | Gain2 <sup>3, 4, 9</sup>                  | 1200                                                            |          | 40           |          |        |

| G = G3               | Gain3 <sup>3, 4, 9</sup>                  | 1400                                                            |          | 25           |          |        |

| G = G4               | Gain4 <sup>3, 4, 9</sup>                  | 11500                                                           |          | 5            |          |        |

| е                    | Gain deviation                            | i = 1, 2, 3, 4                                                  | 0.9 * Gi |              | 1.1 * Gi |        |

| f <sub>P</sub> _AMP  | Pole frequency 4, 5                       |                                                                 | 15       |              |          | kHz    |

| εT1                  | Gain drift with temperature <sup>6</sup>  | -20°C to +65°C<br>Gain 5, 25, referenced to room<br>temperature |          |              | ±0.3     | %      |

| V <sub>OSDRIFT</sub> | Offset drift with temperature 7, 10       | @65°C                                                           |          | 350          | 2700     | μV     |

| V <sub>os</sub>      | 7.10                                      | After trim at -20°C                                             |          |              | 420      | μV     |

| V <sub>os_ch</sub>   | Input referred offset <sup>7, 10</sup>    | Chopping enabled                                                |          | 0            |          | LSB    |

| V <sub>Ndin</sub>    | Noise density 4,8                         |                                                                 |          | 25           |          | nV/√Hz |

| THD                  | Total harmonic distortion                 | For 150 Hz input signal                                         |          | 70           |          | dB     |

- 1. Leakage test accuracy is limited by tester resource accuracy and tester hardware.

- 2. For gain 100 PGA input common mode is 0V and the minimum supply is 3.15V.

- 3. The measurement ranges are referred only by the gain of input amplifier, while other parameters such as bandwidth etc. are programmed independently.

- 4. This parameter is not measured directly in production. It is measured indirectly via gain measurements of the whole path. It is guaranteed by design.

- 5. Pole frequency of input amplifier changes with GAIN. The number is valid for the gain at G1, while the bandwidth will be higher for other ranges. This parameter is not measured in production.

- 6. Based on device evaluation. Not tested.

- 7. These offsets are cancelled if chopping enabled (default).

- 8. Noise density calculated by taking system bandwidth as 150Hz.

- 9. Refer to Measurement Ranges shown in Table 13.

- 10. No impact on the measurement path. If the chopping is enabled, both the offset and offset drift will be eliminated.

- 11. For negative input voltages up to -160mV below ground, Input leakage is typically -20nA @ 65°C due to forward conductance of protection diode.

## 6.4.2 Differential Input Amplifier for Voltage Channel

Table 16. Differential Input Amplifier for Voltage Channel

| Symbol               | Parameter                                  | Conditions                                                      | Min      | Тур          | Мах      | Units  |

|----------------------|--------------------------------------------|-----------------------------------------------------------------|----------|--------------|----------|--------|

| V <sub>IN_AMP</sub>  | Input voltage range <sup>1, 10</sup>       |                                                                 | -160     |              | +160     | mV     |

| I <sub>IN_AMP</sub>  | Input current <sup>2, 10</sup>             | VBAT_IN, ETR, ETS @ +160mV input<br>voltage at 125°C with PGA   | -50      | 2            | 50       | nA     |

| ICM                  | Absolute input voltage range <sup>3</sup>  |                                                                 |          | -160<br>+300 |          | mV     |

| G = G1               | Gain1 <sup>4, 5</sup>                      |                                                                 |          | 100          |          |        |

| G = G2               | Gain2 <sup>4,5</sup>                       |                                                                 |          | 40           |          |        |

| G = G3               | Gain3 <sup>4, 5</sup>                      |                                                                 |          | 25           |          |        |

| G = G4               | Gain4 <sup>4, 5</sup>                      |                                                                 |          | 5            |          |        |

| е                    | Gain deviation                             | i = 1, 2, 3, 4                                                  | 0.9 * Gi |              | 1.1 * Gi |        |

| f <sub>P_AMP</sub>   | Pole frequency 5, 6                        |                                                                 | 15       |              |          | kHz    |

| V <sub>NDIN</sub>    | Noise density <sup>5, 7</sup>              |                                                                 |          | 25           |          | nV/√Hz |

| THD                  | Total harmonic distortion                  | For 150Hz input signal                                          |          | 70           |          | dB     |

| εт1                  | Gain drift with temperature <sup>8</sup>   | -20°C to +65°C<br>Gain 5, 25, referenced to room<br>temperature |          |              | ±0.3     | %      |

| V <sub>OS</sub>      | land a fame d attack 9                     | After trim at -20°C                                             |          |              | 420      | μV     |

| V <sub>os_ch</sub>   | Input referred offset <sup>9</sup>         | Chopping enabled                                                |          | 0            |          | LSB    |

| V <sub>OSDRIFT</sub> | Offset drift with temperature <sup>9</sup> | @65°C                                                           |          | 350          | 2700     | μV     |

- 1. Input for the voltage channel can be as high as 1220mV, in this high input case PGA will be bypassed.

- 2. Leakage test accuracy is limited by tester resource accuracy and tester hardware, especially at low temperatures due to condensing moisture.

- 3. For gain 100 PGA input common mode is 0V and the minimum supply is 3.15V.

- 4. The measurement ranges are referred only by the gain of input amplifier, while other parameters such as bandwidth etc. are programmed independently.

- 5. This parameter is not measured directly in production. It is measured indirectly via gain measurements of the whole path. It is guaranteed by design.

- 6. Pole frequency of input amplifier changes with changing the GAIN. The number is valid for the gain at G1, while the bandwidth will be higher for other ranges. This parameter is not measured in production.

- 7. Noise density calculated by taking system bandwidth as 150Hz.

- 8. Based on device evaluation. Not tested.

- 9. No impact on the measurement path. If the chopping is enabled, both the offset and offset drift will be eliminated.

- 10. For negative input voltages up to -160mV below ground, Input leakage is typically -20nA @ 65°C due to forward conductance of protection diode.

## 6.4.3 Sigma Delta Analog to Digital Converter

Table 17. Sigma Delta Analog to Digital Converter

| Symbol           | Parameter                                        | Conditions                  | Min | Тур           | Мах   | Units |

|------------------|--------------------------------------------------|-----------------------------|-----|---------------|-------|-------|

| VREF             | Reference voltage <sup>6</sup>                   |                             |     | 1.225         |       | V     |

| VINADC           | Input range <sup>1</sup>                         | At V <sub>ref</sub> = 1.22V | 0   |               | ±1.22 | V     |

| R1               | Oversampling ratio/Decimation Ratio <sup>2</sup> |                             | 64  | 128           | 128   |       |

| f <sub>ovs</sub> | Oversampling frequency <sup>3</sup>              |                             |     | 1024/<br>2048 |       | kHz   |

| RES              | Number of bits                                   |                             |     |               | 16    | bits  |

| BW               | Bandwidth <sup>4</sup>                           |                             | 1   |               | 500   | Hz    |

| S/N              | Signal to noise ratio <sup>5</sup>               |                             |     | 90            |       | dB    |

#### Notes:

- 1. Production test at ±800mV. Maximum VIN can be 1.22V with VREF=1.225V.

- 2. Programmable. It is defined with respect to the first decimator in the  $\Sigma\Delta$  ADC.

- 3. Programmable: Internal clock is 1024/2048 kHz; external clock max is 8192 kHz.

- Dependent on fovs, R1 and R2. The bandwidth is calculated according to the formula: BW=fovs/(2\*R1\*R2); the sampling frequency at the output of the A/D converter is 2\*BW.

- 5. Defined at maximum input signal, BW=500 Hz (1Hz to 500 Hz), fovs=1024 kHz, R1=64, fchop=2 kHz and R2=2.

- 6. Reference voltage might be forced from external.

#### 6.4.4 Bandgap Reference Voltage

Table 18. Bandgap Reference Voltage

| Symbol                                    | Parameter                                            | Conditions                         | Min  | Тур           | Max  | Units  |

|-------------------------------------------|------------------------------------------------------|------------------------------------|------|---------------|------|--------|

| V <sub>REFtrim</sub>                      | Reference Voltage after trim <sup>1, 2</sup>         | Trim at 65°C                       |      | 1.225         |      | V      |

| V <sub>REFACC</sub>                       | Reference Voltage Initial Accuracy 1, 2              | At 65°C                            |      |               | ±3.5 | mV     |

| V <sub>REFDRIFT</sub> Reference Voltage T | Reference Voltage Temperature drift                  | Temperature range<br>-20 to 65 °C  |      |               | ±0.4 | %      |

| V REFURIFI                                |                                                      | Temperature range<br>-40 to 125 °C |      | +0.4/<br>-0.6 |      | %      |

| PSRR <sub>REF</sub>                       | PSR @ dc                                             |                                    |      | 80            |      | dB     |

| SUT <sub>AVDD</sub>                       | Start Up Time with supply ramp <sup>3</sup>          |                                    |      | 5             |      | ms     |

| SUT <sub>PD</sub>                         | Start Up Time from power down <sup>3</sup>           |                                    |      |               | 1    | ms     |

| R <sub>NDVREF</sub>                       | Output resistance of band gap                        |                                    |      | 500           | 1000 | Ω      |

| V <sub>NDVREF</sub>                       | Bandgap reference thermal noise density <sup>3</sup> |                                    |      |               | 300  | nV/√Hz |

| CL <sub>VREF</sub>                        | Quitaut Capacitar (Caramia)                          |                                    |      | 100           |      | nF     |

| ESR <sub>VREF</sub>                       | Output Capacitor (Ceramic)                           |                                    | 0.02 |               | 1    | Ω      |

- 1. Accuracy at 65°C.

- 2. No DC current is allowed from this pin.

- 3. This is a design parameter and not production tested.

## 6.4.5 Internal (Programmable) Current Source for External Temperature Measurement

Table 19. External Temperature Measurement

| Symbol                 | Parameter                                                 | Conditions                        | Min | Тур  | Мах    | Units      |

|------------------------|-----------------------------------------------------------|-----------------------------------|-----|------|--------|------------|

| I <sub>CURON</sub>     | 5-bit current source enabled <sup>1</sup>                 | 5-bit programmable current source | 0   | 270  | 320    | μA         |

|                        | 5-bit current source disabled                             | Limited by leakage                |     | 10   |        | nA         |

| $T_{K_{CS}}$           | Temperature coefficient of current source <sup>2</sup>    |                                   |     | 1000 |        | ppm<br>∕°K |

| V <sub>MAXETR</sub>    | Voltage on pin ETR <sup>3</sup>                           |                                   |     |      | 1000/G | mV         |

| VMAXETRMOD             | Max voltage on pin ETR when PGA is bypassed <sup>4</sup>  |                                   |     |      | 1.22   | V          |

| V <sub>MAXETS</sub>    | Voltage on pin ETS for resistor sensor <sup>3</sup>       |                                   |     |      | 1000/G | V          |

| V <sub>MAXETSMOD</sub> | Max. Voltage on pin ETS when PGA is bypassed <sup>5</sup> |                                   |     |      | 1.22   | V          |

- 1. Current value can be programmed in steps of 8µA from 0 to 256µA with a process error of 30%.

- 2. Temperature coefficient is not important since external temperature measurement is a 2 step measurement. The value specified is guaranteed by design and will not be tested in production.

- 3. Maximum voltage on pin ETR (reference) can be calculated by given formula, where G is the gain of PGA (G=100).

- 4. Maximum voltage on pin ETR, if PGA is bypassed.

- 5. Maximum voltage on pin ETS, if PGA is bypassed.

## 6.4.6 CMREF Circuit (VCM)

Table 20. CMREF Circuit

| Symbol           | Parameter        | Min | Тур | Мах | Units |

|------------------|------------------|-----|-----|-----|-------|

| V <sub>VCM</sub> | Output voltage   | 1.6 | 1.7 | 1.8 | V     |

| CL               | Load capacitance |     | 100 |     | nF    |

#### 6.4.7 Internal AVDD Power-on Reset

Table 21. Internal AVDD Power-on Reset

| Symbol            | Parameter                                                                                                        | Min | Тур | Мах | Units |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| $V_{PORHIA}$      | Power On Reset Threshold                                                                                         | 2.2 | 2.4 | 2.6 | V     |

| t <sub>pora</sub> | POR time - The duration from Power ON till<br>the time, internal Power On Reset signal<br>goes HIGH <sup>1</sup> | 1   |     |     | μs    |

| I <sub>pora</sub> | Current consumption in POR block <sup>2</sup>                                                                    |     | 1.5 |     | μΑ    |

1. POR pulse is always longer than tPORA whatever the slope of the supply.

2.  $I_{\mbox{\tiny PORA}}$  can not be switched off.

#### 6.4.8 Internal DVDD Power-on Reset

Table 22. Internal DVDD Power-on Reset

| Symbol            | Parameter                                                                                                        | Min | Тур  | Мах | Units |

|-------------------|------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| $V_{PORHID}$      | Power On Reset Threshold                                                                                         | 2.2 | 2.4  | 2.7 | V     |

| V <sub>HYST</sub> | Hysteresis <sup>1</sup>                                                                                          | 0.2 | 0.25 | 0.4 | V     |

| t <sub>PORD</sub> | POR time - The duration from Power ON till the<br>time, internal Power On Reset signal goes<br>HIGH <sup>2</sup> | 1   |      |     | μs    |

| I <sub>PORD</sub> | Current <sup>3</sup>                                                                                             |     | 1.5  |     | μΑ    |

1.  $V_{PORLO} = V_{PORHI} - V_{HYST}$  where  $V_{PORLO}$  is the lower threshold of POR.

2.  $V_{PORLO} = V_{PORHI} - V_{HYST}$  where  $V_{PORLO}$  is the lower threshold of POR.

3.  $I_{PORD}$  can not be switched off.

#### 6.4.9 Low Speed Oscillator

Table 23. Low Speed Oscillator

| Symbol              | Parameter      | Min | Тур     | Мах | Units |

|---------------------|----------------|-----|---------|-----|-------|

| $f_{LS}$            | Frequency      |     | 262.144 |     | kHz   |

| f <sub>LS_ACC</sub> | Accuracy       |     | ± 7     |     | %     |

| I <sub>LS</sub>     | Supply current |     | 5       |     | μA    |

## 6.4.10 High Speed Oscillator

Table 24. High Speed Oscillator

| Symbol             | Parameter                | Min | Тур   | Мах | Units |

|--------------------|--------------------------|-----|-------|-----|-------|

| f <sub>HS</sub>    | Frequency                |     | 4.096 |     | MHz   |

| f <sub>HSACC</sub> | Accuracy <sup>1, 2</sup> |     | ±4    |     | %     |

| I <sub>HS</sub>    | Supply current           |     | 300   |     | μA    |

#### Notes:

- 1. Accuracy after trimming.

- 2. Accuracy for limited temperature range of -20 to 65 °C.

#### 6.4.11 External Clock

Table 25. External Clock

| Symbol                | Parameter                    | Conditions                                                             | Min | Тур                    | Мах | Units |

|-----------------------|------------------------------|------------------------------------------------------------------------|-----|------------------------|-----|-------|

| f <sub>clkext</sub>   | Clock frequency              |                                                                        |     | 2048/<br>4096/<br>8192 |     | kHz   |

| DIV <sub>clkext</sub> | Clock division factor        | to be programmed in Register 08<br>CLK_REG through the serial bus SPI. |     | 2/4/8                  |     |       |

| DC <sub>CLKEXT</sub>  | Duty Cycle of external clock |                                                                        | 40  |                        | 60  | %     |

## 6.4.12 Internal Temperature Sensor

Table 26. Internal Temperature Sensor

| Symbol              | Parameter                           | Conditions                                                                                                    | Min   | Тур   | Мах   | Units    |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|

| T <sub>INTRNG</sub> | Temperature sensor range            |                                                                                                               | -40   |       | 125   | °C       |

| $\Delta_{TIN}$      | Temperature measurement accuracy    |                                                                                                               |       | 3     |       | °C       |

| T <sub>INTSLP</sub> | Temperature sensor slope            | Guaranteed by design; at PGA gain 5<br>which is the recommended Gain for<br>internal temperature measurement. |       | 27    |       | Digits/C |

| TINT65G5            | Temperature sensor output at gain 5 |                                                                                                               | 40660 | 41807 | 43012 | Digits   |

## 6.5 System Specifications

Table 27. System Specifications

| Symbol         | Parameter                                                          | Min | Тур | Мах | Units |

|----------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>S</sub> | Channel to channel isolation <sup>1</sup>                          |     |     | -90 | dB    |

| At             | Difference in channel to channel attenuation @600Hz <sup>1,2</sup> |     |     | 3   | dB    |

| Ph             | Difference in phase shift between the two channels @600Hz $^{1,2}$ |     |     | 5   | Deg   |

System Measurement Error Budget for Voltage and Current Channel.

#### Temperature Range: -20°C to +65°C; Output data rate is 1kHz, VCC = 3.3V, chopping enabled.

Table 28. System Measurement Error Budget for Gains 5 and 25

| Symbol | Parameter                                                | Conditions                        | Min | Тур  | Max    | Units |

|--------|----------------------------------------------------------|-----------------------------------|-----|------|--------|-------|

| Err    | System measurement error <sup>3, 4</sup>                 |                                   |     | ±0.5 | ±0.8   | %     |

| Err    | Voltage channel signal path measurement error $^{\rm 5}$ |                                   |     |      | ±0.5   | 70    |

|        | Measurement error due to PGA gain drift                  | From device evaluation            |     |      | ±0.3   | %     |

|        | Measurement error due to VREF drift                      |                                   |     |      | ±0.4   | %     |

|        | Measurement error due to non-linearity of PGA            | Tested by distortion measurements |     |      | ±0.025 | %     |

- 1. These specifications are defined by taking one channel as reference and measured on the other channel.

- 2. Guaranteed by design.

- 3. System measurement error due to noise, individual block parameter drifts and non linearity. Based on evaluation, not tested.

- 4. System error due to offset is neglected because of chopper architecture.

- 5. PGA is by-passed.

| ě ě ě |       |       |

|-------|-------|-------|

|       |       |       |

|       |       |       |

|       |       |       |

|       |       |       |

| 000   | ě ě ě |       |

| ěěě   |       | ěěě   |

|       |       |       |

|       |       |       |

|       |       | ě ě ě |

|       |       | ěěě   |

|       |       |       |

|       |       |       |

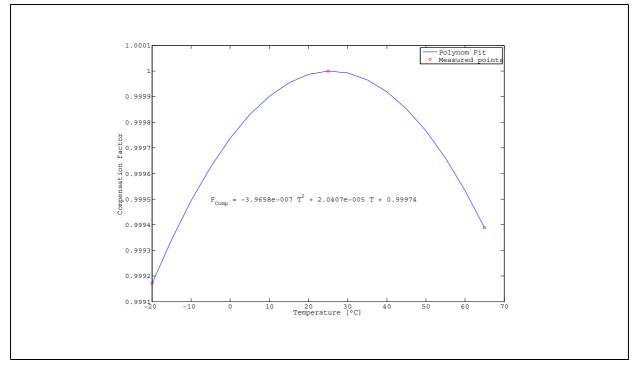

System Error Compensation Function: For battery voltage measurement it is recommended to by-pass the PGA. This eliminates PGA gain drift as an error source, thus error for the VBAT/VBAT\_GND differential signal path is determined by VREF drift with temperature. The typical characteristic of VREF versus temperature extracted from 3 production lots is shown in Figure 3. This function could be used to improve accuracy by an error correction method utilizing the internal temperature sensor. In this case ADC raw data readings need to be corrected with a temperature dependent factor by the software in the external micro controller. This factor is given by a generic compensation function and can be applied to all IC's because VREF is production trimmed to minimize linear coefficient of VREF over temperature.

Figure 3. Reference Error Compensation Function

Generic compensation factor the ADC output need to be multiplied with:

$\mathsf{F}_{\mathsf{comp}} = (\mathsf{A}^*\mathsf{T}^2 + \mathsf{B}^*\mathsf{T} + \mathsf{C})$

Where:

F<sub>comp</sub> is the compensation factor for VREF drift over temperature normalized to 1 at 25°C

T is Temperature reading from calibrated internal temperature sensor in [°C]

A: -4E-7

B: 2E-5

C: 0,9997

The compensated ADC value = raw ADC value \* F<sub>comp</sub>

If PGA is by-passed and an external precision reference is applied, the signal path measurement error is basically determined by the drift due to temperature and ageing of the external reference.

Current channel error contributions for a single temperature end of line calibrated system are shunt resistance, PGA gain and VREF changes

with temperature. The drift of a shunt resistor made from Manganin alloy and VREF drift with temperature are non-linear and show 2<sup>nd</sup> order curvature in same direction and similar relative magnitude. Thus shunt error is already reduced by the generic VREF(T) curvature (see Figure 3) if thermally coupled to the AS8510. Over all error can be further reduced by an error correction method in external micro controller by matching typical VREF(T) curvature to R<sub>shunt</sub> (T) curvature with the help of the internal temperature sensor.

Total final current channel system error calculated from quadratic summing of error contributions from Isabellenhuette shunt PPAP data and AS8510 safe launch data over 21000 units is ±0.5%.

*Temperature sensor system considerations:* Internal temperature sensor can be used to measure the ambient temperature because there is just 13 mW of AS8510 power dissipation in normal mode. This results in internal self-heating of less than 1°C.

# 7 Detailed Description

The AS8510 consists of two independent high resolution 16-bit SD analog to digital conversion channels. The measurement path of these two channels integrates a programmable gain amplifier, chopper and de-chopper, sigma-delta modulator, decimator and a digital filter for simultaneous measurement of Current and Voltage/Temperature.

The two measurement channels, namely the Current and Voltage/Temperature measurement channels have identical data path.

The input signal is amplified in the Programmable Gain Amplifier (PGA) with any of the selected gains of 1, 5, 25, 40 and 100 facilitating measurement of a wide range of Current, voltage and temperature levels. Gain Settings for different input ranges and any associated restrictions are explained in the Table 13.

Offset in the measurement path is minimized with the use of a chopper and a de-chopper at appropriate stages in the data path. By default the chopper/de-chopper is ON in the measurement path. It may be disabled by programming the appropriate register.

The amplified input signal is converted into a single-bit pulse-density modulated stream by the  $\Sigma$ - $\Delta$  Modulator. A decimator acting as a low-pass filter filters out the quantization noise and generates 16-bit data corresponding to the input signal. The decimation ratios of 64, 128 may be selected in the first filter stage. For reducing data rate further, the second stage decimation can be used.

An optional FIR Filter is provided to offer matched low pass filter response typically required in lead acid battery sensor systems.

## 7.1 Current Measurement Channel

The voltage across a Shunt Resistor, connected in series with the Battery negative terminal, forms the input signal to the Current Measurement channel. RSHH and RSHL are the Current measurement input pins. Offset in the input signal is nullified with the use of a chopper and a dechopper at appropriate stages in the data path. The programmable gain amplifier in the data path with programmable settings of 1, 5, 25, 40 and 100 enables measurement of current ranges from  $\pm 1A$  to  $\pm 1500A$ . The sampled input signal is converted into a single-bit pulse-density modulated stream by the  $\Sigma$ - $\Delta$  Modulator. A decimator acting as a low-pass filter filters out the quantization noise and generates 16-bit data equivalent to the input current signal. The programmable input sampling rate and the decimation ratio determine the output data rates. The data path can be programmed to provide 1Hz to 2 kHz rates in the various modes available. An optional FIR filter is provided to offer matched low pass filter response typically required in lead acid battery sensor systems.

After enabling the current measurement channel, the delay for the availability of the first sample is two conversion cycles.

## 7.2 Voltage/Temperature Measurement Channel

The other two parameters of the Battery for measurement are Voltage and its Temperature. The second channel accepts signals from four independent sources through a Multiplexer as listed below:

- An attenuated battery voltage obtained through appropriate external resistor divider, (or)

- A signal from the external temperature sensor, (or)

- A signal from external reference, (or)

- A signal from the internal temperature sensor.

Apart from this difference in the multiplexing of four input signals, the rest of the data path is identical to the Current measurement channel. RSHH and RSHL are the Current measurement input pins

The Battery Voltage which can go up to 18V is attenuated through a Resistor Divider externally and is applied to the Voltage Channel. For Automotive Battery measurement, the Gain of the PGA should be restricted to 5 and 25. The latency for the first result from the voltage measurement channel is two conversion cycles.

A second option on this measurement channel is to measure Temperature. Internally generated constant current is pumped through the Temperature Sensor with positive temperature coefficient, and, a high- precision resistor. The voltages across the sensor and the resistor form the inputs to the measurement channel one at a time. The difference between the two voltages which is independent of the magnitude of the current is used to determine the temperature accurately. The Voltage across the sensor is applied between the ETS and VSS pins and, the voltage across the high-precision resistor is applied between ETR and VSS. External Temperature measurement involves the acquisition of two signals one after the other using the same constant current source. The latency for the first result from the temperature measurement channel is two conversion cycles.

A third option on the measurement channel is to measure the internal temperature. Hence, one of the three options for measurement of Battery Voltage, External Temperature and, internal temperature may be carried out by selection of appropriate inputs through the internal multiplexer selection.

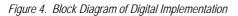

## 7.3 Digital Implementation of Measurement Path

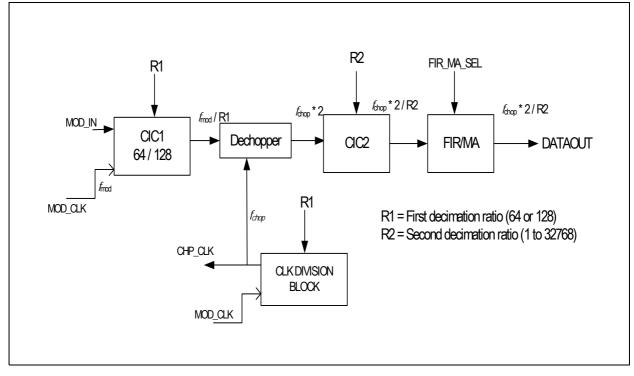

Figure 4 shows the digital implementation of the decimator and filter to process the 1-bit output of the Modulator. This block receives a 1-bit pulse density modulated output (MOD\_IN) from the second order sigma delta modulator along with the oversampling frequency clock (MOD\_CLK). The MOD\_CLK directly goes to a clock division block, which generates chopper clock (CHOP\_CLK). The CHOP\_CLK can be one of 2kHz or 4kHz selected by Register CLK\_REG in Table 33. The MOD\_CLK can be either 1MHz or 2MHz. The Decimation is a two phase process. In the first phase, the R1 down sampling rate can be obtained by selecting either 64 or 128 in Registers DECREG\_R1\_I, DECREG\_R1\_V in Table 33. The 16-bit CIC1 output is dechopped with respect to CHOP\_CLK. The output of Dechopper is passed through the CIC2 filter with a decimation ratio of 1to 32768 in steps of power of 2. This output is then processed through a FIR or Moving Average (MA) filter. FIR Filter is provided to offer matched low pass filter response typically required in lead acid battery sensor systems. MA filter is used to provide averaged output and the number of samples for averaging can be any integer value from 1, 3, 7 or 15.

## 7.4 Modes of Operation

The device operates in four different modes, namely,

- Normal Mode 1 (NOM1),

- Normal Mode 2 (NOM2),

- Standby Mode 1 (SBY1), and,

- Standby Mode 2 (SBY2).

The Normal Modes are full-power modes with the exception that in Normal Mode 2, sampling is normally at a programmed lower frequency and is increased to a higher rate only when a measured input signal level crosses the programmed threshold in the current measurement channel.

The Standby Modes are lower power modes. Sampling is normally at a very low frequency interval. In Standby Mode 2, data sampling can be carried out only when the internal comparator detects the input current to be greater than the programmed threshold and it generates interrupt on the INT pin.

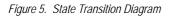

The device enters into the "Stop" state on Power On. This is a state where in the data path is inactive and can be entered into from any of the four Modes. The State transition Diagram involving the state of Stop and the four Modes is illustrated in the Figure 5.

Note:

- 1. Device soft reset can be written in any of the following states STOP, A\_STB, SBM\_ON, SBM\_OFF by writing "0" into D[7] of the RESET \_REG (Address 0X09).

- 2. Measurement path of soft reset should be written in any the states, STOP, SBM\_OFF by writing "0" into D[6] of the RESET\_REG (Address 0X09).

- 3. When soft reset is used for the measurement path or for the device, external clock needs to be disabled if the system clock is external clock in the application.

#### 7.4.1 Normal Mode 1 (NOM1)

On Power-on-reset of the device, AS8510 goes into STOP State.

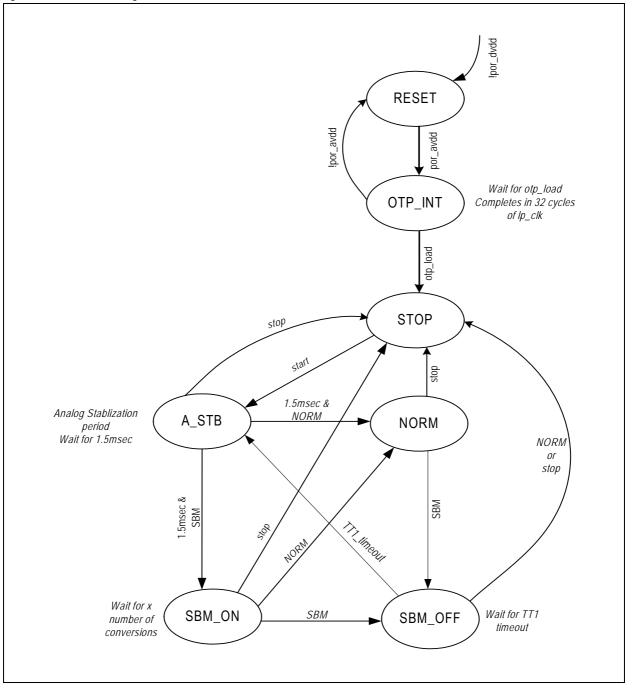

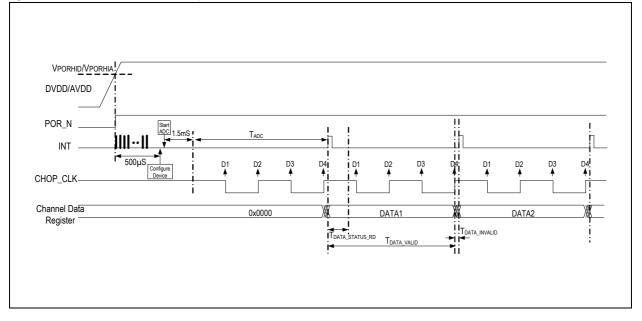

Transition to Normal mode1 (NOM1) occurs when the "START BIT" D0 of Mode Control Register MOD\_CTL\_REG in Table 33 is set to "1" through the serial port SPI. Data Rate of voltage and current channels can be independently programmed and both the channels generate interrupts for every output available from ADC. The interrupt signal is generated on the INT pin. The width of the interrupt pulse is eight cycles of I<sub>p\_clk</sub>. The data is stable up to the next interrupt. If the data rate is different for the two channels, the interrupt rate would follow the higher rate among the two channels. Data update can be known by reading the status register. The functionality is explained in the waveform shown in Figure 6. When the device is configured to NORMAL Mode1 from any mode the configuration should be through the STOP state only.

Figure 6. Normal Mode 1

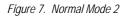

#### 7.4.2 Normal Mode 2 (NOM2)

NOM2 differs from NOM1 in such a way that it allows for a relaxed data rate at a period of  $T_{MC}$  by programming the corresponding register as long as the amplitude of current is less than a programmed threshold  $I_{THC}$ . However, when, the measured input signal exceeds the programmed threshold, the data rate is changed to the rate of NOM1 mode.

Transition to NOM2 occurs when the "START BIT" D0 of Mode Control register MOD\_CTL\_REG in Table 33 is set to 1 and mode control bits to 01 through SPI. In this mode the data rate should be programmed with the time of  $T_{MC}$ . An interrupt signal is generated on INT at the rate of  $T_{MC}$  secs with a pulse width of eight cycles of  $I_{p_clk}$ . The data is stable up to the next interrupt. The data sample is compared against the programmed threshold and when it is exceeded, the data sampling rate is changed to provide data at the data rate of NOM1 mode. However, as soon as the data sample amplitude falls below the programmed threshold, the sampling rate is restored to provide data at the rate of  $T_{MC}$ . The functionality is illustrated in the waveform Figure 7.

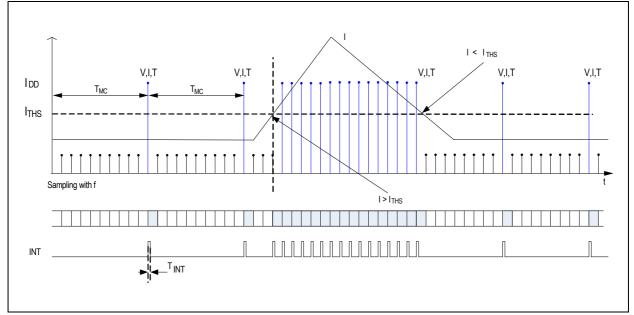

## 7.4.3 Standby Mode1 (SBM1)

The low-power Standby Mode can be entered only through the STOP state. Transition to SBM1 mode occurs when the "START BIT" D0 of Mode Control register MOD\_CTL\_REG in Table 33 is set to "1" and Mode Control Bits to "10" through SPI. In this mode the date rate is programmable with the time of Ta. An interrupt signal is generated on INT at the rate of Ta secs., and with a pulse width of eight cycles of  $I_{p_clk}$ . The data is stable up to the next interrupt. The functionality is illustrated in Figure. During the period of Ta, only one data sample is made available and, during the rest of the period, the device is maintained in STOP state to reduce power consumption. The microcontroller which receives the data on the Interrupt, is also expected to be processing the data for a short time as shown clearly in the Figure 8 to ensure the overall low-power consumption of the data acquisition and processing system.

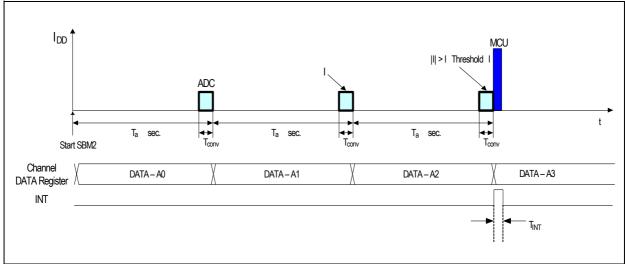

## 7.4.4 Standby Mode2 (SBM2)

Standby Mode 2 is an extension of the Standby Mode1 to achieve even a lower power in the data acquisition system by providing interrupt to the microcontroller only when the data sample exceeds the set current threshold. The Standby Mode can be entered only through the STOP state. Transition to SBM2 mode occurs when the "START BIT" D0 of Mode Control register MOD\_CTL\_REG in Table 33 is set to "1" and Mode Control Bits D7,D6 to "1,1" through SPI. In this mode the date rate is programmable with the time of Ta in the Ta control registers B, C. The data sample is made available and an interrupt signal is generated on INT pin only when the input signal exceeds the threshold set in Current Threshold Registers D,E. It should be noted here that the data is stable for Ta secs. The functionality is illustrated in Figure 9.

## 7.5 Reference-Voltage

Band gap-reference voltage is used for the ADC as a reference and for the generation of the current for external temperature measurement.

## 7.6 Oscillators

A High-speed oscillator (HS) generates the oversampling clock. For internal state machine and Interrupt generation, a low-speed Oscillator (LS) is also available.

## 7.7 Power-On Reset

The AS8510 has PORs, APOR and DPOR on analog and digital power supplies respectively. On PORs of both supplies, initialization sequence happens and the system status is shown in state diagram (see Figure 5).

As shown in the state diagram, the system is in RESET state until DPOR output goes to logic HIGH and subsequently until APOR output goes to logic HIGH. Once analog power supply is available, the system goes into OTP\_INT state and loads the default values into the control and data registers and goes into STOP state. If analog POR, APOR goes low at any time, the system goes into RESET state. In the STOP state, the AS8510 can be programmed and by giving start command it starts working following the state machine.

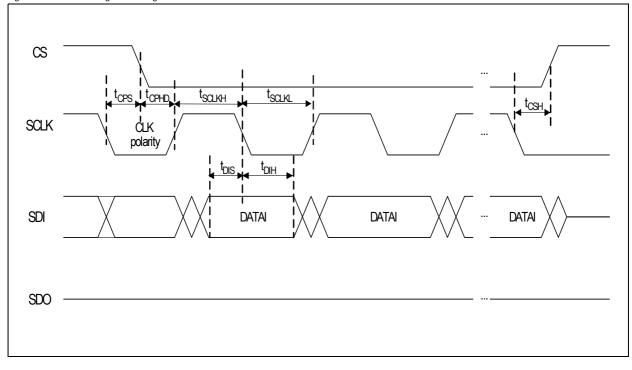

# 7.8 4-Wire Serial Port Interface

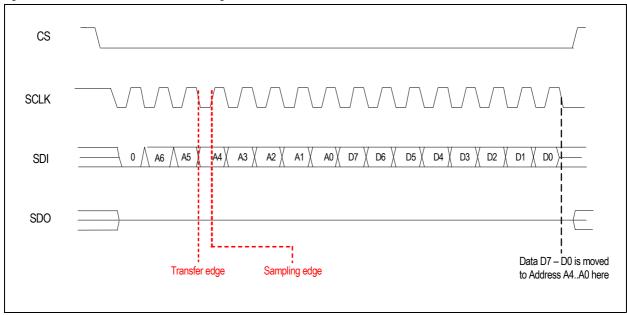

The SPI interface is used as interface between the AS8510 and an external micro-controller to configure the device and access the status information. The micro-controller begins communication with the SPI which is configured as a slave. The SPI protocol is simple and the length of each frame is an integer multiple of bytes except when a transmission is started. Each frame has 1 command bit, 7 address/configuration bits, and one or more data bytes. The edge of CS and the level of SCLK during the start of a SPI transaction, determine the edge on which the data is transferred from the SPI and the edge on which the data is sampled by the slave. Table 29 describes the setting of the transfer and sampling edges of SCLK. Figure 10 shows the falling edge and rising edge for data transfer and data sampling respectively, when SCLK is HIGH on the falling edge of CS.

| Table 29. | CS and SCLK |

|-----------|-------------|

| 10010 27. |             |

| CS   | SCLK | Description                                                                                |

|------|------|--------------------------------------------------------------------------------------------|

| FALL | LOW  | Serial data transferred on rising edge of SPI clock. Sampled at falling edge of SPI clock. |

| FALL | HIGH | Serial data transferred on falling edge of SPI clock. Sampled at rising edge of SPI clock. |

| ANY  | ANY  | Serial data transfer edge is unchanged.                                                    |

Figure 10. Protocol for Serial Data Write with Length = 1

## 7.8.1 SPI Frame

A frame is formed by a first byte for command and address/configuration and a following bit stream that can be formed by an integer number of bytes. Command is coded on the 1 first bit, while address is given on LSB 7 bits (see Table 30).

Table 30. Command Bits

| Command Bits | Register Address or Transmission Configuration |    |    |    |    |    |    |  |

|--------------|------------------------------------------------|----|----|----|----|----|----|--|

| C0           | A6                                             | A5 | A4 | A3 | A2 | A1 | A0 |  |

Table 31. Command Bits

| C0 | Command | <a6:a0></a6:a0> | Description                                     |

|----|---------|-----------------|-------------------------------------------------|

| 0  | WRITE   | ADDRESS         | Writes data byte on the given starting address. |

| 1  | READ    | ADDRESS         | Read data byte from the given starting address. |

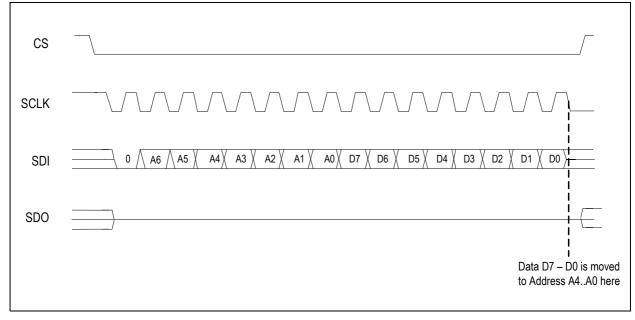

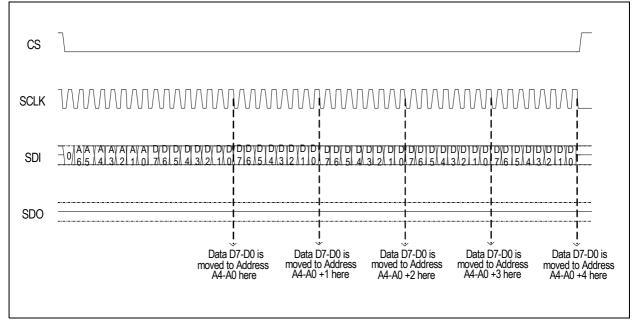

If the command is read or write, one or more bytes follow. When the micro-controller sends more bytes (keeping CS LOW and SCLK toggling), the SPI interface increments the address of the previous data byte and writes/reads data to/from consecutive addresses.

#### 7.8.2 Write Command

For write command, C0=0. After the command code C0 is transferred, the address of register to be written is provided from MSB to LSB. Subsequently one or more data bytes can be transferred from MSB to LSB. For each data byte following the first one, used address is the incremented value of the previously written address. Each bit of the frame has to be driven by the SPI master on the SPI clock transfer edge. The SPI slave samples it on the next clock edge. These edges are determined by the level of SCLK as shown in Table 29. Figure 11 and Figure 12 are examples of write command without and with address self-increment.

Figure 11. Protocol for Serial Data Write with Length = 1

Figure 12. Protocol for Serial Data Write with Length = 4

## 7.8.3 Read Command

For Read command C0=1. After the command code C0, the address of register to be read is provided from MSB to LSB. Then one or more data bytes can be transferred from the SPI slave to the master, always from MSB to LSB. To transfer more bytes from consecutive addresses, SPI master keeps CS signal LOW and SPI clock active as long as it desires to read data from the slave. Each bit of the command and address of the frame is to be driven by the SPI master on the SPI clock transfer edge where SPI slave samples it on the next SPI clock edge.

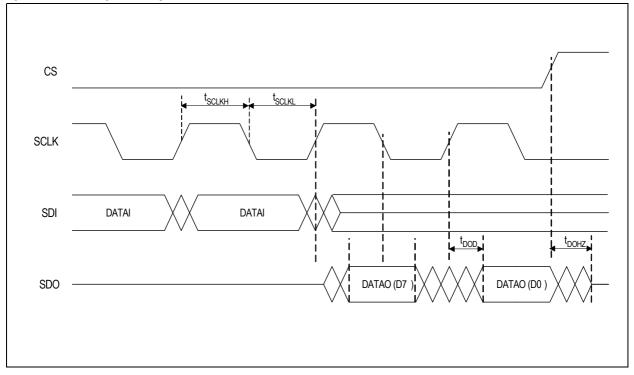

Each bit of the data section of the frame is driven by the SPI slave on the SPI clock transfer edge and SPI master samples it on the next SPI clock edge. These edges are determined as per Table 29 and examples of read command without and with address self-increment.

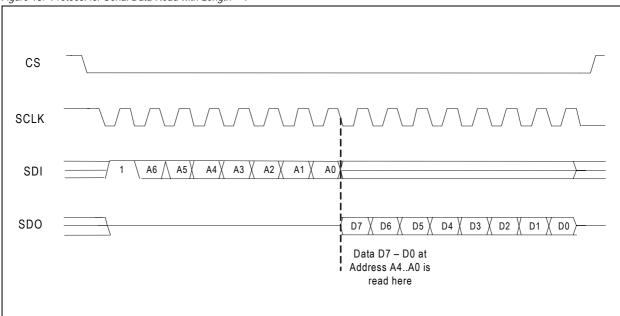

Figure 13. Protocol for Serial Data Read with Length = 1

Figure 14. Protocol for Serial Data Read with Length = 4

| ::: |     |     |

|-----|-----|-----|

| ::: | 000 |     |

| *** |     | *** |

|     |     |     |

|     |     | ::: |

|     |     |     |

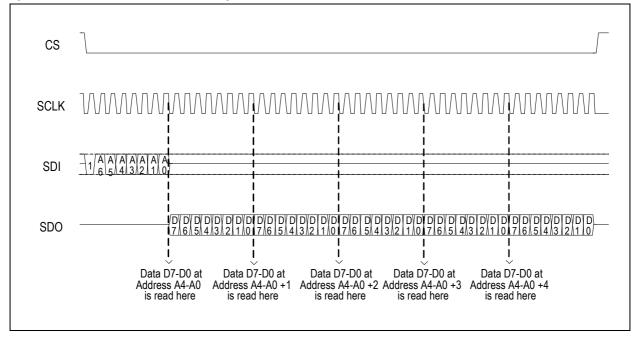

## 7.8.4 Timing

In the following timing waveforms and parameters are exposed.

Figure 15. Write Timing for Writing

Figure 16. Read Timing for Reading

## 7.8.5 SPI Interface Timing

Table 32. SPI Interface Timing

| Symbol             | Parameter                              | Conditions                                         | Min | Тур | Max | Units |

|--------------------|----------------------------------------|----------------------------------------------------|-----|-----|-----|-------|

| General            | •                                      |                                                    |     |     |     |       |

| BR <sub>SPI</sub>  | Bit rate                               |                                                    |     |     | 1   | Mbps  |

| T <sub>SCLKH</sub> | Clock high time                        |                                                    | 400 |     |     | ns    |

| T <sub>SCLKL</sub> | Clock low time                         |                                                    | 400 |     |     | ns    |

| Write timing       |                                        |                                                    |     |     |     |       |

| t <sub>DIS</sub>   | Data in setup time                     |                                                    | 20  |     |     | ns    |

| t <sub>DIH</sub>   | Data in hold time                      |                                                    | 20  |     |     | ns    |

| T <sub>CSH</sub>   | CS hold time                           |                                                    | 20  |     |     | ns    |

| Read timing        |                                        |                                                    |     |     |     |       |

| t <sub>DOD</sub>   | Data out delay                         |                                                    |     |     | 80  | ns    |

| t <sub>DOHZ</sub>  | Data out to high impedance delay       | Time for the SPI to release the SDO bus            |     |     | 80  | ns    |

| Timing param       | eters when entering 4-Wire SPI mode (f | or determination of CLK polarity)                  |     |     |     |       |

| t <sub>CPS</sub>   | Clock setup time<br>(CLK polarity)     | Setup time of SCLK with respect to CS falling edge | 20  |     |     | ns    |

| tсрнр              | Clock hold time<br>(CLK polarity)      | Hold time of SCLK with respect to CS falling edge  | 20  |     |     | ns    |

## 7.9 Control Register

This section describes the control registers used in AS8510. Registers can be broadly classified into the following categories.

- Data access registers

- Status Registers

- Digital signal path control registers

- Digital Control registers

- Analog Control Registers

| Addr in<br>HEX        | Register Name                              | POR Value | R/W  | 8-bit Control / Status Data |                                                |  |  |  |

|-----------------------|--------------------------------------------|-----------|------|-----------------------------|------------------------------------------------|--|--|--|

| Data Access Registers |                                            |           |      |                             |                                                |  |  |  |

| 00                    | DREG_I1<br>(ADC Data Register for Current) | 0000_0000 | R    | D[7:0]                      | Denotes the Current ADC MSB Byte (ADC_I[15:8]) |  |  |  |

| 01                    | DREG_I2<br>(ADC Data Register for Current) | 0000_0000 | R    | D[7:0]                      | Denotes the Current ADC LSB Byte (ADC_I[7:0])  |  |  |  |

| 02                    | DREG_V1<br>(ADC Data Register for Voltage) | 0000_0000 | R    | D[7:0]                      | Denotes the Voltage ADC MSB Byte (ADC_V[15:8]) |  |  |  |

| 03                    | DREG_V2<br>(ADC Data Register for Voltage) | 0000_0000 | R    | D[7:0]                      | Denotes the Voltage ADC LSB Byte (ADC_V[7:0])  |  |  |  |

| Status Regi           | sters                                      |           |      |                             |                                                |  |  |  |

|                       |                                            |           |      | D[7]                        | NOM1/NOM2 Data Ready                           |  |  |  |

|                       |                                            |           |      | D[6]                        | NOM2 Threshold Crossover                       |  |  |  |

|                       |                                            |           |      | D[5]                        | SBM1 Data Ready                                |  |  |  |

| 04                    |                                            | 0000 0000 | R    | D[4]                        | SBM2 Threshold Crossover                       |  |  |  |

| 04                    | 04 STATUS_REG 0000_0000 R                  | ĸ         | D[3] | APOR status                 |                                                |  |  |  |