128K x 36, 256K x 18 3.3V Synchronous ZBT SRAMs 3.3V I/O, Burst Counter Pipelined Outputs

AS8C403601-QC166N AS8C401801-QC166N

#### **Features**

- 128K x 36, 256K x 18 memory configurations

- Supports high performance system speed 166 MHz (x18)

(3.2 ns Clock-to-Data Access)

- Supports high performance system speed 166 MHz (x36)

(3.5 ns Clock-to-Data Access)

- ◆ ZBT<sup>™</sup> Feature No dead cycles between write and read cycles

- Internally synchronized output buffer enable eliminates the need to control OE

- ◆ Single R/W (READ/WRITE) control pin

- Positive clock-edge triggered address, data, and control signal registers for fully pipelined applications

- 4-word burst capability (interleaved or linear)

- ◆ Individual byte write (BW1 BW4) control (May tie active)

- Three chip enables for simple depth expansion

- ◆ 3.3V power supply (±5%), 3.3V I/O Supply (VDDQ)

- Optional- Boundary Scan JTAG Interface (IEEE 1149.1 compliant)

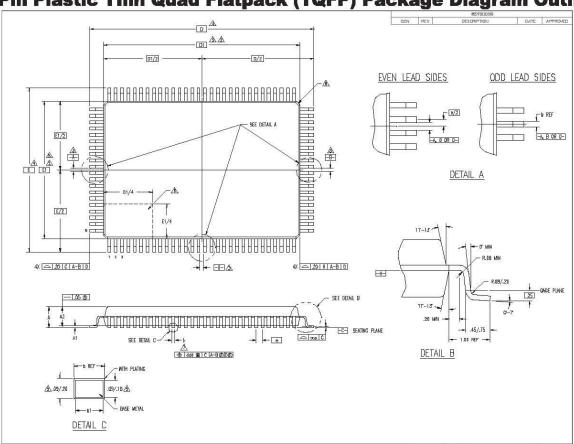

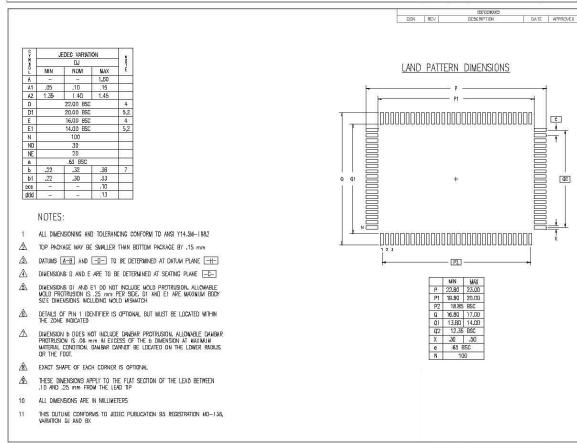

- Packaged in a JEDEC standard 100-pin plastic thin quad flatpack (TQFP)

#### **Description**

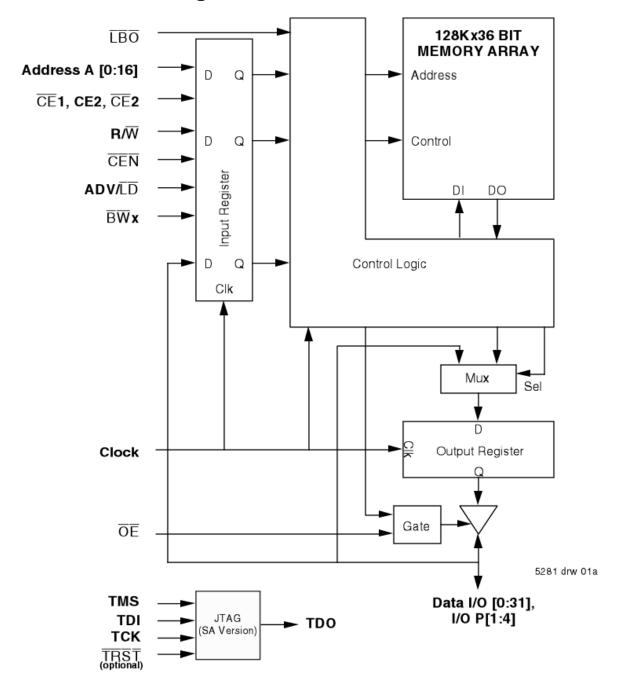

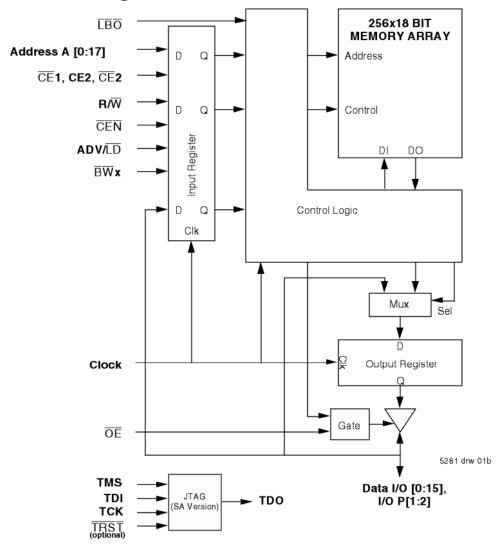

The 403601/401801 are 3.3V high-speed 4,718,592-bit (4.5 Megabit) synchronous SRAMS. They are designed to eliminate dead bus cycles when turning the bus around between reads and writes, or writes and reads. Thus, they have been given the name  $ZBT^{TM}$ , or Zero Bus Turnaround.

Address and control signals are applied to the SRAM during one clock cycle, and two cycles later the associated data cycle occurs, be it read or write.

The 403601/401801 contain data I/O, address and control signal registers. Output enable is the only asynchronous signal and can be used to disable the outputs at any given time.

A Clock Enable  $(\overline{\text{CEN}})$  pin allows operation of the 403601/401801 to be suspended as long as necessary. All synchronous inputs are ignored when  $(\overline{\text{CEN}})$  is high and the internal device registers will hold their previous values.

There are three chip enable pins ( $\overline{CE}1$ , CE2,  $\overline{CE}2$ ) that allow the user to deselect the device when desired. If any one of these three are not asserted when ADV/ $\overline{LD}$  is low, no new memory operation can be initiated. However, any pending data transfers (reads or writes) will be completed. The data bus will tri-state two cycles after chip is deselected or a write is initiated.

### **Pin Description Summary**

| A0-A17                                                                        | Address Inputs                           | Input  | Synchronous  |

|-------------------------------------------------------------------------------|------------------------------------------|--------|--------------|

| $\overline{CE}_1$ , CE <sub>2</sub> , $\overline{CE}_2$                       | Chip Enables                             | Input  | Synchronous  |

| ŌĒ                                                                            | Output Enable                            | Input  | Asynchronous |

| R/W                                                                           | Read/Write Signal                        | Input  | Synchronous  |

| CEN                                                                           | Clock Enable                             | Input  | Synchronous  |

| $\overline{BW}_1$ , $\overline{BW}_2$ , $\overline{BW}_3$ , $\overline{BW}_4$ | Individual Byte Write Selects            | Input  | Synchronous  |

| CLK                                                                           | Clock                                    | Input  | N/A          |

| ADV/LD                                                                        | Advance burst address / Load new address | Input  | Synchronous  |

| ĪBO                                                                           | Linear / Interleaved Burst Order         | Input  | Static       |

| TMS                                                                           | Test Mode Select                         | Input  | Synchronous  |

| TDI                                                                           | Test Data Input                          | Input  | Synchronous  |

| TCK                                                                           | Test Clock                               | Input  | N/A          |

| TDO                                                                           | Test Data Output                         | Output | Synchronous  |

| TRST                                                                          | JTAG Reset (Optional)                    | Input  | Asynchronous |

| ZZ                                                                            | Sleep Mode                               | Input  | Synchronous  |

| I/O0-I/O31, I/OP1-I/OP4                                                       | Data Input / Output                      | I/O    | Synchronous  |

| VDD, VDDQ                                                                     | Core Power, I/O Power                    | Supply | Static       |

| Vss                                                                           | Ground                                   | Supply | Static       |

#### **Description continued**

The 403601/401801 has an on-chip burst counter. In the burst mode, the 403601/401801 can provide four cycles of data for a single address presented to the SRAM. The order of the burst sequence is defined by the  $\overline{LBO}$  input pin. The  $\overline{LBO}$  pin selects between linear and interleaved burst sequence. The  $\overline{ADV/LD}$  signal is used to load a new

external address (ADV/ $\overline{LD}$  = LOW) or increment the internal burst counter (ADV/ $\overline{LD}$  = HIGH).

The 403601/401801 SRAMs utilize Alliance's latest high-performance CMOS process and are packaged in a JEDEC standard 14mm x 20mm 100-pin thin plastic quad flatpack (TQFP)

5281 tol 02

#### Pin Definition<sup>(1)</sup>

| Symbol                | Pin Function                     | 1/0 | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|----------------------------------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A17                | Address Inputs                   | I   | N/A    | Synchronous Address inputs. The address register is triggered by a combination of the rising edge of CLK, ADV/LD low, CEN low, and true chip enables.                                                                                                                                                                                                                                                                                                                                                       |

| ADV/LD                | Advance / Load                   | I   | N/A    | ADV/\(\overline{\D}\) is a synchronous input that is used to load the internal registers with new address and control when it is sampled low at the rising edge of clock with the chip selected. When ADV/\(\overline{\D}\) is low with the chip deselected, any burst in progress is terminated. When ADV/\(\overline{\D}\) is sampled high then the internal burst counter is advanced for any burst that was in progress. The external addresses are ignored when ADV/\(\overline{\D}\) is sampled high. |

| R/W                   | Read / Write                     | Ĩ   | N/A    | R/W signal is a synchronous input that identifies whether the current load cycle initiated is a Read or Write access to the memory array. The data bus activity for the current cycle takes place two clock cycles later.                                                                                                                                                                                                                                                                                   |

| CEN                   | Clock Enable                     | Ĩ   | LOW    | Synchronous Clock Enable Input. When $\overline{\text{CEN}}$ is sampled high, all other synchronous inputs, including clock are ignored and outputs remain unchanged. The effect of $\overline{\text{CEN}}$ sampled high on the device outputs is as if the low to high clock transition did not occur. For normal operation, $\overline{\text{CEN}}$ must be sampled low at rising edge of clock.                                                                                                          |

| BW1-BW4               | Individual Byte<br>Write Enables | ı   | LOW    | Synchronous byte write enables. Each 9-bit byte has its own active low byte write enable. On load write cycles (When R/W and ADV/LD are sampled low) the appropriate byte write signal (BW-BW4) must be valid. The byte write signal must also be valid on each cycle of a burst write. Byte Write signals are ignored when R/W is sampled high. The appropriate byte(s) of data are written into the device two cycles later. BW1-BW4 can all be tied low if always doing write to the entire 36-bit word. |

| CE1, CE2              | Chip Enables                     | I   | LOW    | Synchronous active low chip enable. CE₁ and CE₂ are used with CE₂ to enable the 403601/401801.(CE₁ or CE₂ sampled high or CE₂ sampled low) and ADV/ID low at the rising edge of clock, initiates a deselect cycle. The ZBT™ has a two cycle deselect, i.e., the data bus will tri-state two clock cycles after deselect is initiated.                                                                                                                                                                       |

| CE2                   | Chip Enable                      | Ţ   | HIGH   | Synchronous active high chip enable. CE2 is used with CE1 and CE2 to enable the chip. CE2 has inverted polarity but otherwise identical to CE1 and CE2.                                                                                                                                                                                                                                                                                                                                                     |

| CLK                   | Clock                            | Ï   | N/A    | This is the clock input to the 403601/401801. Except for $\overline{\text{OE}}$ , all timing references for the device are made with respect to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                     |

| VO0-VO31<br>VOP1-VOP4 | Data Input/Output                | VO  | N/A    | Synchronous data input/output (I/O) pins. Both the data input path and data output path are registered and triggered by the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                             |

| <u>IBO</u>            | Linear Burst Order               | Ĩ   | LOW    | Burst order selection input. When $\overline{\text{LBO}}$ is high the Interleaved burst sequence is selected. When $\overline{\text{LBO}}$ is low the Linear burst sequence is selected. $\overline{\text{LBO}}$ is a static input and it must not change during device operation.                                                                                                                                                                                                                          |

| Œ                     | Output Enable                    | Į.  | LOW    | Asynchronous output enable. $\overline{OE}$ must be low to read data from the 403601/1801. When $\overline{OE}$ is high the I/O pins are in a high-impedance state. $\overline{OE}$ does not need to be actively controlled for read and write cycles. In normal operation, $\overline{OE}$ can be tied low.                                                                                                                                                                                                |

| TMS                   | Test Mode Select                 | Ī   | N/A    | Gives input command for TAP controller. Sampled on rising edge of TDK. This pin has an internal pullup.                                                                                                                                                                                                                                                                                                                                                                                                     |

| ТОІ                   | Test Data Input                  | Ĩ   | N/A    | Serial input of registers placed between TDI and TDO. Sampled on rising edge of TCK. This pin has an internal pullup.                                                                                                                                                                                                                                                                                                                                                                                       |

| тск                   | Test Clock                       | Ĭ   | N/A    | Clock input of TAP controller. Each TAP event is clocked. Test inputs are captured on rising edge of TCK, while test outputs are driven from the falling edge of TCK. This pin has an internal pullup.                                                                                                                                                                                                                                                                                                      |

| тро                   | Test Data Output                 | 0   | N/A    | Serial output of registers placed between TDI and TDO. This output is active depending on the state of the TAP controller.                                                                                                                                                                                                                                                                                                                                                                                  |

| TRST                  | JTAG Reset<br>(Optional)         | I   | LOW    | Optional Asynchronous JTAG reset. Can be used to reset the TAP controller, but not required. JTAG reset occurs automatically at power up and also resets using TMS and TCK per IEEE 1149.1. If not used TRST can be left floating. This pin has an internal pullup. Only available in BGA package.                                                                                                                                                                                                          |

| zz                    | Sleep Mode                       | Ĩ   | HIGH   | Synchronous sleep mode input. ZZ HIGH will gate the CLK internally and power down the 403601/1801 to its lowest power consumption level. Data retention is guaranteed in Sleep Mode. This pin has an internal pulldown.                                                                                                                                                                                                                                                                                     |

| Voo                   | Power Supply                     | NA  | N/A    | 3.3V core power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VDDQ                  | Power Supply                     | NA  | N/A    | 3.3V VO Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Vss                   | Ground                           | NΑ  | N/A    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

NOTE:

#### **Functional Block Diagram**

#### **Functional Block Diagram**

## **Recommended DC Operating Conditions**

| Symbol | Parameter                   | Min.                | Тур. | Max.                     | Unit |  |  |  |  |  |  |  |

|--------|-----------------------------|---------------------|------|--------------------------|------|--|--|--|--|--|--|--|

| VDD    | Core Supply Voltage         | 3.135               | 3.3  | 3.465                    | ٧    |  |  |  |  |  |  |  |

| VDDQ   | I/O Supply Voltage          | 3.135               | 3.3  | 3.465                    | ٧    |  |  |  |  |  |  |  |

| Vss    | Supply Voltage              | 0                   | 0    | 0                        | ٧    |  |  |  |  |  |  |  |

| Vн     | Input High Voltage - Inputs | 2.0                 | _    | VDD +0.3                 | ٧    |  |  |  |  |  |  |  |

| Vн     | Input High Voltage - I/O    | 2.0                 | _    | VDDQ +0.3 <sup>(2)</sup> | ٧    |  |  |  |  |  |  |  |

| VIL    | Input Low Voltage           | -0.3 <sup>(1)</sup> |      | 0.8                      | ٧    |  |  |  |  |  |  |  |

NOTES:

- 1. VIL (min.) = -1.0V for pulse width less than tcyc/2, once per cycle.

- 2. VIH (max.) = +6.0V for pulse width less than tcyc/2, once per cycle.

#### Recommended Operating Temperature and Supply Voltage

| Grade      | Temperature <sup>(1)</sup> | Vss | V <sub>DD</sub> | VDDQ    |

|------------|----------------------------|-----|-----------------|---------|

| Commercial | 0°C to +70°C               | 0V  | 3.3V±5%         | 3.3V±5% |

| Industrial | -40°C to +85°C             | 0V  | 3.3V±5%         | 3.3V±5% |

NOTES:

5281 tbl 05

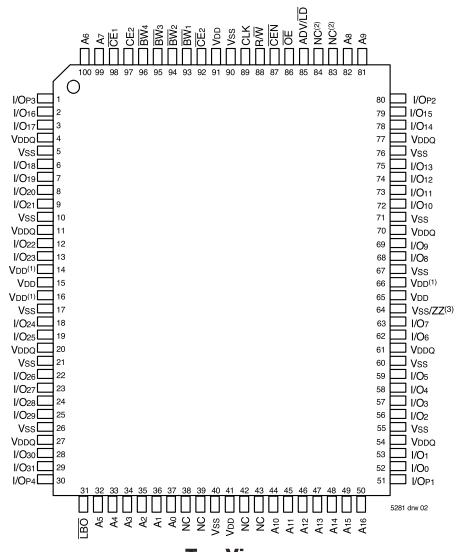

#### Pin Configuration - 128K x 36

# Top View 100 TQFP

- 1. Pins 14, 16 and 66 do not have to be connected directly to VDD as long as the input voltage is  $\geq$  VIH.

- 2. Pins 83 and 84 are reserved for future 8M and 16M respectively.

- 3. Pin 64 does not have to be connected directly to Vss as long as the input voltage is ≤ VIL; on the latest die revision this pin supports ZZ (sleep mode).

<sup>1.</sup> TA is the "instant on" case temperature.

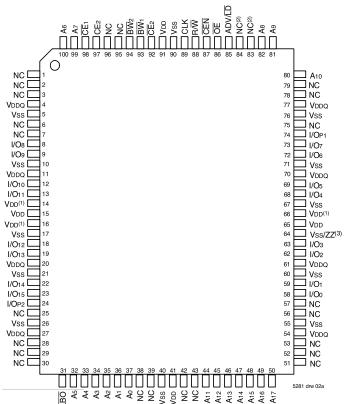

#### Pin Configuration - 256K x 18

## Top View 100 TQFP

#### NOTES:

- Pins 14, 16 and 66 do not have to be connected directly to VDD as long as the input voltage is ≥ VIH.

- 2. Pins 83 and 84 are reserved for future 8M and 16M respectively.

- Pin 64 does not have to be connected directly to Vss as long as the input voltage is ≤ Vıι.; on the latest die revision this pin supports ZZ (sleep mode).

### Absolute Maximum Ratings (1)

|                        | 110 11100211111101111                | Matings                           |      |  |  |  |

|------------------------|--------------------------------------|-----------------------------------|------|--|--|--|

| Symbol                 | Rating                               | Commercial &<br>Industrial Values | Unit |  |  |  |

| VTERM <sup>(2)</sup>   | Terminal Voltage with Respect to GND | -0.5 to +4.6                      | V    |  |  |  |

| VTERM <sup>(3,6)</sup> | Terminal Voltage with Respect to GND | -0.5 to VDD                       | V    |  |  |  |

| VTERM <sup>(4,6)</sup> | Terminal Voltage with Respect to GND | -0.5 to V <sub>DD</sub> +0.5      | V    |  |  |  |

| VTERM <sup>(5,6)</sup> | Terminal Voltage with Respect to GND | -0.5 to VDDQ +0.5                 | V    |  |  |  |

| TA <sup>(7)</sup>      | Commercial Operating Temperature     | -0 to +70                         | °C   |  |  |  |

|                        | Industrial Operating Temperature     | -40 to +85                        | °C   |  |  |  |

| TBIAS                  | Temperature<br>Under Bias            | -55 to +125                       | °C   |  |  |  |

| Тѕтѕ                   | Storage<br>Temperature               | -55 to +125                       | °C   |  |  |  |

| Рт                     | Power Dissipation                    | 2.0                               | W    |  |  |  |

| Іоит                   | DC Output Current                    | 50                                | mA   |  |  |  |

#### NOTES:

5281 tbl 06

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may

cause permanent damage to the device. This is a stress rating only and functional

operation of the device at these or any other conditions above those indicated in the

operational sections of this specification is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect reliability.

- 2. VDD terminals only.

- VDDQ terminals only.

- 4. Input terminals only.

- 5. I/O terminals only.

- This is a steady-state DC parameter that applies after the power supply has

reached its nominal operating value. Power sequencing is not necessary; however,

the voltage on any input or I/O pin cannot exceed VDDQ during power supply ramp

up.

- 7. TA is the "instant on" case temperature.

## **100 Pin TQFP Capacitance**<sup>(1)</sup> (TA = +25° C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 3dV  | 5    | pF   |

| Cı/o   | I/O Capacitance          | Vout = 3dV | 7    | pF   |

5281 tbl 07

#### NOTE:

1. This parameter is guaranteed by device characterization, but not production tested.

### Synchronous Truth Table (1)

| CEN | R/W | Chip <sup>(5)</sup><br>Enable | ADV/LD | B₩x   | ADDRESS<br>USED | PREVIOUS CYCLE              | CURRENT CYCLE                                         | I/O<br>(2 cycles later) |

|-----|-----|-------------------------------|--------|-------|-----------------|-----------------------------|-------------------------------------------------------|-------------------------|

| L   | L   | Select                        | L      | Valid | External        | X                           | LOAD WRITE                                            | D <sup>(7)</sup>        |

| L   | Н   | Select                        | L      | Х     | External        | X                           | LOAD READ                                             | Q <sup>(7)</sup>        |

| L   | Х   | Х                             | Н      | Valid | Internal        | LOAD WRITE /<br>BURST WRITE | BURST WRITE<br>(Advance burst counter) <sup>(2)</sup> | D <sup>(7)</sup>        |

| L   | Х   | Х                             | Н      | Х     | Internal        | LOAD READ /<br>BURST READ   | BURST READ<br>(Advance burst counter) <sup>(2)</sup>  | Q <sup>(7)</sup>        |

| L   | Х   | Deselect                      | L      | Х     | Х               | X                           | DESELECT or STOP <sup>(3)</sup>                       | HiZ                     |

| L   | Х   | Х                             | Н      | Х     | Х               | DESELECT / NOOP             | NOOP                                                  | HiZ                     |

| Н   | Х   | Х                             | Х      | Χ     | Х               | Х                           | SUSPEND <sup>(4)</sup>                                | Previous Value          |

#### NOTES:

5281 tbl 08

- 1. L = VIL, H = VIH, X = Don't Care.

- 2. When ADV/\(\overline{LD}\) signal is sampled high, the internal burst counter is incremented. The R\(\overline{W}\) signal is ignored when the counter is advanced. Therefore the nature of the burst cycle (Read or Write) is determined by the status of the R\(\overline{W}\) signal when the first address is loaded at the beginning of the burst cycle.

- 3. Deselect cycle is initiated when either (CE1, or CE2 is sampled high or CE2 is sampled low) and ADV/LD is sampled low at rising edge of clock. The data bus will tri-state two cycles after deselect is initiated.

- 4. When CEN is sampled high at the rising edge of clock, that clock edge is blocked from propagating through the part. The state of all the internal registers and the I/Os remains unchanged.

- 5. To select the chip requires  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$ ,  $\overline{CE}_2 = H$  on these chip enables. Chip is deselected if any one of the chip enables is false.

- 6. Device Outputs are ensured to be in High-Z after the first rising edge of clock upon power-up.

- 7. Q Data read from the device, D data written to the device.

### Partial Truth Table for Writes (1)

| OPERATION                                                   | R/W | BW₁ | BW <sub>2</sub> | <b>BW</b> 3 <sup>(3)</sup> | BW <sub>4</sub> <sup>(3)</sup> |

|-------------------------------------------------------------|-----|-----|-----------------|----------------------------|--------------------------------|

| READ                                                        | H   | Х   | Х               | Х                          | Х                              |

| WRITE ALL BYTES                                             | L   | L   | L               | L                          | L                              |

| WRITE BYTE 1 (I/O[0:7], I/OP1) <sup>(2)</sup>               | L   | L   | Н               | Н                          | Н                              |

| WRITE BYTE 2 (I/O[8:15], I/O <sub>P2</sub> ) <sup>(2)</sup> | L   | Н   | L               | Н                          | Н                              |

| WRITE BYTE 3 (I/O[16:23], I/OP3)(2.3)                       | L   | Н   | Н               | L                          | Н                              |

| WRITE BYTE 4 (I/O[24:31], I/OP4) <sup>(2,3)</sup>           | L   | Н   | Н               | Н                          | L                              |

| NO WRITE                                                    | L   | Н   | Н               | Н                          | Н                              |

- NOTES:

- 1.  $L = V_{IL}$ ,  $H = V_{IH}$ , X = Don't Care.

- 2. Multiple bytes may be selected during the same cycle.

- 3. N/A for X18 configuration.

### Interleaved Burst Sequence Table (LBO=VDD)

|                               | Sequ | Sequence 1 |    | Sequence 2 |    | Sequence 3 |    | Sequence 4 |  |

|-------------------------------|------|------------|----|------------|----|------------|----|------------|--|

|                               | A1   | A0         | A1 | A0         | A1 | Α0         | A1 | Α0         |  |

| First Address                 | 0    | 0          | 0  | 1          | 1  | 0          | 1  | 1          |  |

| Second Address                | 0    | 1          | 0  | 0          | 1  | 1          | 1  | 0          |  |

| Third Address                 | 1    | 0          | 1  | 1          | 0  | 0          | 0  | 1          |  |

| Fourth Address <sup>(1)</sup> | 1    | 1          | 1  | 0          | 0  | 1          | 0  | 0          |  |

#### NOTE:

1. Upon completion of the Burst sequence the counter wraps around to its initial state and continues counting.

5281 tbl 10

### **Linear Burst Sequence Table (LBO=Vss)**

|                               | Seque | Sequence 1 |    | Sequence 2 |    | Sequence 3 |    | Sequence 4 |  |

|-------------------------------|-------|------------|----|------------|----|------------|----|------------|--|

|                               | A1    | A0         | A1 | A0         | A1 | A0         | A1 | A0         |  |

| First Address                 | 0     | 0          | 0  | 1          | 1  | 0          | 1  | 1          |  |

| Second Address                | 0     | 1          | 1  | 0          | 1  | 1          | 0  | 0          |  |

| Third Address                 | 1     | 0          | 1  | 1          | 0  | 0          | 0  | 1          |  |

| Fourth Address <sup>(1)</sup> | 1     | 1          | 0  | 0          | 0  | 1          | 1  | 0          |  |

NOTE:

5281 tbl 11

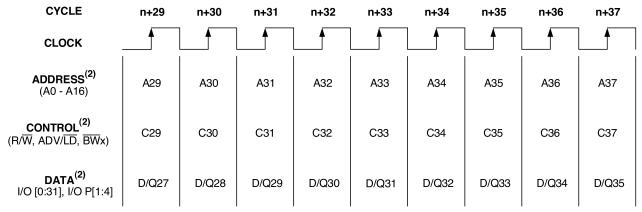

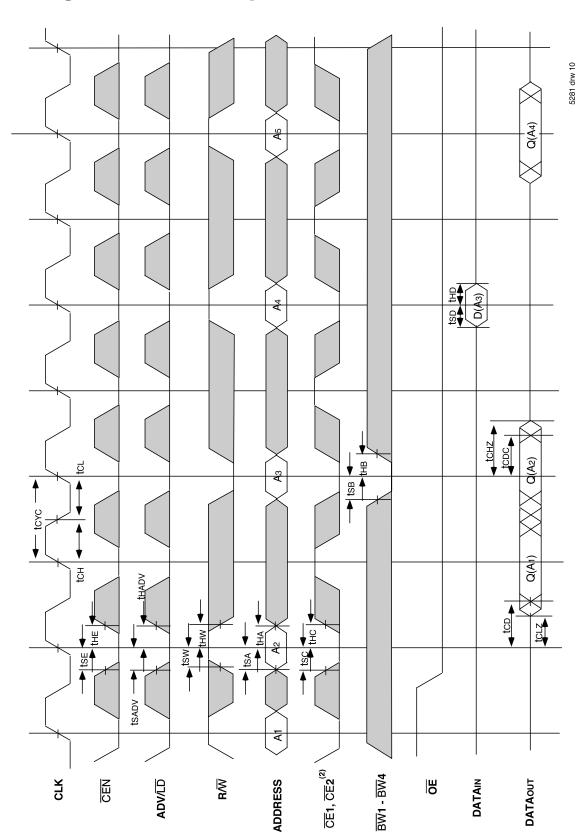

### Functional Timing Diagram (1)

5281 drw 03

#### NOTES:

- 1. This assumes  $\overline{CEN}$ ,  $\overline{CE}_1$ ,  $\overline{CE}_2$ ,  $\overline{CE}_2$  are all true.

- 2. All Address, Control and Data\_In are only required to meet set-up and hold time with respect to the rising edge of clock. Data\_Out is valid after a clock-to-data delay from the rising edge of clock.

<sup>1.</sup> Upon completion of the Burst sequence the counter wraps around to its initial state and continues counting.

## Device Operation - Showing Mixed Load, Burst, Deselect and NOOP Cycles $^{(2)}$

| Cycle | Address        | R/W | ADV/LD | ŒE <sup>(1)</sup> | CEN | B₩x | ŌĒ | I/O            | Comments         |

|-------|----------------|-----|--------|-------------------|-----|-----|----|----------------|------------------|

| n     | <b>A</b> 0     | Н   | L      | L                 | L   | Х   | Х  | Х              | Load read        |

| n+1   | Х              | Х   | Ħ      | Х                 | L   | Х   | Х  | Х              | Burst read       |

| n+2   | <b>A</b> 1     | Н   | L      | L                 | L   | Х   | L  | Q <sub>0</sub> | Load read        |

| n+3   | X              | Х   | L      | Η                 | ٦   | Х   | L  | Q0+1           | Deselect or STOP |

| n+4   | Х              | Х   | Ι      | Х                 | ١   | Х   | L  | Q1             | NOOP             |

| n+5   | <b>A</b> 2     | Н   | L      | L                 | L   | Х   | Х  | Z              | Load read        |

| n+6   | Х              | Χ   | Н      | Χ                 | L   | Х   | Х  | Z              | Burst read       |

| n+7   | Х              | Х   | L      | Η                 | L   | Х   | L  | Q2             | Deselect or STOP |

| n+8   | Аз             | L   | L      | L                 | L   | L   | L  | Q2+1           | Load write       |

| n+9   | Х              | Х   | H      | Χ                 | L   | L   | Х  | Z              | Burst write      |

| n+10  | A4             | L   | L      | L                 | L   | L   | Х  | D3             | Load write       |

| n+11  | Х              | Х   | L      | Η                 | L   | Х   | Х  | D3+1           | Deselect or STOP |

| n+12  | Х              | Х   | Н      | Χ                 | L   | Х   | Х  | D4             | NOOP             |

| n+13  | <b>A</b> 5     | L   | L      | L                 | L   | L   | Х  | Z              | Load write       |

| n+14  | A <sub>6</sub> | Η   | L      | L                 | L   | Х   | Х  | Z              | Load read        |

| n+15  | <b>A</b> 7     | L   | L      | L                 | ┙   | L   | Х  | D5             | Load write       |

| n+16  | Х              | Х   | Ι      | Χ                 | ┙   | L   | L  | Q6             | Burst write      |

| n+17  | <b>A</b> 8     | Н   | L      | L                 | L   | Х   | Х  | D7             | Load read        |

| n+18  | X              | Х   | Н      | Х                 | L   | Х   | Х  | D7+1           | Burst read       |

| n+19  | <b>A</b> 9     | L   | L      | L                 | L   | L   | L  | Q8             | Load write       |

NOTES:

1.  $\overline{CE} = L$  is defined as  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$  and  $\overline{CE}_2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}_1 = H$ ,  $\overline{CE}_2 = H$  or  $\overline{CE}_2 = L$ .

2. H = High; L = Low; X = Don't Care; Z = High Impedance.

### Read Operation (1)

| Cycle | Address        | R/W | ADV/LD | CE(2) | CEN | BWx | ŌĒ | I/O            | Comments                        |

|-------|----------------|-----|--------|-------|-----|-----|----|----------------|---------------------------------|

| n     | A <sub>0</sub> | Н   | L      | L     | L   | Х   | Х  | Х              | Address and Control meet setup  |

| n+1   | Х              | Х   | Х      | Х     | L   | Χ   | Χ  | Х              | Clock Setup Valid               |

| n+2   | Х              | Χ   | Х      | Χ     | Х   | Х   | L  | Q <sub>0</sub> | Contents of Address Ao Read Out |

NOTES:

5281 tbl 13

5281 tbl 12

2.  $\overline{CE}$  = L is defined as  $\overline{CE}_1$  = L,  $\overline{CE}_2$  = L and  $\overline{CE}_2$  = H.  $\overline{CE}$  = H is defined as  $\overline{CE}_1$  = H,  $\overline{CE}_2$  = H or  $\overline{CE}_2$  = L.

<sup>1.</sup> H = High; L = Low; X = Don't Care; Z = High Impedance.

### **Burst Read Operation (1)**

| Cycle | Address    | R/W | ADV/LD | CE(2) | CEN | B₩x | ŌĒ | I/O            | Comments                                               |  |  |

|-------|------------|-----|--------|-------|-----|-----|----|----------------|--------------------------------------------------------|--|--|

| n     | <b>A</b> 0 | Н   | L      | L     | L   | Х   | Х  | Х              | Address and Control meet setup                         |  |  |

| n+1   | Х          | Х   | Н      | Х     | L   | Х   | Х  | Х              | Clock Setup Valid, Advance Counter                     |  |  |

| n+2   | Х          | Х   | Η      | Х     | L   | Х   | L  | Q <sub>0</sub> | Address Ao Read Out, Inc. Count                        |  |  |

| n+3   | Х          | Х   | Η      | Х     | L   | Х   | L  | Q0+1           | Address A <sub>0+1</sub> Read Out, Inc. Count          |  |  |

| n+4   | Х          | Х   | Н      | Х     | L   | Χ   | L  | Q0+2           | Address A <sub>0+2</sub> Read Out, Inc. Count          |  |  |

| n+5   | <b>A</b> 1 | Н   | L      | L     | L   | Х   | L  | Q0+3           | Address A <sub>0+3</sub> Read Out, Load A <sub>1</sub> |  |  |

| n+6   | Х          | Х   | Н      | Х     | L   | Х   | L  | Q <sub>0</sub> | Address Ao Read Out, Inc. Count                        |  |  |

| n+7   | Х          | Х   | Н      | Х     | L   | Х   | L  | Q1             | Address A <sub>1</sub> Read Out, Inc. Count            |  |  |

| n+8   | <b>A</b> 2 | Н   | L      | L     | L   | Х   | L  | Q1+1           | Address A <sub>1+1</sub> Read Out, Load A <sub>2</sub> |  |  |

#### NOTES:

5281 tbl 14

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance..

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$  and  $\overline{CE}_2 = H$ .  $\overline{CE}_3 = H$  is defined as  $\overline{CE}_1 = H$ ,  $\overline{CE}_2 = H$  or  $\overline{CE}_2 = H$ .

### Write Operation (1)

| Cycle | Address        | R/W | ADV/LD | CE(2) | CEN | B₩x | Œ | I/O            | Comments                       |

|-------|----------------|-----|--------|-------|-----|-----|---|----------------|--------------------------------|

| n     | A <sub>0</sub> | L   | L      | L     | L   | L   | Х | Х              | Address and Control meet setup |

| n+1   | Х              | Х   | Х      | Х     | L   | Х   | Х | Х              | Clock Setup Valid              |

| n+2   | Х              | Χ   | Х      | Х     | L   | Х   | Χ | D <sub>0</sub> | Write to Address Ao            |

#### **NOTES**

5281 tbl 15

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$  and  $\overline{CE}_2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}_1 = H$ ,  $\overline{CE}_2 = H$  or  $\overline{CE}_2 = L$ .

### **Burst Write Operation (1)**

| Dui 3 | , wille        | ohei | ation · | •                       |     |     |    |                |                                                     |

|-------|----------------|------|---------|-------------------------|-----|-----|----|----------------|-----------------------------------------------------|

| Cycle | Address        | R/W  | ADV/LD  | <u>CE<sup>(2)</sup></u> | CEN | ₿₩x | ŌĒ | I/O            | Comments                                            |

| n     | A <sub>0</sub> | L    | L       | L                       | L   | L   | Х  | Х              | Address and Control meet setup                      |

| n+1   | Х              | Χ    | Н       | Х                       | L   | L   | Х  | Х              | Clock Setup Valid, Inc. Count                       |

| n+2   | Х              | Х    | Н       | Х                       | L   | L   | Х  | D <sub>0</sub> | Address A <sub>0</sub> Write, Inc. Count            |

| n+3   | Х              | Х    | Н       | Х                       | L   | L   | Х  | D0+1           | Address A <sub>0+1</sub> Write, Inc. Count          |

| n+4   | Х              | Х    | Н       | Х                       | L   | L   | Х  | D0+2           | Address A <sub>0+2</sub> Write, Inc. Count          |

| n+5   | A1             | L    | L       | L                       | L   | L   | Х  | D0+3           | Address A <sub>0+3</sub> Write, Load A <sub>1</sub> |

| n+6   | Х              | Χ    | Н       | Х                       | L   | ٦   | Х  | D <sub>0</sub> | Address At Write, Inc. Count                        |

| n+7   | Х              | Х    | Н       | Х                       | L   | L   | Х  | D1             | Address A1 Write, Inc. Count                        |

| n+8   | A <sub>2</sub> | L    | L       | L                       | L   | L   | Х  | D1+1           | Address A1+1 Write, Load A2                         |

#### NOTES:

- 1. H = High; L = Low; X = Don't Care; ? = Don't Know; Z = High Impedance.

- 2.  $\overline{CE}$  = L is defined as  $\overline{CE}_1$  = L,  $\overline{CE}_2$  = L and  $\overline{CE}_2$  = H.  $\overline{CE}$  = H is defined as  $\overline{CE}_1$  = H,  $\overline{CE}_2$  = H or  $\overline{CE}_2$  = L.

### Read Operation with Clock Enable Used (1)

| Cycle | Address        | R/W | ADV/LD | CE(2) | CEN | B₩x | ŌĒ | I/O            | Comments                                     |

|-------|----------------|-----|--------|-------|-----|-----|----|----------------|----------------------------------------------|

| n     | A <sub>0</sub> | Н   | L      | L     | L   | Χ   | Χ  | Х              | Address and Control meet setup               |

| n+1   | Х              | Х   | Х      | Х     | H   | Х   | Х  | Х              | Clock n+1 Ignored                            |

| n+2   | <b>A</b> 1     | Н   | L      | L     |     | Χ   | Χ  | Х              | Clock Valid                                  |

| n+3   | Х              | Χ   | Х      | Χ     | Н   | Χ   | L  | Q <sub>0</sub> | Clock Ignored. Data Qo is on the bus.        |

| n+4   | Х              | Х   | Х      | Х     | Ξ   | Х   |    | Q <sub>0</sub> | Clock Ignored. Data Qo is on the bus.        |

| n+5   | <b>A</b> 2     | Н   | L      | L     | L   | Χ   |    | Q <sub>0</sub> | Address Ao Read out (bus trans.)             |

| n+6   | Аз             | Н   | L      | L     | L   | Χ   | L  | Q1             | Address A <sub>1</sub> Read out (bus trans.) |

| n+7   | A4             | Н   | L      | L     | L   | Χ   | L  | Q2             | Address A2 Read out (bus trans.)             |

#### NOTES:

5281 th 17

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.

- 2.  $\overline{CE}$  = L is defined as  $\overline{CE}_1$  = L,  $\overline{CE}_2$  = L and  $\overline{CE}_2$  = H.  $\overline{CE}$  = H is defined as  $\overline{CE}_1$  = H,  $\overline{CE}_2$  = H or  $\overline{CE}_2$  = L.

### Write Operation with Clock Enable Used (1)

| Cycle | Address        | R/W | ADV/LD | <b>C</b> E <sup>(2)</sup> | CEN | B₩x | ŌĒ | I/O            | Comments                        |

|-------|----------------|-----|--------|---------------------------|-----|-----|----|----------------|---------------------------------|

| n     | A <sub>0</sub> | L   | L      | L                         | L   | L   | Χ  | Х              | Address and Control meet setup. |

| n+1   | Х              | Х   | Х      | Χ                         | Η   | Χ   | Х  | Х              | Clock n+1 Ignored.              |

| n+2   | <b>A</b> 1     | L   | L      | L                         | L   | L   | Х  | Х              | Clock Valid.                    |

| n+3   | Х              | Х   | Х      | Χ                         | Н   | Χ   | Х  | Х              | Clock Ignored.                  |

| n+4   | Х              | Х   | Х      | Χ                         | Н   | Χ   | Х  | Х              | Clock Ignored.                  |

| n+5   | <b>A</b> 2     | L   | L      | L                         | L   | L   | Х  | D <sub>0</sub> | Write Data Do                   |

| n+6   | Аз             | L   | L      | L                         | L   | L   | Χ  | D1             | Write Data D1                   |

| n+7   | A4             | L   | L      | L                         | L   | L   | Х  | D2             | Write Data D2                   |

#### NOTES:

- 1. H = High; L = Low; X = Don't Care; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$  and  $\overline{CE}_2 = H$ .  $\overline{CE} = H$  is defined as  $\overline{CE}_1 = H$ ,  $\overline{CE}_2 = H$  or  $\overline{CE}_2 = L$ .

### Read Operation with CHIP Enable Used (1)

| Cycle | Address    | R/W | ADV/LD | CE(2) | CEN | B₩x | ŌĒ | I/O <sup>(3)</sup> | Comments                                     |

|-------|------------|-----|--------|-------|-----|-----|----|--------------------|----------------------------------------------|

| n     | Х          | Χ   | L      | Н     | L   | Х   | Х  | ?                  | Deselected.                                  |

| n+1   | Х          | Х   | L      | Ι     | L   | Х   | Х  | ?                  | Deselected.                                  |

| n+2   | <b>A</b> 0 | Н   | L      | L     | L   | Х   | Х  | Z                  | Address and Control meet setup               |

| n+3   | Х          | Х   | L      | Η     | L   | Х   | Х  | Z                  | Deselected or STOP.                          |

| n+4   | <b>A</b> 1 | Н   | L      | L     | L   | Х   | L  | Q <sub>0</sub>     | Address Ao Read out. Load A1.                |

| n+5   | Х          | Х   | L      | Ι     | L   | Х   | Х  | Z                  | Deselected or STOP.                          |

| n+6   | Х          | Х   | L      | Ι     | ٦   | Х   | _  | Q1                 | Address A <sub>1</sub> Read out. Deselected. |

| n+7   | <b>A</b> 2 | Н   | L      | L     | L   | Х   | Х  | Z                  | Address and control meet setup.              |

| n+8   | Х          | Х   | L      | Н     | L   | Х   | Х  | Z                  | Deselected or STOP.                          |

| n+9   | Х          | Χ   | L      | Н     | L   | Χ   | L  | Q2                 | Address A <sub>2</sub> Read out. Deselected. |

#### NOTES:

5281 tbl 19

- 1. H = High; L = Low; X = Don't Care; ? = Don't Know; Z = High Impedance.

- 2.  $\overline{CE} = L$  is defined as  $\overline{CE}_1 = L$ ,  $\overline{CE}_2 = L$  and  $\overline{CE}_2 = H$ .  $\overline{CE}_3 = H$  is defined as  $\overline{CE}_1 = H$ ,  $\overline{CE}_2 = H$  or  $\overline{CE}_2 = H$ .

- 3. Device Outputs are ensured to be in High-Z after the first rising edge of clock upon power-up.

### Write Operation with Chip Enable Used (1)

| ***** | Opera      |     | •••••  | P —   |     | -   | -  |                    |                                              |

|-------|------------|-----|--------|-------|-----|-----|----|--------------------|----------------------------------------------|

| Cycle | Address    | R/W | ADV/LD | CE(2) | CEN | BWx | ŌĒ | I/O <sup>(3)</sup> | Comments                                     |

| n     | Х          | Χ   | L      | Н     | L   | Х   | Х  | ?                  | Deselected.                                  |

| n+1   | Х          | Х   | L      | Н     | L   | Х   | Х  | ?                  | Deselected.                                  |

| n+2   | <b>A</b> 0 | L   | L      | L     | L   | L   | Х  | Z                  | Address and Control meet setup               |

| n+3   | Х          | Х   | L      | Н     | L   | Х   | Х  | Z                  | Deselected or STOP.                          |

| n+4   | <b>A</b> 1 | L   | L      | L     | L   | L   | Х  | D <sub>0</sub>     | Address Do Write in. Load A1.                |

| n+5   | Х          | Х   | L      | Н     | L   | Х   | Х  | Z                  | Deselected or STOP.                          |

| n+6   | Х          | Х   | L      | Н     | L   | Х   | Х  | D1                 | Address D <sub>1</sub> Write in. Deselected. |

| n+7   | <b>A</b> 2 | L   | L      | L     | L   | L   | Х  | Z                  | Address and control meet setup.              |

| n+8   | Х          | Χ   | L      | Н     | L   | Х   | Х  | Z                  | Deselected or STOP.                          |

| n+9   | Х          | Χ   | L      | Н     | L   | Х   | Х  | D2                 | Address D <sub>2</sub> Write in. Deselected. |

#### NOTES:

- 1. H = High; L = Low; X = Don't Care; ? = Don't Know; Z = High Impedance.

- 2.  $\overline{CE}$  = L is defined as  $\overline{CE}_1$  = L,  $\overline{CE}_2$  = L and  $\overline{CE}_2$  = H.  $\overline{CE}$  = H is defined as  $\overline{CE}_1$  = H,  $\overline{CE}_2$  = H or  $\overline{CE}_2$  = L.

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (VDD = 3.3V +/-5%)

| Symbol | Parameter                                             | Test Conditions                                                 | Min. | Max. | Unit |

|--------|-------------------------------------------------------|-----------------------------------------------------------------|------|------|------|

| Li     | Input Leakage Current                                 | V <sub>DD</sub> = Max., V <sub>IN</sub> = 0V to V <sub>DD</sub> | _    | 5    | μΑ   |

| L      | LBO, JTAG and ZZ Input Leakage Current <sup>(1)</sup> | V <sub>DD</sub> = Max., V <sub>IN</sub> = 0V to V <sub>DD</sub> |      | 30   | μΑ   |

| lLO    | Output Leakage Current                                | Vout = 0V to VDDQ, Device Deselected                            | _    | 5    | μΑ   |

| Vol    | Output Low Voltage                                    | IOL = +8mA, VDD = Min.                                          | _    | 0.4  | ٧    |

| Vон    | Output High Voltage                                   | Iон = -8mA, Vod = Min.                                          | 2.4  | _    | V    |

5281 tbl 21

#### NOTE

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (1) (VDD = 3.3V +/-5%)

|            |                                       |                                                                                                                                                                | 200MHz <sup>(4)</sup> | 166   | MHz | 133   | MHz | 100   |     |      |

|------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----|-------|-----|-------|-----|------|

| Symbol     | Parameter                             | Test Conditions                                                                                                                                                | Com'l Only            | Com'l | Ind | Com'l | Ind | Com'l | Ind | Unit |

| <b>D</b> D | Operating Power<br>Supply Current     | Device Selected, Outputs Open, ADV/LD = X, V <sub>DD</sub> = Max., V <sub>IN</sub> $\geq$ V <sub>IH</sub> or $\leq$ V <sub>IL</sub> , f = f <sub>MAX</sub> (2) | 400                   | 350   | 360 | 300   | 310 | 250   | 255 | mA   |

| ISB1       | CMOS Standby<br>Power Supply Current  | Device Deselected, Outputs Open, $VDD = Max.$ , $VIN \ge VHD$ or $\le VLD$ , $f = 0^{(2,3)}$                                                                   | 40                    | 40    | 45  | 40    | 45  | 40    | 45  | mA   |

| ISB2       | Clock Running Power<br>Supply Current | Device Deselected, Outputs Open, $VDD = Max., VIN \ge VHD \text{ or } < VLD, f$ = $f_{MAX}^{(2.3)}$                                                            | 130                   | 120   | 130 | 110   | 120 | 100   | 110 | mA   |

| ISB3       | ldle Power<br>Supply Current          | Device Selected, Outputs Open,<br>CEN ≥ VIH, VDD = Max.,<br>VIN ≥ VHD or ≤ VLD, f = fMax <sup>(2,3)</sup>                                                      | 40                    | 40    | 45  | 40    | 45  | 40    | 45  | mA   |

#### NOTES:

5281 tbl 22

- 1. All values are maximum guaranteed values.

- 2. At f = fMAX, inputs are cycling at the maximum frequency of read cycles of 1/tcyc; f=0 means no input lines are changing.

- 3. For I/Os VHD = VDDQ 0.2V, VLD = 0.2V. For other inputs VHD = VDD 0.2V, VLD = 0.2V.

- 4. Only available in 256K x 18 configuration.

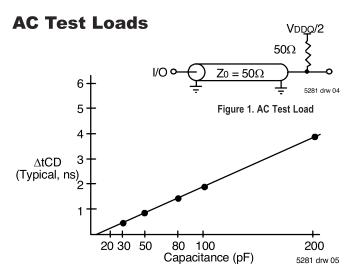

Figure 2. Lumped Capacitive Load, Typical Derating

### **AC Test Conditions**

(VDDQ = 3.3V)

| (1004)                         |              |

|--------------------------------|--------------|

| Input Pulse Levels             | 0 to 3V      |

| Input Rise/Fall Times          | 2ns          |

| Input Timing Reference Levels  | 1.5V         |

| Output Timing Reference Levels | 1.5V         |

| AC Test Load                   | See Figure 1 |

<sup>1.</sup> The LBO, TMS, TDI, TCK and TRST pins will be internally pulled to VDD and ZZ will be internally pulled if they are not actively driven in the application.

#### **AC Electrical Characteristics**

(VDD = 3.3V +/-5%, Commercial and Industrial Temperature Ranges)

|                         |                                             | 2001 | 1Hz <sup>(6)</sup> | 166  | MHz  | 133  | MHz  | 100  | MHz  |      |

|-------------------------|---------------------------------------------|------|--------------------|------|------|------|------|------|------|------|

| Symbol                  | Parameter                                   | Min. | Max.               | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

|                         | 1                                           |      |                    |      |      |      |      |      |      |      |

| tcyc                    | Clock Cycle Time                            | 5    |                    | 6    |      | 7.5  |      | 10   |      | ns   |

| tF <sup>(1)</sup>       | Clock Frequence                             |      | 200                |      | 166  |      | 133  |      | 100  | MHz  |

| tсн <sup>(2)</sup>      | Clock High Pulse Width                      | 1.8  |                    | 1.8  |      | 2.2  |      | 3.2  |      | ns   |

| tcL <sup>(2)</sup>      | Clock Low Pulse Width                       | 1.8  |                    | 1.8  |      | 2.2  |      | 3.2  |      | ns   |

| Output Para             | ameters                                     |      |                    |      |      |      |      |      |      |      |

| tcp                     | Clock High to Valid Data                    |      | 3.2                |      | 3.5  |      | 4.2  |      | 5    | ns   |

| tcpc                    | Clock High to Data Change                   | 1    |                    | 1    |      | 1    |      | 1    |      | ns   |

| tcLz <sup>(3,4,5)</sup> | Clock High to Output Active                 | 1    | -                  | 1    |      | 1    |      | 1    |      | ns   |

| tcHz <sup>(3,4,5)</sup> | Clock High to Data High-Z                   | 1    | 3                  | 1    | 3    | 1    | 3    | 1    | 3.3  | ns   |

| toe                     | Output Enable Access Time                   |      | 3.2                |      | 3.5  |      | 4.2  |      | 5    | ns   |

| toLz <sup>(3,4)</sup>   | Output Enable Low to Data Active            | 0    |                    | 0    |      | 0    |      | 0    |      | ns   |

| tонz <sup>(3,4)</sup>   | Output Enable High to Data High-Z           |      | 3.5                | _    | 3.5  |      | 4.2  |      | 5    | ns   |

| Set Up Time             | es                                          |      |                    |      |      |      |      |      |      |      |

| tse                     | Clock Enable Setup Time                     | 1.5  |                    | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| tsa                     | Address Setup Time                          | 1.5  |                    | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| tsD                     | Data In Setup Time                          | 1.5  | _                  | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| tsw                     | Read/Write (R/W) Setup Time                 | 1.5  |                    | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| tsadv                   | Advance/Load (ADV/\overline{LD}) Setup Time | 1.5  |                    | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| tsc                     | Chip Enable/Select Setup Time               | 1.5  |                    | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| tsB                     | Byte Write Enable (BWx) Setup Time          | 1.5  |                    | 1.5  |      | 1.7  |      | 2.0  |      | ns   |

| Hold Times              |                                             |      |                    |      |      |      |      |      |      |      |

| the                     | Clock Enable Hold Time                      | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

| tha                     | Address Hold Time                           | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

| tHD                     | Data In Hold Time                           | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

| thw                     | Read/Write (R/W) Hold Time                  | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

| thadv                   | Advance/Load (ADV/\overline{LD}) Hold Time  | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

| thc                     | Chip Enable/Select Hold Time                | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  | _    | ns   |

| tнв                     | Byte Write Enable (BWx) Hold Time           | 0.5  |                    | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

#### NOTES:

- 1. te = 1/tcyc.

- 2. Measured as HIGH above 0.6Vppq and LOW below 0.4Vppq.

- 3. Transition is measured ±200mV from steady-state.

- 4. These parameters are guaranteed with the AC load (Figure 1) by device characterization. They are not production tested.

- 5. To avoid bus contention, the output buffers are designed such that tcHz (device turn-off) is about 1ns faster than tcLz (device turn-on) at a given temperature and voltage. The specs as shown do not imply bus contention because tcLz is a Min. parameter that is worse case at totally different test conditions (0 deg. C, 3.465V) than tcHz, which is a Max. parameter (worse case at 70 deg. C, 3.135V).

- 6. Commercial temperature range only. Only available in 256K x 18 configuration.

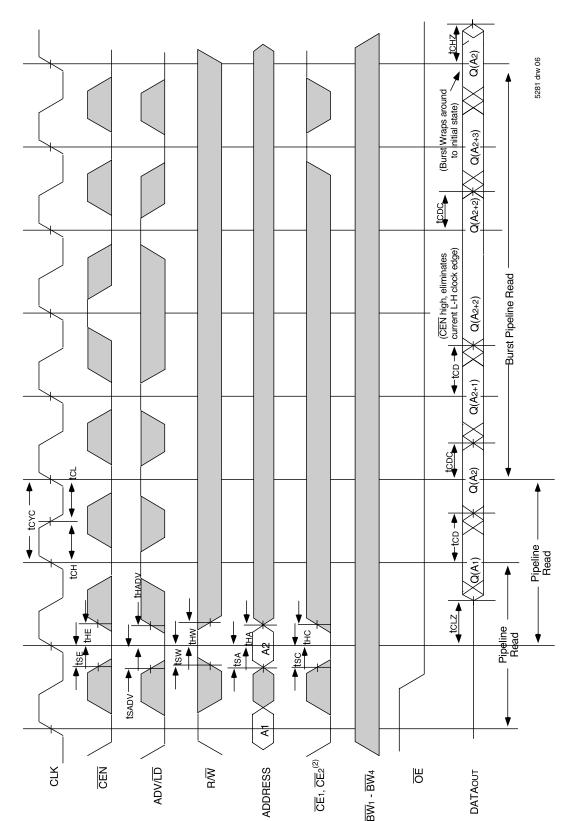

### Timing Waveform of Read Cycle (1,2,3,4)

- 1. Q(A1) represents the first output from the external address A1. Q(A2) represents the first output from the external address A2; Q(A2+1) represents the next output data in the burst sequence of the base address A2, etc. where address bits A0 and A1 are advancing for the four word burst in the sequence defined by the state of the  $\overline{\text{LBO}}$  input. CE2 timing transitions are identical but inverted to the  $\overline{\text{CE}}_1$  and  $\overline{\text{CE}}_2$  signals. For example, when  $\overline{\text{CE}}_1$  and  $\overline{\text{CE}}_2$  are LOW on this waveform, CE2 is HIGH.

- Burst ends when new address and control are loaded into the SRAM by sampling ADV/LD LOW.

R\W is don't care when the SRAM is bursting (ADV/LD sampled HIGH). The nature of the burst access (Read or Write) is fixed by the state of the R\W signal when new address and control are loaded into the SRAM.

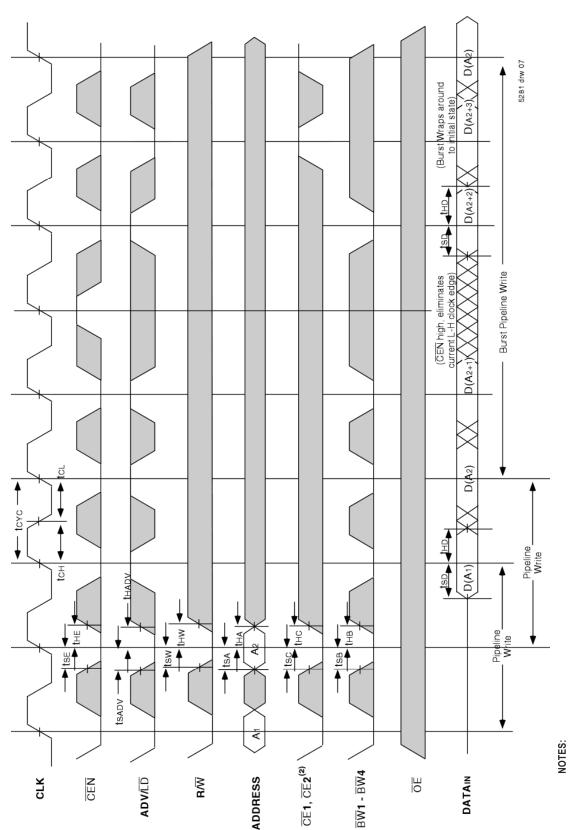

### Timing Waveform of Write Cycles (1,2,3,4,5)

- 1. D (A1) represents the first input to the external address A1. D (A2) represents the first input to the external address A2; D (A2+1) represents the next input data in the burst sequence of the base address A2, etc. where address bits A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input. CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH

- 3. Burst ends when new address and control are loaded into the SRAM by sampling ADV/LD LOW.

4. RW is don't care when the SRAM is bursting (ADV/LD sampled HIGH). The nature of the burst access (Read or Write) is fixed by the state of the R/W signal when new address and control are loaded into the SRAM.

- Individual Byte Write signals (BWx) must be valid on all write and burst-write cycles. A write cycle is initiated when R/W signal is sampled LOW. The byte write information comes in two cycles before the actual data is presented to the SRAM.

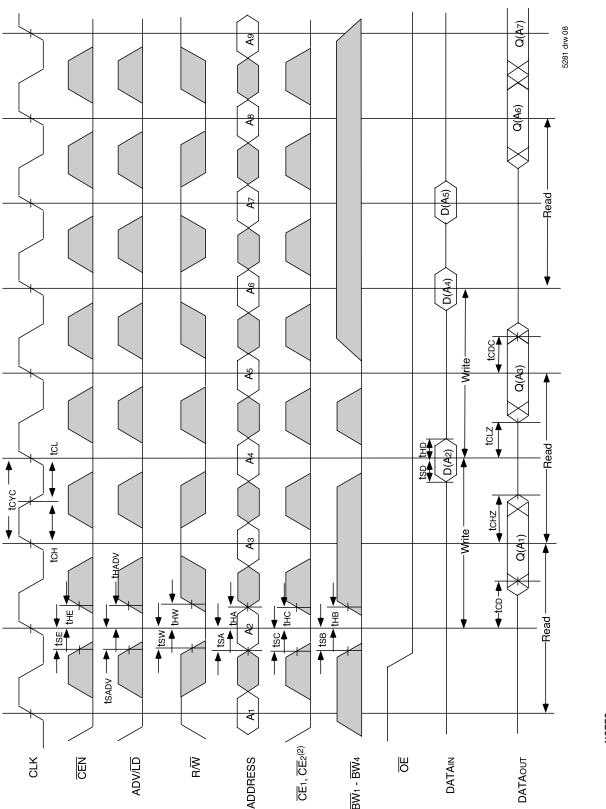

### Timing Waveform of Combined Read and Write Cycles (1,2,3)

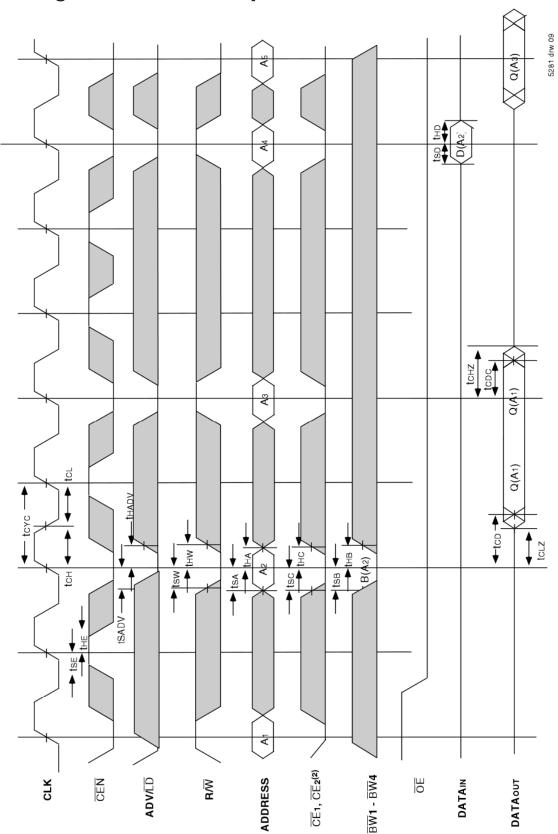

### Timing Waveform of **CEN** Operation (1,2,3,4)

- 1. Q (A1) represents the first output from the external address A1. D (A2) represents the input data to the SRAM corresponding to address A2.

2. CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH.

3. CEN when sampled high on the rising edge of clock will block that L-H transition of the clock from propogating into the SRAM. The part will behave as if the L-H clock transition did not occur. All internal registers in the SRAM will retain their previous state.

- 4. Individual Byte Write signals (BWx) must be valid on all write and burst-write cycles. A write cycle is initiated when R/W signal is sampled LOW. The byte write information comes in two cycles before the actual data is presented to the SRAM.

### Timing Waveform of $\overline{\text{CS}}$ Operation (1,2,3,4)

- 1. Q (41) represents the first output from the external address A1. D (A3) represents the input data to the SRAM corresponding to address A3.

- CE2 timing transitions are identical but inverted to the CE1 and CE2 signals. For example, when CE1 and CE2 are LOW on this waveform, CE2 is HIGH.

OEN when sampled high on the rising edge of clock will block that L-H transition of the clock from propogating into the SRAM. The part will behave as if the L-H clock transition did not occur. All internal registers in the SRAM will retain their previous state.

- Individual Byte Write signals (BWx) must be valid on all write and burst-write cycles. A write cycle is initiated when RW signal is sampled LOW. The byte write information comes in two cycles before the actual data is presented to the SRAM.

#### 100-Pin Plastic Thin Quad Flatpack (TQFP) Package Diagram Outline