# C8051F064 EVALUATION KIT USER'S GUIDE

## 1. Relevant Devices

The C8051F064 Evaluation Kit is intended as an evaluation platform for the microcontrollers in the C8051F06x MCU family. The members of this MCU family are C8051F060, C8051F061, C8051F062, C8051F063, C8051F064, C8051F065, C8051F066, and C8051F067.

- The evaluation board included in this kit is provided with a pre-soldered C8051F064 MCU (TQFP100 package).

- Code developed on the C8051F064 can be easily ported to the other members of this MCU family.

- Refer to the C8051F06x data sheet for the differences between the members of this MCU family.

## 2. Kit Contents

C8051F064 Evaluation Kits contain the following items:

- C8051F064 Evaluation Board

- Silicon Laboratories Evaluation Kit IDE and Product Information CD-ROM. CD content includes the following:

- Silicon Laboratories Integrated Development Environment (IDE)

- Keil Software 8051 Development Tools (evaluation assembler, linker, and C compiler)

- Source code examples and register definition files

- Documentation

- Evaluation Kit Demos, C8051F064 ADC Demo

- USB Cable

- C8051F064 Evaluation Kit User's Guide

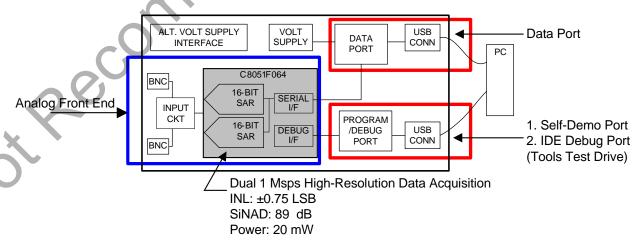

### 3. Kit Overview

Figure 1 illustrates the block diagram of the C8051F064 Evaluation Kit. The board includes an analog front end to signal condition and digitize (through the C8051F064) analog input signals. The board also includes two USB ports to transfer conversions to a PC: the DATA Port and the Self-Demo/IDE Debug port. The DATA port consists of a Silicon Laboratories CP2101 (UART to USB bridge) and a USB connector. The Self-Demo/IDE Debug port consists of Silicon Laboratories' debug interface hardware and a USB connector.

Power for the C8051F064 board can be supplied from either USB connection. An alternative lower noise supply can be used for better measurement performance if desired. Refer to Section 9. for more details.

Figure 1. C8051F064 Evaluation Board Block Diagram

The C8051F064EK has three purposes:

- **Noise Performance Demonstration**—Demonstrates 16-bit dc performance; displays FFT plot and key parameters.

- Performance Evaluation—Facilitates easy programming and analog front end input for dynamic performance evaluation of ac signals.

- **Tools Test Drive**—Allows easy evaluation of the Silicon Laboratories Integrated Development Environment (IDE) (code download and on-chip debug function).

## 4. Evaluation Kit ADC Demo

The C8051F064 evaluation kit includes a demonstration of the noise performance of the 16-bit ADCs on the C8051F064 device. A 1.25 V dc input signal is provided on the board as an input to the ADC input pins, AIN0 and AIN1. The ADCs convert and store 32,768 samples (differential, 16-bit samples in 2s complement) in off-chip SRAM. The PC application then downloads the data through the debug USB port. After processing these conversions, the software generates a spectral plot (magnitude versus frequency) of the ADC input signal. The spectral plot illustrates the C8051F064s noise floor for the given sample set. The minimum and maximum values sampled, mean of values sampled, standard deviation, and dynamic range are displayed. To run the ADC Demo, first configure the evaluation board and install the PC application.

## 4.1. ADC Demo Hardware Setup

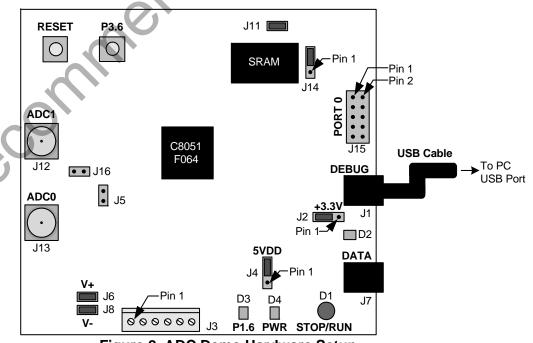

Configure the evaluation board according to the instructions below. A diagram of the final configuration is shown in Figure 2. Configuration shorting blocks may already be installed.

- 1. Place a shorting block on the J2 header connecting Pin 2 and Pin 3. This configures the evaluation board to be powered from the DEBUG USB connector (J1).

- 2. Place a shorting block on the J4 header connecting Pin 2 and Pin 3. This configures the external voltage reference to be powered from the DEBUG USB connector (J1).

- 3. Place shorting blocks on the "V+" (J6) and "V-" (J8) headers.

- 4. Configure SRAM(U5): Place shorting blocks on J11 and on J14 connecting Pin 2 and Pin 3.

- 5. Connect one end of the provided USB cable to any available USB port on the PC.

- 6. Connect the other end of the USB cable into the USB connector on the board labeled "DEBUG" (J1). This connection should power the board. Evaluation board power is indicated by the "PWR" LED (D4).

Figure 2. ADC Demo Hardware Setup

#### 4.2. ADC Demo Software Installation

Install the ADC Demo application software according to the instructions below.

- 1. Place the Evaluation Kit CD-ROM into the PC.

- 2. An installation dialogue box will appear. Click the "Install Evaluation Kit Tools" button.

- 3. The Kit Selection window will open, showing the available Evaluation Kits. To install the application, select the "C8051F064 Evaluation Kit" option. Click the "Install" button.

- 4. The "Confirm Installations" window will open, showing the available installation options. Only the "Install C8051F064 Evaluation Kit Demo" needs to be selected to run the demo. The "Install CP210x Drivers" option must be selected in order to communicate with the board through the DATA USB port.

- 5. Follow the installation prompts to install the demo application. By default, the software will be installed in the C:\Silabs\MCU\C8051F064\_EK directory. In addition, shortcuts to the application will be placed on the desktop and in the Start > Programs menu.

# 4.3. Running the ADC Demo Software

To run the demo, run the installed application. When executed, the following occurs automatically:

- 1. Firmware is downloaded to the C8051F064 FLASH code memory.

- 2. The C8051F064's 8051 MCU executes the firmware to configure the 16-bit ADC, direct memory access (DMA) interface, and parallel interface to store samples in the onboard SRAM.

- 3. The ADCs sample a dc voltage (32,768 samples) to measure the inherent noise floor of the ADC and analog front-end (AFE) circuit.

- **Note**: There is also noise contributed by the circuit board, including noise from the USB connection to the ground on the PC.

- 4. The ADC performs data conversions, and the DMA stores these samples in the onboard SRAM via a parallel interface.

- 5. Once the ADC samples are stored, the application reads these samples from the board (download through the DEBUG USB port) and analyzes them.

- 6. The application displays a frequency analysis plot of the samples and shows their maximum, minimum, and mean values and the standard code deviation or "sigma" (in LSBs) and calculates the dynamic range based on a full-scale signal (rms) value. Such an evaluation is an important dc noise performance measurement of high-resolution ADCs.

# 5. Software Setup

The included CD-ROM contains the Silicon Laboratories Integrated Development Environment (IDE), Keil software 8051 tools and additional documentation. Insert the CD-ROM into your PC's CD-ROM drive. An installer will automatically launch, allowing you to install the IDE software or read documentation by clicking buttons on the Installation Panel. If the installer does not automatically start when you insert the CD-ROM, run *autorun.exe* found in the root directory of the CD-ROM. Refer to the *ReleaseNotes.txt* file on the CD-ROM for the latest information regarding known problems and restrictions. After installing the software, see the following sections for information regarding the software and running one of the demo applications.

### 5.1. CP210x USB to UART VCP Driver Installation

The C8051F064 Evaluation Board includes a Silicon Laboratories CP2101 USB-to-UART Bridge Controller. Device drivers for the CP2101 need to be installed before PC software such as HyperTerminal can communicate with the evaluation board over the USB connection. If the "Install CP210x Drivers" option was selected during installation, this will launch a driver "unpacker" utility.

- 1. Follow the steps to copy the driver files to the desired location. The default directory is C:\SiLabs\MCU\CP210x.

- 2. The final window will give an option to install the driver on the target system. Select the "Launch the CP210x VCP Driver Installer" option if you are ready to install the driver.

- 3. If selected, the driver installer will now launch, providing an option to specify the driver installation location. After pressing the "Install" button, the installer will search your system for copies of previously installed CP210x Virtual COM Port drivers. It will let you know when your system is up to date. The driver files included in this installation have been certified by Microsoft.

- 4. If the "Launch the CP210x VCP Driver Installer" option was not selected in step 3, the installer can be found in the location specified in step 2, by default C:\SiLabs\MCU\CP210x\Windows\_2K\_XP\_S2K3\_Vista. At this location run CP210xVCPInstaller.exe.

- 5. To complete the installation process, connect the included USB cable between the host computer and the Data USB connector (J7) on the C8051F064 Evaluation Board. Windows will automatically finish the driver installation. Information windows will pop up from the taskbar to show the installation progress.

- 6. If needed, the driver files can be uninstalled by selecting "Silicon Laboratories CP210x USB to UART Bridge (Driver Removal)" option in the "Add or Remove Programs" window.

## 6. Software Overview

## 6.1. Silicon Laboratories IDE

The Silicon Laboratories IDE integrates a source-code editor, a source-level debugger, and an in-system Flash programmer. See Section "7. Using the Keil Software 8051 Tools with the Silicon Laboratories IDE" on page 7 for detailed information on how to use the IDE. The Keil Evaluation Toolset includes a compiler, linker, and assembler and easily integrates into the IDE. The use of third-party compilers and assemblers is also supported.

#### 6.1.1. IDE System Requirements

The Silicon Laboratories IDE requirements:

- Pentium-class host PC running Microsoft Windows 2000 or newer.

- One available USB port.

- 64 MB RAM and 40 MB free HD space recommended.

#### 6.1.2. 3rd Party Toolsets

The Silicon Laboratories IDE has native support for many 8051 compilers. The full list of natively supported tools is as follows:

- Keil

- IAR

- Raisonance

- Tasking

- Hi-Tech

- SDCC

The demo applications for the C8051F064 evaluation board are written to work with the Keil and SDCC toolsets.

### 6.2. Keil Evaluation Toolset

#### 6.2.1. Keil Assembler and Linker

The assembler and linker that are part of the Keil Demonstration Toolset are the same versions that are found in the full Keil Toolset. The complete assembler and linker reference manual can be found on-line under the **Help** menu in the IDE or in the "SiLabsWCUVIIP" directory (A51.chm).

### 6.2.2. Keil Evaluation C51 C Compiler

The evaluation version of the C51 compiler is the same as the full version with the following limitation: (1) Maximum 4 kB code generation. When installed from the CD-ROM, the C51 compiler is initially limited to a code size of 2 kB, and programs start at code address 0x0800. Refer to the Application Note "AN104: Integrating Keil Tools into the Silicon Labs IDE" for instructions to change the limitation to 4 kB, and have the programs start at code address 0x0000.

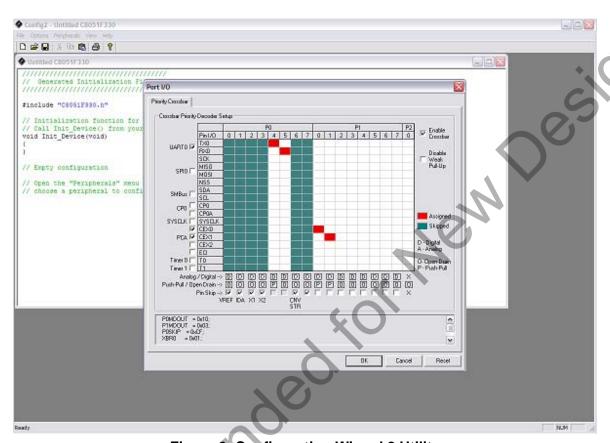

## 6.3. Configuration Wizard 2

The Configuration Wizard 2 is a code generation tool for all of the Silicon Laboratories devices. Code is generated through the use of dialog boxes for each of the device's peripherals.

Figure 3. Configuration Wizard 2 Utility

The Configuration Wizard 2 utility helps accelerate development by automatically generating initialization source code to configure and enable the on-chip resources needed by most design projects. In just a few steps, the wizard creates complete startup code for a specific Silicon Laboratories MCU. The program is configurable to provide the output in C or assembly. For more information, refer to the Configuration Wizard 2 help available under the **Help** menu in Config Wizard 2.

# 6.4. Keil uVision2 and uVision3 Silicon Laboratories Drivers

As an alternative to the Silicon Laboratories IDE, the uVision debug driver allows the Keil uVision IDE to communicate with Silicon Laboratories on-chip debug logic. In-system Flash memory programming integrated into the driver allows for rapidly updating target code. The uVision IDE can be used to start and stop program execution, set breakpoints, check variables, inspect and modify memory contents, and single-step through programs running on the actual target hardware.

# 7. Using the Keil Software 8051 Tools with the Silicon Laboratories IDE

To perform source-level debugging with the IDE, you must configure the Keil 8051 tools to generate an absolute object file in the OMF-51 format with object extensions and debug records enabled. You may build the OMF-51 absolute object file by calling the Keil 8051 tools at the command line (e.g., batch file or make file) or by using the project manager built into the IDE. The default configuration when using the Silicon Laboratories IDE project manager enables object extension and debug record generation. Refer to Application Note "AN104: Integrating Keil 8051 Tools into the Silicon Labs IDE" in the "SiLabs WCU\Documentation\ApplicationNotes" directory for additional information on using the Keil 8051 tools with the Silicon Laboratories IDE.

To build an absolute object file using the Silicon Laboratories IDE project manager, you must first create a project. A project consists of a set of files, IDE configuration, debug views, and a target build configuration (list of files and tool configurations used as input to the assembler, compiler, and linker when building an output object file).

The following sections illustrate the steps necessary to manually create a project with one or more source files, build a program, and download the program to the target in preparation for debugging. (The IDE will automatically create a single-file project using the currently open and active source file if you select **Build/Make Project** before a project is defined.)

# 7.1. Creating a New Project

- 1. Select Project New Project to open a new project and reset all configuration settings to default.

- 2. Select **File** → **New File** to open an editor window. Create your source file(s) and save the file(s) with a recognized extension, such as .c, .h, or .asm, to enable color syntax highlighting.

- 3. Right-click on "New Project" in the **Project Window**. Select **Add files to project**. Select files in the file browser and click Open. Continue adding files until all project files have been added.

- 4. For each of the files in the **Project Window** that you want assembled, compiled, and linked into the target build, right-click on the file name and select **Add file to build**. Each file will be assembled or compiled as appropriate (based on file extension) and linked into the build of the absolute object file.

**Note:** If a project contains a large number of files, the "Group" feature of the IDE can be used to organize. Right-click on "New Project" in the **Project Window**. Select **Add Groups to project**. Add pre-defined groups or add customized groups. Right-click on the group name and choose **Add file to group**. Select files to be added. Continue adding files until all project files have been added.

# 7.2. Building and Downloading the Program for Debugging

- Once all source files have been added to the target build, build the project by clicking on the Build/Make

Project button in the toolbar or selecting Project → Build/Make Project from the menu.

Note: After the project has been built the first time, the Build/Make Project command will only build the files that have been changed since the previous build. To rebuild all files and project dependencies, click on the Rebuild All button in the toolbar or select Project → Rebuild All from the menu.

- Before connecting to the target device, several connection options may need to be set. Open the Connection

Options window by selecting Options—Connection Options... in the IDE menu. First, select the appropriate

adapter in the "Serial Adapter" section. Next, the correct "Debug Interface" must be selected. C8051F06x family

devices use the JTAG debug interface. Once all the selections are made, click the OK button to close the

window.

- 3. Click the **Connect** button in the toolbar or select **Debug**  $\rightarrow$  **Connect** from the menu to connect to the device.

- 4. Download the project to the target by clicking the **Download Code** button in the toolbar. **Note:** To enable automatic downloading if the program build is successful, select **Enable automatic connect/download after build** in the **Project**—**Target Build Configuration** dialog. If errors occur during the build process, the IDE will not attempt the download.

- 5. Save the project when finished with the debug session to preserve the current target build configuration, editor settings and the location of all open debug views. To save the project, select **Project** → **Save Project As...** from the menu. Create a new name for the project and click on **Save**.

# 8. Example Source Code

Example source code and register definition files are provided in the "SiLabsWCU\Examples\C8051F06x" directory during IDE installation. These files may be used as a template for code development. Example applications include a blinking LED example that configures the green LED on the evaluation board to blink at a fixed rate.

## 8.1. Register Definition Files

Register definition files *C8051F060.inc* and *C8051F060.h* define all SFR registers and bit-addressable control/status bits. They are installed into the "*SiLabs\MCU\Examples\C8051F06x*" directory during IDE installation. The register and bit names are identical to those used in the C8051F06x data sheet. Both register definition files are also installed in the default search path used by the Keil Software 8051 tools. Therefore, when using the Keil 8051 tools included with the evaluation kit (A51, C51), it is not necessary to copy a register definition file to each project's file directory.

# 8.2. Blinking LED Example

The example source files, blink.asm and blinky.c, show examples of several basic C8051F06x functions. These include disabling the watchdog timer (WDT), configuring the Port I/O crossbar, configuring a timer for an interrupt routine, initializing the system clock, and configuring a GPIO port. When compiled/assembled and linked, this program flashes the green LED on the evaluation board about five times a second using the interrupt handler with e Recommended Ro a timer.

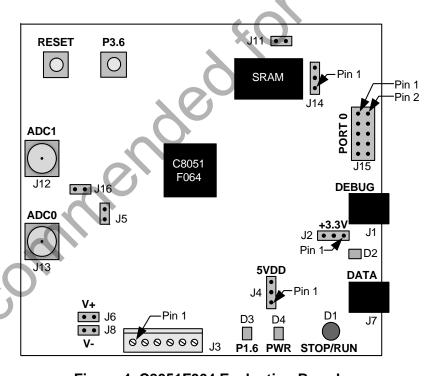

## 9. Evaluation board

The C8051F064 Evaluation Kit includes an evaluation board with a C8051F064 device pre-installed for evaluation and preliminary software development. Numerous input/output (I/O) connections are provided to facilitate prototyping using the evaluation board. Refer to Figure 4 for the locations of the various I/O connectors.

DEBUG USB port connector for code download and on-chip debug functions J1 J2 Evaluation board power supply selector J3 Analog I/O terminal block J4 External voltage reference supply selector J5 External conversion start header J7 DATA USB port connector for data communications with the PC J6, J8 Op-amp supply voltage headers J11, J14 External memory interface connectors J12, J13 ADC1 & ADC0; BNC connectors for analog inputs J15 Port 0 header J16 ADC differential input header

Figure 4. C8051F064 Evaluation Board

## 9.1. System Clock Sources

The C8051F064 device installed on the evaluation board features a calibrated programmable internal oscillator that is enabled as the system clock source on reset. After reset, the internal oscillator operates at a frequency of 3.0625 MHz (±2%) by default but may be configured by software to operate at other frequencies. Therefore, in many applications, an external oscillator is not required. However, an external 22.1184 MHz crystal is installed on the evaluation board for additional applications. Refer to the C8051F06x data sheet for more information on configuring the system clock source.

#### 9.2. Switches and LEDs

Two switches are provided on the evaluation board. Switch SW1 is connected to the RESET pin of the C8051F064. Pressing SW1 puts the device into its hardware-reset state. Switch SW2 is connected to the C8051F060's general-purpose I/O (GPIO) pin P3.7. Pressing SW2 generates a logic low signal on the port pin.

Four LEDs are also provided on the evaluation board.

- D1—The bi-color LED labeled "Run/Stop" indicates communications between the PC and the DEBUG USB port.

- D2—The red LED D2 reflects the state of the SUSPEND signal of the DATA port device.

- D3—The green LED labeled "P1.6" is connected to the C8051F064's GPIO pin P1.6.

- D4—The red LED labeled "PWR" indicates a power connection to the evaluation board.

# 9.3. DEBUG Interface (J1)

The evaluation board DEBUG USB port (J1) provides the interface between a PC USB port and the C8051F064's in-system debug/programming circuitry. In addition, this port is used for the ADC Demo detailed in Section 4. Table 1 shows the DEBUG USB pin definitions.

**Table 1. DEBUG USB Connector Pin Descriptions**

| Pin # | Description |  |

|-------|-------------|--|

| 1     | VBUS        |  |

| 2     | D-          |  |

| 3     | D+          |  |

| 4     | GND         |  |

# 9.4. DATA Interface (J7)

The evaluation board DATA USB port (J7) provides a data interface between a PC USB port and the CP2101 (Silicon Labs USB to UART bridge). This interface provides a virtual COM port via USB and will appear as a COM port to PC applications. Table 2 shows the DATA USB pin definitions.

**Table 2. DATA USB Connector Pin Descriptions**

| Pin # | Description |  |

|-------|-------------|--|

| 1     | VBUS        |  |

| 2     | D-          |  |

| 3     | D+          |  |

| 4     | GND         |  |

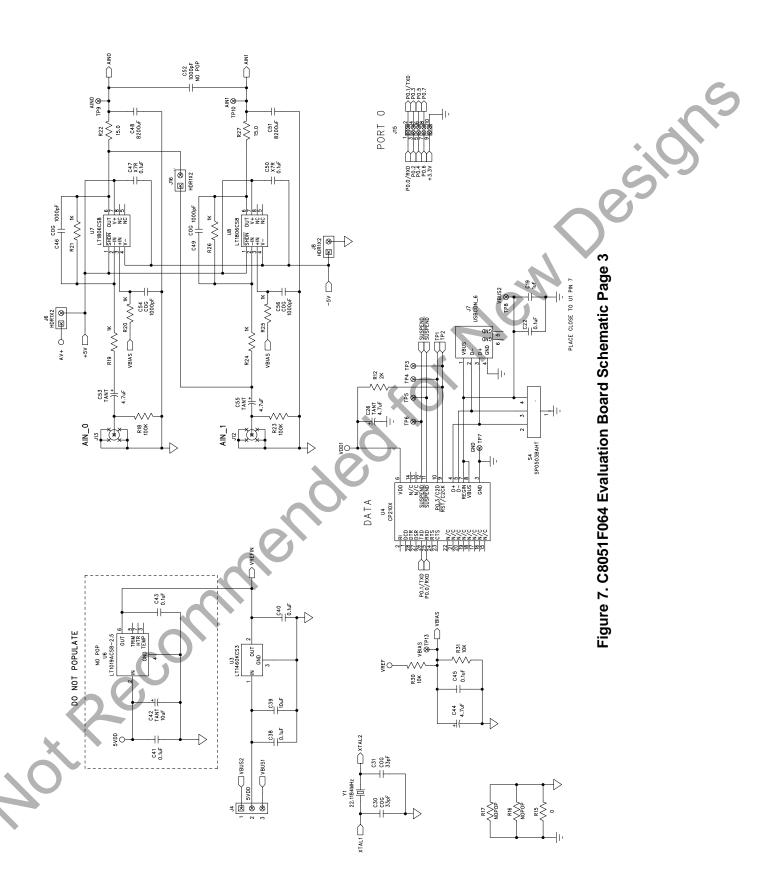

# 9.5. Analog Inputs (J4, J5, J6, J8, J16, ADC0 [J13], ADC1 [J12])

Two BNC connectors (J13 (ADC0) and J12 (ADC1)) are provided on the C8051F064 board for easy evaluation of the 16-bit on-chip ADCs. These analog inputs can be used to input an ac analog signal to the ADCs, ADC0 and ADC1. Additionally, front-end circuitry is provided to condition the analog signals. To use this circuitry, follow the guidelines listed below in conjunction with the schematic located in Section 10. See "AN190: Understanding ADC Specifications" for a detailed discussion of issues related to ADC performance.

- Select the 5 V supply voltage for the Voltage References U3 and U6 at header J4. Place a shorting block on J4, Pin 1 and Pin 2, to select the DATA VBUS signal. Place a shorting block on J4, Pin 2 and Pin 3, to select the DEBUG VBUS signal.

- A single-supply voltage option is provided on the evaluation board for the op-amps. Place a shorting block on J6 to connect the "V+" op-amp supply to AV+. Additionally, place a shorting block on J8 to connect the "V-" op-amp supply to GND.

- Provide a dual-supply voltage to the op-amps for optimal performance by removing the shorting blocks on headers J6 and J8. To supply the voltages, +5 V and -5 V signals will need to be provided at the J3 terminal block (Pin 1 and Pin 2).

**Note:**Remove shorting blocks from J6 and J8 BEFORE applying voltages to the J3 terminal block. Voltages applied to J3 while shorting blocks are on J6 and J8 could cause damage to the evaluation board.

- Provide an external Conversion Start signal to ADC0 at header J5 Pin 1.

- Provide an external Conversion Start signal to ADC1 at header J5 Pin 2.

- Differential measurement from one test source: input signal to ADC0 and place shorting block on header J16.

# 9.6. Analog I/O (Terminal Block [J3])

J3 is used to provide off-board voltage supply and voltage references for better noise performance evaluation in a lab environment. Refer to Table 3 for terminal block connections.

Pin #

Description

1

-5 V

2

+5 V

3

AGND

4

GND

5

+3.3 VIN

6

5VDD

Table 3. Terminal Block (J3) Pin Descriptions

# 9.7. External Memory Interface (J11, J14)

The C8051F064 evaluation board provides an External Memory Interface by connecting a 128 kB SRAM to the device port pins. The device's External Memory Interface can be enabled by installing a shorting block at header J11. This connects port pin P4.5 to the Chip Select ( $\overline{\text{CS}}$ ) signal on the SRAM, pulling this signal low. Placing a shorting block on header J14, Pin 2 and Pin 3, enables the use of the lower address bank on the SRAM. Moving the shorting block to J14, Pin 1 and Pin 2, enables port pin P3.7 to select between the upper and lower address banks on the SRAM. Refer to Table 4 for the external memory interface signal descriptions.

| <b>, , , ,</b> |                  |                       |  |

|----------------|------------------|-----------------------|--|

| SRAM Signal    | C8051F060 Signal | Description           |  |

| WE             | P4.7             | Write Enable          |  |

| CS             | P4.5 (J11)       | Chip Select           |  |

| ŌĒ             | P4.6             | Output Enable         |  |

| $V_{DD}$       | +3VD2            | Digital Power         |  |

| GND            | GND              | Digital Ground        |  |

| I/O0I/O7       | P7.0P7.7         | Data Bus              |  |

| A0A7           | P6.0P6.7         | Address Bus Low Byte  |  |

| A8A15          | P5.0P5.7         | Address Bus High Byte |  |

| A16            | P3.7 (J14[1-2])  | Bank Select           |  |

| A16            | GND (J14[2-3])   | Bank Select Always 0  |  |

**Table 4. External Memory Interface Signal Descriptions**

# 9.8. PORT I/O Connectors (J15)

12

The Port 0 signals on the C8051F064 have their own 10-pin header (J15). This header provides a pin for each of the corresponding port pins 0-7, +3.3 V and digital ground. See Table 5 for the J15 pin connections.

Pin# Description P0.0 2 P0.1 3 P0.2 P0.3 4 5 P<sub>0.4</sub> P0.5 6 7 P0.6 P0.7 8 9 +3 VD (+3.3 V) GND (Ground) 10

**Table 5. J15 Port Connector Pin Descriptions**

## 9.9. Power Supply Selector (J2)

The C8051F064 evaluation board can be powered from either the DEBUG or DATA ports through the USB connection. The J2 header allows the user to select between these ports. Each configuration includes an on-board voltage regulator to supply 3.3 V to the board. To power the 3.3 V supply from the DATA port, place a shorting block on J2, Pin 1 and Pin 2. To supply the 3.3 V supply from the DEBUG port, place a shorting block on J2, Pin 2 and Pin 3.

Note: If supplying the 3.3 V supply from an off-board source via the J3 terminal block, do not place a shorting block on J2.

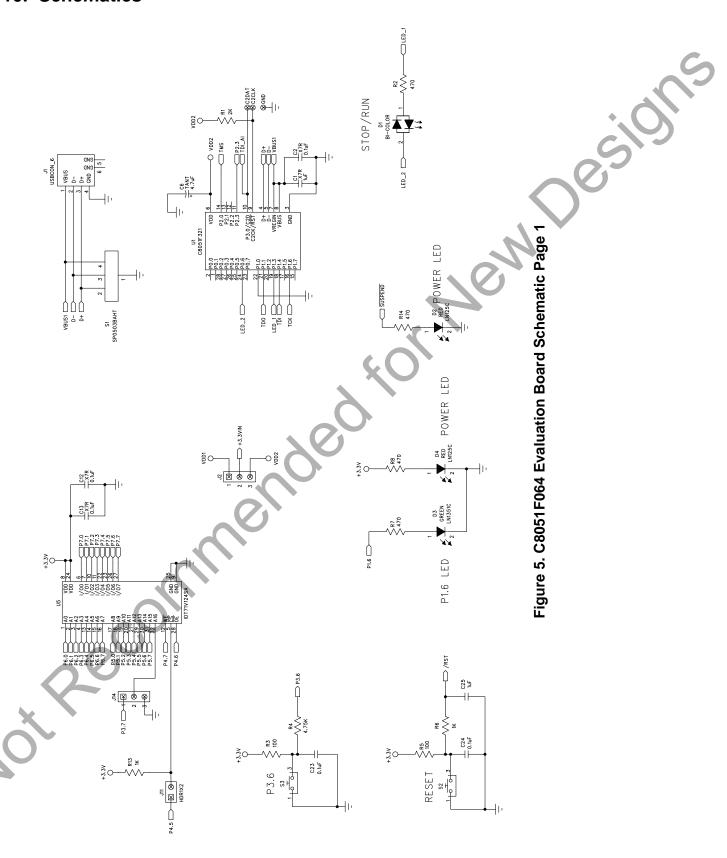

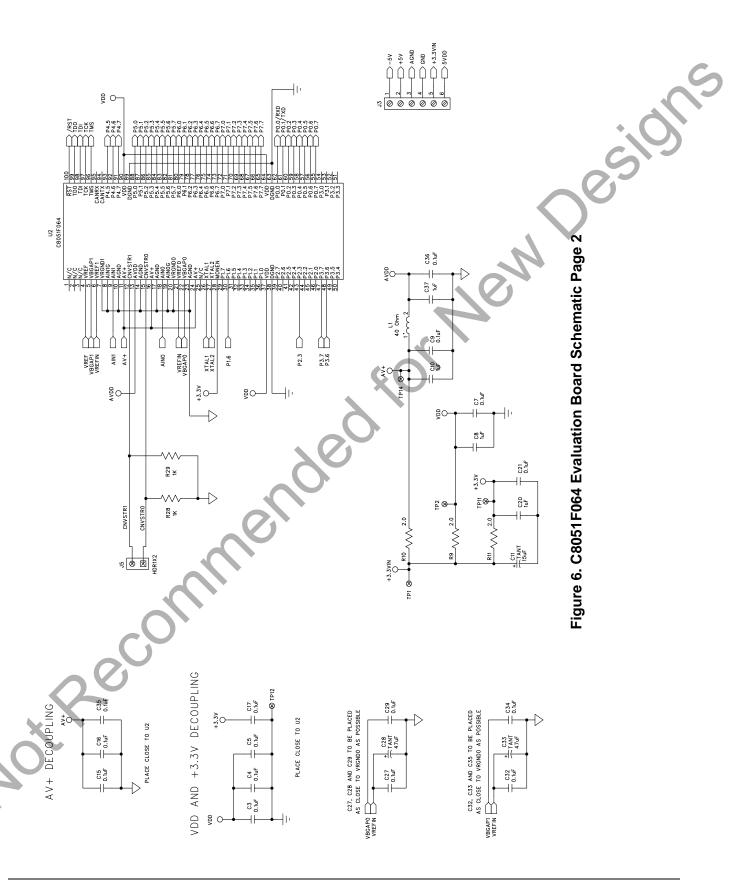

# 10. Schematics

Rev. 0.4

15

# **DOCUMENT CHANGE LIST**

### Revision 0.1 to Revision 0.2

Changed "6' USB Cables (2)" to "USB Cable" under

"2. Kit Contents" on page 1.

## Revision 0.2 to Revision 0.4

- Added Relevant Devices section.

- Changed Section 3 to "Getting Started."

- Updated Section 4 to include latest VCP driver installation instructions

- Changed Section 6 to "Software Overview."

- Updated Evaluation Compiler restrictions in Section 6.2.2.

- Added overview of Configuration Wizard 2 and Keil uVision Drivers to section 6.

- Created new Section 7.