# RF Low Noise FET CE3521M4

## 20 GHz Low Noise FET in Dual Mold Plastic PKG

#### DESCRIPTION

- Low Noise and High Gain

- Original Dual Mold Plastic package

#### **FEATURES**

• Low noise figure and high associated gain: NF = 0.70 dB TYP., Ga = 11.9 dB TYP.  $@V_{DS} = 2 V$ , I<sub>D</sub> = 10 mA, f = 20 GHz

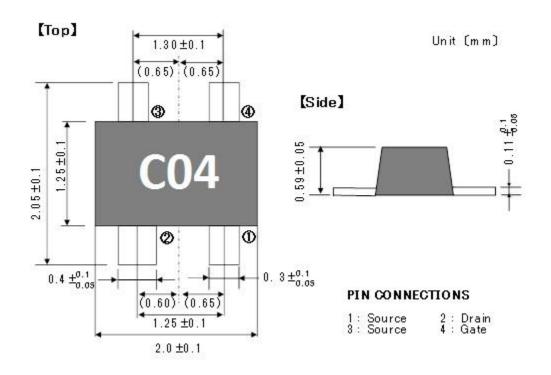

#### PACKAGE

• Flat-lead 4-pin thin-type super minimold package

#### **APPLICATIONS**

- DBS LNB gain-stage, Mix-stage

- Low noise amplifier for microwave communication systems

#### **ORDERING INFORMATION**

| Part Number | Order Number | Package         | Marking | Description                                 |

|-------------|--------------|-----------------|---------|---------------------------------------------|

| CE3521M4    | CE3521M4-C2  | Flat-lead 4-pin | C04     | <ul> <li>Embossed tape 8 mm wide</li> </ul> |

|             |              | thin-type super |         | Pin 1 (source), Pin 2 (drain)               |

|             |              | minimold        |         | face the perforation side of                |

|             |              | package         |         | the tape                                    |

|             |              |                 |         | MOQ 15 kpcs/reel                            |

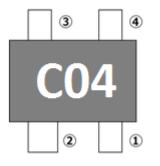

### PIN CONFIGURATION AND INTERNAL BLOCK DIAGRAM

| Pin No. | Pin Name |

|---------|----------|

| 1       | Source   |

| 2       | Drain    |

| 3       | Source   |

| 4       | Gate     |

#### **ABSOLUTE MAXIMUM RATINGS**

#### $(TA = +25^{\circ}C, unless otherwise specified)$

| Parameter               | Symbol           | Rating                      | Unit |

|-------------------------|------------------|-----------------------------|------|

| Drain to Source Voltage | V <sub>DS</sub>  | 4.0                         | V    |

| Gate to Source Voltage  | V <sub>GS</sub>  | -3.0                        | V    |

| Drain Current           | Ι <sub>D</sub>   | I <sub>DSS</sub>            | mA   |

| Gate Current            | l <sub>G</sub>   | 80                          | μA   |

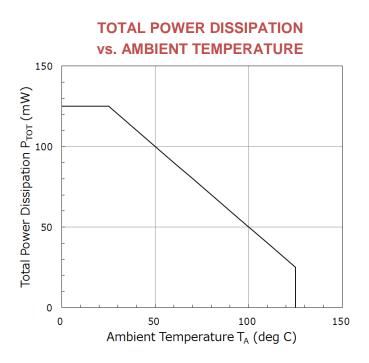

| Total Power Dissipation | P <sub>tot</sub> | 125                         | mW   |

| Channel Temperature     | T <sub>ch</sub>  | +150                        | °C   |

| Storage Temperature     | T <sub>stg</sub> | -55 to +125                 | °C   |

| Operation Temperature   | T <sub>op</sub>  | -55 to +125 <sup>Note</sup> | °C   |

Note Refer to Total Power Dissipation vs. Ambient Temperature graph on page 4

#### **RECOMMENDED OPERATING RANGE**

(TA = +25°C, unless otherwise specified) Parameter Symbol MIN. TYP. MAX. Unit Drain to Source Voltage V  $V_{\text{DS}}$ +1 +2 +3 **Drain Current** 5 10 15 mΑ  $I_{D}$

#### This document is subject to change without notice.

## **ELECTRICAL CHARACTERISTICS**

#### $(TA = +25^{\circ}C, unless otherwise specified)$

| Parameter                      | Symbol               | Condition                        | MIN.  | TYP.  | MAX.  | Unit |

|--------------------------------|----------------------|----------------------------------|-------|-------|-------|------|

| Gate to Source Leak Current    | I <sub>GSO</sub>     | V <sub>GS</sub> = -3.0V          | -     | 0.4   | 10    | μA   |

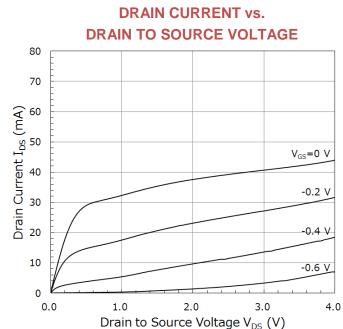

| Saturated Drain Current        | I <sub>DSS</sub>     | $V_{DS} = 2V, V_{GS} = 0V$       | 23    | 40    | 57    | mA   |

| Gate to Source Cut-off Voltage | V <sub>GS(off)</sub> | $V_{DS} = 2V, I_{D} = 100 \mu A$ | -1.10 | -0.75 | -0.39 | V    |

| Transconductance               | Gm                   | $V_{DS} = 2V, I_{D} = 10mA$      | 47    | 62    | -     | mS   |

| Noise Figure                   | NF                   | $V_{DS} = 2V, I_{D} = 10mA,$     | -     | 0.70  | 1.05  | dB   |

| Associated Gain                | Ga                   | f = 20GHz                        | 9.9   | 11.9  | -     | dB   |

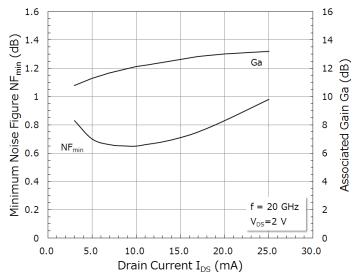

#### **TYPICAL CHARACTERISTICS**:

(TA=+25℃, unless otherwise specified)

DRAIN CURRENT vs. GATE TO SOURCE VOLTAGE

MINIMUM NOISE FIGURE & ASSOCIATED GAIN vs. DRAIN CURRENT

#### **S-PARAMETERS**

S-Parameters are available on the CEL web site.

#### **RECOMMENDED SOLDERING CONDITIONS**

Recommended Soldering Conditions are provided on the CEL web site.

#### PACKAGE DIMENSIONS

Flat-lead 4-pin thin-type super minimold package

#### **REVISION HISTORY**

| Version               | Change to current version                         | Page(s) |

|-----------------------|---------------------------------------------------|---------|

| CDS-0020-03 (Issue A) | Initial datasheet                                 | N/A     |

| February 19, 2016     |                                                   |         |

| CDS-0020-03 (Issue B) | Updated Marking Information                       | 1, 2, 3 |

| April 27, 2016        |                                                   |         |

| CDS-0020-04 (Issue A) | Updated Specs in "Absolute Maximum Ratings" Table | 2, 4, 5 |

| July 29, 2016         | Added "Typical Characteristics" section (graphs)  |         |

| -                     | Added "S-Parameters" and "Recommended Soldering   |         |

|                       | Conditions" sections                              |         |

#### [CAUTION]

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice.

- You should not alter, modify, copy, or otherwise misappropriate any CEL product, whether in whole or in part.

- CEL does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of CEL products or technical information described in this document. No license, expressed, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of CEL or others.

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the

operation of semiconductor products and application examples. You are fully responsible for the incorporation of

these circuits, software, and information in the design of your equipment. CEL assumes no responsibility for any

losses incurred by you or third parties arising from the use of these circuits, software, or information.

- CEL has used reasonable care in preparing the information included in this document, but CEL does not warrant that such information is error free. CEL assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- Although CEL endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions.

Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a CEL product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures

Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- Please use CEL products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive.

CEL assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of CEL.

- Please contact CEL if you have any questions regarding the information contained in this document or CEL products, or if you have any other inquiries.