# 1-Mbit (128K × 8) Quad SPI nvSRAM with Real Time Clock

#### **Features**

- Density

- □ 1 Mbit (128K × 8)

- Bandwidth

- □ 108-MHz high-speed interface

- □ Read and write at 54 MBps

- Serial Peripheral Interface

- Clock polarity and phase modes 0 and 3

- □ Multi I/O option Single SPI (SPI), Dual SPI (DPI), and Quad SPI (QPI)

- High reliability

- □ Infinite read, write, and RECALL cycles

- One million STORE cycles to nonvolatile elements (SONOS FLASH Quantum trap)

- □ Data retention: 20 years at 85 °C

- Read

- □ Commands: Standard, Fast, Dual I/O, and Quad I/O

- □ Modes: Burst Wrap, Continuous (XIP)

- Write

- □ Commands: Standard, Fast, Dual I/O, and Quad I/O

- □ Modes: Burst Wrap

- Data protection

- ☐ Hardware: Through Write Protect Pin (WP)

- ☐ Software: Through Write Disable instruction

- Block Protection: Status Register bits to control protection

- Special instructions

- □ STORE/RECALL: Transfer data between SRAM and Quantum Trap nvSRAM

- □ Serial Number: 8-byte customer selectable (OTP)

- □ Identification Number: 4-byte Manufacturer ID and Product ID

- Store from SRAM to nonvolatile SONOS FLASH Quantum Trap

- □ AutoStore: Initiated automatically at power-down with a small capacitor (V<sub>CAP</sub>)

- □ Software: Using SPI instruction (STORE)

- ☐ Hardware: HSB pin

- Recall from nonvolatile SONOS FLASH Quantum Trap to SRAM

- ☐ Auto RECALL: Initiated automatically at power-up

- □ Software: Using SPI instruction (RECALL)

- Low-power modes

- □ Sleep: Average current = 380 μA at 85 °C

- □ Hibernate: Average current = 8 µA at 85 °C

- Operating supply voltages

- $\hfill\Box$  Core V\_CC: 2.7 V to 3.6 V  $\hfill\Box$  I/O V\_CCQ: 1.71 V to 2.0 V

- Temperature range

- □ Industrial: -40 °C to 85 °C

- Packages

- □ 16-pin SOIC

#### **Functional Overview**

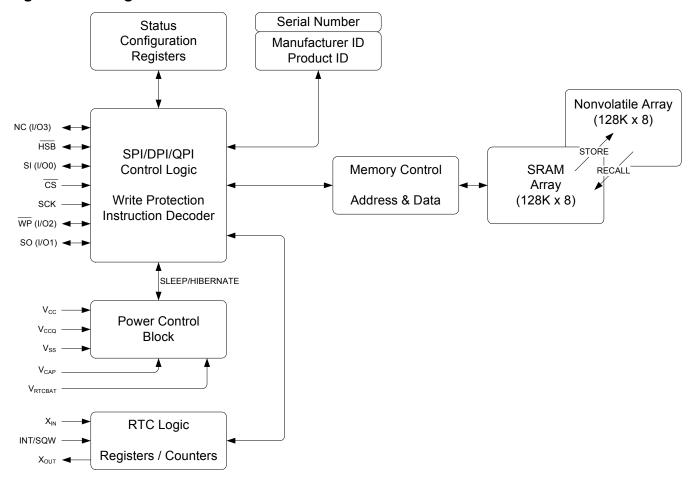

The Cypress CY14V101PS combines a 1-Mbit nvSRAM with a QPI interface. The QPI allows writing and reading the memory in either a single (one I/O channel for one bit per clock cycle), dual (two I/O channels for two bits per clock cycle), or quad (four I/O channels for four bits per clock cycle) through the use of selected opcodes.

The memory is organized as 128 Kbytes each consisting of SRAM and nonvolatile SONOS FLASH Quantum Trap cells. The SRAM provides infinite read and write cycles, while the nonvolatile cells provide highly reliable storage of data. Data transfers from SRAM to the nonvolatile cells (STORE operation) take place automatically at power-down. On power-up, data is restored to the SRAM from the nonvolatile cells (RECALL operation). The user can initiate the STORE and RECALL operations through SPI instructions.

## **Logic Block Diagram**

## **Contents**

| Pinout4                                           |

|---------------------------------------------------|

| Pin Definitions4                                  |

| Device Operation6                                 |

| SRAM Write6                                       |

| SRAM Read6                                        |

| STORE Operation6                                  |

| AutoStore Operation6                              |

| Software STORE Operation7                         |

| Hardware STORE and HSB Pin Operation7             |

| RECALL Operation7                                 |

| Hardware RECALL (Power-Up)7                       |

| Software RECALL7                                  |

| Disabling and Enabling AutoStore7                 |

| Quad Serial Peripheral Interface8                 |

| SPI Overview8                                     |

| Dual and Quad I/O Modes10                         |

| SPI Modes10                                       |

| SPI Operating Features11                          |

| Power-Up11                                        |

| Power-Down11                                      |

| Active Power Mode and Standby State11             |

| SPI Functional Description12                      |

| Status Register                                   |

| Write Disable (WRDI) Instruction                  |

| Write Enable (WREN) Instruction                   |

| Enable DPI (DPIEN) Instruction                    |

| Enable QPI (QPIEN) Instruction                    |

| Enable SPI (SPIEN) Instruction                    |

| SPI Memory Read Instructions                      |

| Read Instructions                                 |

| Fast Read Instructions                            |

|                                                   |

| Write Instructions                                |

| Software Reset (RESET) Instruction                |

|                                                   |

| Default Recovery Instruction                      |

|                                                   |

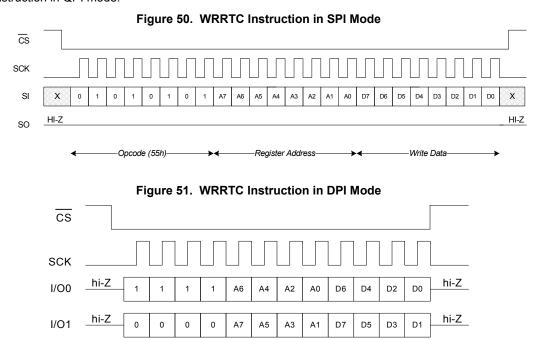

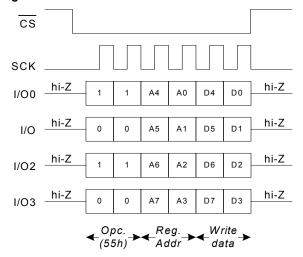

| Write Real Time Clock (WRRTC) Instruction31       |

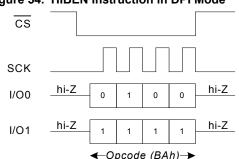

| Hibernate (HIBEN) Instruction                     |

| Sleep (SLEEP) Instruction                         |

| Register Instructions                             |

| Read Status Register (RDSR) Instruction           |

| Write Status Register (WRSR) Instruction          |

| Read Configuration Register (RDCR) Instruction36  |

| Write Configuration Register (WRCR) Instruction37 |

| Identification Register (RDID) Instruction        |

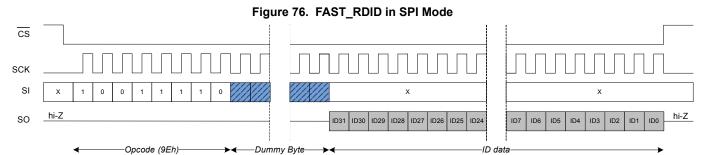

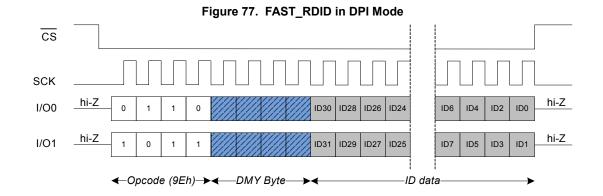

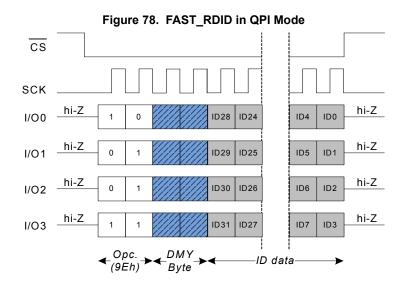

| Identification Register (FAST_RDID) Instruction39 |

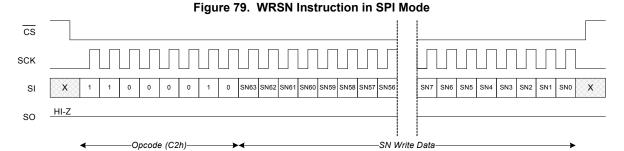

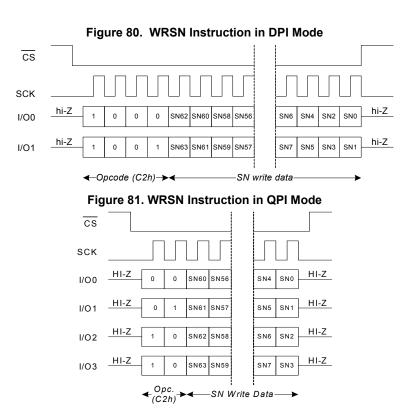

| Serial Number Register Write (WRSN) Instruction40 |

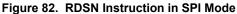

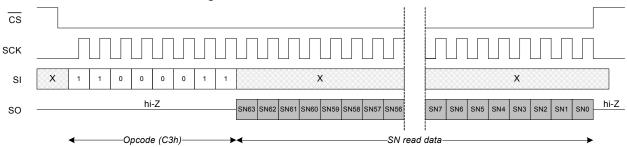

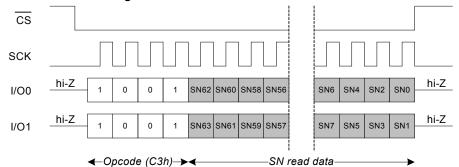

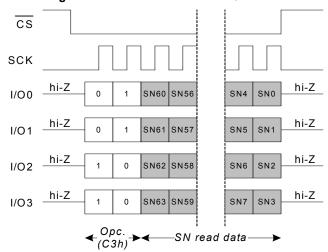

| Serial Number Register Read (RDSN) Instruction41  |

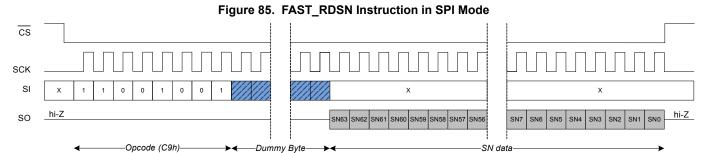

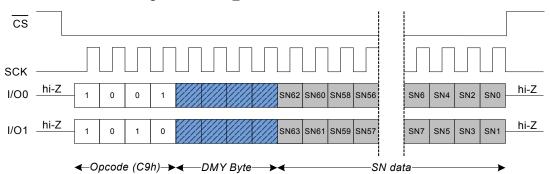

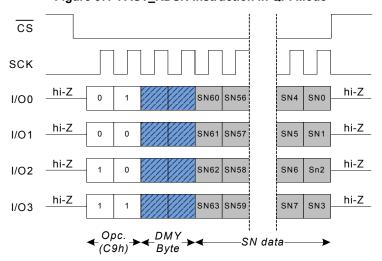

| Fast Read Serial Number Register (FAST_RDSN)      |

| Instruction                                       |

| NV Specific Instructions43                        |

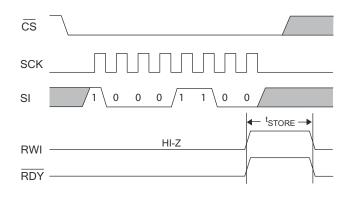

| Software Store (STORF) Instruction 43             |

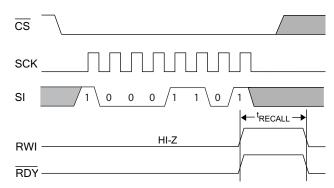

| Software Recall (RECALL) Instruction                                                                                      | 43                                 |

|---------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Autostore Enable (ASEN) Instruction                                                                                       | 44                                 |

| Autostore Disable (ASDI) Instruction                                                                                      | 44                                 |

| Real Time Clock Operation                                                                                                 |                                    |

| nvTIME Operation                                                                                                          | 45                                 |

| Clock Operations                                                                                                          | 45                                 |

| Reading the Clock                                                                                                         | 45                                 |

| Setting the Clock                                                                                                         | 45                                 |

| Backup Power                                                                                                              |                                    |

| Stopping and Starting the Oscillator                                                                                      | 45                                 |

| Calibrating the Clock                                                                                                     | 46                                 |

| Alarm                                                                                                                     | 46                                 |

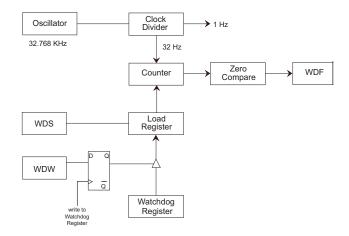

| Watchdog Timer                                                                                                            | 46                                 |

| Programmable Square Wave Generator                                                                                        | 47                                 |

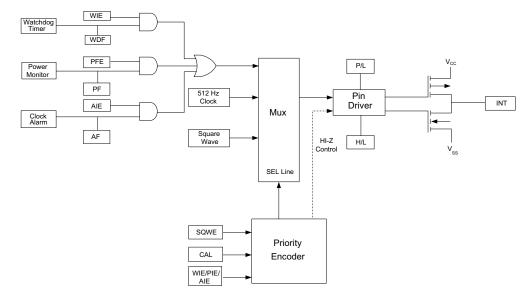

| Power Monitor                                                                                                             | 47                                 |

| Backup Power Monitor                                                                                                      | 47                                 |

| Interrupts                                                                                                                | 47                                 |

| Interrupt Register                                                                                                        |                                    |

| Flags Register                                                                                                            | 48                                 |

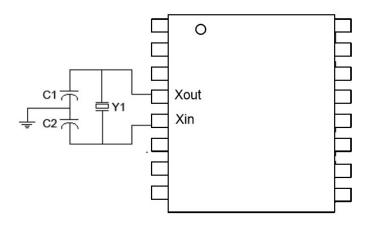

| RTC External Components                                                                                                   | 49                                 |

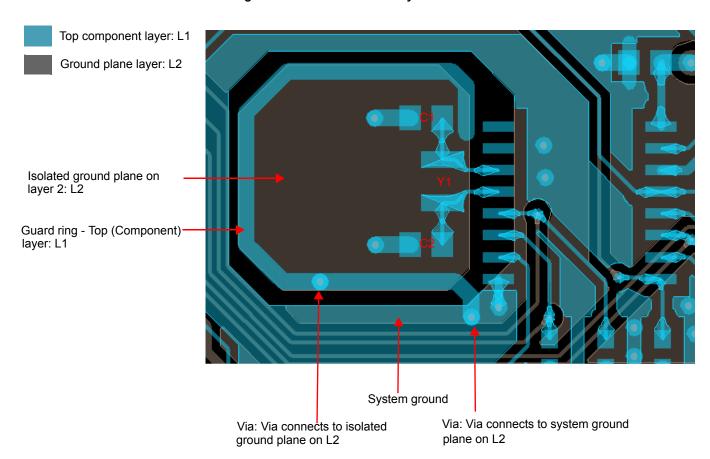

| PCB Design Considerations for RTC                                                                                         | 50                                 |

| Layout Requirements                                                                                                       | 50                                 |

| Maximum Ratings                                                                                                           | 55                                 |

| Operating Range                                                                                                           | 55                                 |

| DC Specifications                                                                                                         |                                    |

| Data Retention and Endurance                                                                                              |                                    |

| Capacitance                                                                                                               | 56                                 |

| Thermal Resistance                                                                                                        | 56                                 |

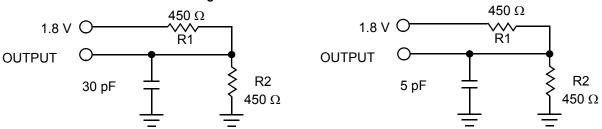

| AC Test Loads and Waveforms                                                                                               | 57                                 |

| AC Test Conditions                                                                                                        | 57                                 |

| RTC Characteristics                                                                                                       | 57                                 |

| AC Switching Characteristics                                                                                              | 58                                 |

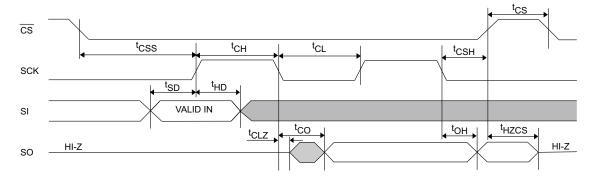

| Switching Waveforms                                                                                                       |                                    |

| AutoStore or Power-Up RECALL                                                                                              | 59                                 |

| Switching Waveforms                                                                                                       | 60                                 |

| Software Controlled STORE and RECALL Cycles                                                                               | 61                                 |

| Switching Waveforms                                                                                                       | 61                                 |

| Hardware STORE Cycle                                                                                                      |                                    |

| Switching Waveforms                                                                                                       | 62                                 |

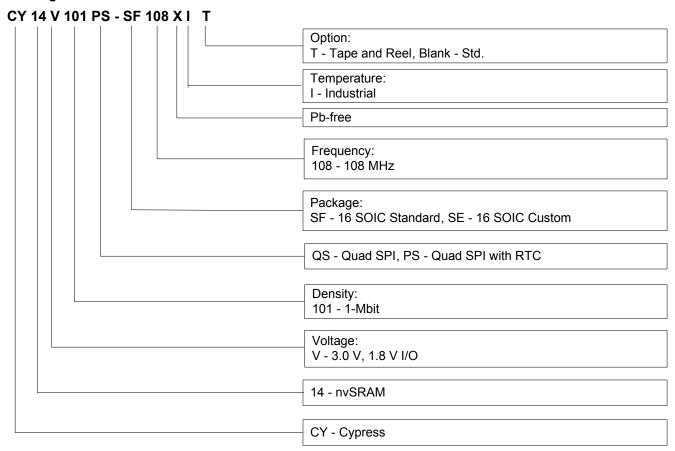

| Ordering Information                                                                                                      |                                    |

| Ordering Code Definitions                                                                                                 |                                    |

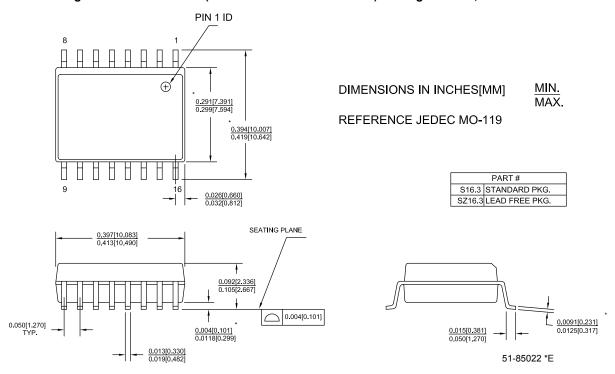

| Package Diagrams                                                                                                          |                                    |

| Acronyms                                                                                                                  |                                    |

| Document Conventions                                                                                                      |                                    |

| Units of Measure                                                                                                          |                                    |

|                                                                                                                           |                                    |

| Document History Page                                                                                                     | 66                                 |

| Document History PageSales, Solutions, and Legal Information                                                              | 66<br>67                           |

| Document History Page  Sales, Solutions, and Legal Information  Worldwide Sales and Design Support                        | <b>66</b><br><b>67</b><br>67       |

| Sales, Solutions, and Legal Information                                                                                   | <b>66</b><br><b>67</b><br>67<br>67 |

| Document History Page Sales, Solutions, and Legal Information Worldwide Sales and Design Support Products PSoC® Solutions | <b>66 67</b> 67 67                 |

| Sales, Solutions, and Legal Information                                                                                   | <b>66 67</b> 67 67 67              |

## **Pinout**

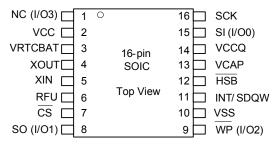

Figure 1. 16-pin SOIC Pinout

#### **Pin Definitions**

| Pin Name            | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Input        | Not connected. In Single or Dual mode, this pin is not connected and left floating. These two modes do not support QSPI instructions.                                                                                                                                                                                                                                                                                |

| NC (I/O3)           | Input/Output | I/O3: When the part is in Quad mode, the NC (I/O3) pin becomes I/O3 pin and acts as input/output. In Quad mode supporting SPI/DPI instructions, this pin needs to be tri-stated while CS is enabled.                                                                                                                                                                                                                 |

| V <sub>CCQ</sub>    | Power Supply | Power supply for the I/Os of the device.                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub>     | Power Supply | Power supply to the core of the device.                                                                                                                                                                                                                                                                                                                                                                              |

| CS                  | Input        | Chip Select. Activates the device when pulled LOW. Driving this pin HIGH puts the device in standby state.                                                                                                                                                                                                                                                                                                           |

|                     | Output       | Serial Output. Pin for output of data through SPI.                                                                                                                                                                                                                                                                                                                                                                   |

| SO (I/O1)           | Input/Output | I/O1: When the part is in dual or quad mode, the SO (I/O1) pin becomes I/O1 pin and acts as input/output.                                                                                                                                                                                                                                                                                                            |

|                     | Input        | Write Protect. Implements hardware write-protection in SPI/DPI modes.                                                                                                                                                                                                                                                                                                                                                |

| WP (I/O2)           | Input/Output | I/O2: When the part is in quad mode, the WP (I/O2) pin becomes an I/O2 pin and acts as input/output.                                                                                                                                                                                                                                                                                                                 |

| $V_{SS}$            | Ground       | Power supply ground to the core and I/Os of the device.                                                                                                                                                                                                                                                                                                                                                              |

| HSB                 | Input/Output | Hardware STORE Busy: Output: Indicates the busy status of nvSRAM when LOW. After each Hardware and Software STORE operation, HSB is driven HIGH for a short time (t <sub>HHHD</sub> ) with standard output HIGH current and then a weak internal pull-up resistor keeps this pin HIGH (external pull-up resistor connection is optional). Input: Hardware STORE can be initiated by pulling this pin LOW externally. |

| V <sub>CAP</sub>    | Power Supply | AutoStore Capacitor. Supplies power to the nvSRAM during power loss to STORE data from the SRAM to nonvolatile elements. If AutoStore is not needed, this pin must be left as No Connect. It must never be connected to ground.                                                                                                                                                                                      |

| V <sub>RTCbat</sub> | Power supply | Battery backup for RTC.                                                                                                                                                                                                                                                                                                                                                                                              |

| Xout                | Output       | Crystal output connection. Left unconnected if RTC feature is not used.                                                                                                                                                                                                                                                                                                                                              |

| Xin                 | Input        | Crystal input connection. Left unconnected if RTC feature is not used.                                                                                                                                                                                                                                                                                                                                               |

## Pin Definitions (continued)

| Pin Name       | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT/SQW Output |              | Interrupt output/calibration/square wave. Programmable to respond to the clock alarm, the watchdog timer, and the power monitor. Also programmable to either active HIGH (push or pull) or LOW (open drain). In calibration mode, a 512-Hz square wave is driven out. In the square wave mode, you may select a frequency of 1 Hz, 512 Hz, 4,096 Hz, or 32,768 Hz to be used as a continuous output. |

|                |              | Left unconnected if RTC feature is not used.                                                                                                                                                                                                                                                                                                                                                         |

|                | Input        | Serial Input. Pin for input of all SPI instructions and data.                                                                                                                                                                                                                                                                                                                                        |

| SI (I/O0)      | Input/Output | I/O0: When the part is in dual or quad mode, the SI (I/O0) pin becomes I/O0 pin and acts as input/output.                                                                                                                                                                                                                                                                                            |

| SCK            | Input        | Serial Clock. Runs at speeds up to a maximum of $f_{SCK}$ . Serial input is latched at the rising edge of this clock. Serial output is driven at the falling edge of the clock.                                                                                                                                                                                                                      |

| NC             | -            | Not connected.                                                                                                                                                                                                                                                                                                                                                                                       |

| RFU            | _            | Reserved for future use.                                                                                                                                                                                                                                                                                                                                                                             |

## **Device Operation**

CY14V101PS is a 1-Mbit quad serial interface nvSRAM memory with a SONOS FLASH nonvolatile element interleaved with an SRAM element in each memory cell. All the reads and writes to nvSRAM happen to the SRAM, which gives nvSRAM the unique capability to handle infinite writes to the memory. The data in SRAM is secured by a STORE sequence, which transfers the data in parallel to the nonvolatile cells. A small capacitor ( $V_{CAP}$ ) is used to AutoStore the SRAM data into the nonvolatile cells when power goes down providing data integroty. The nonvolatile cells are built in the reliable SONOS technology make nvSRAM the ideal choice for data storage.

The 1-Mbit memory array is organized as 128 Kbytes. The memory can be accessed through a standard SPI interface (Single mode, Dual mode, and Quad mode) up to clock speeds of 40-MHz with zero-cycle latency for read and write operations. This SPI interface also supports 108-MHz operations (Single mode, Dual mode, and Quad mode) with cycle latency for read operations only. The device operates as a SPI slave and supports SPI modes 0 and 3 (CPOL, CPHA = [0, 0] and [1, 1]). All instructions are executed using Chip Select (CS), Serial Input (SI) (I/O0), Serial Output (SO) (I/O1), and Serial Clock (SCK) pins in single and dual modes. Quad mode uses WP (I/O2) and I/O3 pins as well for command, address, and data entry.

The device uses SPI opcodes for memory access. The opcodes support SPI, Dual Data, Dual Addr/Data, Dual I/O, Quad Data, Quad Addr/Data, and Quad I/O modes for read and write operations. In addition, four special instructions are included that allow access to nvSRAM specific functions: STORE, RECALL, AutoStore Disable (ASDI), and AutoStore Enable (ASEN).

The device has built-in data security features. <u>It</u> provides hardware and software write-protection through the WP pin and WRDI instruction respectively. Furthermore, the memory array block is write-protected through Status register block protect bits.

#### **SRAM Write**

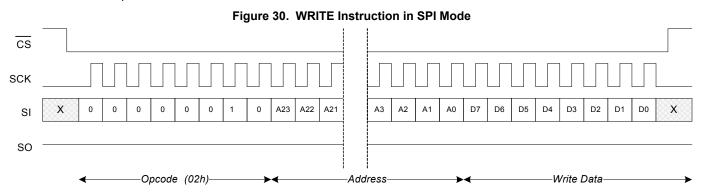

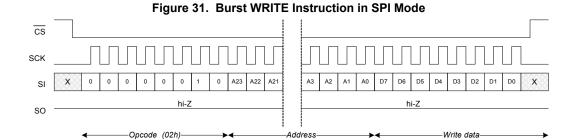

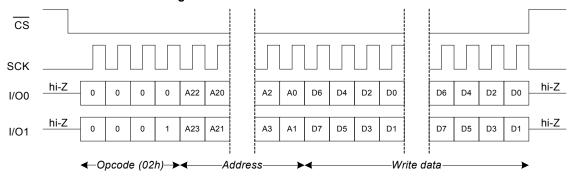

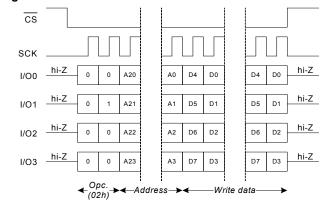

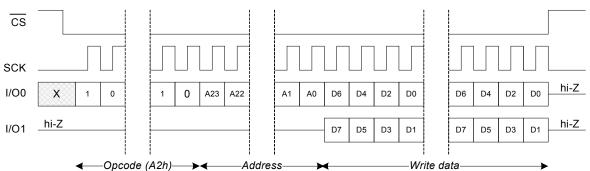

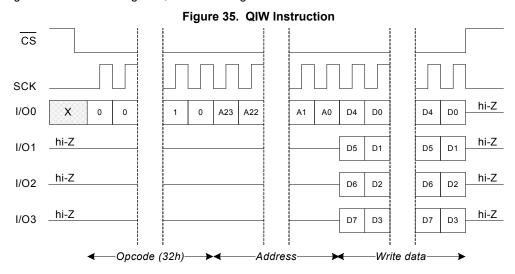

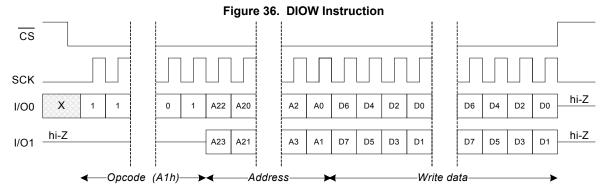

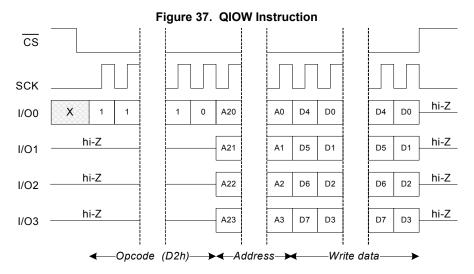

All writes to nvSRAM are carried out on the SRAM cells and do not use any endurance cycles of the SONOS FLASH nonvolatile memory. This allows you to perform infinite write operations. A write cycle is initiated through one of the Write instructions: WRITE, DIW, QIW, DIOW, and QIOW. The Write instructions consist of a write opcode, three bytes of address, and one byte of data. Write to nvSRAM is done at SPI bus speed with zero-cycle latency.

The device allows burst mode writes. This enables write operations on consecutive addresses without issuing a new Write instruction. When the last address in memory is reached in burst mode, the address rolls over to 0x00000 and the device continues to write.

The SPI write cycle sequence is defined explicitly in the nvSRAM Read Write Instructions in "SPI Functional Description" on page 12.

#### **SRAM Read**

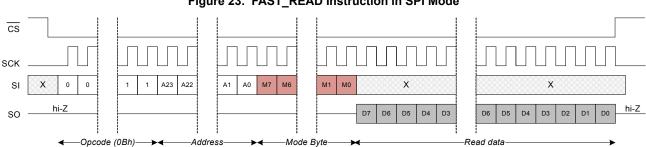

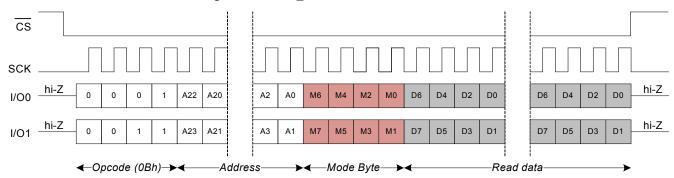

All reads to nvSRAM are carried out on the SRAM cells at SPI bus speeds. Read instruction (READ) executes at 40-MHz with zero cycle latency. It consists of a Read opcode byte followed by three bytes of address. The data is read out on the data output pin/pins.

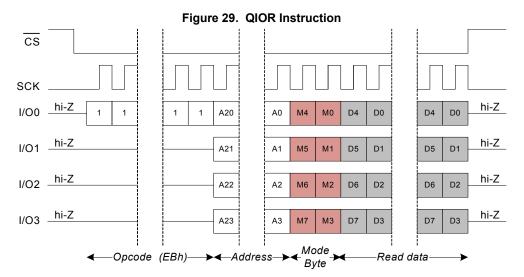

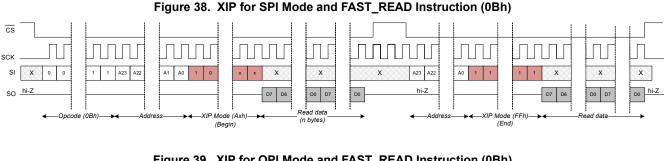

Speeds higher than 40 MHz (up to 108 MHz) require Fast Read instructions: FAST\_READ, DOR, QOR, DIOR, and QIOR. The Fast Read instructions consist of a Fast Read opcode byte, three bytes of address, and a dummy/mode byte. The data is read out on the data output pin/pins.

The device allows burst mode reads. This enables read operations on consecutive addresses without issuing a new Read instruction. When the last address in memory is reached in burst mode, the address rolls over to 0x00000 and the device continues to read.

The SPI read cycle sequence is defined explicitly in the nvSRAM Read Write Instructions in "SPI Functional Description" on page 12.

#### **STORE Operation**

STORE operation transfers the data from the SRAM to the nonvolatile cells. The device stores data using one of the three STORE operations: AutoStore, activated on device power-down (requires  $V_{CAP}$ ); Software STORE, activated by a <u>STORE</u> instruction; and Hardware STORE, activated by the HSB pin. During the STORE cycle, the nonvolatile cell is first erased and then programmed. After a STORE cycle is initiated, read/write to the device is inhibited until the cycle is completed.

The HSB signal or the WIP bit in Status Register can be monitored by the system to detect if a STORE cycle is in progress. The busy status of nvSRAM is indicated by HSB being pulled LOW or the WIP bit being set to '1'. To avoid unnecessary nonvolatile STOREs, AutoStore and Hardware STORE operations are ignored unless at least one SRAM write operation has taken place since the most recent STORE cycle. However, software initiated STORE cycles are performed regardless of whether a SRAM write operation has taken place.

#### **AutoStore Operation**

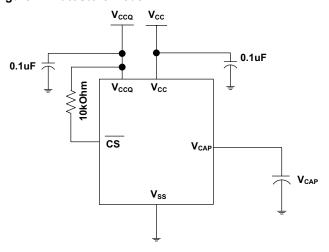

The AutoStore operation is a unique feature of nvSRAM, which automatically stores the SRAM data to the SONOS FLASH nonvolatile cells during power-down. This STORE makes use of an external capacitor ( $V_{CAP}$ ) and enables the device to safely STORE the data in the nonvolatile memory when power goes down.

During normal operation, the device draws current from  $V_{CC}$  to charge the capacitor connected to the  $V_{CAP}$  pin. When the voltage on the  $V_{CC}$  pin drops below  $V_{SWITCH}$  during power-down, the device inhibits all memory accesses to nvSRAM and automatically performs a STORE operation using the charge from the  $V_{CAP}$  capacitor. The AutoStore operation is not initiated if a write cycle has not been performed since last RECALL.

**Note** If a capacitor is not connected to the  $V_{CAP}$  pin, AutoStore must be disabled by issuing the AutoStore Disable instruction (Autostore Disable (ASDI) Instruction on page 44). If AutoStore is enabled without a capacitor on the  $V_{CAP}$  pin, the device attempts AutoStore without sufficient charge to complete the operation. This will corrupt the data stored in the memory array along with the serial number and Status Register. Updating them will be required to resume normal functionality.

Figure 2 shows the connection of the storage capacitor ( $V_{CAP}$ ) for AutoStore operation. Refer to on page 55 for the size of the  $V_{CAP}$

Figure 2. AutoStore Mode

## **Software STORE Operation**

Software STORE allows an instruction-based STORE operation. It is initiated by executing a STORE instruction, irrespective of whether a write has been previously performed.

A STORE cycle takes  $t_{STORE}$  time to complete, during which all the memory accesses to  $nv\underline{SRA}M$  are inhibited. The WIP bit of the Status Register or the  $\overline{HSB}$  pin may be polled to find the Ready or Busy status. After the  $t_{STORE}$  cycle time is completed, the nvSRAM is ready for normal operations.

#### Hardware STORE and HSB Pin Operation

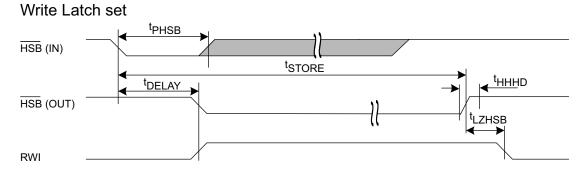

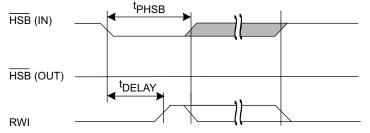

The HSB pin in the device is a dual-purpose pin used to either initiate a STORE operation or to poll STORE/RECALL completion status. If a STORE or RECALL is not in progress, the HSB pin can be driven low to initiate a Hardware STORE cycle.

Detecting a low on HSB, nvSRAM will start a STORE operation after  $t_{\mbox{\scriptsize DELAY}}$  duration. A hardware STORE cycle is only possible if a SRAM write operation has been performed since the last STORE/RECALL cycle. This allows for optimizing the SONOS FLASH endurance cycles. All reads and writes to the memory are inhibited for  $t_{\mbox{\scriptsize STORE}}$  duration. The HSB pin also acts as an open drain driver (internal 100-k $\Omega$  weak pull-up resistor) that is internally driven LOW to indicate a busy condition when the STORE/RECALL is in progress.

**Note** After each Hardware and Software STORE operation,  $\overline{\text{HSB}}$  is driven HIGH for a short time (t<sub>HHHD</sub>) with standard output HIGH current and then remains HIGH by an internal 100-k $\Omega$  pull-up resistor.

**Note** For successful last data byte STORE, a hardware STORE should be initiated at least one clock cycle after the last data bit D0 is received.

**Note** It is recommended to perform a Hardware STORE only when the device is in Standby state. Execute-in-place (XIP) should be exited as well.

Upon completion of the STORE operation, the nvSRAM memory access is inhibited for  $t_{\rm LZHSB}$  time after HSB pin returns HIGH. The HSB pin must be left unconnected if not used.

#### **RECALL Operation**

A RECALL operation transfers the data stored in the nonvolatile cells to the SRAM cells. A RECALL may be initiated in two ways: Hardware RECALL, initiated on power-up and Software RECALL, initiated by a SPI RECALL instruction.

Internally, RECALL is a two-step procedure. First, the SRAM data is cleared (set to '0'). Next, the nonvolatile information is transferred into the SRAM cells. All memory accesses are inhibited while a RECALL cycle is in progress. The RECALL operation does not alter the data in the nonvolatile elements.

#### **Hardware RECALL (Power-Up)**

During power-up, when  $V_{CC}$  crosses  $V_{SWITCH}$ , an automatic RECALL sequence is initiated, which transfers the content of nonvolatile cells to the SRAM cells.

A Power-Up RECALL cycle takes  $t_{\text{FA}}$  time to complete and the memory access is disabled during this time. The HSB pin is used to detect the ready status of the device.

#### **Software RECALL**

Software RECALL allows you to initiate a RECALL operation to restore the content of the nonvolatile memory to the SRAM. A Software RECALL is issued by using the RECALL instruction.

A Software RECALL takes  $t_{\mbox{\scriptsize RECALL}}$  time to complete during which all memory accesses to nvSRAM are inhibited.

#### **Disabling and Enabling AutoStore**

If the application does not require the AutoStore feature, it can be disabled by using the ASDI instruction. If this is done, the nvSRAM does not perform a STORE operation at power-down.

AutoStore can be re-enabled by using the ASEN instruction. However, ASEN and ASDI operations require a STORE operation to make them nonvolatile.

**Note** The device has AutoStore enabled and 0x00 written to all cells from the factory.

**Note** If AutoStore is disabled and  $V_{CAP}$  is not required, then the  $V_{CAP}$  pin must be left open. The  $V_{CAP}$  pin must never be connected to ground. The Power-Up RECALL operation cannot be disabled.

## **Quad Serial Peripheral Interface**

#### **SPI Overview**

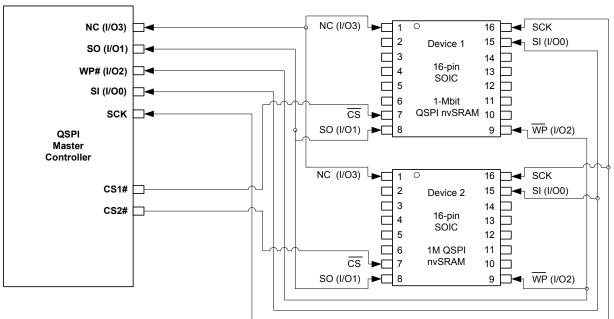

The SPI is a four-pin interface with Chip Select  $(\overline{CS})$ , Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins. The device provides serial access to the nvSRAM through the SPI interface. The SPI bus on the device can run at speed up to 108 MHz.

The SPI is a synchronous serial interface, which uses clock and data pins for memory access and supports multiple devices on the data bus. A device on the SPI bus is activated using the CS pin.

The relationship between chip select, clock, and data is dictated by the SPI mode. This device supports SPI modes 0 and 3. In both these modes, data is clocked into the nvSRAM on the rising edge of SCK starting from the first rising edge after CS goes active.

The SPI protocol is controlled by opcodes. These opcodes specify the commands from the bus master to the slave device. After CS is activated, the first byte transferred from the bus master is the opcode. Following the opcode, any addresses and data are then transferred. The CS must go inactive after an operation is complete and before a new opcode can be issued. The commonly used terms in the SPI protocol are described in the following sections.

#### SPI Master

The SPI master device controls the operations on an SPI bus. An SPI bus may have only one master with one or more slave devices. All the slaves share the same SPI bus lines <u>and</u> the master may select any of the slave devices with its own  $\overline{\text{CS}}$  pin. All the operations must be <u>initiated</u> by the master activating a slave device by pulling the  $\overline{\text{CS}}$  pin of the slave LOW. The master also generates the SCK and all the data transmission on SI and SO lines are synchronized with this clock.

#### SPI Slave

The SPI slave device is activated by the master through the Chip Select line. A slave device gets the SCK as an input from the SPI master and all the communication is synchronized with this clock. The SPI slave never initiates a communication on the SPI bus and acts on the instruction from the master.

The device operates as an SPI slave and may share the SPI bus with other SPI slave devices.

## Chip Select ( $\overline{CS}$ )

For selecting any slave device, the master needs to pull down the corresponding CS pin. Any instruction can be issued to a slave device only while the CS pin is LOW. When the device is not selected, data through the SI pin is ignored and the serial output pin (SO) remains in a high-impedance state.

**Note** A new instruction must begin with the falling edge of CS. Therefore, only one opcode can be issued for each active Chip Select cycle.

**Note** It is recommended to attach an external 10-k $\Omega$  pull-up resistor to  $V_{CCO}$  on  $\overline{CS}$  pin.

#### Serial Clock (SCK)

The serial clock is generated by the SPI master and the communication is synchronized with this clock after  $\overline{\text{CS}}$  goes LOW.

The device enables SPI modes 0 and 3 for data communication. In both these modes, the inputs are latched by the slave device on the rising edge of SCK and outputs are issued on the falling edge. Therefore, the first rising edge of SCK signifies the arrival of the first bit (MSB) of SPI instruction on the SI pin. Further, all data inputs and outputs are synchronized with SCK.

#### Data Transmission - SI/SO

The SPI data bus consists of two lines, SI and SO, for serial data communication. The SI is also referred to as Master Out Slave In (MOSI) and SO is referred to as Master In Slave Out (MISO). The master issues instructions to the slave through the SI pin, while the slave responds through the SO pin. Multiple slave devices may share the SI and SO lines as described earlier.

The device has two separate pins for SI and SO, which can be connected with the master as shown in Figure 3 on page 9.

This SI input signal is used to transfer data serially into the device. It receives opcode, addresses, and data to be programmed. Values are latched on the rising edge of serial SCK clock signal. SI becomes I/O0 - an input and output during Extended-SPI and DPI/QPI commands for receiving opcodes, addresses, and data to be written (values latched on rising edge of serial SCK clock signal) as well as shifting out data (on the falling edge of SCK).

The SO output signal is used to transfer data serially out of the device. Data is shifted out on the falling edge of the serial SCK clock signal. SO becomes I/O1 - an input and output during Extended-SPI and DPI/QPI commands for receiving opcodes, addresses, and data to be programmed (values latched on rising edge of serial SCK clock signal) as well as shifting out data (on the falling edge of SCK). SO has a Repeater/Bus-Hold circuit implemented.

## Write-Protect ( $\overline{WP}$ )

In SPI and DSPI modes, the WP pin when driven low protects against writes to the Status registers and all data bytes in the memory area that are protected by the Block Protect bits in the Status registers.

When  $\overline{\text{WP}}$  is driven Low, during a WRSR command and while the Status Register Write Disable (SRWD) bit of the Status Register is set to a 1, it is not possible to write to the Status and Configuration Registers. This prevents any alteration of the Block Protect (BP2, BP1, BP0) and TBPROT bits. As a consequence, all the data bytes in the memory area that are protected by the Block Protect and TBPROT bits, are protected against data modification if  $\overline{\text{WP}}$  is Low during a WRSR command.

The  $\overline{WP}$  function is not available while in the Quad transfer mode. The  $\overline{WP}$  function is replaced by I/O2 for input and output during these modes for receiving opcode, addresses, and data to be written/programmed as well as shifting out data.  $\overline{WP}$  has an internal pull-up resistor; and may be left unconnected in the host system if not used for Quad transfer mode.  $\overline{WP}$  has an internal 100-k $\Omega$  weak pull-up resistor in SPI mode.

#### NC (I/O3)

The NC (I/O3) pin functions as I/O3 for input and output during Quad transfer modes for receiving opcode, addresses, data to be written/programmed and shifting out data. NC (I/O3) has an internal pull-up resistor; and may be left unconnected in the host system if not used for Quad transfer mode. NC (I/O3) has an internal 100-k $\Omega$  weak pull-up resistor in SPI mode.

#### Most Significant Bit (MSB)

The SPI protocol requires that the first bit to be transmitted is the MSB. This is valid for both address and data transmission.

The 1-Mbit serial nvSRAM requires a 3-byte address for any read or write operation. However, because the address is only 17 bits, it implies that the first seven bits that are fed in are ignored by the device. Although these seven bits are 'don't care', Cypress recommends that these bits are treated as 0s to enable seamless transition to higher memory densities.

#### Serial Opcode

After the slave device is selected with  $\overline{\text{CS}}$  going LOW, the first byte received is treated as the opcode for the intended operation. The device uses the standard opcodes for memory accesses. In addition to the memory accesses, it provides additional opcodes for the nvSRAM specific functions: STORE, RECALL, AutoStore Enable, and AutoStore Disable. Refer to Table 2 on page 12 for details.

#### Invalid Opcode

If an invalid opcode is received, the opcode is ignored and the device ignores any <u>add</u>itional serial data on the SI pin until the next falling edge of CS and the SO pin remains tristated.

#### Instruction

The combination of the opcode, address, and mode/dummy cycles used to issue a command.

#### Mode Bits

Control bits that follow the address bits. The device uses control bits to enable execute-in-place (XIP). These bits are driven by the system controller when they are specified.

#### Wait States

Required dummy clock cycles after the address bits or optional mode bits.

#### Status Register

The device has one 8-bit Status Register. The bits in the Status Registers are used to configure the SPI bus. These bits are described in Table 3 and Table 4 on page 14.

Figure 3. System Configuration Using Multiple 1-Mbit Quad SPI nvSRAM Devices

All Control/Data signals are shared except for CS

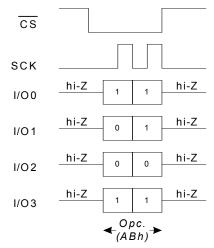

#### **Dual and Quad I/O Modes**

The device also has the capability to reconfigure the standard SPI pins to work in dual or quad I/O modes.

When the part is in the dual I/O mode, the SI pin and SO pin become I/O0 pin and I/O1 pin for either opcode, address, and data (Dual I/O mode) or both the address and data (Dual Addr/Data Mode) or just the data (Dual Data Mode).

When the part is in the quad I/O mode, the SI pin, SO pin, WP pin, and NC (I/O3) pin become I/O0 pin, I/O1 pin, I/O2 pin, and I/O3 pin for either opcode, address and data (Quad I/O Mode), or both the address and data (Quad Addr/Data Mode), or just the data (Quad Data Mode).

Table 1. I/O Modes

| Protocol                                 | Command<br>Input | Address<br>Input | Data<br>Input/Output |

|------------------------------------------|------------------|------------------|----------------------|

| SPI                                      | SI               | SI               | SI/SO                |

| DPI                                      | I/O[1:0]         | I/O[1:0]         | I/O[1:0]             |

| QPI                                      | PI I/O[3:0] I/O  |                  | I/O[3:0]             |

| Dual Data Mode<br>(Dual Out)             | I/O[0]           | I/O[0]           | I/O[1:0]             |

| Dual Address/<br>Data Mode<br>(Dual I/O) | I/O[0]           | I/O[1:0]         | I/O[1:0]             |

| Quad Data Mode<br>(Quad Out)             | I/O[0]           | I/O[0]           | I/O[3:0]             |

| Quad Address/<br>Data Mode<br>(Quad I/O) | I/O[0]           | I/O[3:0]         | I/O[3:0]             |

For more details, refer to read and write timing diagrams later in the datasheet.

#### **SPI Modes**

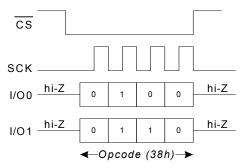

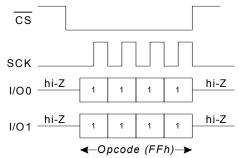

The device also has the capability to reconfigure. The device may be driven by a microcontroller with its SPI peripheral running in either of the following two modes:

- SPI Mode 0 (CPOL = 0, CPHA = 0)

- SPI Mode 3 (CPOL = 1, CPHA = 1)

For both these modes, the input data is latched in on  $\underline{\text{the}}$  rising edge of SCK starting from the first rising edge after  $\overline{\text{CS}}$  goes active. If the clock starts from a HIGH state (in mode 3), the first rising edge after the clock toggles, is considered. The output data is available on the falling edge of SCK.

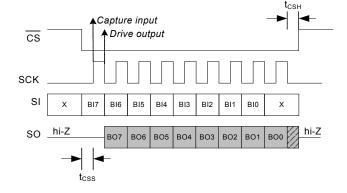

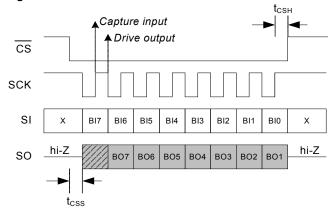

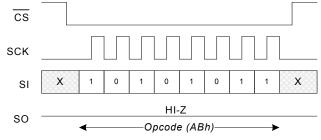

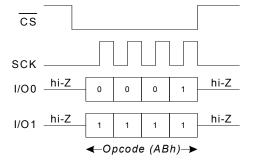

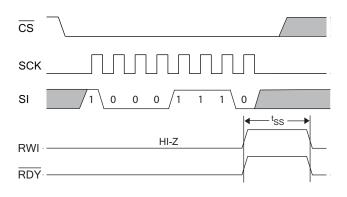

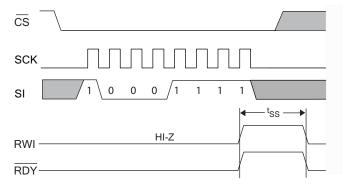

The two SPI modes are shown in Figure 4 and Figure 5. The status of clock when the bus master is in standby state and not transferring data is:

- SCK remains at '0' for Mode 0

- SCK remains at '1' for Mode 3

The device detects the SPI mode from the status of SCK pin when the device is selected by bringing the CS pin LOW. If the SCK pin is LOW when the device is selected, SPI Mode 0 is assumed and if the SCK pin is HIGH, it works in SPI Mode 3.

Figure 4. SPI Mode 0

Figure 5. SPI Mode 3

## **SPI Operating Features**

### Power-Up

Power-up is defined as the condition when the power supply is turned on and  $V_{CC}$  crosses  $V_{SWITCH}$  voltage.

As described earlier, at power-up nvSRAM performs a Power-Up RECALL operation for  $t_{\text{FA}}$  duration during which all memory accesses are disabled. The HSB pin can be probed to check the Ready/Busy status of nvSRAM after power-up.

The following is the device status after power-up:

- SPI I/O Mode

- Pull-ups activated for HSB

- SO is tristated

- <u>Sta</u>ndby power mode if <del>CS</del> pin is high. Active power mode if <del>CS</del> pin is LOW.

- Status Register state:

- □ Write Enable bit is reset to '0'

- □ SRWD not changed from previous STORE operation

- □ SNL not changed from previous STORE operation

- □ Block Protection bits are not changed from previous STORE operation

- WP and NC (I/O3) functionality as defined by Quad Data Width (QUAD) CR[1]. Pull-ups activated on WP and NC (I/O3) if Quad Data width CR[1] is logic '0'.

#### Power-Down

At power-down (continuous decay of  $V_{CC}$ ), when  $V_{CC}$  drops from the normal operating voltage and below the  $V_{SWITCH}$  threshold voltage, the device stops responding to any instruction sent to it.

If a write cycle is in progress and the last data bit D0 has been received when the power goes down, it is allowed  $t_{DELAY}$  time to complete the write. After this, all memory accesses are inhibited and a AutoStore operation is performed (AutoStore is not performed, if no write operations have been executed since the last RECALL cycle). This feature prevents inadvertent writes to nvSRAM from happening during power-down.

However, to completely avoid the possibility of inadvertent writes during power-down, ensure that the device is deselected and is in standby state, and the CS follows the voltage applied on  $V_{\rm CC}$ .

#### **Active Power Mode and Standby State**

When  $\overline{\text{CS}}$  is LOW, the device is selected and is in the active power mode. The device consumes  $\underline{\text{I}_{CC}}$  ( $\underline{\text{I}_{CC1}}$  +  $\underline{\text{I}_{CCQ1}}$ ) current, as specified in on page 55. When  $\overline{\text{CS}}$  is HIGH, the device is deselected and the device goes into the standby state time, if a STORE or RECALL cycle is not in progress. If a STORE/RECALL cycle is in progress, the device goes into the standby state after the STORE or RECALL cycle is completed.

## **SPI Functional Description**

The device has an 8-bit instruction register. Instructions and their opcodes are listed in Table 2. All instructions, addresses, and data are transferred with a HIGH to LOW CS transition. The SPI instructions along with WP, NC (I/O3), and HSB pins provide access to all the functions in nvSRAM.

Table 2. Instruction Set

| Instruction<br>Category  | Instruction<br>Name | Opcode | SPI | Dual Out   | Quad Out | Dual I/O | Quad I/O | DPI | QPI | Max Frequency (MHz) |

|--------------------------|---------------------|--------|-----|------------|----------|----------|----------|-----|-----|---------------------|

|                          |                     |        |     | Cor        | ntrol    |          |          |     |     |                     |

| Write Disable            | WRDI                | 04h    | Yes | _          | -        | -        | _        | Yes | Yes | 108                 |

| Write Enable             | WREN                | 06h    | Yes | _          | -        | Ī        | _        | Yes | Yes | 108                 |

| Enable DPI               | DPIEN               | 37h    | Yes | _          | _        |          | _        | 1   | Yes | 108                 |

| Enable QPI               | QPIEN               | 38h    | Yes | _          | _        | -        | _        | Yes | _   | 108                 |

| Enable SPI               | SPIEN               | FFh    | ı   | -          | _        | -        | _        | Yes | Yes | 108                 |

|                          |                     |        |     | Memo       | ry Read  |          |          |     |     |                     |

| Read                     | READ                | 03h    | Yes | _          | _        | -        | _        | Yes | Yes | 40                  |

| FastRead                 | FAST_READ           | 0Bh    | Yes | -          | -        | -        | -        | Yes | Yes | 108                 |

| Dual Out (Fast)<br>Read  | DOR                 | 3Bh    | -   | Yes        | _        | _        | -        | _   | _   | 108                 |

| Quad Out (Fast)<br>Read  | QOR                 | 6Bh    | _   | _          | Yes      | _        | _        | _   | -   | 108                 |

| Dual I/O (Fast)<br>Read  | DIOR                | BBh    | Ī   | _          | -        | Yes      | _        | -   | _   | 108                 |

| Quad I/O (Fast)<br>Read  | QIOR                | EBh    | _   | -          | -        | _        | Yes      | _   | _   | 108                 |

|                          |                     |        |     | Memoi      | ry Write |          |          |     |     |                     |

| Write                    | WRITE               | 02h    | Yes | _          | _        | _        | _        | Yes | Yes | 108                 |

| Dual Input Write         | DIW                 | A2h    | _   | Yes        | -        | -        | _        | -   | _   | 108                 |

| Quad Input Write         | QIW                 | 32h    | -   | _          | Yes      | _        | _        | -   | _   | 108                 |

| Dual I/O Write           | DIOW                | A1h    | _   | _          | _        | Yes      | _        | _   | _   | 108                 |

| Quad I/O Write           | QIOW                | D2h    | ı   | -          | ı        | ı        | Yes      | ı   | -   | 108                 |

|                          |                     |        |     | SR Cor     | nmands   |          |          |     |     |                     |

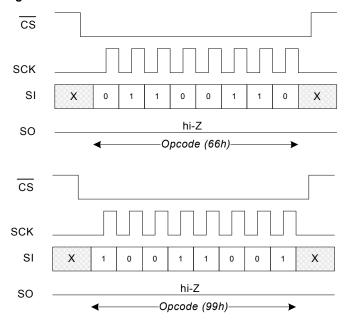

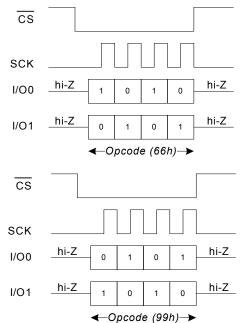

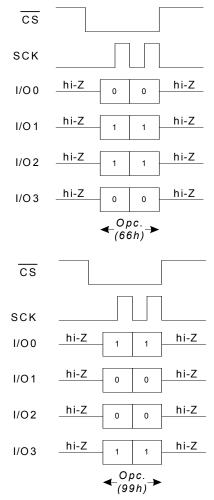

| Software Reset<br>Enable | RSTEN               | 66h    | Yes | 1          | 1        | 1        | -        | Yes | Yes | 108                 |

| Software Reset           | RESET               | 99h    | Yes | -          | _        | -        | _        | Yes | Yes | 108                 |

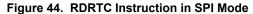

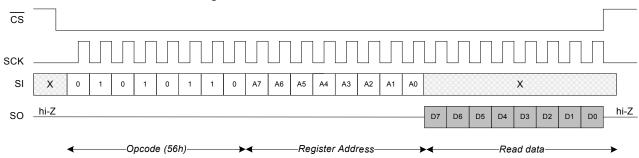

| Read RTC                 | RDRTC               | 56h    | Yes | _          | _        |          | _        | Yes | Yes | 40                  |

| Write RTC                | WRRTC               | 55h    | Yes | _          | -        | -        | _        | Yes | Yes | 108                 |

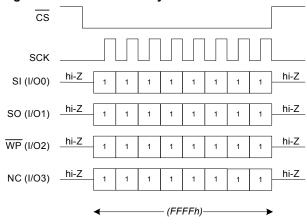

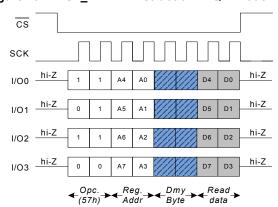

| Fast Read RTC            | FAST_RDRTC          | 57h    | Yes | -          | _        | _        | -        | Yes | Yes | 108                 |

| Enter Hibernate<br>Mode  | HIBEN               | BAh    | Yes | _          | -        | _        | -        | Yes | Yes | 108                 |

| Enter Sleep Mode         | SLEEP               | B9h    | Yes | _          | _        | _        | _        | Yes | Yes | 108                 |

| Exit Sleep Mode          | EXSLP               | ABh    | Yes | _          | _        | _        | _        | Yes | Yes | 108                 |

|                          |                     |        |     | Register C | Commands |          |          |     |     |                     |

| Read Status<br>Register  | RDSR                | 05h    | Yes | -          | _        | _        | _        | Yes | Yes | 108                 |

Table 2. Instruction Set (continued)

| Instruction<br>Category             | Instruction<br>Name | Opcode          | SPI | <b>Dual Out</b> | Quad Out | Dual I/O | Quad I/O | DPI | QPI | Max Frequency (MHz) |

|-------------------------------------|---------------------|-----------------|-----|-----------------|----------|----------|----------|-----|-----|---------------------|

| Write Status<br>Register            | WRSR                | 01h             | Yes | _               | _        | _        | -        | Yes | Yes | 108                 |

| Read Configuration<br>Register      | RDCR                | 35h             | Yes | _               | _        | _        | -        | Yes | Yes | 108                 |

| Write Configuration Register        | WRCR                | 87h             | Yes | -               | -        | -        | _        | Yes | -   | 108                 |

| Read ID Register                    | RDID                | 9Fh             | Yes | -               | _        | _        | -        | Yes | Yes | 40                  |

| Fast Read ID<br>Register            | FAST_RDID           | 9Eh             | Yes | _               | -        | _        | -        | Yes | Yes | 108                 |

| Write Serial Number<br>Register     | WRSN                | C2h             | Yes | _               | _        | _        | _        | Yes | Yes | 108                 |

| Read Serial<br>Number Register      | RDSN                | C3h             | Yes | _               | _        | _        | _        | Yes | Yes | 40                  |

| Fast Read Serial<br>Number Register | FAST_RDSN           | C9h             | Yes | -               | -        | -        | _        | Yes | Yes | 108                 |

|                                     |                     |                 |     | NV Specific     | Command  | s        |          |     |     |                     |

| STORE                               | STORE               | 8Ch             | Yes | -               | -        | _        | -        | Yes | Yes | 108                 |

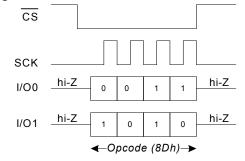

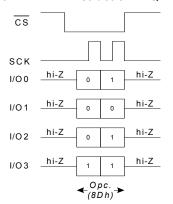

| RECALL                              | RECALL              | 8Dh             | Yes | -               | _        | _        | -        | Yes | Yes | 108                 |

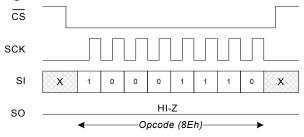

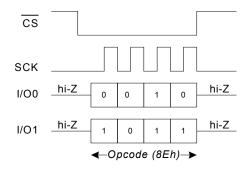

| Autostore Enable                    | ASEN                | 8Eh             | Yes | -               | _        | _        | -        | Yes | Yes | 108                 |

| Autostore Disable                   | ASDI                | 8Fh             | Yes | _               | _        | _        | _        | Yes | Yes | 108                 |

|                                     | Mode Bits           |                 |     |                 |          |          |          |     |     |                     |

| Mode Bit (Set,<br>Reset)            | _                   | Axh,<br>not Axh | Yes | _               | -        | -        | _        | Yes | Yes | _                   |

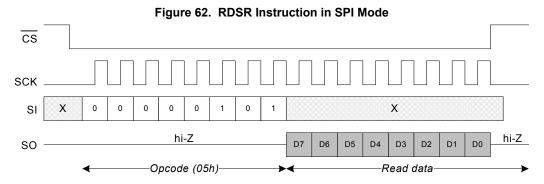

Based on their functionality, the SPI instructions are divided into the following types:

- Control instructions:

- □ Write-protection: WREN, WRDI instructions

- □ I/O modes: DPIEN, QPIEN, SPIEN

- Memory Read instructions:

- □ Memory access: READ, FAST\_READ, DOR, QOR, DIOR, QIOR

- Memory Write instructions:

- ☐ Memory access: WRITE, DIW, QIW, DIOW, QIOW

- System Resources instructions:

- □ Software Reset: RSTEN, RESET

- □ Real Time Clock: RDRTC, WRRTC, FAST RDRTC

- □ Power modes: HIBEN, SLEEP, EXSLP

- Register instructions:

- □ Configuration Register: RDCR, WRCR

- □ Status Register: RDSR, WRSR

- □ Identification: RDID, FAST\_RDID

- □ Serial Number: RDSN, WRSN, FAST\_RDSN

- nvSRAM Special instructions:

- □ STORE: STORE

- □ RECALL: RECALL

- □ Enable/Disable: ASEN, ASDI

**Note** The instruction waveforms shown in the following sections do not incorporate the effects of pull-ups on WP (I/O2), NC (I/O3) and Repeater/Bus-Hold circuitry on SO.

**Note** Instruction Opcode C5h, 1Eh, C8h, CEh, CBh, CCh, CDh are Cypress reserved opcodes and change the configuration of the device. If any one of these opcodes are erroneously entered, a software reset (66h, 99h) is required to return the device back to correct configuration. Otherwise, the device will not behave correctly.

## Status Register

The device has one Status Register, which is listed in Table 3 along with its bit descriptions. The bit format in the Status Register shows whether the bit is read only (R) or can be written to as well (W/R). The only exception to this is the serial number lock bit (SNL). The serial number can be written using the WRSN

instruction multiple times while SNL is still '0'. When set to '1', this bit prevents any modification to the serial number. This bit is factory-programmed to '0' and can only be written to once. After this bit is set to '1', it can never be cleared to '0'.

Table 3. Status Register Format and Bit Definitions

| Bit | Field Name | Function                         | Туре | R/W | Default State | Description                                                                                                                                                                                                                           |

|-----|------------|----------------------------------|------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SRWD       | Status Register<br>Write Disable | NV   | R/W | 0             | 1 = Locks state of SR when WP is low by ignoring WRSR command     0 = No protection, even when WP is low                                                                                                                              |

| 6   | SNL        | Serial Number<br>Lock            | ОТР  | R/W | 0             | Locks the Serial Number                                                                                                                                                                                                               |

| 5   | TBPROT     | Configures Start of Block        | NV   | R/W | 0             | 1 = BP starts at bottom (Low address)<br>0 = BP starts at top (High address)                                                                                                                                                          |

| 4   | BP2        |                                  | NV   | R/W | 0             |                                                                                                                                                                                                                                       |

| 3   | BP1        | Block Protection                 | NV   | R/W | 0             | Protects selected range of Block from Write, Program or Erase                                                                                                                                                                         |

| 2   | BP0        |                                  | NV   | R/W | 0             |                                                                                                                                                                                                                                       |

| 1   | WEL        | Write Enable<br>Latch            | ٧    | R   | 0             | Device accepts Write Registers (WRSR), Write, program or erase commands     Device ignores Write Registers (WRSR), write, program or erase commands     This bit is not affected by WRSR, only WREN and WRDI commands affect this bit |

| 0   | WIP        | Work in Progress                 | V    | R   | 0             | Device Busy, a Write Registers (WRSR), program, erase or other operation is in progress     Ready Device is in standby state and can accept commands                                                                                  |

Status Register Write Disable (SRWD) SR[7]

Places the device in the Hardware Protected mode when this bit is set to '1' and the WP input is driven LOW. In this mode, all the SRWD bits except WEL, become read-only bits and the Write Registers (WRSR) command is no longer accepted for execution. If WP is HIGH, the SRWD bits may be changed by the WRSR command. If SRWD is '0', WP has no effect and the SRWD bits may be changed by the WRSR command.

Note WP internally defaults to logic '0', if Quad bit CR[1] in Configuration register is set. If SRWD is set to logic '1', protection cannot be changed till Quad bit CR[1] is reset to logic '0'.

Table 4. SRWD, WP, WEL and Protection

| SRWD | WP   | WEL | Protected Blocks | Unprotected<br>Blocks | Status Register<br>(Except WEL) |

|------|------|-----|------------------|-----------------------|---------------------------------|

| X    | X    | 0   | Protected        | Protected             | Protected                       |

| 0    | Х    | 1   | Protected        | Writable              | Writable                        |

| 1    | Low  | 1   | Protected        | Writable              | Protected                       |

| 1    | High | 1   | Protected        | Writable              | Writable                        |

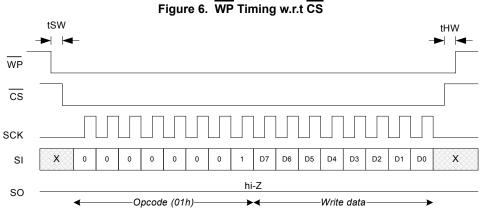

**Note** WP is sampled with respect to  $\overline{CS}$  during a write Status register instruction to determine if hardware protection is enabled. The timing waveforms are shown in Figure 6.

Document Number: 001-94176 Rev. \*J Page 14 of 67

\$0 —

Serial Number Lock (SNL) SR[6]

When set to '1', this bit prevents any modification to the serial number. This bit is factory programmed to '0' and can only be written to once. After this bit is set to '1', it can never be cleared to '0'.

#### Top or Bottom Protection (TBPROT) CR[5]

This bit defines the operation of the Block Protection bits BP2, BP1, and BP0. The desired state of TBPROT must be selected during the initial configuration of the device during system manufacture.

Block Protection (BP2, BP1, BP0) SR[4:2]

These bits define the memory array area to be software-protected against write commands. The BP bits are nonvolatile. When one or more of the BP bits is set to '1', the relevant memory area is protected against write, program, and erase.

The Block Protect bits (Status Register bits BP2, BP1, BP0) in combination with the TBPROT bit can be used to protect an address range of the memory array. The size of the range is determined by the value of the BP bits and the upper or lower starting point of the range is selected by the TBPROT bit of the status register.

Table 5. Upper Array Start of Protection (TBPROT = 0)

| Statu | s Register Content |     | <b>Protection Fraction of Memory</b> | Address Range     |

|-------|--------------------|-----|--------------------------------------|-------------------|

| BP2   | BP1                | BP0 | Array                                | Address Kange     |

| 0     | 0                  | 0   | None                                 | None              |

| 0     | 0                  | 1   | Upper 64th                           | 0x1F800 - 0x1FFFF |

| 0     | 1                  | 0   | Upper 32nd                           | 0x1F000 - 0x1FFFF |

| 0     | 1                  | 1   | Upper 16th                           | 0x1E000 - 0x1FFFF |

| 1     | 0                  | 0   | Upper 8th                            | 0x1C000 - 0x1FFFF |

| 1     | 0                  | 1   | Upper 4th                            | 0x18000 - 0x1FFFF |

| 1     | 1                  | 0   | Upper Half                           | 0x10000 - 0x1FFFF |

| 1     | 1                  | 1   | All Sectors                          | 0x00000 - 0x1FFFF |

Table 6. Lower Array Start of Protection (TBPROT = 1)

| Statu | s Register Content |     | Protection Fraction of Memory | Address Range     |

|-------|--------------------|-----|-------------------------------|-------------------|

| BP2   | BP1                | BP0 | Array                         | Address Kange     |

| 0     | 0                  | 0   | None                          | None              |

| 0     | 0                  | 1   | Lower 64th                    | 0x00000 - 0x007FF |

| 0     | 1                  | 0   | Lower 32nd                    | 0x00000 - 0x00FFF |

| 0     | 1                  | 1   | Lower 16th                    | 0x00000 - 0x01FFF |

| 1     | 0                  | 0   | Lower 8th                     | 0x00000 - 0x03FFF |

| 1     | 0                  | 1   | Lower 4th                     | 0x00000 - 0x07FFF |

| 1     | 1                  | 0   | Lower Half                    | 0x00000 - 0x0FFFF |

| 1     | 1                  | 1   | All Sectors                   | 0x00000 - 0x1FFFF |

#### Write Enable (WEL) SR[1]

The WEL bit must be set to '1' to enable program, write, or erase operations as a means to provide protection against inadvertent changes to memory or register values. The Write Enable (WREN) command execution sets the Write Enable Latch to a '1' to allow any write commands to execute afterwards. The Write Disable (WRDI) command sets the Write Enable Latch to 0 to prevent all write commands from execution. The WEL bit is cleared to 0 at the end of any successful write to registers, STORE, RECALL, program or erase operation – note it is not cleared after write operations to memory macro. After a power-down/power-up sequence, hardware reset, or software reset, the Write Enable Latch is set to '0'. The WRSR command does not affect this bit.

**<u>Note:</u>** AutoStore, power up RECALL and Hardware STORE (HSB based) are not affected by WEL bit.

Table 7. Instructions Requiring WEL Bit Set

| Instruction Description      | Instruction Name | Opcode |  |  |  |  |  |

|------------------------------|------------------|--------|--|--|--|--|--|

| Memory Write                 |                  |        |  |  |  |  |  |

| Write                        | WRITE            | 02h    |  |  |  |  |  |

| Dual Input Write             | DIW              | A2h    |  |  |  |  |  |

| Quad Input Write             | QIW              | 32h    |  |  |  |  |  |

| Dual I/O Write               | DIOW             | A1h    |  |  |  |  |  |

| Quad I/O Write               | QIOW             | D2h    |  |  |  |  |  |

| Register Commands            |                  |        |  |  |  |  |  |

| Write Status Register        | WRSR             | 01h    |  |  |  |  |  |

| Write Configuration Register | WRCR             | 87h    |  |  |  |  |  |

| Write Serial Number Register | WRSN             | C2h    |  |  |  |  |  |

| NV Specific Commands         |                  |        |  |  |  |  |  |

| STORE                        | STORE            | 8Ch    |  |  |  |  |  |

| RECALL                       | RECALL           | 8Dh    |  |  |  |  |  |

| AutoStore Enable             | ASEN             | 8Eh    |  |  |  |  |  |

| AutoStore Disable            | ASDI             | 8Fh    |  |  |  |  |  |

#### Work In Progress (WIP) SR[0]

Indicates whether the device is performing a program, write, erase operation, or any other operation, during which a new operation command will be ignored. When the bit is set to '1', the device is busy performing a background operation. While WIP is '1', only Read Status (RDSR) command may be accepted. When the WIP bit is cleared to '0', no operation is in progress. This is a read-only bit.

All values written to SR are saved to nonvolatile memory only after a STORE operation. If AutoStore is disabled, any modifications to the Status Register must be secured by performing a software STORE operation.

Hardware Store will only commit Status register values to non-volatile memory if there is a write to the SRAM.

#### Configuration Register

QPI nvSRAM has one Configuration register which is listed in Table 8 along with its bit descriptions. The bit format in the Configuration register shows whether the bit is read only (R) or can be written to as well (W/R). The Configuration register controls interface functions.

Table 8. Configuration Register

| Bit | Field Name | Function                 | Type | R/W | Default State | Description                  |

|-----|------------|--------------------------|------|-----|---------------|------------------------------|

| 7   | RFU        | Reserved                 | _    | R/W | 0             | Reserved for future use      |

| 6   | RFU        | Reserved                 | -    | R/W | 1             | Reserved for future use      |

| 5   | RFU        | Reserved                 | _    | _   | 0             | Reserved for future use      |

| 4   | RFU        | Reserved                 | _    | _   | 0             | Reserved for future use      |

| 3   | RFU        | Reserved                 | -    | _   | 0             | Reserved for future use      |

| 2   | RFU        | Reserved                 | -    | _   | 0             | Reserved for future use      |

| 1   | QUAD       | Puts device in Quad Mode | NV   | R/W | 0             | 1 = Quad; 0 = Dual or Serial |

| 0   | RFU        | Reserved                 | _    | _   | 0             | Reserved for future use      |

#### Quad Data Width (QUAD) CR[1]

When set to '1', this bit switches the data width of the device to four bits i.e. WP becomes I/O2 and NC (I/O3) becomes I/O3. The WP input is not monitored for its normal function and is internally taken to be active. The commands for Serial, Dual Output, and Dual I/O Read still function normally but, there is no need to drive WP input for those commands when switching between commands using different data path widths. The QUAD bit must be set to '1' when using QUAD Out Read, QUAD I/O Read, QUAD Input Write, QUAD I/O Write, and all QUAD SPI commands. The QUAD bit is non-volatile.

**Note** To set the Quad bit, 0x42 must be written to the Configuration register. Similarly, to reset the Quad bit, 0×40 must be written to the Configuration register. Any other data combination will change the configuration of the device and make it unusable.

**Note** When Quad bit CR[1] in Configuration register is set, WP internally defaults to logic '0'.

**Note** The values written to Configuration Register are saved to nonvolatile memory only after a STORE operation. If AutoStore is disabled, any modifications to the Configuration Register must be secured by performing a Software STORE operation. Hardware Store will only commit Configuration register values to nonvolatile memory if there is a write to the SRAM.

#### **SPI Control Instructions**

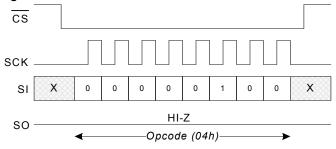

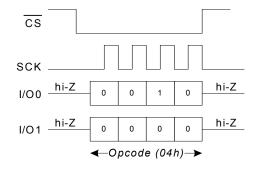

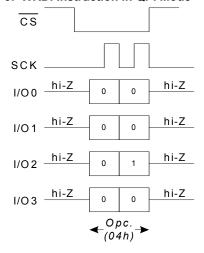

#### Write Disable (WRDI) Instruction

The Write Disable instruction disables all writes by clearing the WEL bit to '0' to protect the device against inadvertent writes. This instruction is issued after the falling edge of CS followed by opcode for WRDI instruction. The WEL bit is cleared on the rising edge of CS.

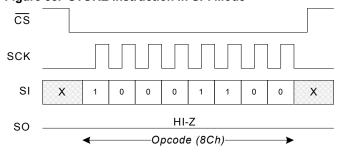

Figure 7. WRDI Instruction in SPI Mode

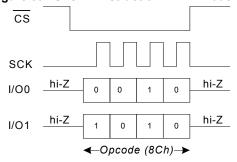

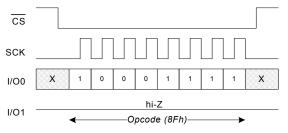

Figure 8. WRDI Instruction in DPI Mode

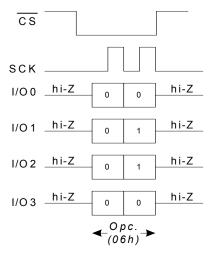

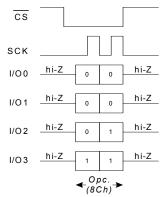

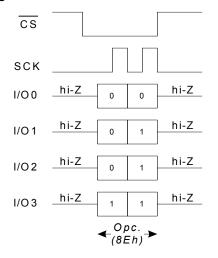

Figure 9. WRDI Instruction in QPI Mode

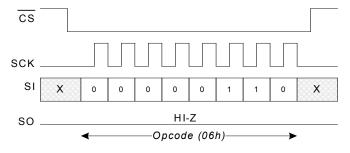

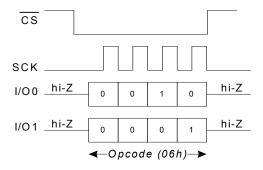

## Write Enable (WREN) Instruction

On power-up, the device is always in the Write Disable state. The write instructions and nvSRAM special instruction must therefore be preceded by a Write Enable instruction. If the device is not write enabled (WEL = '0'), it ignores the write instructions and returns to the standby state when CS is brought HIGH. This instruction is issued following the falling edge of CS and sets the WEL bit of the Status Register to '1'. The WEL bit defaults to '0' on power-up.

**Note** The WEL bit is cleared to 0 at the end of any successful write to registers, STORE, RECALL, ASEN, and ASDI operation. It is not cleared after write operations to memory macro.

Figure 10. WREN Instruction in SPI Mode

Figure 11. WREN Instruction in DPI Mode

Figure 12. WREN Instruction in QPI Mode

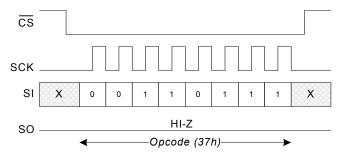

## **Enable DPI (DPIEN) Instruction**

DPIEN enables the Dual I/O mode wherein opcode, address, mode bits, and data is sent over I/O0 and I/O1.

Figure 13. Enable Dual I/O Instruction in SPI Mode

Figure 14. Enable Dual I/O Instruction in QPI Mode

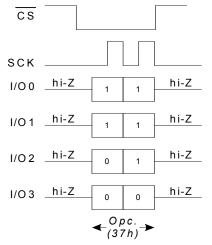

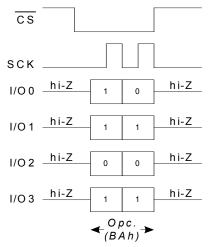

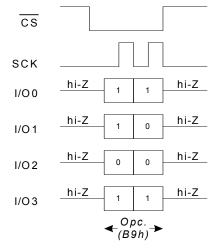

#### **Enable QPI (QPIEN) Instruction**

QPIEN enables QPI mode wherein opcode, address, dummy/mode bits and data is sent over I/O0, I/O1, I/O2, and I/O3. QPIEN instruction does not set the Quad bit CR[1] in Configuration register. WRCR instruction to set Quad bit CR[1] must therefore proceed QPIEN instruction.

Note Disabling QPI mode does not reset Quad bit CR[1].

Figure 15. Enable Quad I/O instruction in SPI Mode

Figure 16. Enable Quad I/O in DPI Mode

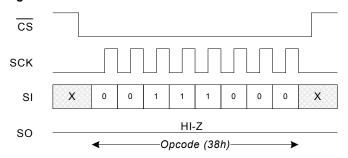

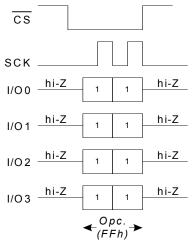

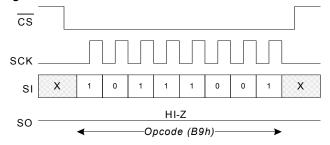

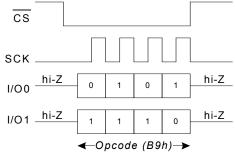

#### **Enable SPI (SPIEN) Instruction**

SPIEN disables Dual I/O or Quad I/O modes and returns the device in SPI mode. SPIEN instruction does not reset the Quad bit CR[1] in Configuration register.

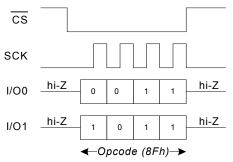

Figure 17. Enable SPI Instruction in DPI Mode

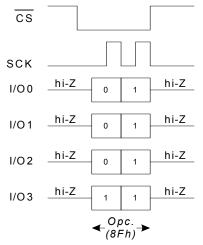

Figure 18. Enable SPI Instruction in QPI Mode

## **SPI Memory Read Instructions**

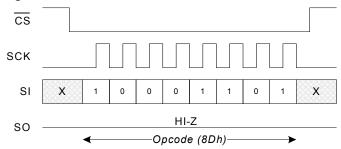

Read instructions access the memory array. These instructions cannot be used while a STORE or RECALL cycle is in progress. A STORE cycle in progress is indicated by the WIP bit of the Status Register and the HSB pin.

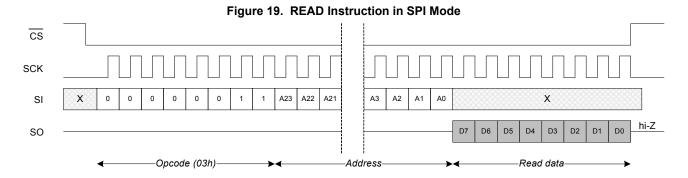

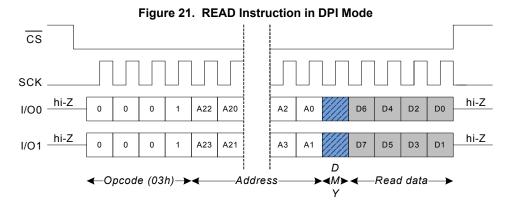

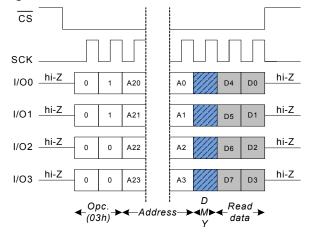

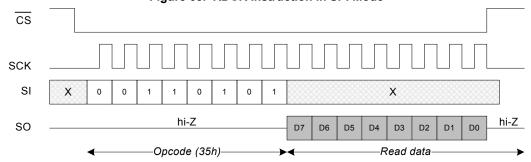

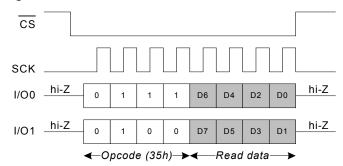

#### Read Instructions

The device performs the read operations when read instruction opcodes are given on the SI pin and provides the read output data on the SO pin for SPI mode or the I/O1, I/O0 pins for Dual I/O Mode or the I/O3, I/O2, I/O1, and I/O0 pins for Quad I/O Mode. After the CS pin is pulled LOW to select a device, the read opcode is entered followed by three bytes of address. The device contains a 17-bit address space for 1-Mbit configuration.

The most significant address byte contains A16 in bit 0 and other bits as 'don't care'. Address bits A15 to A0 are sent in the following two address bytes. After the last address bit is transmitted, the data (D7-D0) at the specific address is shifted out on the falling edge of SCK starting with D7. The reads can be performed in burst mode if  $\overline{\text{CS}}$  is held LOW.

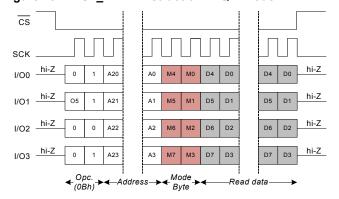

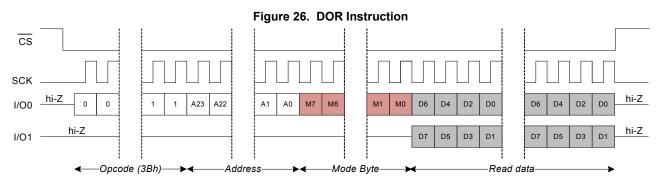

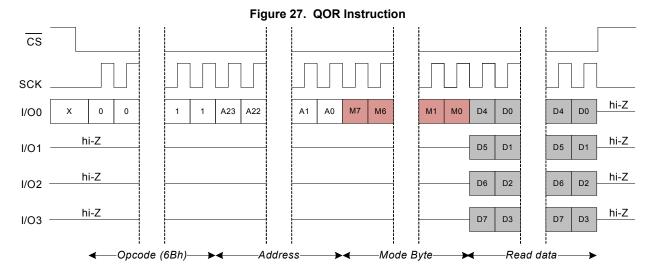

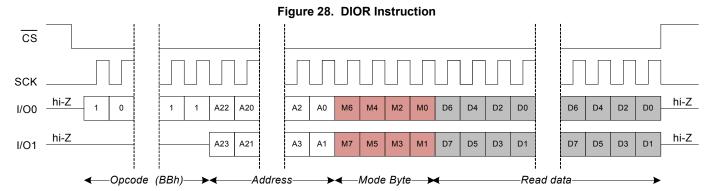

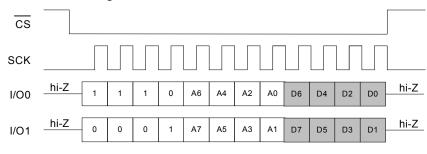

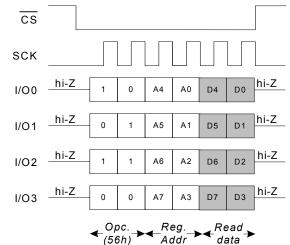

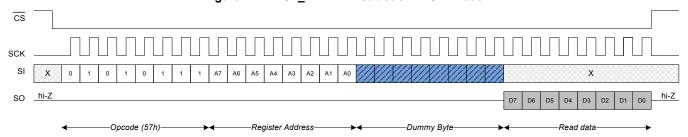

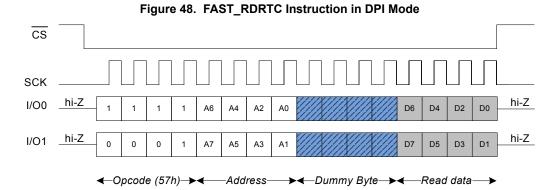

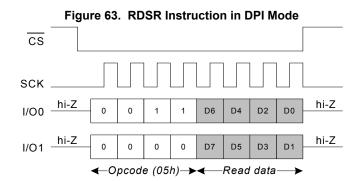

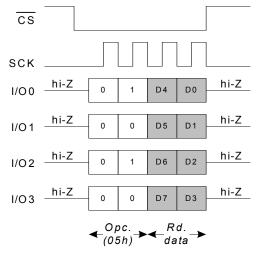

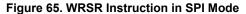

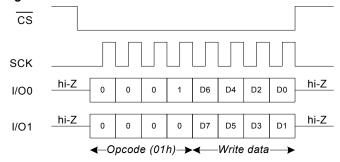

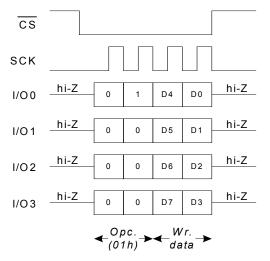

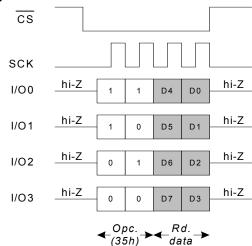

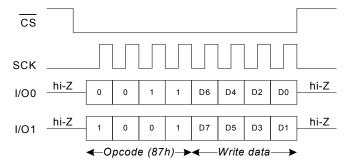

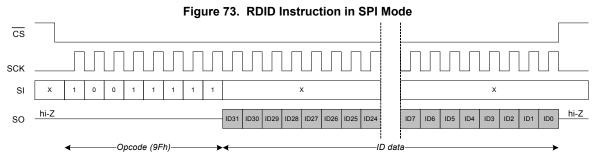

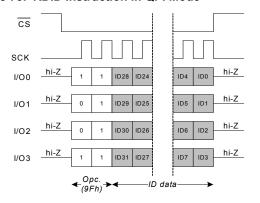

The device automatically increments to the next higher address after each byte of data is output. When the last data memory address (0x1FFFF) is reached, the address rolls over to 0x00000 and the device continues the <u>read</u> instruction. The read operation is terminated by driving CS HIGH at any time during data output.