# CY62167G Automotive

# 16-Mbit (1M Words × 16-Bit) Static RAM with Error-Correcting Code (ECC)

### Features

- AEC-Q100 qualified

- Ultra-low standby power

Typical standby current: 5.5 μA

Maximum standby current: 75 μA

- High speed: 45 ns / 55 ns

- Embedded error-correcting code (ECC) for single-bit error correction

- Temperature Ranges:

Automotive-A: -40 °C to +85 °C

Automotive-E: -40 °C to +125 °C

- Operating voltage range: 2.2 V to 3.6 V

- 1.0-V data retention

- TTL-compatible inputs and outputs

- Available in Pb-free 48-ball VFBGA and 48-pin TSOP I packages

### **Functional Description**

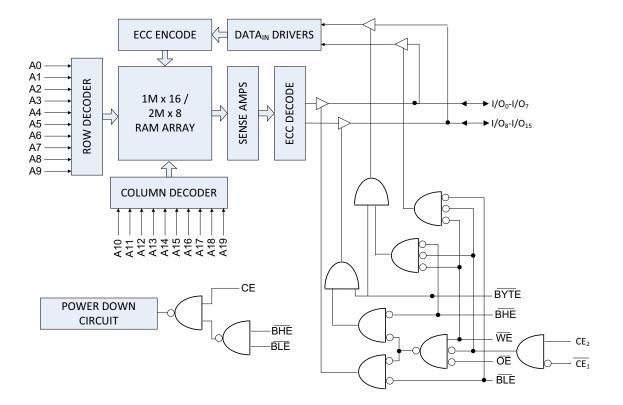

CY62167G is high-performance CMOS low-power (MoBL) SRAM devices with embedded ECC. This device is offered in dual chip-enable.

Devices with dual chip-enable are accessed by asserting both chip-enable inputs –  $\overline{CE}_1$  as LOW and  $CE_2$  as HIGH.

<u>Data</u> writes are performed by asserting the Write Enable input (WE) LOW, and providing the data and address on device data (I/O<sub>0</sub> through I/O<sub>15</sub>) and address (A<sub>0</sub> through <u>A<sub>19</sub></u>) pins respectively. The Byte High/Low Enable (BHE, BLE) inputs control byte writes, and write data on the corresponding I/O lines

to the memory location specified. BHE controls I/O<sub>8</sub> through I/O<sub>15:</sub> BLE controls I/O<sub>0</sub> through I/O<sub>7</sub>.

Data reads are performed by asserting the Output Enable  $(\overline{OE})$  input and providing the required address on the address lines. Read data is accessible on I/O lines (I/O<sub>0</sub> through I/O<sub>15</sub>). Byte accesses can <u>be performed</u> by asserting the required byte enable signal (BHE, BLE) to read either the upper byte or the lower byte of data from the specified address location.

All I/Os (I/O<sub>0</sub> through  $\underline{I/O}_{15}$ ) are placed in a HI-Z state when the device is deselected (CE<sub>1</sub> HIGH / CE<sub>2</sub> LOW for dual chip-enable

device), or control signals are de-asserted ( $\overline{OE}$ ,  $\overline{BLE}$ , and  $\overline{BHE}$ ).

These devices also have a unique "Byte Power down" feature

where if both the Byte Enables ( $\overline{BHE}$  and  $\overline{BLE}$ ) are disabled, the devices seamlessly switches to standby mode irrespective of the state of the chip enable(s), thereby saving power.

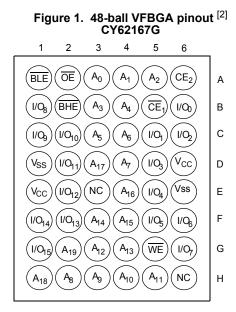

The CY62167G device is available in a Pb-free 48-ball VFBGA and 48-pin TSOP I packages. The device in the 48-pin TSOP I package can also be configured to function as a 2M words × 8 bit device. The logic block diagram is on page 2. Refer to Pin Configurations on page 4 and the associated footnotes for details.

Note 1. This device does not support automatic write-back on error detection.

# Logic Block Diagram – CY62167G

# CY62167G Automotive

### Contents

| Pin Configurations             | 4 |

|--------------------------------|---|

| Product Portfolio              |   |

| Maximum Ratings                | 5 |

| Operating Range                | 5 |

| DC Electrical Characteristics  | 5 |

| Capacitance                    | 6 |

| Thermal Resistance             |   |

| AC Test Loads and Waveforms    |   |

| Data Retention Characteristics | 7 |

| Data Retention Waveform        |   |

| Switching Characteristics      |   |

| Switching Waveforms            |   |

| Truth Table – CY62167G         |   |

| Ordering Information                    | 14 |

|-----------------------------------------|----|

| Ordering Code Definitions               | 14 |

| Package Diagram                         | 15 |

| Acronyms                                | 17 |

| Document Conventions                    | 17 |

| Units of Measure                        | 17 |

| Document History Page                   | 18 |

| Sales, Solutions, and Legal Information | 19 |

| Worldwide Sales and Design Support      | 19 |

| Products                                | 19 |

| PSoC® Solutions                         | 19 |

| Cypress Developer Community             | 19 |

| Technical Support                       | 19 |

### **Pin Configurations**

Figure 2. 48-pin TSOP I pinout (Dual Chip Enable without ERR) – CY62167G<sup>[2, 3]</sup>

| 0                                      |                                                                         |

|----------------------------------------|-------------------------------------------------------------------------|

| A15 🗖 1                                | 19 116                                                                  |

| A14 0                                  | 48 <b>–</b> <u>A16</u><br>47 <b>–</b> BYTE                              |

| A14 🖬 2<br>A13 🗖 3                     | 46 <b>V</b> ss                                                          |

| A12 - 4                                | 45 <b>I</b> /O15/A20                                                    |

| A11 🖬 5                                | 44 🖬 1/07                                                               |

| A10 🖬 6                                | 43 🗖 I/O14                                                              |

| A9 🗖 7                                 | 42 🗖 1/06                                                               |

| A8 🖴 8                                 | 41 🗖 1/013                                                              |

| A19 🛏 9                                | 40 🖿 I/O5                                                               |

| <u>NC</u> <b>=</b> 10                  | 39 🗖 I/O12                                                              |

| WE = 11                                | 38 🖬 1/04                                                               |

| CE <sub>2</sub> = 12<br><u>NC</u> = 13 | 37 🗖 Vcc                                                                |

| <u>NC</u>                              | 36 🗖 I/O11                                                              |

|                                        | 35 🗖 1/03                                                               |

|                                        | 34 <b>=</b> 1/O10                                                       |

| A18 = 16<br>A17 = 17                   | 33 🗖 1/02                                                               |

| A17 🖬 17<br>A7 🖬 18                    | 32 <b>=</b> 1/09<br>31 <b>=</b> 1/01                                    |

| A7 <b>L</b> 18<br>A6 <b>L</b> 19       | 31 = 1/01<br>30 = 1/08                                                  |

| A5 <b>2</b> 0                          | 29 1/00                                                                 |

| A4 = 21                                | 28 <b>–</b> OE                                                          |

| A3 <b>H</b> 22                         | 20 - 0L<br>27 - Ves                                                     |

| A2 = 23                                | $26 = \frac{\sqrt{33}}{CE}$                                             |

| A1 = 24                                | 27 <b>P</b> <u>Vss</u><br>26 <b>P</b> CE <sub>1</sub><br>25 <b>P</b> A0 |

|                                        | 110                                                                     |

### **Product Portfolio**

|            |              |                           |               | Power Dissipation                                           |      |                    |                       |  |  |

|------------|--------------|---------------------------|---------------|-------------------------------------------------------------|------|--------------------|-----------------------|--|--|

| Product    | Range        | V <sub>CC</sub> Range (V) | Speed<br>(ns) | Operating I <sub>CC</sub> , (mA), f = f <sub>max</sub> Star |      | Standby,           | Ι <sub>SB2</sub> (μΑ) |  |  |

|            |              |                           | ()            | Тур <sup>[4]</sup>                                          | Max  | Тур <sup>[4]</sup> | Max                   |  |  |

| CY62167G30 | Automotive-E | 2.2 V–3.6 V               | 55            | 29.0                                                        | 40.0 | 5.5                | 75.0                  |  |  |

|            | Automotive-A |                           | 45            | 29.0                                                        | 36.0 | 5.5                | 16.0                  |  |  |

Notes

NC pins are not connected internally to the die and are typically used for address expansion to a higher-density device. Refer to the respective datasheets for pin configuration. 2.

The BYTE pin in the <u>48-pin TSOP I package</u> must be tied to V<sub>CC</sub> to use the device as a 1<u>M × 16 SRAM</u>. The 48-pin TSOP I package can also be used as a 2M × 8 SRAM by tying the BYTE signal to V<sub>SS</sub>. In the 2 M × 8 configuration, pin 45 is A20, while BHE, BLE and I/O<sub>8</sub> to I/O<sub>14</sub> pins are not used.

Indicates the value for the center of Distribution at 3.0 V, 25 °C and not 100% tested.

### **Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

| Storage temperature                                        | –65 °C to + 150 °C                |

|------------------------------------------------------------|-----------------------------------|

| Ambient temperature with power applied                     | –55 °C to + 125 °C                |

| Supply voltage to ground potential <sup>[5]</sup>          | –0.5 V to V <sub>CC</sub> + 0.5 V |

| DC voltage applied to outputs in HI-Z state <sup>[5]</sup> | –0.5 V to V <sub>CC</sub> + 0.5 V |

| DC input voltage [5]                                       | –0.5 V to V <sub>CC</sub> + 0.5 V |

### **DC Electrical Characteristics**

Over the Operating Range

| Output current into outputs (LOW) 20 mA                       |

|---------------------------------------------------------------|

| Static discharge voltage<br>(MIL-STD-883, Method 3015)>2001 V |

| Latch-up current>140 mA                                       |

## **Operating Range**

| Grade        | Ambient Temperature | V <sub>cc</sub> |

|--------------|---------------------|-----------------|

| Automotive-E | –40 °C to +125 °C   | 2.2 V to 3.6 V  |

| Automotive-A | –40 °C to +85 °C    |                 |

| Parameter                       | ameter Description                                                               |                                                              | Test Conditio                                                                                                                                                                                                                                                                                                        | t Conditions                                     |      | 55 ns (Automotive-E)      |                       |      | 45 ns (Automotive-A) |                       |      |  |

|---------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------|---------------------------|-----------------------|------|----------------------|-----------------------|------|--|

| Parameter                       | Descr                                                                            | iption                                                       | Test Conditio                                                                                                                                                                                                                                                                                                        |                                                  |      | <b>Typ</b> <sup>[6]</sup> | Max                   | Min  | Тур [6]              | Мах                   | Unit |  |

| V <sub>OH</sub>                 |                                                                                  | 2.2 V to 2.7 V                                               | V <sub>CC</sub> = Min, I <sub>OH</sub> = –0.1                                                                                                                                                                                                                                                                        | V <sub>CC</sub> = Min, I <sub>OH</sub> = –0.1 mA |      | -                         | _                     | 2.0  | -                    | _                     | V    |  |

|                                 | voltage                                                                          | 2.7 V to 3.6 V                                               | $V_{CC}$ = Min, $I_{OH}$ = -1.0                                                                                                                                                                                                                                                                                      | mA                                               | 2.4  | -                         | _                     | 2.4  | -                    | _                     |      |  |

| V <sub>OL</sub>                 | Output LOW                                                                       | 2.2 V to 2.7 V                                               | V <sub>CC</sub> = Min, I <sub>OL</sub> = 0.1 m                                                                                                                                                                                                                                                                       | ۱A                                               | -    | -                         | 0.4                   | -    | -                    | 0.4                   | V    |  |

|                                 | voltage                                                                          | 2.7 V to 3.6 V                                               | V <sub>CC</sub> = Min, I <sub>OL</sub> = 2.1 m                                                                                                                                                                                                                                                                       | ۱A                                               | -    | -                         | 0.4                   | -    | -                    | 0.4                   |      |  |

| V <sub>IH</sub>                 | Input HIGH                                                                       | 2.2 V to 2.7 V                                               | -                                                                                                                                                                                                                                                                                                                    |                                                  | 1.8  | -                         | V <sub>CC</sub> + 0.3 | 1.8  | -                    | V <sub>CC</sub> + 0.3 | V    |  |

|                                 | voltage <sup>[5]</sup>                                                           | 2.7 V to 3.6 V                                               | -                                                                                                                                                                                                                                                                                                                    |                                                  | 2.0  | -                         | V <sub>CC</sub> + 0.3 | 2.0  | -                    | V <sub>CC</sub> + 0.3 |      |  |

| V <sub>IL</sub>                 | Input LOW                                                                        | 2.2 V to 2.7 V                                               | _                                                                                                                                                                                                                                                                                                                    | _                                                |      | -                         | 0.6                   | -0.3 | _                    | 0.6                   | V    |  |

|                                 | voltage <sup>[5]</sup>                                                           | 2.7 V to 3.6 V                                               |                                                                                                                                                                                                                                                                                                                      |                                                  | -0.3 | -                         | 0.8                   | -0.3 | -                    | 0.8                   |      |  |

| I <sub>IX</sub>                 | Input leakage                                                                    | current                                                      | $GND \leq V_{IN} \leq V_{CC}$                                                                                                                                                                                                                                                                                        |                                                  | -4.0 | -                         | +4.0                  | -1.0 | -                    | +1.0                  | μA   |  |

| I <sub>OZ</sub>                 | Output leakage current                                                           |                                                              | $GND \leq V_{OUT} \leq V_{CC}$ , Output disabled                                                                                                                                                                                                                                                                     |                                                  | -4.0 | -                         | +4.0                  | -1.0 | -                    | +1.0                  | μA   |  |

| I <sub>CC</sub>                 |                                                                                  | <sub>CC</sub> operating supply $V_{CC}$ = Max, $f = f_{MAX}$ | f = f <sub>MAX</sub>                                                                                                                                                                                                                                                                                                 | -                                                | 29.0 | 40.0                      | _                     | 29.0 | 36.0                 | mA                    |      |  |

|                                 | current                                                                          |                                                              | I <sub>OUT</sub> = 0 mA,<br>CMOS levels                                                                                                                                                                                                                                                                              | f =1 MHz                                         | -    | 7.0                       | 18.0                  | -    | 7.0                  | 9.0                   | mA   |  |

| I <sub>SB1</sub> [7]            | Automatic power down<br>current – CMOS inputs;<br>V <sub>CC</sub> = 2.2 to 3.6 V |                                                              | $ \overline{CE}_1 \ge V_{CC} - \underbrace{0.2}_{CC} \text{ V or } CE_2 \le 0.2 \text{ V} $ or (BHE and BLE) $\ge V_{CC} - 0.2 \text{ V}, $ $ V_{IN} \ge V_{CC} - 0.2 \text{ V},  V_{IN} \le 0.2 \text{ V}, $ $ f = f_{max} \text{ (address and data only)}, $ $ f = 0 \text{ (OE, and WE)},  V_{CC} = V_{CC(max)} $ |                                                  | _    | 5.5                       | 75.0                  | _    | 5.5                  | 16.0                  | μA   |  |

| I <sub>SB2</sub> <sup>[7]</sup> | Automatic pov<br>current – CM0<br>V <sub>CC</sub> = 2.2 to 3                     | OS inputs;                                                   | $\overline{CE}_{1} \ge V_{CC} - 0.2V \text{ or } C$ or (BHE and BLE) $\ge V_{IN}$ $V_{IN} \ge V_{CC} - 0.2 \text{ V or } V$ f = 0, $V_{CC} = V_{CC(max)}$                                                                                                                                                            | E <sub>2</sub> ≤ 0.2 V<br><sub>CC</sub> – 0.2 V, | _    | 5.5                       | 75.0                  | _    | 5.5                  | 16.0                  | μA   |  |

- S. V<sub>IL(min)</sub> = -2.0 V and V<sub>IH(max)</sub> = V<sub>CC</sub> + 2 V for pulse durations of less than 20 ns.

6. Indicates the value for the center of <u>Distribution at 3.0 V</u>, 25 °C and not 100% tested.

7. Chip enables (CE<sub>1</sub> and CE<sub>2</sub>) and BHE, BLE and BYTE must be tied to CMOS levels to meet the I<sub>SB1</sub> / I<sub>SB2</sub> / I<sub>CCDR</sub> spec. Other inputs can be left floating.

# Capacitance

| Parameter <sup>[8]</sup> | Description        | Test Conditions                                                | Max | Unit |

|--------------------------|--------------------|----------------------------------------------------------------|-----|------|

| C <sub>IN</sub>          | Input capacitance  | $T_A = 25 \text{ °C}, f = 1 \text{ MHz}, V_{CC} = V_{CC(typ)}$ | 10  | рF   |

| C <sub>OUT</sub>         | Output capacitance |                                                                | 10  | рF   |

### **Thermal Resistance**

| Parameter [8] | Description                              | Test Conditions                                                            | 48-ball VFBGA | 48-pin TSOP I | Unit |

|---------------|------------------------------------------|----------------------------------------------------------------------------|---------------|---------------|------|

| JA            |                                          | Still air, soldered on a 3 × 4.5 inch,<br>four-layer printed circuit board | 31.50         | 57.99         | °C/W |

| - 30          | Thermal resistance<br>(junction to case) |                                                                            | 15.75         | 13.42         | °C/W |

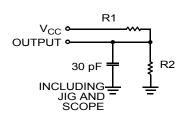

### AC Test Loads and Waveforms

### Figure 3. AC Test Loads and Waveforms

| Parameters        | 3.0 V | Unit |

|-------------------|-------|------|

| R1                | 317   | Ω    |

| R2                | 351   | Ω    |

| V <sub>HIGH</sub> | 3.0   | V    |

### **Data Retention Characteristics**

Over the Operating Range

| Parameter                         | Description                          | Conditions                                                                                                                                                                                                                                                                                                                                                                                                      | 55 ns (Automotive-E) |                           |      | 45 ns ( | Unit                      |      |      |

|-----------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|------|---------|---------------------------|------|------|

|                                   |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                 | Min                  | <b>Typ</b> <sup>[9]</sup> | Мах  | Min     | <b>Typ</b> <sup>[9]</sup> | Мах  | Unit |

| V <sub>DR</sub>                   | V <sub>CC</sub> for data retention   |                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                    | -                         | -    | 1       | -                         | Ι    | V    |

| I <sub>CCDR</sub> <sup>[10]</sup> |                                      | $\begin{array}{l} 2.2 \text{ V} < \text{V}_{\text{CC}} \leq 3.6 \text{ V} \\ \hline \overline{\text{CE}}_1 \geq \text{V}_{\text{CC}} - 0.2 \text{ V} \text{ or } \text{CE}_2 \leq 0.2 \text{ V} \\ \text{or (BHE and BLE)} \geq \text{V}_{\text{CC}} - 0.2 \text{ V}, \\ \hline \text{V}_{\text{IN}} \geq \text{V}_{\text{CC}} - 0.2 \text{ V} \text{ or } \text{V}_{\text{IN}} \leq 0.2 \text{ V} \end{array}$ | _                    | 5.5                       | 75.0 | _       | 5.5                       | 16.0 | μΑ   |

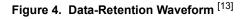

| t <sub>CDR</sub> <sup>[11]</sup>  | Chip deselect to data-retention time |                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                    | -                         | _    | 0       | -                         | -    | -    |

| t <sub>R</sub> <sup>[12]</sup>    | Operation-recovery time              |                                                                                                                                                                                                                                                                                                                                                                                                                 | 55                   | -                         | _    | 45      | -                         | _    | ns   |

### **Data Retention Waveform**

- Indicates the value for the center of distribution at 3.0 V, 25°C and not 100% tested.

Chip enables (CE<sub>1</sub> and CE<sub>2</sub>) and BYTE must be tied to CMOS levels to meet the I<sub>SB1</sub> / I<sub>SB2</sub> / I<sub>CCDR</sub> spec. Other inputs can be left floating.

Tested initially and after any design or process changes that may affect these parameters.

Full device operation requires linear V<sub>CC</sub> ramp from V<sub>DR</sub> to V<sub>CC(min)</sub> ≥ 100 µs or stable at V<sub>CC(min)</sub> ≥ 100 µs.

BHE.BLE is the AND of both BHE and BLE. Deselect the chip by either disabling the chip enable signals or by disabling both BHE and BLE.

### **Switching Characteristics**

| $\begin{array}{c c} t_{AA} & Add \\ \hline t_{OHA} & Data \\ \hline t_{ACE} & \overline{CE}_{1} \\ \hline t_{DOE} & \overline{OE} \\ \hline t_{LZOE} & \overline{OE} \\ \hline t_{LZCE} & \overline{CE}_{2} \\ \end{array}$ | Description<br>ad cycle time<br>dress to data valid<br>ta hold from address change | Min<br>55<br>–<br>10 | Max<br>-<br>55 | <b>Min</b><br>45 | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------|----------------|------------------|-----|------|

| $\begin{array}{c c} t_{RC} & Rea \\ t_{AA} & Add \\ t_{OHA} & Data \\ t_{ACE} & CE_{1} \\ t_{DOE} & OE \\ t_{LZOE} & OE \\ t_{LZCE} & CE_{1} \\ \end{array}$                                                                | dress to data valid<br>ta hold from address change                                 | -                    |                | 45               |     |      |

| $\begin{array}{c c} t_{AA} & Add \\ t_{OHA} & Data \\ t_{ACE} & \overline{CE} \\ t_{DOE} & \overline{OE} \\ t_{LZOE} & \overline{OE} \\ t_{HZOE} & \overline{OE} \\ t_{LZCE} & \overline{CE} \\ \end{array}$                | dress to data valid<br>ta hold from address change                                 | -                    |                | 45               | _   | r    |

| $\begin{array}{c c} t_{OHA} & Data \\ t_{ACE} & \overline{CE}_{1} \\ t_{DOE} & \overline{OE} \\ t_{LZOE} & \overline{OE} \\ t_{LZCE} & \overline{CE}_{1} \\ \end{array}$                                                    | ta hold from address change                                                        | - 10                 | 55             |                  |     | ns   |

| t <sub>ACE</sub> CE<br>t <sub>DOE</sub> OE<br>t <sub>LZOE</sub> OE<br>t <sub>HZOE</sub> OE<br>t <sub>LZCE</sub> CE                                                                                                          |                                                                                    | 10                   |                | -                | 45  | ns   |

| t <sub>DOE</sub> OE<br>t <sub>LZOE</sub> OE<br>t <sub>HZOE</sub> OE<br>t <sub>LZCE</sub> CE                                                                                                                                 | $_{1}$ LOW and CE <sub>2</sub> HIGH to data valid / $\overline{CE}$ LOW            |                      | _              | 10               | -   | ns   |

| t <sub>LZOE</sub> OE<br>t <sub>HZOE</sub> OE<br>t <sub>LZCE</sub> CE                                                                                                                                                        | · <u> </u>                                                                         | -                    | 55             | -                | 45  | ns   |

| t <sub>LZOE</sub> OE<br>t <sub>HZOE</sub> OE<br>t <sub>LZCE</sub> CE                                                                                                                                                        | LOW to data valid / OE LOW                                                         | -                    | 25             | _                | 22  | ns   |

| t <sub>HZOE</sub> OE<br>t <sub>LZCE</sub> CE                                                                                                                                                                                | LOW to Low Z <sup>[15]</sup>                                                       | 5                    | -              | 5                | _   | ns   |

|                                                                                                                                                                                                                             | HIGH to High Z <sup>[15, 16]</sup>                                                 | -                    | 20             | -                | 18  | ns   |

| t <sub>HZCE</sub> CE                                                                                                                                                                                                        | $_1$ LOW and CE <sub>2</sub> HIGH to Low Z <sup>[15]</sup>                         | 10                   | -              | 10               | _   | ns   |

|                                                                                                                                                                                                                             | 1 HIGH and CE <sub>2</sub> LOW to High Z <sup>[15, 16]</sup>                       | -                    | 20             | -                | 18  | ns   |

| t <sub>PU</sub> CE                                                                                                                                                                                                          | 1 LOW and CE <sub>2</sub> HIGH to power-up                                         | 0                    | -              | 0                | _   | ns   |

| t <sub>PD</sub> CE                                                                                                                                                                                                          | 1 HIGH and CE <sub>2</sub> LOW to power-down                                       | -                    | 55             | -                | 45  | ns   |

| t <sub>DBE</sub> BLE                                                                                                                                                                                                        | E / BHE LOW to data valid                                                          | -                    | 55             | _                | 45  | ns   |

| t <sub>LZBE</sub> BLE                                                                                                                                                                                                       | E / BHE LOW to Low Z <sup>[15]</sup>                                               | 5                    | -              | 5                | _   | ns   |

|                                                                                                                                                                                                                             | E / BHE HIGH to High Z <sup>[15, 16]</sup>                                         | -                    | 20             | _                | 18  | ns   |

| Write Cycle [17]                                                                                                                                                                                                            |                                                                                    | •                    |                |                  |     |      |

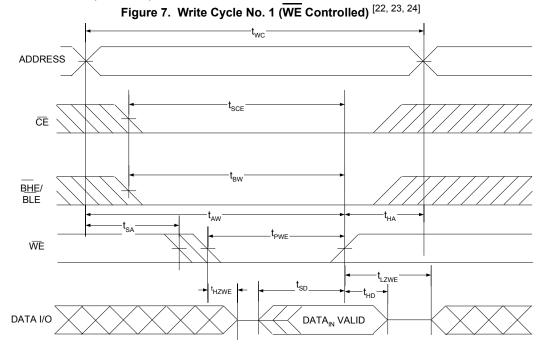

| t <sub>WC</sub> Writ                                                                                                                                                                                                        | ite cycle time                                                                     | 55                   | _              | 45               | _   | ns   |

| t <sub>SCE</sub> CE                                                                                                                                                                                                         | 1 LOW and CE <sub>2</sub> HIGH to write end                                        | 40                   | -              | 35               | _   | ns   |

| t <sub>AW</sub> Add                                                                                                                                                                                                         | dress setup to write end                                                           | 40                   | -              | 35               | _   | ns   |

| t <sub>HA</sub> Add                                                                                                                                                                                                         | dress hold from write end                                                          | 0                    | _              | 0                | _   | ns   |

| t <sub>SA</sub> Add                                                                                                                                                                                                         | dress setup to write start                                                         | 0                    | _              | 0                | _   | ns   |

| t <sub>PWE</sub> WE                                                                                                                                                                                                         | pulse width                                                                        | 40                   | -              | 35               | _   | ns   |

| t <sub>BW</sub> BLE                                                                                                                                                                                                         | E / BHE LOW to write end                                                           | 40                   | -              | 35               | _   | ns   |

| t <sub>SD</sub> Data                                                                                                                                                                                                        | ta setup to write end                                                              | 25                   | -              | 25               | _   | ns   |

| t <sub>HD</sub> Data                                                                                                                                                                                                        | ta hold from write end                                                             | 0                    | -              | 0                | _   | ns   |

| t <sub>HZWE</sub> WE                                                                                                                                                                                                        |                                                                                    |                      | 1              | 1                | 1 1 | 1    |

| t <sub>LZWE</sub> WE                                                                                                                                                                                                        | LOW to High Z <sup>[15, 16]</sup>                                                  | -                    | 20             | _                | 18  | ns   |

Notes

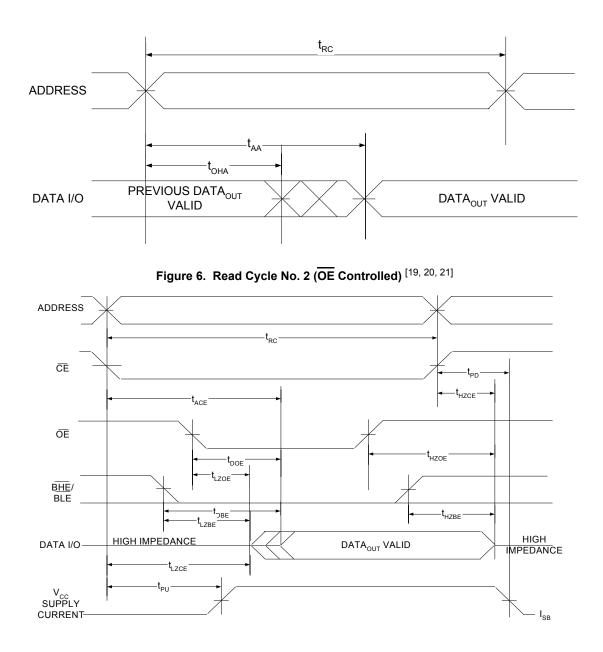

- 14. Test conditions assume signal transition time (rise/fall) of 3 ns or less, timing reference levels of 1.5 V (for V<sub>CC</sub> ≥ 3 V) and V<sub>CC</sub>/2 (for V<sub>CC</sub> < 3 V), and input pulse levels of 0 to 3 V (for V<sub>CC</sub> ≥ 3 V) and 0 to V<sub>CC</sub> (for V<sub>CC</sub> < 3 V). Test conditions for the read cycle use output loading shown in AC Test Loads and Waveforms section, unless specified otherwise.</p>

15. At any temperature and voltage condition, t<sub>HZCE</sub> is less than t<sub>LZCE</sub>, t<sub>HZBE</sub> is less than t<sub>LZDE</sub>, t<sub>HZCE</sub>, t<sub>HZCE</sub>, t<sub>HZDE</sub>, and t<sub>HZWE</sub> is less than t<sub>LZWE</sub> for any device.

16. t<sub>HZCE</sub>, t<sub>HZCE</sub>, t<sub>HZEE</sub>, and t<sub>HZWE</sub> transitions are measured when the outputs enter a high impedance state.

17. The internal write time of the memory is defined by the overlap of WE = V<sub>IL</sub>, CE<sub>1</sub> = V<sub>IL</sub>, BHE or BLE or both = V<sub>IL</sub>, and CE<sub>2</sub> = V<sub>IH</sub>. All signals must be ACTIVE to initiate a write. Any of these signals can terminate a write by going INACTIVE. The data input setup and hold timing must refer to the edge of the signal that terminates the write.

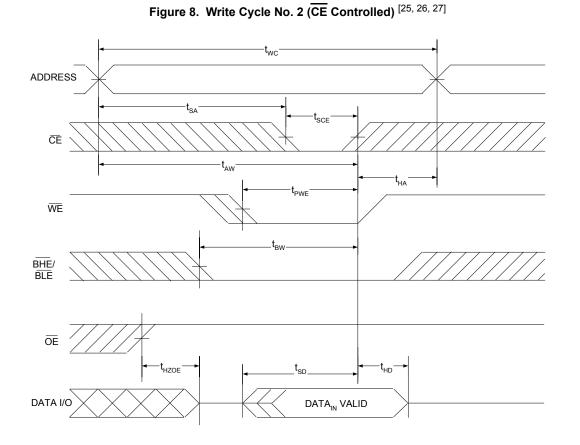

### **Switching Waveforms**

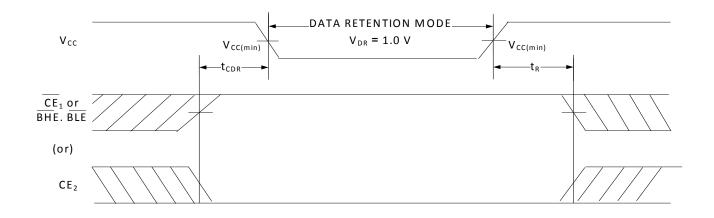

Figure 5. Read Cycle No. 1 of CY62167G (Address Transition Controlled) <sup>[18, 19]</sup>

#### Notes

18. The device is continuously selected.  $\overline{OE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$ ,  $\overline{BHE}$  or  $\overline{BLE}$  or both =  $V_{IL}$ .

19. WE is HIGH for read cycle.

20. For all dual chip enable devices,  $\overline{CE}$  is the logical combination of  $\overline{CE}_1$  and  $CE_2$ . When  $\overline{CE}_1$  is LOW and  $CE_2$  is HIGH,  $\overline{CE}$  is LOW; when  $\overline{CE}_1$  is HIGH or  $CE_2$  is LOW, CE is HIGH.

21. Address valid prior to or coincident with  $\overline{\text{CE}}$  LOW transition.

### Switching Waveforms (continued)

Notes

22. For all dual chip enable devices,  $\overline{CE}$  is the logical combination of  $\overline{CE}_1$  and  $CE_2$ . When  $\overline{CE}_1$  is LOW and  $CE_2$  is HIGH,  $\overline{CE}$  is LOW; when  $\overline{CE}_1$  is HIGH or  $CE_2$  is LOW, CE is HIGH.

23. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{|L}$ ,  $\overline{CE}_1 = V_{|L}$ ,  $\overline{BHE}$  or  $\overline{BLE}$  or both =  $V_{|L}$ , and  $CE_2 = V_{|H}$ . All signals must be ACTIVE to initiate a write and any of these signals can terminate a write by going INACTIVE. The data input setup and hold timing must refer to the edge of the signal that terminates the write.

<sup>24.</sup> Data I/O is in HI-Z state if  $\overline{CE} = V_{IH}$ , or  $\overline{OE} = V_{IH}$  or  $\overline{BHE}$ , and/or  $\overline{BLE} = V_{IH}$ .

### Switching Waveforms (continued)

- 25. Eor all dual chip enable devices,  $\overline{CE}$  is the logical combination of  $\overline{CE}_1$  and  $CE_2$ . When  $\overline{CE}_1$  is LOW and  $CE_2$  is HIGH,  $\overline{CE}$  is LOW; when  $\overline{CE}_1$  is HIGH or  $CE_2$  is LOW, CE is HIGH.

- 26. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{IL}$ ,  $\overline{EE}_1 = V_{IL}$ ,  $\overline{BHE}$  or  $\overline{BLE}$  or both =  $V_{IL}$ , and  $CE_2 = V_{IH}$ . All signals must be ACTIVE to initiate a write and any of these signals can terminate a write by going INACTIVE. The data input setup and hold timing must refer to the edge of the signal that terminates the write.

- 27. Data I/O is in high impedance state if  $\overline{CE} = V_{IH}$ , or  $\overline{OE} = V_{IH}$  or  $\overline{BHE}$ , and/or  $\overline{BLE} = V_{IH}$ .

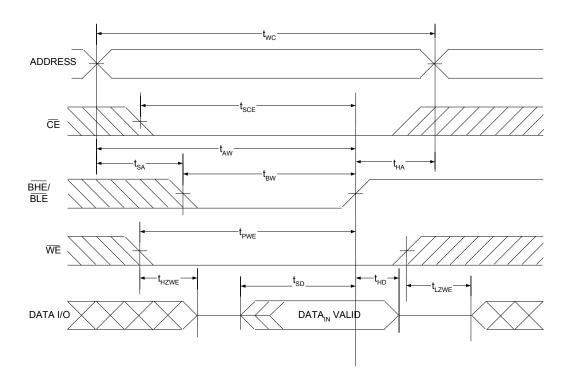

### Switching Waveforms (continued)

Figure 9. Write Cycle No. 3 (BHE/BLE Controlled, OE LOW) <sup>[28, 29, 30]</sup>

- 28. Eor all dual chip enable devices,  $\overline{CE}$  is the logical combination of  $\overline{CE}_1$  and  $CE_2$ . When  $\overline{CE}_1$  is LOW and  $CE_2$  is HIGH,  $\overline{CE}$  is LOW; when  $\overline{CE}_1$  is HIGH or  $CE_2$  is LOW,  $\overline{CE}$  is HIGH.

- 29. The internal write time of the memory is defined by the overlap of  $\overline{WE} = V_{\parallel}$ ,  $\overline{CE}_1 = V_{\parallel}$ ,  $\overline{BHE}$  or  $\overline{BLE}$  or both =  $V_{\parallel}$ , and  $CE_2 = V_{\parallel}$ . All signals must be ACTIVE to initiate a write and any of these signals can terminate a write by going INACTIVE. The data input setup and hold timing must refer to the edge of the signal that terminates the write.

- 30. Data I/O is in high impedance state if  $\overline{CE} = V_{IH}$ , or  $\overline{OE} = V_{IH}$  or  $\overline{BHE}$ , and/or  $\overline{BLE} = V_{IH}$ .

### Truth Table – CY62167G

| CE <sub>1</sub>   | CE <sub>2</sub>   | WE | OE | BHE | BLE | Inputs/Outputs                                                                                 | Mode                | Power                      |

|-------------------|-------------------|----|----|-----|-----|------------------------------------------------------------------------------------------------|---------------------|----------------------------|

| Н                 | X <sup>[31]</sup> | Х  | Х  | Х   | Х   | HI-Z                                                                                           | Deselect/Power-down | Standby (I <sub>SB</sub> ) |

| X <sup>[31]</sup> | L                 | Х  | Х  | Х   | Х   | HI-Z                                                                                           | Deselect/Power-down | Standby (I <sub>SB</sub> ) |

| X <sup>[31]</sup> | X <sup>[31]</sup> | Х  | Х  | Н   | Н   | HI-Z                                                                                           | Deselect/Power-down | Standby (I <sub>SB</sub> ) |

| L                 | Н                 | Н  | L  | L   | L   | Data Out (I/O <sub>0</sub> –I/O <sub>15</sub> )                                                | Read                | Active (I <sub>CC</sub> )  |

| L                 | Н                 | Η  | L  | Н   | L   | Data Out (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>HI-Z (I/O <sub>8</sub> –I/O <sub>15</sub> ) | Read                | Active (I <sub>CC</sub> )  |

| L                 | Н                 | Η  | L  | L   | Н   | HI-Z (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>Data Out (I/O <sub>8</sub> –I/O <sub>15</sub> ) | Read                | Active (I <sub>CC</sub> )  |

| L                 | Н                 | Н  | Н  | Х   | Х   | HI-Z                                                                                           | Output disabled     | Active (I <sub>CC</sub> )  |

| L                 | Н                 | L  | Х  | L   | L   | Data In (I/O <sub>0</sub> –I/O <sub>15</sub> )                                                 | Write               | Active (I <sub>CC</sub> )  |

| L                 | Н                 | L  | Х  | Н   | L   | Data In (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>HI-Z (I/O <sub>8</sub> –I/O <sub>15</sub> )  | Write               | Active (I <sub>CC</sub> )  |

| L                 | Н                 | L  | Х  | L   | Н   | HI-Z (I/O <sub>0</sub> –I/O <sub>7</sub> );<br>Data In (I/O <sub>8</sub> –I/O <sub>15</sub> )  | Write               | Active (I <sub>CC</sub> )  |

Note 31. The 'X' (Don't care) state for the chip enables refer to the logic state (either HIGH or LOW). Intermediate voltage levels on these pins is not permitted.

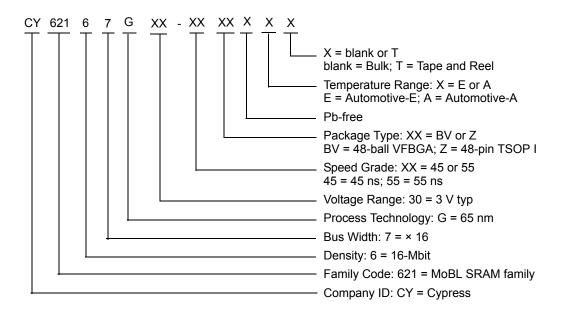

### **Ordering Information**

| Speed<br>(ns) | Ordering Code      | Package<br>Diagram | Package Type                                                  | Operating<br>Range        |

|---------------|--------------------|--------------------|---------------------------------------------------------------|---------------------------|

| 55            | CY62167G30-55BVXE  | 51-85150           | 48-ball VFBGA (6 × 8 × 1 mm) (Pb-free),<br>Package Code: BZ48 | Automotive-E Automotive-A |

|               | CY62167G30-55BVXET |                    |                                                               |                           |

|               | CY62167G30-55ZXE   | 51-85183           | 48-pin TSOP I (12 × 18.4 × 1 mm) (Pb-free),                   |                           |

|               | CY62167G30-55ZXET  |                    | Package Code: Z48A                                            |                           |

| 45            | CY62167G30-45ZXA   | 51-85183           |                                                               |                           |

|               | CY62167G30-45ZXAT  |                    | Package Code: Z48A                                            |                           |

|               | CY62167G30-45BVXA  | 51-85150           | 48-ball VFBGA (6 × 8 × 1 mm) (Pb-free),                       |                           |

|               | CY62167G30-45BVXAT |                    | Package Code: BZ48                                            |                           |

### **Ordering Code Definitions**

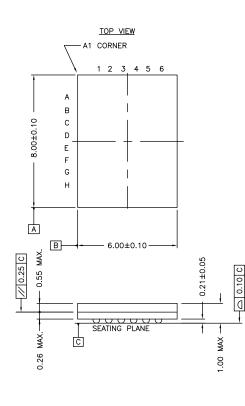

### Package Diagram

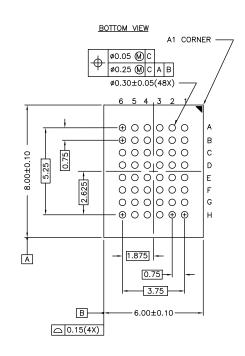

Figure 10. 48-ball VFBGA (6 × 8 × 1.0 mm) BV48/BZ48 Package Outline, 51-85150

NOTE:

PACKAGE WEIGHT: See Cypress Package Material Declaration Datasheet (PMDD) posted on the Cypress web.

51-85150 \*H

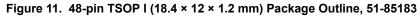

### Package Diagram (continued)

| SYMBOL | DIMENSIONS  |        |      |

|--------|-------------|--------|------|

| STMBOL | MIN.        | NOM.   | MAX. |

| A      | —           | —      | 1.20 |

| A1     | 0.05        | —      | 0.15 |

| A2     | 0.95        | 1.00   | 1.05 |

| b1     | 0.17        | 0.20   | 0.23 |

| b      | 0.17        | 0.22   | 0.27 |

| c1     | 0.10        | _      | 0.16 |

| с      | 0.10        | —      | 0.21 |

| D      | 20.00 BASIC |        |      |

| D1     | 18.40 BASIC |        |      |

| E      | 12.00 BASIC |        |      |

| е      | 0.          | 50 BAS | IC   |

| L      | 0.50        | 0.60   | 0.70 |

| θ      | 0°          | _      | 8    |

| R      | 0.08        | —      | 0.20 |

| N      |             | 48     |      |

#### NOTES:

- <u>DIMENSIONS ARE IN MILLIMETERS (mm).</u>

- 2. PIN 1 IDENTIFIER FOR STANDARD PIN OUT (DIE UP).

- 3. PIN 1 IDENTIFIER FOR REVERSE PIN OUT (DIE DOWN): INK OR LASER MARK.

- TO BE DETERMINED AT THE SEATING PLANE C-. THE SEATING PLANE IS DEFINED AS THE PLANE OF CONTACT THAT IS MADE WHEN THE PACKAGE LEADS ARE ALLOWED TO REST FREELY ON A FLAT HORIZONTAL SURFACE.

- DIMENSIONS D1 AND E DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE MOLD PROTRUSION ON E IS 0.15mm PER SIDE AND ON D1 IS 0.25mm PER SIDE.

- Image: Construction of the second second

- THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10mm AND 0.25mm FROM THE LEAD TIP.

- LEAD COPLANARITY SHALL BE WITHIN 0.10mm AS MEASURED FROM THE SEATING PLANE.

- DIMENSION "e" IS MEASURED AT THE CENTERLINE OF THE LEADS.

- 10. JEDEC SPECIFICATION NO. REF: MO-142(D)DD.

51-85183 \*F

### Acronyms

| Acronym | Description                             |  |  |

|---------|-----------------------------------------|--|--|

| BHE     | byte high enable                        |  |  |

| BLE     | byte low enable                         |  |  |

| CE      | chip enable                             |  |  |

| CMOS    | complementary metal oxide semiconductor |  |  |

| I/O     | input/output                            |  |  |

| OE      | output enable                           |  |  |

| SRAM    | static random access memory             |  |  |

| VFBGA   | very fine-pitch ball grid array         |  |  |

| WE      | write enable                            |  |  |

### **Document Conventions**

### **Units of Measure**

| Symbol | Unit of Measure |

|--------|-----------------|

| °C     | Degrees Celsius |

| MHz    | megahertz       |

| μA     | microamperes    |

| μS     | microseconds    |

| mA     | milliamperes    |

| mm     | millimeters     |

| ns     | nanoseconds     |

| Ω      | ohms            |

| %      | percent         |

| pF     | picofarads      |

| V      | volts           |

| W      | watts           |

# **Document History Page**

| Rev. | ECN No. | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *C   | 5083752 | NILE               | 01/13/2016         | Changed status from Preliminary to Final.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *D   | 5130998 | NILE               | 02/12/2016         | Updated Logic Block Diagram – CY62167G.<br>Updated Pin Configurations:<br>Added Note 3 and referred the same note in Figure 2.<br>Updated DC Electrical Characteristics:<br>Updated Note 7.<br>Updated Data Retention Characteristics:<br>Updated Note 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| *E   | 5555173 | VINI               | 01/18/2017         | Updated Features:<br>Added "AEC-Q100 qualified".<br>Updated Maximum Ratings:<br>Updated Note 5 (Replaced "2 ns" with "20 ns").<br>Updated DC Electrical Characteristics:<br>Replaced "55 ns (Automotive-E)" with "45 ns (Automotive-A)" in column<br>heading.<br>Replaced "55 ns (Automotive-A)" with "55 ns (Automotive-E)" in column<br>heading.<br>Changed minimum value of V <sub>OH</sub> parameter from 2.2 V to 2.4 V corresponding<br>to Operating Range "2.7 V to 3.6 V".<br>Changed minimum value of V <sub>IH</sub> parameter from 2.0 V to 1.8 V corresponding<br>to Operating Range "2.2 V to 2.7 V".<br>Updated Ordering Information:<br>Updated part numbers.<br>Updated Ordering Code Definitions.<br>Updated Package Diagram:<br>spec 51-85183 – Changed revision from *D to *E.<br>Updated to new template.<br>Completing Sunset Review. |

| *F   | 5725191 | NILE               | 05/03/2017         | Updated DC Electrical Characteristics:<br>Fixed typo in values of $I_{IX}$ and $I_{OZ}$ parameters (both "Min" and "Max" columns<br>Fixed typo in values of $I_{SB1}$ and $I_{SB2}$ parameters (only "Max" column).<br>Updated Data Retention Characteristics:<br>Fixed typo in values of $I_{CCDR}$ parameter (only "Max" column).<br>Updated to new template.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |