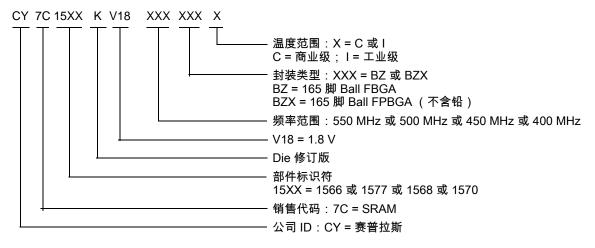

# CY7C1566KV18/CY7C1577KV18 CY7C1568KV18/CY7C1570KV18

# 72-Mbit DDR II+ SRAM 2- 字突发架构 (2.5 周期读延迟)

# 特性

- 72-Mbit 容量 (8 M × 8、8 M × 9、4 M × 18、2 M × 36)

- 550 MHz 时钟实现高带宽

- 2 字突发降低地址总线频率

- 双数据速率 (DDR) 接口 (数据传输速率 1100 MHz), 工作频率 550 MHz

- 可提供 2.5 个时钟周期延迟

- 两个输入时钟 (K 和 K),能够实现精确的 DDR 时序 □ SRAM 仅使用上升沿

- 随路时钟 (CQ 和 CQ),能够简化高速系统中的数据捕获

- 数据有效引脚 (QVLD) 表示输出上的有效数据

- 同步内部自定时写入

- 当 DOFF 置为高电平时, DDR II+ 会有 2.5 个周期的读延迟

- 当 DOFF 置为低电平时,其工作方式与 QDR I 器件类似,会有 1 个周期的读延迟

- 内核 V<sub>DD</sub> = 1.8 V ± 0.1 V ; I/O V<sub>DDQ</sub> = 1.4 V 至 V<sub>DD</sub><sup>[1]</sup>

□ 支持 1.5V 和 1.8 V I/O 电源

- HSTL 输入和驱动能力可调的 HSTL 输出缓冲器

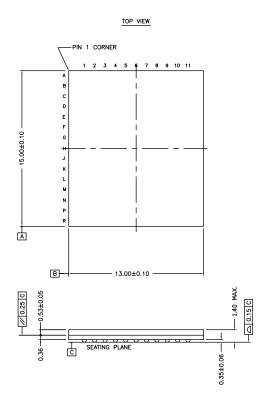

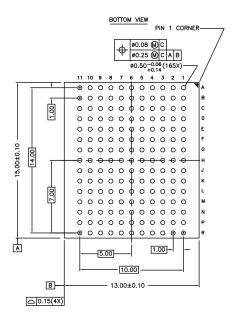

- 可提供 165 脚小间距 BGA (FBGA) 封装 (13 × 15 × 1.4 mm)

- 有含铅和不含铅封装可供选择

- JTAG 1149.1 兼容测试端口

- 锁相环 (PLL),能够实现精确的数据放置

### 配置

#### 具有 2.5 周期的读周期延迟:

CY7C1566KV18 – 8 M × 8 CY7C1577KV18 – 8 M × 9 CY7C1568KV18 – 4 M × 18 CY7C1570KV18 – 2 M × 36

### 功能描述

CY7C1566KV18、CY7C1577KV18、CY7C1568KV18 和 CY7C1570KV18 都是包含 DDR II+ 架构的 1.8 V 同步流水线 SRAM。 DDR II+ 包含一个带有先进同步外围电路的 SRAM 内核。用于读和写的地址被锁止在输入 (K) 时钟的备选上升沿。写数据同时在 K 和 K 的上升沿被寄存。读数据同时在 K 和 K 的上升沿被寄存。读数据同时在 K 和 K 的上升沿被驱动。每个地址都与两个 8 位字 (CY7C1566KV18)、9 位字 (CY7C1577KV18)、18 位字 (CY7C1568KV18) 或 36 位字 (CY7C1570KV18) 相关联,这些字以突发模式按顺序传入或传出器件。

异步输入包含输出阻抗匹配输入 (ZQ)。 同步数据输出 (Q,与数据输入 D 共享相同的物理引脚)与两个输出随路时钟 CQ/CQ 紧密匹配,消除了系统设计中从单个 DDR SRAM 单独捕获数据的需要。

所有同步输入都会通过由 K 或  $\overline{K}$  控制的输入寄存器。所有数据输出都会通过由 K 或  $\overline{K}$  输入时钟控制的输出寄存器。写操作通过片上同步自定时写电路进行。

### 产品选择指南

| 说明     |     | 550 MHz | 500 MHz | 450 MHz | 400 MHz | 单位  |

|--------|-----|---------|---------|---------|---------|-----|

| 最大工作频率 |     | 550     | 500     | 450     | 400     | MHz |

| 最大工作电流 | ×8  | 740     | 690     | 630     | 580     | mA  |

|        | ×9  | 740     | 690     | 630     | 580     |     |

|        | ×18 | 760     | 700     | 650     | 590     |     |

|        | ×36 | 970     | 890     | 820     | 750     |     |

注

1. 赛普拉斯 QDR II+ 器件超过了 QDR 联盟规范,可支持 V<sub>DDQ</sub> = 1.4 V 到 V<sub>DD</sub>。

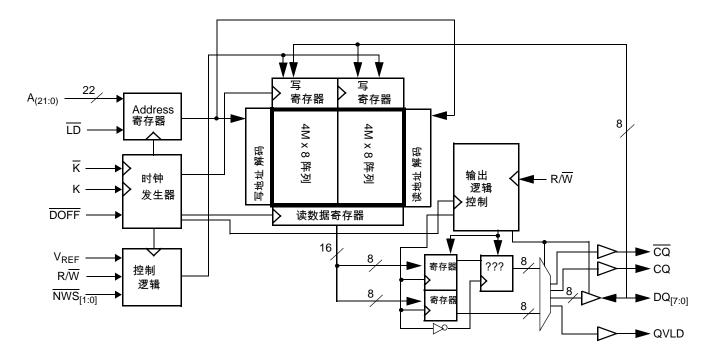

# 逻辑框图 (CY7C1566KV18)

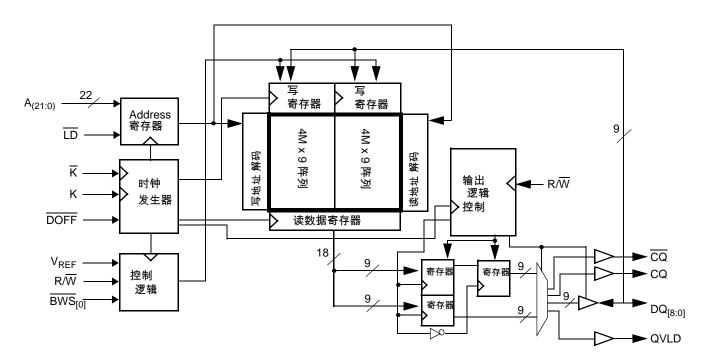

# 逻辑框图 (CY7C1577KV18)

文档编号: 001-63674 修订版 \*B 第 2 页, 共 页

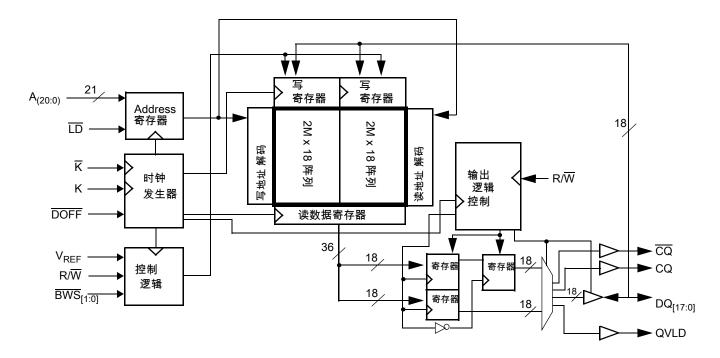

# 逻辑框图 (CY7C1568KV18)

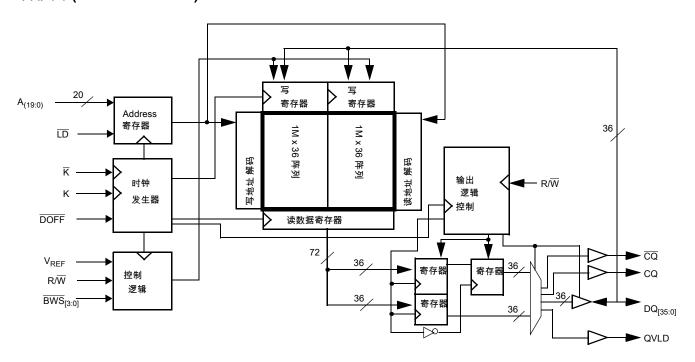

# 逻辑框图 (CY7C1570KV18)

文档编号:001-63674 修订版 \*B 第 3 页, 共 页

# 目录

|                                         | .1     |

|-----------------------------------------|--------|

| 特性                                      |        |

| 配置                                      |        |

| 功能描述                                    | 1      |

| 产品选择指南                                  |        |

| 逻辑框图 (CY7C1566KV18)                     |        |

| 逻辑框图 (CY7C1577KV18)                     |        |

| 逻辑框图 (CY7C1568KV18)                     |        |

| 逻辑框图 (CY7C1570KV18)                     | 3      |

| 引脚配置                                    | 5      |

| 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 引脚分布 | . 5    |

| 引脚定义                                    |        |

| 功能概述                                    | 9      |

| 读操作                                     | . 9    |

| 写操作                                     | . 9    |

| 字节写操作                                   |        |

| DDR 操作                                  |        |

| 深度扩展 (Depth Expansion)                  |        |

| 可编程阻抗                                   |        |

| 随路时钟                                    |        |

| 有效数据指示器 (QVLD)                          | .9     |

| PLL                                     |        |

| 应用示例                                    |        |

| 真值表                                     |        |

| 写周期说明                                   |        |

| 写周期说明                                   |        |

| 写周期说明                                   |        |

| IEEE 1149.1 串行边界扫描 (JTAG)               | <br>13 |

| 禁用 JTAG 特性                              | 13     |

| 测试端口 - 测试时钟                             | 13     |

| 测试模式选择 (TMS)                            |        |

| 测试数据输入 (TDI)                            |        |

| <ul><li></li></ul>                      |        |

| 执行 TAP 复位                               |        |

| TAP 寄存器                                 | 13     |

| TAP 指令集                                 |        |

| TAP 控制器状态图                              |        |

| TAP 控制器框图                               |        |

| · · · · · · · · · · · · · · · · · · ·   | . •    |

| TAP 电气特性                                 |    |

|------------------------------------------|----|

| TAP 交流开关特性                               | 17 |

| TAP 时序和测试条件                              | 17 |

| 标识寄存器定义                                  | 18 |

| 扫描寄存器大小                                  | 18 |

| 指令代码                                     |    |

|                                          | 19 |

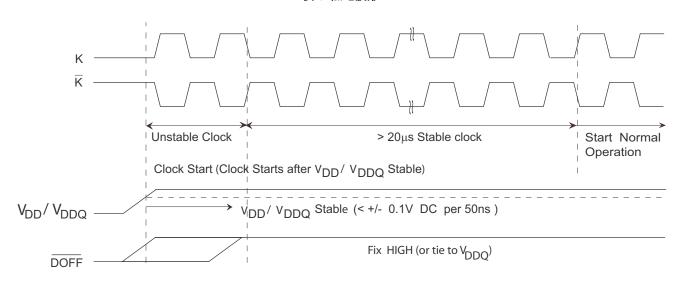

| DDR II+ SRAM 中的加电顺序                      | 20 |

| 加电顺序                                     |    |

| PLL 限制                                   |    |

| 最大额定值                                    |    |

| 工作范围                                     |    |

| 抗中子软失效                                   | 21 |

| 电气特性                                     | 21 |

| DC Electrical Characteristics            |    |

| 交流电气特性                                   | 22 |

| 电容                                       |    |

| 热阻                                       |    |

| 开关特性                                     |    |

| 开关波形                                     | 25 |

| 读 / 写 / 取消选中操作过程 <sup>[35, 36, 37]</sup> | 25 |

| 订购代码定义                                   | 26 |

| 订购信息                                     | 26 |

| 封装图                                      | 27 |

| 缩略语                                      | 28 |

| 文档规范                                     | 28 |

| 测量单位                                     | 28 |

| 文档修订记录页                                  |    |

| 销售、解决方案和法律信息                             |    |

| 全球销售和设计支持                                | 29 |

| 产品                                       |    |

| PSoC 解决方案                                | 29 |

# 引脚配置

The pin configurations for CY7C1566KV18, CY7C1577KV18, CY7C1568KV18, and CY7C1570KV18 follow. [2]

# 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 引脚分布

CY7C1566KV18 (8 M × 8)

|   | 1    | 2         | 3         | 4         | 5                | 6        | 7                | 8                  | 9         | 10               | 11  |

|---|------|-----------|-----------|-----------|------------------|----------|------------------|--------------------|-----------|------------------|-----|

| Α | CQ   | Α         | Α         | R/W       | NWS <sub>1</sub> | K        | NC/144M          | LD                 | Α         | Α                | CQ  |

| В | NC   | NC        | NC        | Α         | NC/288M          | K        | NWS <sub>0</sub> | Α                  | NC        | NC               | DQ3 |

| С | NC   | NC        | NC        | $V_{SS}$  | Α                | Α        | Α                | $V_{SS}$           | NC        | NC               | NC  |

| D | NC   | NC        | NC        | $V_{SS}$  | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{SS}$           | NC        | NC               | NC  |

| E | NC   | NC        | DQ4       | $V_{DDQ}$ | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{\mathrm{DDQ}}$ | NC        | NC               | DQ2 |

| F | NC   | NC        | NC        | $V_{DDQ}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | NC               | NC  |

| G | NC   | NC        | DQ5       | $V_{DDQ}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | NC               | NC  |

| Н | DOFF | $V_{REF}$ | $V_{DDQ}$ | $V_{DDQ}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | $V_{DDQ}$ | V <sub>REF</sub> | ZQ  |

| J | NC   | NC        | NC        | $V_{DDQ}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | DQ1              | NC  |

| K | NC   | NC        | NC        | $V_{DDQ}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC        | NC               | NC  |

| L | NC   | DQ6       | NC        | $V_{DDQ}$ | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{DDQ}$          | NC        | NC               | DQ0 |

| М | NC   | NC        | NC        | $V_{SS}$  | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{SS}$           | NC        | NC               | NC  |

| N | NC   | NC        | NC        | $V_{SS}$  | Α                | Α        | Α                | $V_{SS}$           | NC        | NC               | NC  |

| Р | NC   | NC        | DQ7       | Α         | Α                | QVLD     | Α                | Α                  | NC        | NC               | NC  |

| R | TDO  | TCK       | Α         | Α         | Α                | NC       | Α                | Α                  | Α         | TMS              | TDI |

### CY7C1577KV18 (8 M × 9)

|   | 1    | 2         | 3                  | 4                  | 5               | 6        | 7                | 8         | 9                  | 10        | 11  |

|---|------|-----------|--------------------|--------------------|-----------------|----------|------------------|-----------|--------------------|-----------|-----|

| Α | CQ   | Α         | Α                  | R/W                | NC              | K        | NC/144M          | LD        | Α                  | Α         | CQ  |

| В | NC   | NC        | NC                 | Α                  | NC/288M         | K        | BWS <sub>0</sub> | Α         | NC                 | NC        | DQ3 |

| С | NC   | NC        | NC                 | $V_{SS}$           | Α               | Α        | Α                | $V_{SS}$  | NC                 | NC        | NC  |

| D | NC   | NC        | NC                 | $V_{SS}$           | $V_{SS}$        | $V_{SS}$ | $V_{SS}$         | $V_{SS}$  | NC                 | NC        | NC  |

| E | NC   | NC        | DQ4                | $V_{DDQ}$          | $V_{SS}$        | $V_{SS}$ | $V_{SS}$         | $V_{DDQ}$ | NC                 | NC        | DQ2 |

| F | NC   | NC        | NC                 | $V_{DDQ}$          | $V_{DD}$        | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | NC        | NC  |

| G | NC   | NC        | DQ5                | $V_{DDQ}$          | $V_{DD}$        | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | NC        | NC  |

| Н | DOFF | $V_{REF}$ | $V_{\mathrm{DDQ}}$ | $V_{\mathrm{DDQ}}$ | $V_{DD}$        | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | $V_{\mathrm{DDQ}}$ | $V_{REF}$ | ZQ  |

| J | NC   | NC        | NC                 | $V_{DDQ}$          | $V_{DD}$        | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | DQ1       | NC  |

| K | NC   | NC        | NC                 | $V_{DDQ}$          | $V_{DD}$        | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | NC        | NC  |

| L | NC   | DQ6       | NC                 | $V_{DDQ}$          | V <sub>SS</sub> | $V_{SS}$ | V <sub>SS</sub>  | $V_{DDQ}$ | NC                 | NC        | DQ0 |

| М | NC   | NC        | NC                 | $V_{SS}$           | V <sub>SS</sub> | $V_{SS}$ | V <sub>SS</sub>  | $V_{SS}$  | NC                 | NC        | NC  |

| N | NC   | NC        | NC                 | $V_{SS}$           | Α               | Α        | Α                | $V_{SS}$  | NC                 | NC        | NC  |

| Р | NC   | NC        | DQ7                | Α                  | Α               | QVLD     | Α                | Α         | NC                 | NC        | DQ8 |

| R | TDO  | TCK       | Α                  | Α                  | Α               | NC       | Α                | Α         | Α                  | TMS       | TDI |

文档编号:001-63674 修订版\*B 第5页,共页

**注:** 2. NC/144M 和 NC/288M 未连接到 Die,可连接到任何电压电平。

# 引脚配置 (continued)

The pin configurations for CY7C1566KV18, CY7C1577KV18, CY7C1568KV18, and CY7C1570KV18 follow. [2]

# 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 引脚分布 CY7C1568KV18 (4 M × 18)

|   | 1    | 2         | 3                  | 4                  | 5                | 6        | 7                | 8                  | 9                  | 10        | 11  |

|---|------|-----------|--------------------|--------------------|------------------|----------|------------------|--------------------|--------------------|-----------|-----|

| Α | CQ   | Α         | Α                  | R/W                | BWS <sub>1</sub> | K        | NC/144M          | LD                 | Α                  | Α         | CQ  |

| В | NC   | DQ9       | NC                 | Α                  | NC/288M          | K        | BWS <sub>0</sub> | Α                  | NC                 | NC        | DQ8 |

| С | NC   | NC        | NC                 | $V_{SS}$           | Α                | NC       | Α                | $V_{SS}$           | NC                 | DQ7       | NC  |

| D | NC   | NC        | DQ10               | $V_{SS}$           | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{SS}$           | NC                 | NC        | NC  |

| E | NC   | NC        | DQ11               | $V_{DDQ}$          | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{DDQ}$          | NC                 | NC        | DQ6 |

| F | NC   | DQ12      | NC                 | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC                 | NC        | DQ5 |

| G | NC   | NC        | DQ13               | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC                 | NC        | NC  |

| Н | DOFF | $V_{REF}$ | $V_{\mathrm{DDQ}}$ | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | $V_{\mathrm{DDQ}}$ | $V_{REF}$ | ZQ  |

| J | NC   | NC        | NC                 | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC                 | DQ4       | NC  |

| K | NC   | NC        | DQ14               | $V_{DDQ}$          | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$          | NC                 | NC        | DQ3 |

| L | NC   | DQ15      | NC                 | $V_{\mathrm{DDQ}}$ | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{\mathrm{DDQ}}$ | NC                 | NC        | DQ2 |

| М | NC   | NC        | NC                 | $V_{SS}$           | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{SS}$           | NC                 | DQ1       | NC  |

| N | NC   | NC        | DQ16               | $V_{SS}$           | Α                | Α        | Α                | $V_{SS}$           | NC                 | NC        | NC  |

| Р | NC   | NC        | DQ17               | Α                  | Α                | QVLD     | Α                | Α                  | NC                 | NC        | DQ0 |

| R | TDO  | TCK       | Α                  | Α                  | Α                | NC       | Α                | Α                  | Α                  | TMS       | TDI |

### CY7C1570KV18 (2 M × 36)

|   | 1    | 2         | 3         | 4                  | 5                | 6        | 7                | 8         | 9                  | 10        | 11   |

|---|------|-----------|-----------|--------------------|------------------|----------|------------------|-----------|--------------------|-----------|------|

| Α | Q    | NC/144M   | Α         | R/W                | BWS <sub>2</sub> | K        | BWS <sub>1</sub> | LD        | Α                  | Α         | CQ   |

| В | NC   | DQ27      | DQ18      | Α                  | BWS <sub>3</sub> | K        | BWS <sub>0</sub> | Α         | NC                 | NC        | DQ8  |

| С | NC   | NC        | DQ28      | $V_{SS}$           | Α                | NC       | Α                | $V_{SS}$  | NC                 | DQ17      | DQ7  |

| D | NC   | DQ29      | DQ19      | $V_{SS}$           | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{SS}$  | NC                 | NC        | DQ16 |

| E | NC   | NC        | DQ20      | $V_{DDQ}$          | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{DDQ}$ | NC                 | DQ15      | DQ6  |

| F | NC   | DQ30      | DQ21      | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | NC        | DQ5  |

| G | NC   | DQ31      | DQ22      | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | NC        | DQ14 |

| Н | DOFF | $V_{REF}$ | $V_{DDQ}$ | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | $V_{\mathrm{DDQ}}$ | $V_{REF}$ | ZQ   |

| J | NC   | NC        | DQ32      | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | DQ13      | DQ4  |

| K | NC   | NC        | DQ23      | $V_{\mathrm{DDQ}}$ | $V_{DD}$         | $V_{SS}$ | $V_{DD}$         | $V_{DDQ}$ | NC                 | DQ12      | DQ3  |

| L | NC   | DQ33      | DQ24      | $V_{DDQ}$          | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{DDQ}$ | NC                 | NC        | DQ2  |

| М | NC   | NC        | DQ34      | $V_{SS}$           | $V_{SS}$         | $V_{SS}$ | $V_{SS}$         | $V_{SS}$  | NC                 | DQ11      | DQ1  |

| N | NC   | DQ35      | DQ25      | $V_{SS}$           | Α                | Α        | Α                | $V_{SS}$  | NC                 | NC        | DQ10 |

| Р | NC   | NC        | DQ26      | Α                  | Α                | QVLD     | Α                | Α         | NC                 | DQ9       | DQ0  |

| R | TDO  | TCK       | Α         | Α                  | Α                | NC       | А                | Α         | Α                  | TMS       | TDI  |

文档编号: 001-63674 修订版 \*B 第 6 页, 共 页

# 引脚定义

| 引脚名称                                                                               | I/O         | 引脚说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ <sub>[x:0]</sub>                                                                | 输入输出<br>同步  | 数据输入输出信号。在有效的写操作期间,在 K 和 $\overline{\text{K}}$ 时钟的上升沿被采样。在有效的读操作期间,这些引脚会输出所请求的数据。在读操作期间,在 K 和 $\overline{\text{K}}$ 时钟的上升沿输出有效数据。未选中读端口时, $Q_{[x:0]}$ 会自动进入三态。 CY7C1566KV18 – $DQ_{[7:0]}$ CY7C1577KV18 – $DQ_{[8:0]}$ CY7C1568KV18 – $DQ_{[17:0]}$ CY7C1568KV18 – $DQ_{[35:0]}$                                                                                                                                                                                                                                                                                                                                                                           |

| LD                                                                                 | 输入<br>同步    | 同步负载。在 K 时钟的上升沿被采样。定义总线周期序列时,该输入为低电平。该定义包括地址和读 / 写方向。所有数据操作在 2 数据突发上运行。LD 必须满足 K 边沿周围的建立和保持时间。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NWS <sub>0</sub> ,<br>NWS <sub>1</sub>                                             | 输入<br>同步    | 半字节写选择 $0$ 、 $1-$ 低电平有效(仅限 CY7C1566KV18)。在写操作期间,在 K 和 $\overline{\text{K}}$ 时钟的上升沿被采样。用于选择在写操作的当前部分,将哪个半字节写入到器件中。不写入的半字节将保持不变。 $\overline{\text{NWS}}_0$ 控制 $D_{[3:0]}$ 和 $\overline{\text{NWS}}_1$ 控制 $D_{[7:4]}$ 。 所有 " 半字节写选择 (Nibble Write Select)" 均在数据采样的相同沿被采样。取消选中" 半字节写选择 (Nibble Write Select)" 会忽略相应的数据半字节,并且不会将其写入到器件中。                                                                                                                                                                                                                                                                                                                        |

| BWS <sub>0</sub> ,<br>BWS <sub>1</sub> ,<br>BWS <sub>2</sub> ,<br>BWS <sub>3</sub> | 输入<br>同步    | 字节写选择 $0$ 、 $1$ 、 $2$ 和 $3$ – 低电平有效。在写操作期间,在 K 和 $\overline{\text{K}}$ 时钟的上升沿被采样。用于选择在写操作的当前部分,将哪个字节写入到器件中。不写入的字节将保持不变。 CY7C1577KV18 – $\overline{\text{BWS}}_0$ 控制 $D_{[8:0]}$ CY7C1568KV18 – $\overline{\text{BWS}}_0$ 控制 $D_{[8:0]}$ 和 $\overline{\text{BWS}}_1$ 控制 $D_{[17:9]}$ 是制 $D_{[26:18]}$ 以及 $\overline{\text{BWS}}_3$ 控制 $D_{[35:27]}$ 。 CY7C1570KV18 – $\overline{\text{BWS}}_0$ 控制 $D_{[8:0]}$ , $\overline{\text{BWS}}_1$ 控制 $D_{[17:9]}$ , $\overline{\text{BWS}}_2$ 控制 $D_{[26:18]}$ 以及 $\overline{\text{BWS}}_3$ 控制 $D_{[35:27]}$ 。 所有"字节写选择 (Byte Write Select)" 均在数据采样的相同沿被采样。取消选中"字节写选择 (Byte Write Select)" 会忽略相应的数据字节,并且不会将其写入到器件中。 |

| A                                                                                  | 输入<br>同步    | 地址输入。在有效的读操作和写操作期间,在 K 时钟的上升沿被采样。这些地址输入复用于读操作和写操作。在器件内部,CY7C1566KV18 采取的是 8M × 8(2 个阵列,每个阵列均为 4M × 8)的组织方式,CY7C1577KV18 采取的是 8M × 9(2 个阵列,每个阵列均为 4M × 9)的组织方式,CY7C1568KV18 采取 4M × 18(2 个阵列,每个阵列均为 2M × 18)的组织方式,CY7C1570KV18 采取 2M × 36(2 个阵列,每个阵列均为 1M × 36)的组织方式。                                                                                                                                                                                                                                                                                                                                                                                       |

| R/W                                                                                | 输入<br>同步    | 同步读或写输入。当 $\overline{LD}$ 为低电平时,该输入指定加载的地址的访问类型 (当 $R/\overline{W}$ 为高电平时读取,当 $R/\overline{W}$ 为低电平时写入)。 $R/\overline{W}$ 必须满足 $K$ 边沿周围的建立和保持时间。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| QVLD                                                                               | 有效输出指示<br>器 | 有效输出指示器。Q 有效表示有效输出数据。QVLD 与 CQ 和 CQ 的边沿对齐。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| К                                                                                  | 输入时钟        | 正向输入时钟输入。K 的上升沿用于捕获器件的同步输入,并通过 Q <sub>[x:0]</sub> 输出数据。所有访问都在 K 的上<br>升沿启动。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| K                                                                                  | 输入时钟        | 负向输入时钟输入。 $\overline{K}$ 用于捕获器件的同步输入,并通过 $Q_{[x:0]}$ 输出数据。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CQ                                                                                 | 随路时钟        | 同步随路时钟输出。这是一个自由运行的时钟,与 QDR II+ 的输入时钟 (K) 保持同步。随路时钟的时序如第 24 页的 开关特性所示。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CQ                                                                                 | 随路时钟        | 同步随路时钟输出。这是一个自由运行的时钟,与 QDR II+ 的输入时钟 (K) 保持同步。随路时钟的时序如第 24 页的 开关特性所示。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ZQ                                                                                 | 输入          | 输出阻抗匹配输入。此输入用于调整器件输出相对于系统数据总线的阻抗。CQ、 $\overline{CQ}$ 和 $Q_{[x:0]}$ 输出阻抗为 $0.2 \times RQ$ 。其中,RQ 是位于 ZQ 与接地之间的电阻。也可以将此引脚直接连接到 $V_{DDQ}$ ,这样会启用最小阻抗模式。此引脚不能直接连接到 GND,也不能保持未连接状态。                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DOFF                                                                               | 输入          | PLL 关闭 – 低电平有效。将此引脚接地会关闭器件内部的 PLL。PLL 处于关闭状态时,工作时序会与本数据表中列出的时序有所不同。在正常工作时,请将此引脚通过一个 10 KΩ 或更小的电阻上拉。PLL 处于关闭状态时,器件会以 DDR Ⅰ模式工作。在此模式下,器件能够以高达 167 MHz 的频率工作,同时满足 DDR Ⅰ 时序要求。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

文档编号:001-63674 修订版 \*B 第 7 页, 共 页

# 引脚定义 (continued)

| 引脚名称      | I/O        | 引脚说明                                      |

|-----------|------------|-------------------------------------------|

| TDO       | 输出         | JTAG 的测试数据输出 (TDO)                        |

| TCK       | 输入         | JTAG 的测试时钟 (TCK) 引脚                       |

| TDI       | 输入         | JTAG 的测试数据输入 (TDI) 引脚                     |

| TMS       | 输入         | JTAG 的测试模式选择 (TMS) 引脚                     |

| NC        | 不可用        | 未连接到 die。可连接到任何电压电平。                      |

| NC/144M   | 输入         | 未连接到 die。可连接到任何电压电平。                      |

| NC/288M   | 输入         | 未连接到 die。可连接到任何电压电平。                      |

| $V_{REF}$ | 输入 -<br>参考 | 参考电压输入。静态输入,用于设置 HSTL 输入、输出和 AC 测量点的参考电平。 |

| $V_{DD}$  | 电源         | 器件内核的电源输入                                 |

| $V_{SS}$  | 接地         | 器件的接地                                     |

| $V_{DDQ}$ | 电源         | 器件输出的电源输入                                 |

### 功能概述

CY7C1566KV18、CY7C1577KV18、CY7C1568KV18 和 CY7C1570KV18 同步的流水线突发 SRAM,包含一个 DDR 接口,当  $\overline{\text{DOFF}}$  引脚连接到高电平时,会有 2.5 个周期的读延迟。当  $\overline{\text{DOFF}}$  引脚置为低电平或连接到  $V_{\text{SS}}$  时,器件会以 DDR I 模式工作,并有 1 个时钟周期的读延迟。

访问都在正向输入时钟 (K) 的上升沿启动。所有同步的输入和输出时序都参照输入时钟 (K 和  $\overline{\mathsf{K}}$ ) 的上升沿。

所有同步数据输入  $(D_{[x:0]})$  都会通过由输入时钟  $(K \ n \ \overline{K})$  控制的输入寄存器。所有同步数据输出  $(Q_{[x:0]})$  都会通过由输入时钟  $(K \ n \ \overline{K})$  控制的输出寄存器。

所有同步控制(RPS、WPS、NWS[x:0] BWS[x:0])输入都会通过由输入时钟(K和 $_K$ )的上升沿控制的输入寄存器。

#### 读操作

CY7C1568KV18 在器件内部采取的是 2 M × 18 的两个阵列的组织方式。访问在 2 个连续的 18 位数据字的突发中完成。通过在正向输入时钟 (K) 的上升沿将 R/W 置为高电平并将  $\overline{LD}$  置为低电平,即可启动读操作。输入的地址会存储在读地址寄存器中。在  $\overline{K}$  时钟的下两个上升沿,会使用  $\overline{K}$  作为输出时序参考,将相应的 18 位数据字写入到  $Q_{[17:0]}$ 。在接下来的  $\overline{K}$  上升沿,下一个 18 位数据字会写入到  $Q_{[17:0]}$ 。 所请求的数据在输入时钟 ( $\overline{K}$  )上升沿后的 0.45 ns 内有效。若要保持内部逻辑,必须完成每次读访问。读访问都在正向输入时钟 ( $\overline{K}$ ) 的上升沿启动。

未选中读端口时,CY7C1568KV18 首先完成待处理的读数据操作。内部同步电路会在负向输入时钟  $(\overline{K})$  的下一个上升沿自动使输出进入三态。这样一来,在深度扩展的情况下,无需插入等待状态,即可在器件之间实现切换。

#### 写操作

通过在正向输入时钟 (K) 的上升沿将 R/W 置为低电平并将  $\overline{\text{LD}}$  置为低电平,即可启动写操作。呈现给地址输入的地址会存储在写地址寄存器中。如果  $\overline{\text{BWS}}_{[1:0]}$  均置为有效,则在以下 K 时钟上升沿,呈现给  $\overline{\text{D}}_{[17:0]}$  的数据会被锁存,并会存储到 18 位写数据寄存器中。如果  $\overline{\text{BWS}}_{[1:0]}$  均置为有效,则在接下来的负向输入时钟 ( $\overline{\text{K}}$ ) 上升沿,呈现给  $\overline{\text{D}}_{[17:0]}$  的信息将被存储到写数据寄存器中。36 位数据随后会写入到内存阵列的指定位置。写访问在每一个正向输入时钟 (K) 的上升沿启动。这样做即可传输数据流,从而在每个输入时钟 (K) 和  $\overline{\text{K}}$ )的上升沿将 18 位数据传入器件。

未选中写端口时,器件会在待定写操作完成之后忽略所有输入。

#### 字节写操作

CY7C1568KV18 支持字节写操作。 关于写操作的启动,请参见写操作 一节。写入哪些字节由 BWS<sub>0</sub> 和 BWS<sub>1</sub> 决定,并且字节会以每组 18 位数据字的方式被采样。 在写操作的数据部分,如果将相应的"字节写选择"置为输入,则会锁存当前呈现的数据并将其写入到器件中。否则,器件中存储的该字节的数据将保持不变。此特性用于将读操作、修改操作或写操作简化为字节写操作。

#### DDR 操作

CY7C1568KV18 可通过高时钟频率实现高性能操作 (通过流水线实现)和 DDR 模式操作。CY7C1568KV18 在从读周期到写周期跃变期间需要两个无操作 (NOP) 周期。在较高的频率,某些应用需要第三个 NOP 周期才能避免竞争

如果读取发生在写周期之后,则写入的地址和数据存储在寄存器中。由于 SRAM 不能在不与读取冲突的情况下将最后一个字写入到阵列,所以写信息被存储。数据停留在该寄存器中,直到下一个写周期发生为止。在读操作之后的第一个写周期,由之前的写操作存储的数据将被写入到 SRAM 阵列。这称为已发布的写入。

如果读操作在上一个周期执行写操作的地址上执行,则 SRAM 读出最新数据。 SRAM 通过绕过存储器阵列并读取寄存器的数据实现这一操作。

### 深度扩展 (Depth Expansion)

深度扩展需要复制每一组的 LD 控制信号。根据情况,组之间的 所有其他控制信号可以共用。

#### 可编程阻抗

SRAM 上的 ZQ 引脚与  $V_{SS}$  之间必须连接一个外部电阻 RQ,以便 SRAM 能够调整其输出驱动器阻抗。RQ 的值必须相当于由 SRAM 控制的目标线路阻抗的 5 倍。当  $V_{DDQ}$ = 1.5 V 时,保证阻抗容错性不超过 ±15% 的 RQ 允许范围为 175  $\Omega$  and 350  $\Omega$ 。输出阻抗在加电后每 1024 个周期调整一次,以补偿电源电压漂移和温度漂移。

#### 随路时钟

DDR II+ 上提供了随路时钟,能够简化高速系统中的数据捕获。两个随路时钟由 DDR II+ 生成。CQ 参照 K, $\overline{CQ}$  参照  $\overline{K}$ 。它们是自由运行时钟,与 DDR II+ 的输入时钟保持同步。随路时钟的时序如第 24 页的 开关特性所示。

#### 有效数据指示器 (QVLD)

DDR II+ 上提供了 QVLD,能够简化高速系统中的数据捕获。 QVLD 由 DDR II+ 器件和数据输出一起生成。该信号与随路时钟 边沿对齐,并遵循任何数据引脚的时序。有效数据返回之前的半 个周期,该信号被激活。

### **PLL**

这些芯片使用了一个 PLL,其工作频率介于 120 MHz 与指定的最大时钟频率之间。在加电期间,当  $\overline{DOFF}$  连接到高电平时,PLL 在时钟稳定 20  $\mu$ s 后被锁定。通过使输入时钟 K 和  $\overline{K}$  减慢或停止至少 30 ns,可以将 PLL 复位。不过,无需复位 PLL,即可将其锁定至所需的频率。在时钟稳定 20  $\mu$ s 后,PLL 会自动锁定。通过将  $\overline{DOFF}$  引脚接地,可禁用 PLL。当 PLL 处于关闭状态时,器件会以 DDR I 模式工作(具有 1 个周期的延迟,并且访问时间更长)。 有关信息请参考应用笔记,PLL Considerations in QDRII/DDRII/QDRII+/DDRII+ QDRII/DDRII/QDRII+/DDRII+

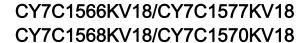

# 应用示例

图 1 显示两个 DDR II+ 在一个应用程序中运行。.

### 表 1. 应用示例

# 真值表

以下是 CY7C1561KV18、CY7C1576KV18 和 CY7C1565KV18 的真值表。<sup>[3, 4, 5, 6, 7, 8]</sup>

| 操作                                                        | К   | LD | R/W | DQ                              | DQ                                   |

|-----------------------------------------------------------|-----|----|-----|---------------------------------|--------------------------------------|

| 写周期:<br>加载地址;等待一个周期;<br>在连续 K 和 K 上升沿输入写数据。               | L-H | L  | L   | 在 K(t + 1) <sup>↑</sup> ?? Δ(A) | 在 K̄(t + 1) <sup>↑</sup> ?? Δ(A + 1) |

| 读周期: (2.5 周期延迟)<br>加载地址;等待 2.5 个周期;<br>在连续 K 和 K 上升沿读取数据。 | L–H | L  | Н   | 在 K̄(t + 2)↑?? Θ(A)             | 在 K(t + 3) <sup>↑</sup> ?? Θ(A + 1)  |

| NOP:无操作                                                   | L–H | Н  | Х   | High-Z                          | High-Z                               |

| 待机:时钟停止                                                   | 停止  | Х  | Х   | 前一个状态                           | 前一个状态                                |

### 写周期说明

CY7C1577KV18 的写周期说明表如下所示。[3, 9]

| BWS <sub>0</sub> /<br>NWS <sub>0</sub> | BWS <sub>1</sub> /<br>NWS <sub>1</sub> | К   | К   | 注释                                                                                                                                                                         |

|----------------------------------------|----------------------------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L                                      | L                                      | L–H | -   | 在写过程的数据部分:<br>CY7C1566KV18 – 两个半字节 (D <sub>[7:0]</sub> ) 均写入到器件中。<br>CY7C1568KV18 – 两个字节 (D <sub>[17:0]</sub> ) 均写入到器件中。                                                   |

| L                                      | L                                      | ı   |     | 在写过程的数据部分 :<br>CY7C1566KV18 – 两个半字节 (D <sub>[7:0]</sub> ) 均写入到器件中。<br>CY7C1568KV18 – 两个字节 (D <sub>[17:0]</sub> ) 均写入到器件中。                                                  |

| L                                      | Н                                      | L–H |     | 在写过程的数据部分:<br>CY7C1566KV18 – 仅低位半字节 (D <sub>[3:0]</sub> ) 写入到器件中,D <sub>[7:4]</sub> 将保持不变。<br>CY7C1568KV18 – 仅低位字节 (D <sub>[8:0]</sub> ) 写入到器件中,D <sub>[17:9]</sub> 将保持不变。 |

| L                                      | Н                                      | 1   |     | 在写过程的数据部分:<br>CY7C1566KV18 – 仅低位半字节 (D <sub>[3:0]</sub> ) 写入到器件中,D <sub>[7:4]</sub> 将保持不变。<br>CY7C1568KV18 – 仅低位字节 (D <sub>[8:0]</sub> ) 写入到器件中,D <sub>[17:9]</sub> 将保持不变。 |

| Н                                      | L                                      | L–H | -   | 在写过程的数据部分:<br>CY7C1566KV18 – 仅高位半字节 (D <sub>[7:4]</sub> ) 写入到器件中,D <sub>[3:0]</sub> 将保持不变。<br>CY7C1568KV18 – 仅高位字节 (D <sub>[17:9]</sub> ) 写入到器件中,D <sub>[8:0]</sub> 将保持不变。 |

| Н                                      | L                                      | 1   |     | 在写过程的数据部分:<br>CY7C1566KV18 – 仅高位半字节 (D <sub>[7:4]</sub> ) 写入到器件中,D <sub>[3:0]</sub> 将保持不变。<br>CY7C1568KV18 – 仅高位字节 (D <sub>[17:9]</sub> ) 写入到器件中,D <sub>[8:0]</sub> 将保持不变。 |

| Н                                      | Н                                      | L–H | 1   | 在写操作的这一部分,不会有任何数据写入到器件中。                                                                                                                                                   |

| Н                                      | Н                                      | -   | L–H | 在写操作的这一部分,不会有任何数据写入到器件中。                                                                                                                                                   |

文档编号:001-63674 修订版\*B

# 写周期说明

CY7C1577KV18 的写周期说明表如下所示。[10, 11]

| BWS <sub>0</sub> | K   | K   | 注释                                           |

|------------------|-----|-----|----------------------------------------------|

| L                | L-H | ı   | 在写过程的数据部分,单个字节 (D <sub>[8:0]</sub> ) 写入到器件中。 |

| L                | 1   | H   | 在写过程的数据部分,单个字节 (D <sub>[8:0]</sub> ) 写入到器件中。 |

| Н                | L-H | 1   | 在写操作的这一部分,不会有任何数据写入到器件中。                     |

| Н                | 1   | L–H | 在写操作的这一部分,不会有任何数据写入到器件中。                     |

# 写周期说明

CY7C1577KV18 的写周期说明表如下所示。[10, 11]

| BWS <sub>0</sub> | BWS <sub>1</sub> | BWS <sub>2</sub> | BWS <sub>3</sub> | K   | K   | 注释                                                                                             |

|------------------|------------------|------------------|------------------|-----|-----|------------------------------------------------------------------------------------------------|

| L                | L                | L                | L                | L–H | _   | 在写过程的数据部分,全部四个字节 (D <sub>[35:0]</sub> ) 都写入到器件中。                                               |

| L                | L                | L                | L                | _   | L–H | 在写过程的数据部分,全部四个字节 (D <sub>[35:0]</sub> ) 都写入到器件中。                                               |

| L                | Η                | Η                | Н                | L–H | -   | 在写过程的数据部分,仅低位字节 (D <sub>[8:0]</sub> ) 写入到器件中。D <sub>[35:9]</sub> 将保持不变。                        |

| L                | Н                | Н                | Н                | _   | L–H | 在写过程的数据部分,仅低位字节 (D <sub>[8:0]</sub> ) 写入到器件中。D <sub>[35:9]</sub> 将保持不变。                        |

| Н                | Ш                | Η                | Н                | L–H | ı   | 在写过程的数据部分,仅字节 ( $D_{[17:9]}$ ) 写入到器件中。 $D_{[8:0]}$ 和 $D_{[35:18]}$ 将保持不变。                      |

| Н                | L                | Н                | Н                | -   | L–H | 在写过程的数据部分,仅字节 ( $D_{[17:9]}$ ) 写入到器件中。 $D_{[8:0]}$ 和 $D_{[35:18]}$ 将保持不变。                      |

| Н                | Н                | L                | Н                | L–H | -   | 在写过程的数据部分,仅字节 (D <sub>[26:18]</sub> ) 写入到器件中。D <sub>[17:0]</sub> 和 D <sub>[35:27]</sub> 将保持不变。 |

| Н                | Н                | L                | Н                | -   | L–H | 在写过程的数据部分,仅字节 ( $D_{[26:18]}$ ) 写入到器件中。 $D_{[17:0]}$ 和 $D_{[35:27]}$ 将保持不变。                    |

| Н                | Н                | Н                | L                | L–H | _   | 在写过程的数据部分,仅字节 (D <sub>[35:27]</sub> ) 写入到器件中。D <sub>[26:0]</sub> 将保持不变。                        |

| Н                | Н                | Н                | L                | _   | L–H | 在写过程的数据部分,仅字节 (D <sub>[35:27]</sub> ) 写入到器件中。D <sub>[26:0]</sub> 将保持不变。                        |

| Н                | Н                | Н                | Н                | L–H | -   | 在写操作的这一部分,不会有任何数据写入到器件中。                                                                       |

| Н                | Н                | Н                | Н                | _   | L–H | 在写操作的这一部分,不会有任何数据写入到器件中。                                                                       |

文档编号:001-63674 修订版\*B 第12页,共页

**注:** 10. X=" 无需关注 ",H=逻辑高电平,L=<u>逻辑低电平、- 代表上升沿。</u> 11. 基于根据写周期说明 表启动的写周期。可以在写周期的不同部分更改 NWS<sub>0</sub>、NWS<sub>1</sub>、BWS<sub>0</sub>、BWS<sub>1</sub>、BWS<sub>2</sub> 和 BWS<sub>3</sub>,只要满足建立和保持要求即可。

# IEEE 1149.1 串行边界扫描 (JTAG)

这些 SRAM 在 FBGA 封装中加入了串行边界扫描测试端口 (TAP)。此部件完全符合 IEEE 标准 #1149.1-2001。TAP 在工作时采用 JEDEC 标准 1.8 V I/O 逻辑电平。

#### 禁用 JTAG 特性

可以在不使用 JTAG 特性的情况下运行 SRAM。要禁用 TAP 控制器,必须将 TCK 连接到低电平 (V<sub>SS</sub>),以防止额外的时钟输入到器件中。TDI 和 TMS 在内部上拉,并可处于未连接状态。它们也可以通过电阻上拉到 V<sub>DD</sub>。TDO 必须保持未连接状态。在加电时,器件会复位,这不会干扰器件的工作。

#### 测试端口 - 测试时钟

测试时钟仅能与 TAP 控制器配合使用。所有输入都在 TCK 的上 升沿被捕获。所有输出都从 TCK 的下降沿被输出。

### 测试模式选择 (TMS)

TMS 输入用于向 TAP 控制器提供指令 ,并在 TCK 的上升沿被采样。如果未使用 TAP ,此引脚可以保持未连接状态。此引脚在内部上拉,从而产生逻辑高电平。

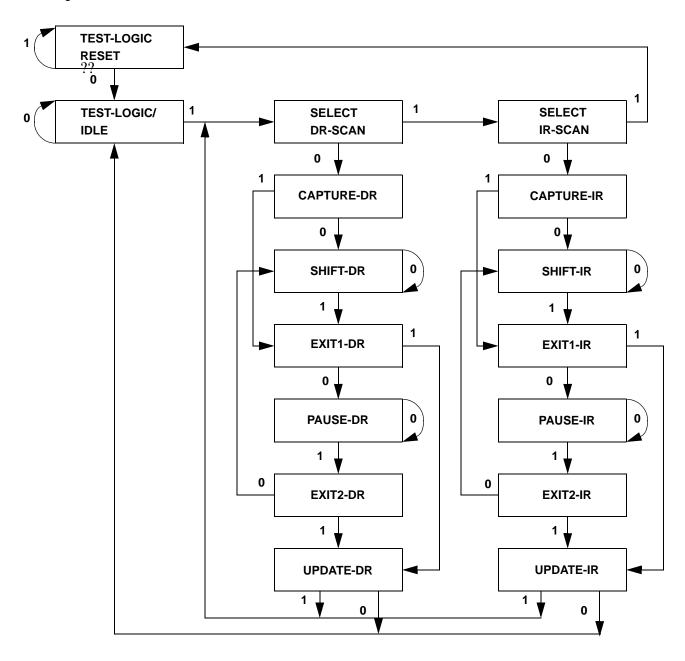

### 测试数据输入 (TDI)

TDI 引脚用于以串行方式将信息输入到寄存器中,并可以连接到任何寄存器的输入。TDI 和 TDO 之间的寄存器由加载到 TAP 指令寄存器中的指令进行选择。有关加载指令寄存器的信息,请参见第 15 页的 TAP 控制器状态图。TDI 在内部上拉。如果未使用TAP,此引脚可以保持未连接状态。TDI 连接到任何寄存器的最高有效位 (MSB)。

#### 测试数据输出 (TDO)

TDO 输出引脚用于以串行方式从寄存器输出时钟数据。 输出有效,取决于 TAP 状态机的当前状态 (请参见第 18 页的 指令代码)。输出会在 TCK 的下降沿改变。TDO 连接到任何寄存器的最低有效位 (LSB)。

#### 执行 TAP 复位

通过将 TMS 强制置为高电平  $(V_{DD})$  达 5 个 TCK 上升沿,即可进行复位。此复位不会影响 SRAM 的工作,并且在 SRAM 工作期间执行。在加电时,TAP 会在内部复位,以确保 TDO 处于 High Z 状态。

#### TAP 寄存器

此类寄存器位于 TDI 和 TDO 引脚之间 ,用于扫描 SRAM 测试电 路的数据输入和输出。 一次只能通过指令寄存器选择一个寄存 器。在 TCK 的上升沿,数据会以串行方式加载到 TDI 引脚。在 TCK 的下降沿,数据会从 TDO 引脚输出。

#### 指令寄存器

三位指令会以串行方式加载到指令寄存器中。 此寄存器在置于TDI 和 TDO 引脚之间时被加载,如第 16 页的 TAP 控制器框图所示。在加电时,指令寄存器会加载 IDCODE 指令。即使控制器处于复位状态,也会加载 IDCODE 指令,如上一节所述。

当 TAP 控制器处于 Capture-IR 状态时,两个最低有效位会加载 二进制 "01" 样本,以便实现模块级别串行测试路径的故障隔离。

#### 旁路寄存器

当数据以串行方式写入寄存器时,跳过某些芯片可能会有助于节省时间。旁路寄存器为单比特寄存器,可置于 TDI 和 TDO 引脚之间, 从而使数据在写入 SRAM 时具有较小的延迟。 执行BYPASS 指令时,旁路寄存器会置为低电平 (V<sub>SS</sub>)。

#### 边界扫描寄存器

边界扫描寄存器连接到 SRAM 上的所有输入和输出引脚。 扫描寄存器中还包含一些无连接 (NC) 引脚,以便供更高密度的器件使用。

当 TAP 控制器处于 Capture-DR 状态时,边界扫描寄存器会加载 RAM 输入和输出环的内容。当控制器转入 Shift-DR 状态后,该 寄存器会被置于 TDI 和 TDO 引脚之间。 EXTEST、SAMPLE/PRELOAD 和 SAMPLE Z 指令用于捕获输入和输出环的内容。

第 19 页的 边界扫描顺序显示了各个位的连接顺序。每个位都对应于 SRAM 封装上的一个管脚。 寄存器的 MSB 连接到 TDI, LSB 连接到 TDO。

#### 标识 (ID) 寄存器

当指令寄存器中加载了 IDCODE 指令时,ID 寄存器会在 Capture-DR 状态期间加载供货商特定的 32 位代码。IDCODE 已硬连线到 SRAM 中,当 TAP 控制器处于 Shift-DR 状态时,可以将其读出。ID 寄存器具有供货商代码和第 18 页的 标识寄存器 定义中所述的其他信息。

#### TAP 指令集

三位指令寄存器可实现八个不同的指令。第 18 页的 指令代码中列出了所有组合。其中三个指令列为了 RESERVED,请勿使用这些指令。本节将详细说明其他五个指令。

当指令寄存器置于 TDI 和 TDO 之间时,这些指令会在 Shift-IR 状态期间加载到 TAP 控制器中。在此状态期间,指令会通过 TDI 和 TDO 引脚被写入指令寄存器。要在写入指令后执行指令,必须使 TAP 控制器转入 Update-IR 状态。

#### **IDCODE**

IDCODE 指令用于将供货商特定的 32 位代码加载到指令寄存器中。它还会将指令寄存器置于 TDI 和 TDO 引脚之间,并会在 TAP 控制器进入 Shift-DR 状态后,将 IDCODE 移出器件。在加电时,或每当 TAP 控制器处于 Test-Logic-Reset 状态时,IDCODE 指令都会加载到指令寄存器中。

#### SAMPLE Z

当 TAP 控制器处于 Shift-DR 状态时,SAMPLE Z 指令会将边界扫描寄存器置于 TDI 和 TDO 引脚之间。SAMPLE Z 指令会将输出总线置于 High Z 状态,直到在 Update-IR 状态期间提供了下一条指令为止。

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD 是 1149.1 强制指令。 当 SAMPLE/PRELOAD 指令加载到指令寄存器中并且 TAP 控制器处于 Capture-DR 状态时,边界扫描寄存器中会捕获输入和输出引脚上数据的快照。

用户必须注意 TAP 控制器时钟的最高工作频率仅为 20 MHz,而 SRAM 时钟的工作频率要比它高一个数量级。 由于在时钟频率 方面存在较大差距,因此在 Capture-DR 状态期间,输入或输出可能会出现跃变。TAP 则可能会在跃变(半稳态)期间尝试捕获信号。 虽然这并不会损坏器件,但无法保证捕获到的值是正确的,并且结果可能无法重复。

为了确保边界扫描寄存器捕获到正确的信号值,SRAM 信号必须在足够长的时间内保持稳定,以达到 TAP 控制器的捕获建立加保持时间(t<sub>CS</sub> 和 t<sub>CH</sub>)要求。 如果在设计上无法在SAMPLE/PRELOAD 指令期间停止(或减慢)时钟,则可能无法正确捕获 SRAM 时钟输入。即使存在这一问题,仍可以捕获所有其他信号,只要忽略边界扫描寄存器中捕获的 CK 和 CK 的值即可。

捕获数据后,通过将 TAP 置于 Shift-DR 状态,可以读出数据。 这会将边界扫描寄存器置于 TDI 和 TDO 引脚之间。 在选择另一个边界扫描测试操作之前,PRELOAD 用于在边界扫描寄存器单元的已锁存并行输出处放置一个初始数据样本。

必要时, SAMPLE 和 PRELOAD 阶段的数据读写可以并发执行,即可以在读出所捕获数据的同时,读入预加载的数据。

#### **BYPASS**

当 BYPASS 指令加载到指令寄存器中并且 TAP 处于 Shift-DR 状态时,旁路寄存器会被置于 TDI 和 TDO 引脚之间。BYPASS 指令的优势是当模块上有多个器件连接在一起时,可以缩短边界扫描路径。

#### **EXTEST**

EXTEST 指令用于通过系统输出引脚输出预加载的数据。 在 Shift-DR 控制器状态下,此指令还会将用于串行访问的边界扫描 寄存器置于 TDI 和 TDO 之间。

#### EXTEST OUTPUT BUS TRISTATE

IEEE 标准 1149.1 强制规定 ,TAP 控制器需要能够将输出总线置于三态模式。

边界扫描寄存器在 108 位有一个特殊位。当此扫描单元(称为"外测试输出总线三态") 在 TAP 控制器处于 Update-DR 状态期间被锁存到预加载寄存器中时,如果输入 EXTEST 作为当前指令,则该单元会直接控制输出(Q 总线)引脚的状态。在置于高电平时,它将允许输出缓冲器控制输出总线。 在置于低电平时,此位会将输出总线置于 High Z 状态。

通过输入 SAMPLE/PRELOAD 或 EXTEST 指令,然后在 Shift-DR 状态期间将所需的位读入到该单元中,即可设置该位。在 Update-DR 期间,加载到该移位寄存器单元中的值会被锁存到预加载寄存器中。输入 EXTEST 指令后,此位会直接控制输出 Q 总线引脚。请注意,此位会预置为高电平,以便在器件加电时,以及当 TAP 控制器处于 Test-Logic-Reset 状态时,启动输出。

#### Reserved

这些指令尚未实现,但可以留作日后使用。请勿使用这些指令。

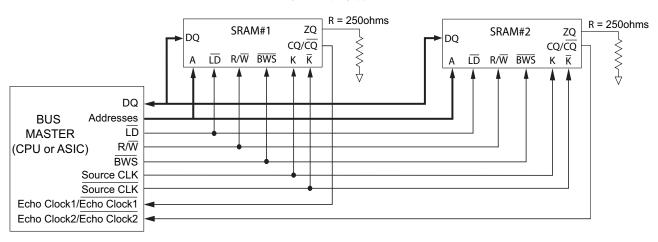

# TAP 控制器状态图

The state diagram for the TAP controller follows. [12]

**注:注** 12. 每个状态旁边的 0/1 代表 TCK 上升沿上对应的 TMS 的值。

文档编号:001-63674 修订版\*B 第15页,共页

# TAP 控制器框图

# TAP 电气特性

Over the Operating Range [13, 14, 15]

| 参数               | 说明        | 测试条件                       | 最小值                  | 最大值                   | 单位 |

|------------------|-----------|----------------------------|----------------------|-----------------------|----|

| V <sub>OH1</sub> | 输出高电平电压   | I <sub>OH</sub> = -2.0 mA  | 1.4                  | _                     | V  |

| V <sub>OH2</sub> | 输出高电平电压   | I <sub>OH</sub> = -100 μA  | 1.6                  | _                     | V  |

| V <sub>OL1</sub> | 输出低电平电压   | I <sub>OL</sub> = 2.0 mA   | _                    | 0.4                   | V  |

| V <sub>OL2</sub> | 输出低电平电压   | I <sub>OL</sub> = 100 μA   | -                    | 0.2                   | V  |

| V <sub>IH</sub>  | 输入高电平电压   |                            | 0.65 V <sub>DD</sub> | V <sub>DD</sub> + 0.3 | V  |

| $V_{IL}$         | 输入低电平电压   |                            | -0.3                 | 0.35 V <sub>DD</sub>  | V  |

| I <sub>X</sub>   | 输入和输出负载电流 | $GND \leq V_I \leq V_{DD}$ | <b>-</b> 5           | 5                     | μΑ |

**注:**13. 这些特性为 TAP 输入 (TMS、TCK、TDI 和 TDO)的特性。并行负载电平在电气特性表中指定。

14. 过冲:V<sub>IJ</sub> (交流)< V<sub>DDO</sub> + 0.3 V (脉冲宽度小于 t<sub>CYC</sub>/2),下冲:V<sub>IL</sub> (交流)>-0.3 V (脉冲宽度小于 t<sub>CYC</sub>/2)。

15. 所有电压都是相对于接地的电压。

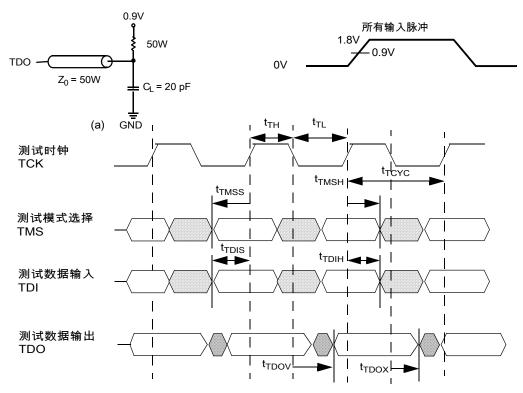

# TAP 交流开关特性

Over the Operating Range [16, 17]

| 参数                | 说明                     | 最小值 | 最大值 | 单位  |

|-------------------|------------------------|-----|-----|-----|

| t <sub>TCYC</sub> | TCK 时钟周期时间             | 50  | -   | ns  |

| t <sub>TF</sub>   | TCK 时钟频率               | -   | 20  | MHz |

| t <sub>TH</sub>   | TCK 时钟高电平              | 20  | -   | ns  |

| t <sub>TL</sub>   | TCK 时钟低电平              | 20  | -   | ns  |

| 建立时间              |                        |     |     |     |

| t <sub>TMSS</sub> | 从 TMS 建立到 TCK 时钟上升沿的时间 | 5   | _   | ns  |

| t <sub>TDIS</sub> | 从 TDI 建立到 TCK 时钟上升沿的时间 | 5   | -   | ns  |

| t <sub>CS</sub>   | 从捕获建立到 TCK 上升沿的时间      | 5   | -   | ns  |

| 保持时间              |                        |     |     |     |

| t <sub>TMSH</sub> | TCK 时钟上升沿之后的 TMS 保持时间  | 5   | _   | ns  |

| t <sub>TDIH</sub> | 时钟上升沿之后的 TDI 保持时间      | 5   | -   | ns  |

| t <sub>CH</sub>   | 时钟上升沿之后的捕获保持时间         | 5   | -   | ns  |

| 输出时间              | •                      | •   | •   |     |

| t <sub>TDOV</sub> | 从 TCK 时钟为低到 TDO 有效的时间  | _   | 10  | ns  |

| t <sub>TDOX</sub> | 从 TCK 时钟为低到 TDO 无效的时间  | 0   | -   | ns  |

# TAP 时序和测试条件

图 2 shows the TAP timing and test conditions. [17]

### 表 2. TAP 时序和测试条件

$m{\dot{z}}$ : 16.  $t_{CS}$  and  $t_{CH}$  指从边界扫描寄存器锁存数据的建立和保持时间要求。 17. 测试条件是使用 TAP 交流测试条件中的负载确定的。 $t_R/t_F$  = 1 ns。

文档编号:001-63674 修订版\*B 第17页,共页

# 标识寄存器定义

| 指令字段                      |                   | ù                 | i                 |                   | 说明                      |

|---------------------------|-------------------|-------------------|-------------------|-------------------|-------------------------|

| 相中于权                      | CY7C1566KV18      | CY7C1577KV18      | CY7C1568KV18      | CY7C1570KV18      | רני שי                  |

| 版本号 (31:29)               | 000               | 000               | 000               | 000               | 版本号。                    |

| 赛普拉斯公司器件<br>ID (28:12)    | 11010111000000100 | 11010111000001100 | 11010111000010100 | 11010111000100100 | 定义 SRAM 的类<br>型。        |

| 赛普拉斯公司<br>JEDEC ID (11:1) | 00000110100       | 00000110100       | 00000110100       | 00000110100       | 允许对 SRAM 供货<br>商使用唯一标识。 |

| ID 寄存器存在情况<br>(0)         | 1                 | 1                 | 1                 | 1                 | 指示是否存在 ID 寄存器。          |

# 扫描寄存器大小

| 寄存器名称 | 位大小 |

|-------|-----|

| 指令    | 3   |

| 绕过    | 1   |

| ID    | 32  |

| 边界扫描  | 109 |

# 指令代码

| THE IS I CAS   |     |                                                                  |

|----------------|-----|------------------------------------------------------------------|

| 指令             | 代码  | 说明                                                               |

| EXTEST         | 000 | 捕获输入和输出环的内容。                                                     |

| IDCODE         | 001 | 在 ID 寄存器中加载供货商 ID 代码 ,并将该寄存器置于 TDI 和 TDO 之间。此操作不会影响 SRAM 的工作。    |

| SAMPLE Z       | 010 | 捕获输入和输出内容。将边界扫描寄存器置于 TDI 和 TDO 之间。强制使所有 SRAM 输出驱动器均进入 High Z 状态。 |

| RESERVED       | 011 | 请勿使用:此指令留作日后使用。                                                  |

| SAMPLE/PRELOAD | 100 | 捕获输入和输出环的内容。将边界扫描寄存器置于 TDI 和 TDO 之间。不会影响 SRAM的工作。                |

| RESERVED       | 101 | 请勿使用:此指令留作日后使用。                                                  |

| RESERVED       | 110 | 请勿使用:此指令留作日后使用。                                                  |

| BYPASS         | 111 | 将旁路寄存器置于 TDI 和 TDO 之间。此操作不会影响 SRAM 的工作。                          |

文档编号:001-63674 修订版 \*B 第 18 页,共 页

# 边界扫描顺序

| 位编号 | 管脚 ID | 位编号 | î |  |  |

|-----|-------|-----|---|--|--|

| 0   | 6R    | 28  |   |  |  |

| 1   | 6P    | 29  |   |  |  |

| 2   | 6N    | 30  |   |  |  |

| 3   | 7P    | 31  |   |  |  |

| 4   | 7N    | 32  |   |  |  |

| 5   | 7R    | 33  |   |  |  |

| 6   | 8R    | 34  |   |  |  |

| 7   | 8P    | 35  |   |  |  |

| 8   | 9R    | 36  |   |  |  |

| 9   | 11P   | 37  |   |  |  |

| 10  | 10P   | 38  |   |  |  |

| 11  | 10N   | 39  |   |  |  |

| 12  | 9P    | 40  |   |  |  |

| 13  | 10M   | 41  |   |  |  |

| 14  | 11N   | 42  |   |  |  |

| 15  | 9M    | 43  |   |  |  |

| 16  | 9N    | 44  |   |  |  |

| 17  | 11L   | 45  |   |  |  |

| 18  | 11M   | 46  |   |  |  |

| 19  | 9L    | 47  |   |  |  |

| 20  | 10L   | 48  |   |  |  |

| 21  | 11K   | 49  |   |  |  |

| 22  | 10K   | 50  |   |  |  |

| 23  | 9J    | 51  |   |  |  |

| 24  | 9K    | 52  |   |  |  |

| 25  | 10J   | 53  |   |  |  |

| 26  | 11J   | 54  |   |  |  |

| 27  | 11H   | 55  |   |  |  |

|     | •     |     |   |  |  |

| 位编号 | 管脚 ID |

|-----|-------|

| 28  | 10G   |

| 29  | 9G    |

| 30  | 11F   |

| 31  | 11G   |

| 32  | 9F    |

| 33  | 10F   |

| 34  | 11E   |

| 35  | 10E   |

| 36  | 10D   |

| 37  | 9E    |

| 38  | 10C   |

| 39  | 11D   |

| 40  | 9C    |

| 41  | 9D    |

| 42  | 11B   |

| 43  | 11C   |

| 44  | 9B    |

| 45  | 10B   |

| 46  | 11A   |

| 47  | 10A   |

| 48  | 9A    |

| 49  | 8B    |

| 50  | 7C    |

| 51  | 6C    |

| 52  | 8A    |

| 53  | 7A    |

| 54  | 7B    |

| 55  | 6B    |

| 位编号 | 管脚 ID |

|-----|-------|

| 56  | 6A    |

| 57  | 5B    |

| 58  | 5A    |

| 59  | 4A    |

| 60  | 5C    |

| 61  | 4B    |

| 62  | 3A    |

| 63  | 2A    |

| 64  | 1A    |

| 65  | 2B    |

| 66  | 3B    |

| 67  | 1C    |

| 68  | 1B    |

| 69  | 3D    |

| 70  | 3C    |

| 71  | 1D    |

| 72  | 2C    |

| 73  | 3E    |

| 74  | 2D    |

| 75  | 2E    |

| 76  | 1E    |

| 77  | 2F    |

| 78  | 3F    |

| 79  | 1G    |

| 80  | 1F    |

| 81  | 3G    |

| 82  | 2G    |

| 83  | 1H    |

| 位编号 | 管脚 ID |

|-----|-------|

| 84  | 1J    |

| 85  | 2J    |

| 86  | 3K    |

| 87  | 3J    |

| 88  | 2K    |

| 89  | 1K    |

| 90  | 2L    |

| 91  | 3L    |

| 92  | 1M    |

| 93  | 1L    |

| 94  | 3N    |

| 95  | 3M    |

| 96  | 1N    |

| 97  | 2M    |

| 98  | 3P    |

| 99  | 2N    |

| 100 | 2P    |

| 101 | 1P    |

| 102 | 3R    |

| 103 | 4R    |

| 104 | 4P    |

| 105 | 5P    |

| 106 | 5N    |

| 107 | 5R    |

| 108 | 内部    |

# DDR II+ SRAM 中的加电顺序

DDR II+ SRAM 必须按预定义的方式加电并初始化,以免执行未 定义的操作。

### 加电顺序

- 通电并将 DOFF 置为高电平或低电平(所有其他输入都可以是 高电平或低电平)。

- □ 在施加 V<sub>DDQ</sub> 之前施加 V<sub>DD</sub>。

- □ 在施加 V<sub>REF</sub> 之前或与 V<sub>REF</sub> 同时施加 V<sub>DDQ</sub>。 □ 将 DOFF 置为高电平。

- ■提供连续 20 μs 的稳定 DOFF (高电平)、电源和时钟 (K、 K),以便锁定 PLL。

#### PLL 限制

- PLL 使用 K 时钟作为其同步输入。输入必须具有较低的相位抖 动(以t<sub>KC Var</sub>表示)。

- PLL 能够正常工作的最低频率为 120 MHz。

- 如果输入时钟不稳定并且启用了 PLL,则 PLL 可能会锁定到不正确的频率,从而导致 SRAM 工作不稳定。 为了避免这种情况,请提供 20 μs 的稳定时钟,以便重新锁定到所需的时钟频 *,* 率。

文档编号:001-63674 修订版\*B 第20页,共页

### 最大额定值

超过最大额定值可能会缩短器件的使用寿命。用户指导未经过测

| 248                                                         |

|-------------------------------------------------------------|

| 存放温度65 °C 到 +150 °C                                         |

| 通电状态下的环境温度55 °C 到 +125 °C                                   |

| V <sub>DD</sub> 上相对于 GND 的供电电压0.5V 到 +2.9V                  |

| V <sub>DDQ</sub> 上相对于 GND 的供电电压 GND0.5 V 到 +V <sub>DD</sub> |

| High Z 状态下为输出施加的直流电压 –0.5 V 到 $V_{DDQ}$ + 0.3 V             |

| 直流输入电压 <sup>[18]</sup> 0.5 V 到 V <sub>DD</sub> + 0.3 V      |

| 输出电流 (低电平)20 mA                                             |

| 静电放电电压 (MIL-STD-883、M 3015)> 2,001V                         |

| 栓锁电流 > 200 mA                                               |

# 抗中子软失效

| 参数   | 说明          | 测试<br>条件 | 典型值 | 最大<br>值 * | 单位          |

|------|-------------|----------|-----|-----------|-------------|

| LSBU | 逻辑单比特<br>错误 | 25 °C    | 197 | 216       | FIT/<br>Mb  |

| LMBU | 逻辑多比特<br>错误 | 25 °C    | 0   | 0.01      | FIT/<br>Mb  |

| SEL  | 软栓锁         | 85 °C    | 0   | 0.1       | FIT/<br>Dev |

<sup>\*</sup> 测试期间未出现 LMBU 或 SEL 事件; 此列为统计得出的  $\chi^2$ ,按 95% 置信区间计算。 如需详细信息,请参考应用笔记 AN 54908 "Accelerated Neutron SER Testing and Calculation of Terrestrial Failure Rates"。

# 工作范围

| 范围 | 环境<br>温度 (T <sub>A</sub> ) | V <sub>DD</sub> [19] | <b>V</b> DDQ [19] |

|----|----------------------------|----------------------|-------------------|

| 商用 | 0 °C 到 +70 °C              | 1.8 ± 0.1 V          | 1.4 V 至           |

| 工业 | –40 °C 至 +85 °C            |                      | VDD               |

# 电气特性

#### **DC Electrical Characteristics**

Over the Operating Range [20]

| 参数              | 说明          | 测试条件                                           | 最小值                        | 典型值  | 最大值                     | 单位       |

|-----------------|-------------|------------------------------------------------|----------------------------|------|-------------------------|----------|

| $V_{DD}$        | 电源电压        |                                                | 1.7                        | 1.8  | 1.9                     | V        |

| $V_{DDQ}$       | I/O 供电电压    |                                                | 1.4                        | 1.5  | $V_{DD}$                | V        |

| V <sub>OH</sub> | 输出高电平电压     | 注 21                                           | V <sub>DDQ</sub> /2 – 0.12 | -    | $V_{DDQ}/2 + 0.12$      | V        |

| $V_{OL}$        | 输出低电平电压     | 注 22                                           | V <sub>DDQ</sub> /2 – 0.12 | -    | $V_{DDQ}/2 + 0.12$      | <b>V</b> |

| $V_{OH(LOW)}$   | 输出高电平电压     | I <sub>OH</sub> = −0.1 mA,额定阻抗                 | V <sub>DDQ</sub> – 0.2     | -    | $V_{\mathrm{DDQ}}$      | <b>V</b> |

| $V_{OL(LOW)}$   | 输出低电平电压     | I <sub>OL</sub> = 0.1 mA,额定阻抗                  | $V_{SS}$                   | -    | 0.2                     | <b>V</b> |

| $V_{IH}$        | 输入高电平电压     |                                                | V <sub>REF</sub> + 0.1     | -    | V <sub>DDQ</sub> + 0.15 | <b>V</b> |

| $V_{IL}$        | 输入低电平电压     |                                                | -0.15                      | -    | V <sub>REF</sub> – 0.1  | V        |

| I <sub>X</sub>  | 输入漏电流       | $GND \leq V_I \leq V_{DDQ}$                    | -2                         | -    | 2                       | μА       |

| I <sub>OZ</sub> | 输出漏电流       | GND ≤ V <sub>I</sub> ≤ V <sub>DDQ</sub> ,输出被禁用 | -2                         | -    | 2                       | μА       |

| $V_{REF}$       | 输入参考电压 [23] | 典型值 = 0.75V                                    | 0.68                       | 0.75 | 0.95                    | V        |

文档编号:001-63674 修订版\*B

# 电气特性 (continued) **DC Electrical Characteristics**

Over the Operating Range [20]

| 参数                              | 说明                    | 测试条何                                                                                                | <del>‡</del> |       | 最小值 | 典型值 | 最大值 | 单位 |

|---------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|--------------|-------|-----|-----|-----|----|

| I <sub>DD</sub> <sup>[24]</sup> | V <sub>DD</sub> 的工作电流 | V <sub>DD</sub> = 最大值 ,I <sub>OUT</sub> = 0                                                         | 550 MHz      | (×8)  | -   | -   | 740 | mA |

|                                 |                       | $   mA ,     f = f_{MAX} = 1/t_{CYC} $                                                              |              | (×9)  | _   | -   | 740 |    |

|                                 |                       | I - IMAX - I/ICYC                                                                                   |              | (×18) | _   | -   | 760 |    |

|                                 |                       |                                                                                                     |              | (×36) | -   | -   | 970 |    |

|                                 |                       |                                                                                                     | 500 MHz      | (×8)  | -   | -   | 690 | mA |

|                                 |                       |                                                                                                     |              | (×9)  | -   | -   | 690 |    |

|                                 |                       |                                                                                                     |              | (×18) | _   | _   | 700 |    |

|                                 |                       |                                                                                                     |              | (×36) | _   | -   | 890 |    |

|                                 |                       |                                                                                                     | 450 MHz      | (×8)  | _   | _   | 630 | mA |

|                                 |                       |                                                                                                     |              | (×9)  | _   | -   | 630 | 7  |

|                                 |                       |                                                                                                     |              | (×18) | _   | -   | 650 | 7  |

|                                 |                       |                                                                                                     |              | (×36) | _   | _   | 820 | 7  |

|                                 |                       |                                                                                                     | 400 MHz      | (×8)  | _   | _   | 580 | mA |

|                                 |                       |                                                                                                     |              | (×9)  | _   | _   | 580 | 1  |

|                                 |                       |                                                                                                     |              | (×18) | _   | _   | 590 | 1  |

|                                 |                       |                                                                                                     |              | (×36) | _   | _   | 750 | 1  |

| I <sub>SB1</sub>                | 自动断电                  | 最大 V <sub>DD</sub> ,<br>两个端口均未选中,V <sub>IN</sub>                                                    | 550 MHz      | (×8)  | _   | _   | 380 | mA |

|                                 | 电流                    | 两个端口均未选中,V <sub>IN</sub>                                                                            |              | (×9)  | _   | _   | 380 | 7  |

|                                 |                       | ≥ V <sub>IH</sub> 或 V <sub>IN</sub> ≤ V <sub>IL</sub><br>If = f <sub>MAX</sub> = 1/t <sub>GYG</sub> |              | (×18) | _   | _   | 380 |    |

|                                 |                       |                                                                                                     |              | (×36) | _   | _   | 380 |    |

|                                 |                       |                                                                                                     | 500 MHz      | (×8)  | _   | _   | 360 | mA |

|                                 |                       |                                                                                                     |              | (×9)  | _   | _   | 360 |    |

|                                 |                       |                                                                                                     |              | (×18) | _   | _   | 360 | 7  |

|                                 |                       |                                                                                                     |              | (×36) | _   | _   | 360 | 7  |

|                                 |                       |                                                                                                     | 450 MHz      | (×8)  | _   | _   | 340 | mA |

|                                 |                       |                                                                                                     |              | (×9)  | _   | _   | 340 | 7  |

|                                 |                       |                                                                                                     |              | (×18) | _   | _   | 340 | 1  |

|                                 |                       |                                                                                                     |              | (×36) | _   | _   | 340 | 1  |

|                                 |                       |                                                                                                     | 400 MHz      | (×8)  | _   | _   | 320 | mA |

|                                 |                       |                                                                                                     |              | (×9)  | _   | _   | 320 | 1  |

|                                 |                       |                                                                                                     |              | (×18) | _   | _   | 320 | -  |

|                                 |                       |                                                                                                     |              | (×36) | _   | _   | 320 | -  |

# 交流电气特性

超出工作范围 [25]

| 参数       | 说明      | 测试条件 | 最小值                    | 典型值 | 最大值                     | 单位 |

|----------|---------|------|------------------------|-----|-------------------------|----|

| $V_{IH}$ | 输入高电平电压 |      | V <sub>REF</sub> + 0.2 | ı   | V <sub>DDQ</sub> + 0.24 | V  |

| $V_{IL}$ | 输入低电平电压 |      | -0.24                  | I   | V <sub>REF</sub> – 0.2  | V  |

**注:**24. 工作电流根据 50% 读周期和 50% 写周期计算得出。

25. 过冲:V<sub>IH</sub> (交流)<V<sub>DDQ</sub> + 0.3 V (脉冲宽度小于 t<sub>CYC</sub>/2),下冲:V<sub>IL</sub> (交流)>-0.3 V (脉冲宽度小于 t<sub>CYC</sub>/2)。

# 电容

在进行可能会影响这些参数的任何设计或工艺更改之前和之后测试。

| 参数              | 说明   | 测试条件                                                                                                  | 最大值 | 单位 |

|-----------------|------|-------------------------------------------------------------------------------------------------------|-----|----|

| C <sub>IN</sub> | 输入电容 | $T_A = 25 ^{\circ}\text{C}$ , $f = 1 \text{MHz}$ , $V_{DD} = 1.8 \text{V}$ , $V_{DDQ} = 1.5 \text{V}$ | 4   | pF |

| Co              | 输出电容 |                                                                                                       | 4   | pF |

# 热阻

在进行可能会影响这些参数的任何设计或工艺更改之前和之后测试。

| 参数                | 说明            | 测试条件                                    | 165 FBGA 封装 | 单位   |

|-------------------|---------------|-----------------------------------------|-------------|------|

| $\Theta_{JA}$     | 热电阻<br>(结温)   | 根据 EIA/JESD51 的要求,测试条件遵循测试热阻的标准测试方法和过程。 | 13.7        | °C/W |

| $\Theta_{\sf JC}$ | 热电阻<br>( 壳温 ) |                                         | 3.73        | °C/W |

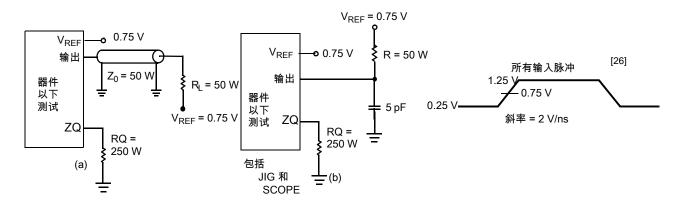

#### 表 4. 交流测试负载和波形

文档编号: 001-63674 修订版 \*B 第 23 页,共 页

**注:**26. 除非另行指定,否则测试条件基于 2V/ns 的信号跃变时间、0.75V 的时序参考电平、V <sub>REF</sub>= 0.75 V、RQ = 250 Ω、V<sub>DDQ</sub> = 1.5 V、0.25V 至 1.25V 的输入脉冲电平以及具有指定 I<sub>OL</sub>/I<sub>OH</sub> 和负载电容的输出负载,如 图 4 的 (a) 所示。

### 开关特性

超出工作范围 [27, 28]

| 主並長に                    |                                |                                                                                                                      | 550   | MHz     | 500 MHz |         | 450 MHz |         | 400 MHz |         | *  |

|-------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|---------|---------|---------|---------|---------|---------|---------|----|

| 赛普拉斯<br>参数              | 联盟参数                           | 说明                                                                                                                   | 最小值   | 最大<br>值 | 最小值     | 最大<br>值 | 最小值     | 最大<br>值 | 最小值     | 最大<br>值 | 单位 |

| t <sub>POWER</sub>      |                                | 从 V <sub>DD</sub> (典型值)到第一次访问的时间 <sup>[29]</sup>                                                                     | 1     | _       | 1       | _       | 1       | _       | 1       | -       | ms |

| t <sub>CYC</sub>        | t <sub>KHKH</sub>              | K 时钟周期时间                                                                                                             | 1.81  | 8.4     | 2.0     | 8.4     | 2.2     | 8.4     | 2.5     | 8.4     | ns |

| t <sub>KH</sub>         | t <sub>KHKL</sub>              | 输入时钟 (K/K) 高电平                                                                                                       | 0.4   | _       | 0.4     | _       | 0.4     | _       | 0.4     | _       | ns |

| $t_{KL}$                | t <sub>KLKH</sub>              | 输入时钟 (K/K) 低电平                                                                                                       | 0.4   | -       | 0.4     | _       | 0.4     | _       | 0.4     | _       | ns |

| tĸн⊼н                   | <sup>t</sup> ĸн <del>к</del> н | 从 K 时钟上升沿到 $\overline{K}$ 时钟上升沿的时间 (从上升沿到上升沿)                                                                        | 0.77  | _       | 0.85    | _       | 0.94    | _       | 1.06    | _       | ns |

| 建立时间                    |                                |                                                                                                                      |       |         |         |         |         |         |         |         |    |

| t <sub>SA</sub>         | t <sub>AVKH</sub>              | 从地址建立到 K 时钟上升沿的时间                                                                                                    | 0.23  | -       | 0.25    | _       | 0.275   | _       | 0.4     | _       | ns |

| t <sub>SC</sub>         | t <sub>IVKH</sub>              | 从控制建立到 K 时钟上升沿的时间 ( $\overline{LD}$ 、 $R/\overline{W}$ )                                                             | 0.23  | -       | 0.25    | -       | 0.275   | -       | 0.4     | -       | ns |

| t <sub>SCDDR</sub>      | t <sub>IVKH</sub>              | 双倍数据速率控制建立到时钟 (K/K) 上升沿 (BWS <sub>0</sub> 、BWS <sub>1</sub> 、 <sub>BWS</sub> 2、 <sub>BWS</sub> 3)的时间                 | 0.18  | _       | 0.20    | -       | 0.22    | -       | 0.28    | -       | ns |

| t <sub>SD</sub><br>保持时间 | t <sub>DVKH</sub>              | 从 D <sub>[X:0]</sub> 建立到时钟 (K/K̄) 上升沿的时间                                                                             | 0.18  | -       | 0.20    | -       | 0.22    | -       | 0.28    | -       | ns |

| t <sub>HA</sub>         | t <sub>KHAX</sub>              | K 时钟上升沿之后的地址保持时间                                                                                                     | 0.23  | _       | 0.25    | _       | 0.275   | _       | 0.4     | _       | ns |

| t <sub>HC</sub>         | t <sub>KHIX</sub>              | K 时钟上升沿之后的控制保持时间(LD、R/W)                                                                                             | 0.23  | _       | 0.25    |         | 0.275   |         | 0.4     | _       | ns |

| t <sub>HCDDR</sub>      | t <sub>KHIX</sub>              | 时钟 $(K/\overline{K})$ 上升沿 $(\overline{BWS_0}, \overline{BWS_1}, \overline{BWS_2}, \overline{BWS_3})$ 之后的双倍数据速率控制保持时间 | 0.18  | -       | 0.20    | -       | 0.22    |         | 0.28    | _       | ns |

| t <sub>HD</sub>         | t <sub>KHDX</sub>              | 时钟 (K/K) 上升沿之后的 D <sub>[X:0]</sub> 保持时间                                                                              | 0.18  | _       | 0.20    | _       | 0.22    | _       | 0.28    | _       | ns |

| 输出时间                    |                                | 1 2 2                                                                                                                | •     |         | •       |         | •       |         | •       |         |    |

| t <sub>CO</sub>         | t <sub>CHQV</sub>              | K/K 时钟上升沿到数据有效的时间                                                                                                    | _     | 0.45    | _       | 0.45    | _       | 0.45    | _       | 0.45    | ns |

| t <sub>DOH</sub>        | t <sub>CHQX</sub>              | 输出 K/K 时钟上升沿之后的数据输出保持时间(从有效到有效)                                                                                      | -0.45 | -       | -0.45   | -       | -0.45   | -       | -0.45   | -       | ns |

| t <sub>CCQO</sub>       | t <sub>CHCQV</sub>             | 从 K/K 时钟上升沿到随路时钟有效的时间                                                                                                | _     | 0.45    | _       | 0.45    | _       | 0.45    | _       | 0.45    | ns |

| t <sub>CQOH</sub>       | t <sub>CHCQX</sub>             | K/K 时钟上升沿之后的随路时钟保持时间                                                                                                 | -0.45 | _       | -0.45   | _       | -0.45   | _       | -0.45   | _       | ns |

| $t_{CQD}$               | t <sub>CQHQV</sub>             | 从随路时钟为高到数据有效的时间                                                                                                      | _     | 0.15    | _       | 0.15    | _       | 0.15    | _       | 0.20    | ns |

| t <sub>CQDOH</sub>      | t <sub>CQHQX</sub>             | 从随路时钟为高到数据无效的时间                                                                                                      | -0.15 | _       | -0.15   | _       | -0.15   | _       | -0.20   | _       | ns |

| $t_{CQH}$               | tcahcal                        | 输出时钟 (CQ/ <del>CQ</del> ) 高电平 <sup>[30]</sup>                                                                        | 0.655 | _       | 0.75    | _       | 0.85    | _       | 1.00    | _       | ns |

| tcqн <del>cq</del> н    | t <sub>CQH</sub> CQH           | 从 CQ 时钟上升沿到 <del>CQ</del> 时钟上升沿的时间<br>(上升沿到上升沿) <sup>[30]</sup>                                                      | 0.655 | _       | 0.75    | _       | 0.85    | _       | 1.00    | _       | ns |

| t <sub>CHZ</sub>        | t <sub>CHQZ</sub>              | 时钟 (K/K) 上升沿到 high Z 的时间 (从有效到 high Z ) <sup>[31, 32]</sup>                                                          | _     | 0.45    | _       | 0.45    | _       | 0.45    | _       | 0.45    | ns |

| t <sub>CLZ</sub>        | t <sub>CHQX1</sub>             | 从时钟 (K/K) 上升沿到 Low Z 的时间 [31, 32]                                                                                    | -0.45 | _       | -0.45   | _       | -0.45   | _       | -0.45   | _       | ns |

| t <sub>QVLD</sub>       | t <sub>CQHQVLD</sub>           | 从随路时钟为高到 QVLD 有效的时间 <sup>[33]</sup>                                                                                  | -0.15 | 0.15    | -0.15   | 0.15    | -0.15   | 0.15    | -0.20   | 0.20    | ns |

| PLL 时序                  |                                |                                                                                                                      |       |         |         |         |         |         |         |         |    |

| t <sub>KC Var</sub>     | t <sub>KC Var</sub>            | 时钟相位抖动                                                                                                               | _     | 0.15    | _       | 0.15    | _       | 0.15    | _       | 0.20    | ns |

| t <sub>KC 时钟</sub>      | t <sub>KC 时钟</sub>             | PLL 锁定时间 (K)                                                                                                         | 20    | -       | 20      | _       | 20      | -       | 20      | _       | μS |

| t <sub>KC 复位</sub>      | t <sub>KC 复位</sub>             | 从 K 为静态到 PLL 复位的时间 <sup>[34]</sup>                                                                                   | 30    | _       | 30      |         | 30      | _       | 30      | _       | ns |

注:

27. 注除非另行指定,否则测试条件基于 2V/ns 的信号跃变时间、0.75V 的时序参考电平、V <sub>REF</sub>= 0.75 V、RQ = 250 Ω、V<sub>DDQ</sub> = 1.5 V、0.25V 至 1.25V 的输入脉冲电平 以及具有指定 I<sub>IO</sub> /I<sub>IO</sub> 和负载电容的输出负载,如 图 4 的 (a) 所示。

28. 当最大频率高于 400 MHz 的部件在较低时钟频率下工作时,它需要工作频率范围的输入时序,并会以该频率范围的输出时序来输出数据。

29. 此部件拥有内部电压调节器;t<sub>POWER</sub> 为要启动读操作或写操作,开始提供的电源必须高于 V<sub>DD</sub> 最小值的时间。

30. 这些参数是根据输入时序参数(1<sub>CYC</sub>/2 - 250 ps,其中 250 ps 是内部抖动)推导出来的。这些参数仅由设计保证,未在生产中进行过测试。

31. 如图 4 的 (b) 部分所示,t<sub>CHZ</sub>、t<sub>CLZ</sub> 是用一个 5 pF 的负载电容确定的。跃变在稳定状态电压 ± 100 mV 的条件下测量。

32. 在任何电压和温度下,t<sub>CHZ</sub> 均小于 t<sub>CLZ</sub>,且 t<sub>CHZ</sub> 均小于 t<sub>CC</sub>。

33. t<sub>QVLD</sub> 规范适用于 QVLD 信号的上升沿和下降沿。

34. 保持为 >V<sub>IL</sub> 或 <V<sub>IL</sub>。

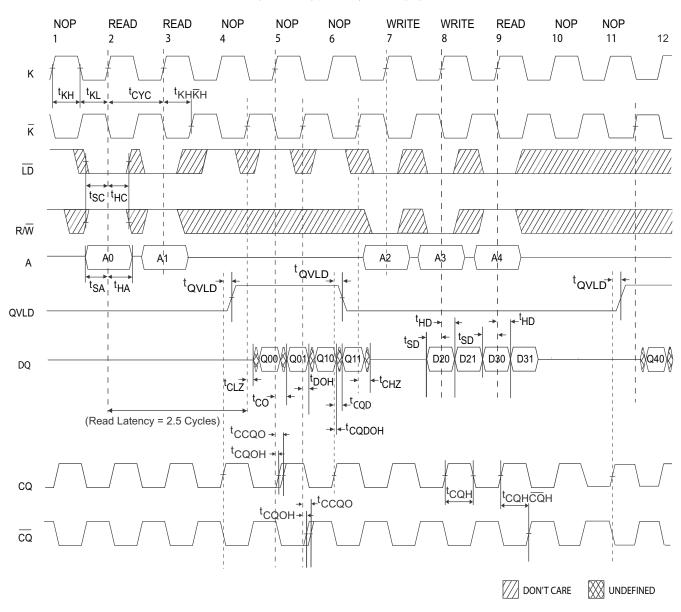

# 开关波形

### 读/写/取消选中操作过程[35,36,37]

### 表 5. 2.5 个周期读取延迟的波形

<sup>&</sup>lt;del>は:注</del> 35. Q00 指地址 A0 的输出。Q01 指 A0 后的下一个内部突发 (Burst) 地址 (即 A0+1)的输出。 36. 在 NOP 后的一个时钟周期内会禁用输出 (High Z)。 37. 在此示例中,如果地址 A4 = A3,则数据 Q40 = D30 且 Q41 = D31。写数据会立即作为读结果往前传。此注解适用于整个示意图。

# 订购信息

下表仅包含目前可以供应的部件。如果您没有看到自己需要的部件,请与当地销售代表联系。如需更多信息,请访问赛普拉斯公司网站 www.cypress.com,并参考 http://www.cypress.com/products 上的产品汇总页。

赛普拉斯公司拥有一个由办事处、解决方案中心、工厂和经销商组成的全球性网络。要查找距您最近的办事处,请访问http://www.cypress.com/go/datasheet/offices?

| 速度<br>(MHz) | 订购代码                 | 封装<br>框图 | 部件和封装类型                                | 工作 范围 |

|-------------|----------------------|----------|----------------------------------------|-------|

| 550         | CY7C1568KV18-550BZXI | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 | 工业    |

|             | CY7C1570KV18-550BZXI |          |                                        |       |

| 500         | CY7C1568KV18-500BZC  | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm)     | 商用    |

|             | CY7C1570KV18-500BZC  |          |                                        |       |

|             | CY7C1568KV18-500BZXC | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 |       |

|             | CY7C1570KV18-500BZXC |          |                                        |       |

|             | CY7C1568KV18-500BZXI | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 | 工业    |

|             | CY7C1570KV18-500BZXI |          |                                        |       |

| 450         | CY7C1568KV18-450BZC  | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm)     | 商用    |

|             | CY7C1570KV18-450BZC  |          |                                        |       |

|             | CY7C1568KV18-450BZXC | 51-85180 | 165 脚 Ball FBGA (13 × 15 × 1.4 mm) 不含铅 |       |

|             | CY7C1570KV18-450BZXC |          |                                        |       |