## LTC2258-12 LTC2257-12/LTC2256-12

12-Bit, 65/40/25Msps Ultralow Power 1.8V ADCs

## FEATURES

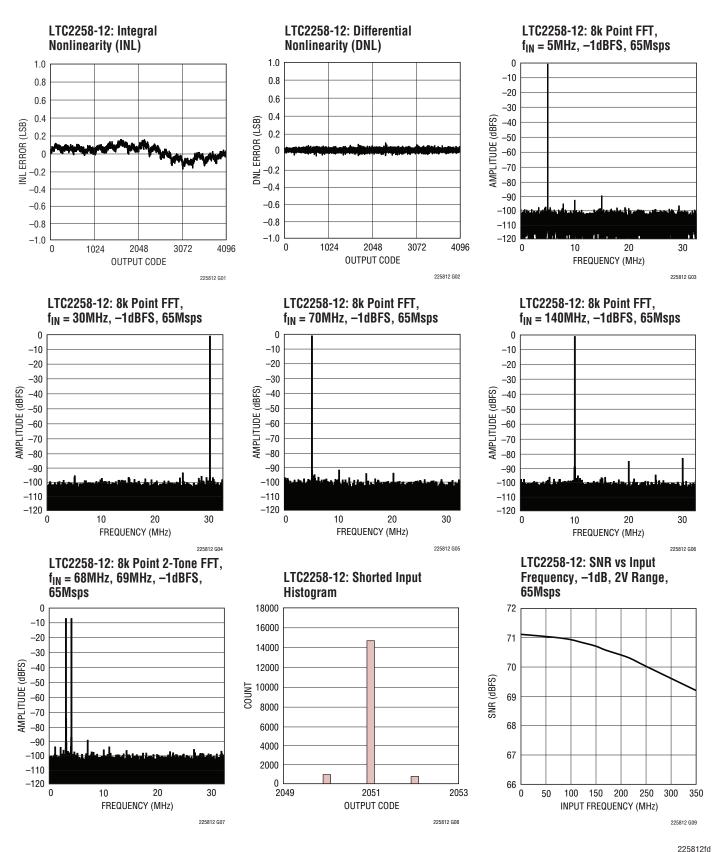

- 71.1dB SNR

- 88dB SFDR

- Low Power: 79mW/47mW/34mW

- Single 1.8V Supply

- CMOS, DDR CMOS or DDR LVDS Outputs

- Selectable Input Ranges: 1V<sub>P-P</sub> to 2V<sub>P-P</sub>

- 800MHz Full-Power Bandwidth S/H

- Optional Data Output Randomizer

- Optional Clock Duty Cycle Stabilizer

- Shutdown and Nap Modes

- Serial SPI Port for Configuration

- Pin Compatible 14-Bit and 12-Bit Versions

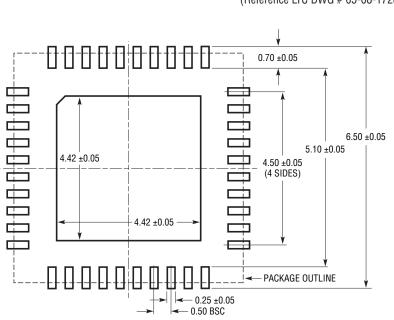

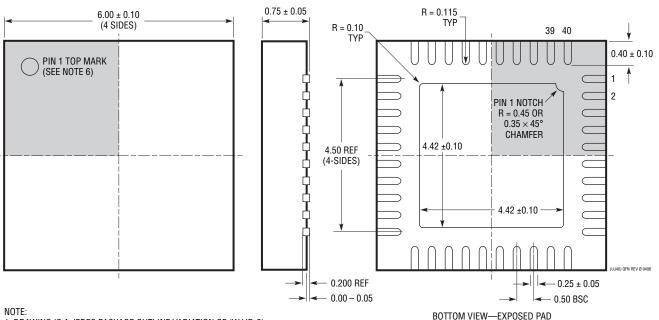

- 40-Pin (6mm × 6mm) QFN Package

## **APPLICATIONS**

- Communications

- Cellular Base Stations

- Software Defined Radios

- Portable Medical Imaging

- Multi-Channel Data Acquisition

- Nondestructive Testing

## DESCRIPTION

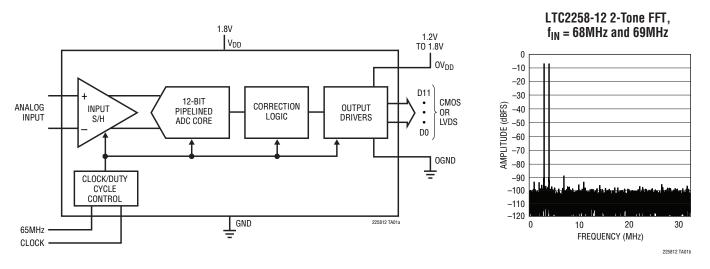

The LTC<sup>®</sup>2258-12/LTC2257-12/LTC2256-12 are sampling 12-bit A/D converters designed for digitizing high frequency, wide dynamic range signals. They are perfect for demanding communications applications with AC performance that includes 71.1dB SNR and 88dB spurious free dynamic range (SFDR). Ultralow jitter of 0.17ps<sub>RMS</sub> allows undersampling of IF frequencies with excellent noise performance.

DC specs include  $\pm 0.3$ LSB INL (typical),  $\pm 0.1$ LSB DNL (typical) and no missing codes over temperature. The transition noise is a low 0.3LSB<sub>RMS</sub>.

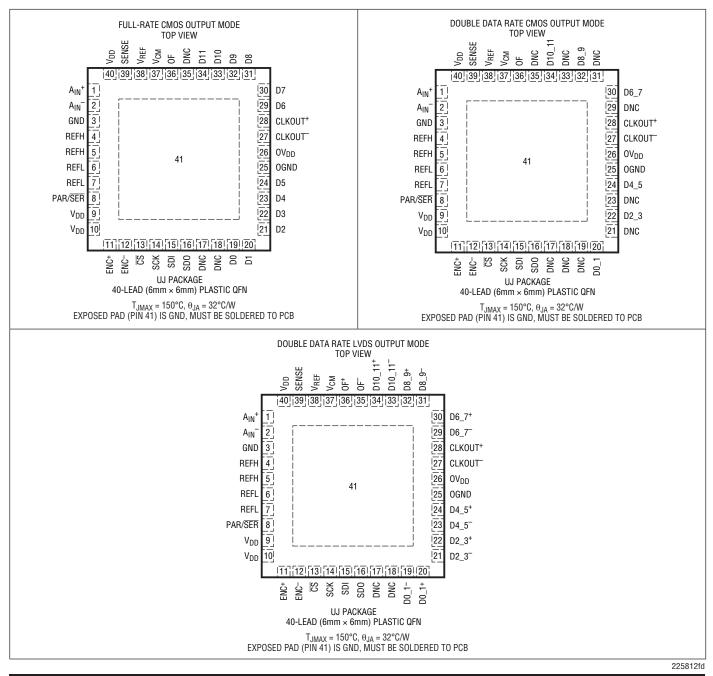

The digital outputs can be either full rate CMOS, double data rate CMOS, or double data rate LVDS. A separate output power supply allows the CMOS output swing to range from 1.2V to 1.8V.

The ENC<sup>+</sup> and ENC<sup>-</sup> inputs may be driven differentially or single-ended with a sine wave, PECL, LVDS, TTL or CMOS inputs. An optional clock duty cycle stabilizer allows high performance at full speed for a wide range of clock duty cycles.

**Δ7**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

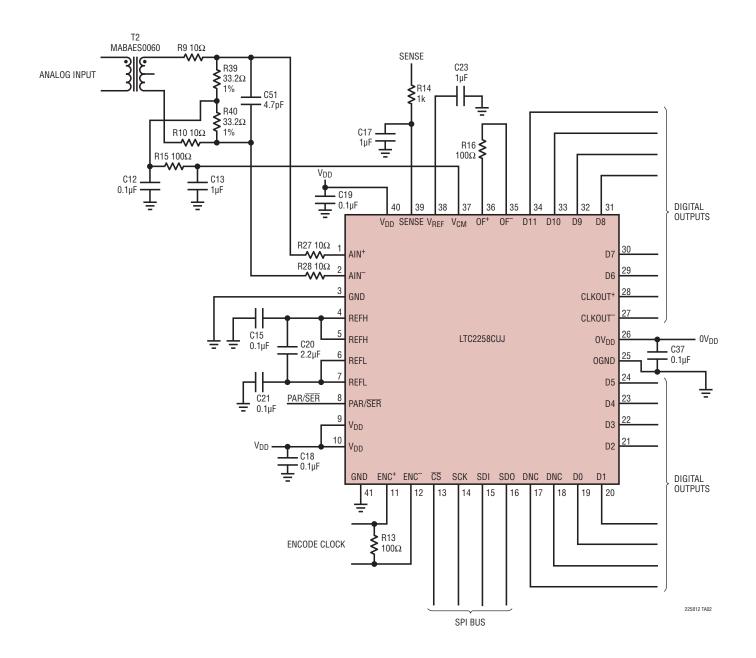

## TYPICAL APPLICATION

## ABSOLUTE MAXIMUM RATINGS (Notes 1, 2)

| Supply Voltages (V <sub>DD</sub> , OV <sub>DD</sub> )0.3V to 2V          |

|--------------------------------------------------------------------------|

| Analog Input Voltage (A <sub>IN</sub> +, A <sub>IN</sub> <sup>-</sup> ,  |

| PAR/ $\overline{SER}$ , SENSE) (Note 3)–0.3V to (V <sub>DD</sub> + 0.2V) |

| Digital Input Voltage (ENC <sup>+</sup> , ENC <sup>-</sup> , CS,         |

| SDI, SCK) (Note 4)0.3V to 3.9V                                           |

| SDO (Note 4)0.3V to 3.9V                                                 |

| Digital Output Voltage –0.3V to (OV <sub>DD</sub> + 0.3 | SV) |

|---------------------------------------------------------|-----|

| Operating Temperature Range:                            |     |

| LTC2258C, LTC2257C, LTC2256C | 0°C to 70°C    |

|------------------------------|----------------|

| LTC2258I, LTC2257I, LTC2256I | 40°C to 85°C   |

| Storage Temperature Range    | -65°C to 150°C |

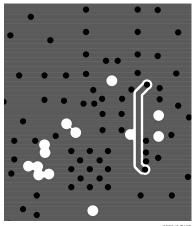

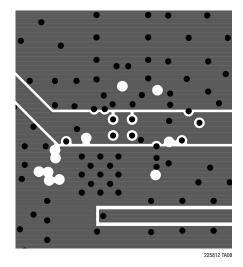

## PIN CONFIGURATIONS

## ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC2258CUJ-12#PBF | LTC2258CUJ-12#TRPBF | LTC2258UJ-12  | 40-Lead (6mm × 6mm) Plastic QFN | 0°C to 70°C       |

| LTC2258IUJ-12#PBF | LTC2258IUJ-12#TRPBF | LTC2258UJ-12  | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 85°C     |

| LTC2257CUJ-12#PBF | LTC2257CUJ-12#TRPBF | LTC2257UJ-12  | 40-Lead (6mm × 6mm) Plastic QFN | 0°C to 70°C       |

| LTC2257IUJ-12#PBF | LTC2257IUJ-12#TRPBF | LTC2257UJ-12  | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 85°C     |

| LTC2256CUJ-12#PBF | LTC2256CUJ-12#TRPBF | LTC2256UJ-12  | 40-Lead (6mm × 6mm) Plastic QFN | 0°C to 70°C       |

| LTC2256IUJ-12#PBF | LTC2256IUJ-12#TRPBF | LTC2256UJ-12  | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

|                               |                                          |   | Ľ    | rc2258-      | 12  | LTC2257-12 |              |     | LI   |              |     |                    |

|-------------------------------|------------------------------------------|---|------|--------------|-----|------------|--------------|-----|------|--------------|-----|--------------------|

| PARAMETER                     | CONDITIONS                               |   | MIN  | ТҮР          | MAX | MIN        | ТҮР          | MAX | MIN  | ТҮР          | MAX | UNITS              |

| Resolution (No Missing Codes) |                                          | • | 12   |              |     | 12         |              |     | 12   |              |     | Bits               |

| Integral Linearity Error      | Differential Analog Input (Note 6)       | • | -1   | ±0.3         | 1   | -1         | ±0.3         | 1   | -1   | ±0.3         | 1   | LSB                |

| Differential Linearity Error  | Differential Analog Input                | • | -0.4 | ±0.1         | 0.4 | -0.4       | ±0.1         | 0.4 | -0.4 | ±0.1         | 0.4 | LSB                |

| Offset Error                  | (Note 7)                                 | • | -9   | ±1.5         | 9   | -9         | ±1.5         | 9   | -9   | ±1.5         | 9   | mV                 |

| Gain Error                    | Internal Reference<br>External Reference | • | -1.5 | ±1.5<br>±0.4 | 1.5 | -1.5       | ±1.5<br>±0.4 | 1.5 | -1.5 | ±1.5<br>±0.4 | 1.5 | %FS<br>%FS         |

| Offset Drift                  |                                          |   |      | ±20          |     |            | ±20          |     |      | ±20          |     | μV/°C              |

| Full-Scale Drift              | Internal Reference<br>External Reference |   |      | ±30<br>±10   |     |            | ±30<br>±10   |     |      | ±30<br>±10   |     | ppm/°C<br>ppm/°C   |

| Transition Noise              | External Reference                       |   |      | 0.32         |     |            | 0.32         |     |      | 0.32         |     | LSB <sub>RMS</sub> |

## **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| SYMBOL              | PARAMETER                                              | CONDITIONS                                            |   | MIN                     | ТҮР             | MAX                     | UNITS             |

|---------------------|--------------------------------------------------------|-------------------------------------------------------|---|-------------------------|-----------------|-------------------------|-------------------|

| V <sub>IN</sub>     | Analog Input Range $(A_{IN}^+ - A_{IN}^-)$             | 1.7V < V <sub>DD</sub> < 1.9V                         | ٠ |                         | 1 to 2          |                         | V <sub>P-P</sub>  |

| V <sub>IN(CM)</sub> | Analog Input Common Mode $(A_{IN}^{+} + A_{IN}^{-})/2$ | Differential Analog Input (Note 8)                    | ٠ | V <sub>CM</sub> – 100mV | V <sub>CM</sub> | V <sub>CM</sub> + 100mV | V                 |

| V <sub>SENSE</sub>  | External Voltage Reference Applied to SENSE            | External Reference Mode                               | ٠ | 0.625                   | 1.250           | 1.300                   | V                 |

| I <sub>INCM</sub>   | Analog Input Common Mode Current                       | Per Pin, 65Msps<br>Per Pin, 40Msps<br>Per Pin, 25Msps |   |                         | 81<br>50<br>31  |                         | μΑ<br>μΑ<br>μΑ    |

| I <sub>IN1</sub>    | Analog Input Leakage Current                           | $0 < A_{IN}^+$ , $A_{IN}^- < V_{DD}$ , No Encode      | ٠ | -1                      |                 | 1                       | μA                |

| I <sub>IN2</sub>    | PAR/SER Input Leakage Current                          | 0 < PAR/ <del>SER</del> < V <sub>DD</sub>             | ٠ | -3                      |                 | 3                       | μA                |

| I <sub>IN3</sub>    | SENSE Input Leakage Current                            | 0.625V < SENSE < 1.3V                                 | ٠ | -6                      |                 | 6                       | μA                |

| t <sub>AP</sub>     | Sample-and-Hold Acquisition Delay Time                 |                                                       |   |                         | 0               |                         | ns                |

| <b>t</b> JITTER     | Sample-and-Hold Acquisition Delay Jitter               |                                                       |   |                         | 0.17            |                         | ps <sub>RMS</sub> |

| CMRR                | Analog Input Common Mode Rejection Ratio               |                                                       |   |                         | 80              |                         | dB                |

| BW-3B               | Full-Power Bandwidth                                   | Figure 6 Test Circuit                                 |   |                         | 800             |                         | MHz               |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. A<sub>IN</sub> = -1dBFS. (Note 5)

|         |                                                       |                                                    |   | Ľ    | rc2258-                    | 12  | LI   | C2257-                       | 12  | LI   | C2256-                       | 12  |                      |

|---------|-------------------------------------------------------|----------------------------------------------------|---|------|----------------------------|-----|------|------------------------------|-----|------|------------------------------|-----|----------------------|

| SYMBOL  | PARAMETER                                             | CONDITIONS                                         |   | MIN  | ТҮР                        | MAX | MIN  | ТҮР                          | MAX | MIN  | ТҮР                          | MAX | UNITS                |

| SNR     | Signal-to-Noise Ratio                                 | 5MHz Input<br>30MHz<br>70MHz Input<br>140MHz Input | • | 69   | 71.1<br>71<br>70.9<br>70.7 |     | 69.6 | 70.8<br>70.7<br>70.6<br>70.4 |     | 69   | 70.5<br>70.5<br>70.1<br>69.9 |     | dB<br>dB<br>dB<br>dB |

| SFDR    | Spurious Free Dynamic Range<br>2nd or 3rd Harmonic    | 5MHz Input<br>30MHz<br>70MHz Input<br>140MHz Input | • | 78   | 90<br>90<br>90<br>84       |     | 79   | 90<br>90<br>90<br>84         |     | 79   | 90<br>90<br>90<br>84         |     | dB<br>dB<br>dB<br>dB |

|         | Spurious Free Dynamic Range<br>4th Harmonic or Higher | 5MHz Input<br>30MHz<br>70MHz Input<br>140MHz Input | • | 83   | 90<br>90<br>90<br>90       |     | 83   | 90<br>90<br>90<br>90         |     | 83   | 90<br>90<br>90<br>84         |     | dB<br>dB<br>dB<br>dB |

| S/(N+D) | Signal-to-Noise Plus<br>Distortion Ratio              | 5MHz Input<br>30MHz<br>70MHz Input<br>140MHz Input | • | 69.1 | 71<br>71<br>70.9<br>70.3   |     | 68.9 | 70.7<br>70.6<br>70.6<br>70.2 |     | 68.3 | 70.5<br>70.4<br>70<br>69.5   |     | dB<br>dB<br>DB<br>dB |

# **INTERNAL REFERENCE CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| PARAMETER                                 | CONDITIONS                      | MIN                          | ТҮР                   | MAX                          | UNITS    |

|-------------------------------------------|---------------------------------|------------------------------|-----------------------|------------------------------|----------|

| V <sub>CM</sub> Output Voltage            | $I_{OUT} = 0$                   | 0.5 • V <sub>DD</sub> – 25mV | 0.5 • V <sub>DD</sub> | 0.5 • V <sub>DD</sub> + 25mV | V        |

| V <sub>CM</sub> Output Temperature Drift  |                                 |                              | ±25                   |                              | ppm/°C   |

| V <sub>CM</sub> Output Resistance         | –600μA < I <sub>OUT</sub> < 1mA |                              | 4                     |                              | Ω        |

| V <sub>REF</sub> Output Voltage           | $I_{OUT} = 0$                   | 1.225                        | 1.250                 | 1.275                        | V        |

| V <sub>REF</sub> Output Temperature Drift |                                 |                              | ±25                   |                              | ppm/°C   |

| V <sub>REF</sub> Output Resistance        | -400μA < I <sub>OUT</sub> < 1mA |                              | 7                     |                              | Ω        |

| V <sub>REF</sub> Line Regulation          | 1.7V < V <sub>DD</sub> < 1.9V   |                              | 0.6                   |                              | mV/V     |

|                                           |                                 | •                            |                       |                              | 225812fd |

## **DIGITAL INPUTS AND OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

| SYMBOL               | PARAMETER                                          | at T <sub>A</sub> = 25°C. (Note 5)<br>Conditions                                       |    | MIN   | ТҮР            | MAX   | UNITS    |

|----------------------|----------------------------------------------------|----------------------------------------------------------------------------------------|----|-------|----------------|-------|----------|

| ENCODE               | INPUTS (ENC <sup>+</sup> , ENC <sup>-</sup> )      | CONDITIONS                                                                             |    |       |                |       |          |

| Different            | ial Encode Mode (ENC <sup>-</sup> Not Tied to GND) |                                                                                        |    |       |                |       |          |

| V <sub>ID</sub>      | Differential Input Voltage                         | (Note 8)                                                                               |    | 0.2   |                |       | V        |

| VICM                 | Common Mode Input Voltage                          | Internally Set<br>Externally Set (Note 8)                                              | •  | 1.1   | 1.2            | 1.6   | V        |

| VIN                  | Input Voltage Range                                | ENC <sup>+</sup> , ENC <sup>-</sup> to GND                                             | •  | 0.2   |                | 3.6   | V        |

| R <sub>IN</sub>      | Input Resistance                                   | (See Figure 10)                                                                        |    |       | 10             |       | kΩ       |

| CIN                  | Input Capacitance                                  | (Note 8)                                                                               |    |       | 3.5            |       | pF       |

| Single-E             | nded Encode Mode (ENC <sup>-</sup> Tied to GND)    |                                                                                        |    |       |                |       |          |

| VIH                  | High Level Input Voltage                           | V <sub>DD</sub> = 1.8V                                                                 |    | 1.2   |                |       | V        |

| VIL                  | Low Level Input Voltage                            | V <sub>DD</sub> = 1.8V                                                                 | •  |       |                | 0.6   | V        |

| VIN                  | Input Voltage Range                                | ENC <sup>+</sup> to GND                                                                | •  | 0     |                | 3.6   | V        |

| R <sub>IN</sub>      | Input Resistance                                   | (See Figure 11)                                                                        |    |       | 30             |       | kΩ       |

| CIN                  | Input Capacitance                                  | (Note 8)                                                                               |    |       | 3.5            |       | pF       |

| DIGITAL              | INPUTS (CS, SDI, SCK)                              |                                                                                        |    |       |                |       |          |

| VIH                  | High Level Input Voltage                           | V <sub>DD</sub> = 1.8V                                                                 | •  | 1.3   |                |       | V        |

| V <sub>IL</sub>      | Low Level Input Voltage                            | V <sub>DD</sub> = 1.8V                                                                 |    |       |                | 0.6   | V        |

| I <sub>IN</sub>      | Input Current                                      | V <sub>IN</sub> = 0V to 3.6V                                                           | •  | -10   |                | 10    | μA       |

| CIN                  | Input Capacitance                                  | (Note 8)                                                                               |    |       | 3              |       | pF       |

| SDO OUT              |                                                    | II-Up Resistor if SDO is Used)                                                         |    |       |                |       |          |

| R <sub>OL</sub>      | Logic Low Output Resistance to GND                 | V <sub>DD</sub> = 1.8V, SDO = 0V                                                       |    |       | 200            |       | Ω        |

| I <sub>OH</sub>      | Logic High Output Leakage Current                  | SDO = 0V to 3.6V                                                                       | •  | -10   |                | 10    | μA       |

| C <sub>OUT</sub>     | Output Capacitance                                 | (Note 8)                                                                               |    |       | 4              |       | pF       |

|                      | DATA OUTPUTS (CMOS MODES: FULL DAT                 | A RATE AND DOUBLE DATA RATE)                                                           |    |       |                |       |          |

| 0V <sub>DD</sub> = 1 | .8V                                                |                                                                                        |    |       |                |       |          |

| V <sub>OH</sub>      | High Level Output Voltage                          | I <sub>0</sub> = -500μA                                                                |    | 1.750 | 1.790          |       | V        |

| V <sub>OL</sub>      | Low Level Output Voltage                           | I <sub>0</sub> = 500μA                                                                 | •  |       | 0.010          | 0.050 | V        |

| 0V <sub>DD</sub> = 1 | .5V                                                |                                                                                        |    |       |                |       |          |

| V <sub>OH</sub>      | High Level Output Voltage                          | I <sub>0</sub> = -500μA                                                                |    |       | 1.488          |       | V        |

| V <sub>OL</sub>      | Low Level Output Voltage                           | I <sub>0</sub> = 500μA                                                                 |    |       | 0.010          |       | V        |

| $OV_{DD} = 1$        | .2V                                                |                                                                                        |    |       |                |       |          |

| V <sub>OH</sub>      | High Level Output Voltage                          | I <sub>0</sub> = -500μA                                                                |    |       | 1.185          |       | V        |

| V <sub>OL</sub>      | Low Level Output Voltage                           | I <sub>0</sub> = 500μA                                                                 |    |       | 0.010          |       | V        |

|                      | DATA OUTPUTS (LVDS MODE)                           |                                                                                        | _( |       |                |       |          |

| V <sub>OD</sub>      | Differential Output Voltage                        | 100 $\Omega$ Differential Load, 3.5mA Mode 100 $\Omega$ Differential Load, 1.75mA Mode | •  | 247   | 350<br>175     | 454   | mV<br>mV |

| V <sub>OS</sub>      | Common Mode Output Voltage                         | 100 $\Omega$ Differential Load, 3.5mA Mode 100 $\Omega$ Differential Load, 1.75mA Mode | •  | 1.125 | 1.250<br>1.250 | 1.375 | V        |

| R <sub>TERM</sub>    | On-Chip Termination Resistance                     | Termination Enabled, OV <sub>DD</sub> = 1.8V                                           |    |       | 100            |       | Ω        |

# **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 9)

|                    |                                                     |                                                     |   | Ľ   | TC2258-        | 12         | Ľ   | TC2257-       | 12         | LI  | C2256-1       | 12        |          |

|--------------------|-----------------------------------------------------|-----------------------------------------------------|---|-----|----------------|------------|-----|---------------|------------|-----|---------------|-----------|----------|

| SYMBOL             | PARAMETER                                           | CONDITIONS                                          |   | MIN | ТҮР            | MAX        | MIN | ТҮР           | MAX        | MIN | ТҮР           | MAX       | UNITS    |

| CMOS Ou            | tput Modes: Full Data Rat                           | e and Double Data Rate                              |   |     |                |            |     |               |            |     |               |           |          |

| V <sub>DD</sub>    | Analog Supply Voltage                               | (Note 10)                                           |   | 1.7 | 1.8            | 1.9        | 1.7 | 1.8           | 1.9        | 1.7 | 1.8           | 1.9       | V        |

| OV <sub>DD</sub>   | Output Supply Voltage                               | (Note 10)                                           | • | 1.1 |                | 1.9        | 1.1 |               | 1.9        | 1.1 |               | 1.9       | V        |

| I <sub>VDD</sub>   | Analog Supply Current                               | DC Input<br>Sine Wave Input                         | • |     | 43.6<br>44.2   | 49         |     | 26.3<br>27.2  | 30         |     | 18.9<br>19.1  | 21        | mA<br>mA |

| I <sub>OVDD</sub>  | Digital Supply Current                              | Sine Wave Input, OV <sub>DD</sub> =1.2V             |   |     | 2.3            |            |     | 1.5           |            |     | 0.9           |           | mA       |

| P <sub>DISS</sub>  | Power Dissipation                                   | DC Input<br>Sine Wave Input, OV <sub>DD</sub> =1.2V | • |     | 78.5<br>82.3   | 89         |     | 47.3<br>50.8  | 54         |     | 34<br>35.5    | 38        | mW<br>mW |

| LVDS Out           | put Mode                                            |                                                     |   |     |                |            |     |               |            |     |               |           |          |

| V <sub>DD</sub>    | Analog Supply Voltage                               | (Note 10)                                           | • | 1.7 | 1.8            | 1.9        | 1.7 | 1.8           | 1.9        | 1.7 | 1.8           | 1.9       | V        |

| OV <sub>DD</sub>   | Output Supply Voltage                               | (Note 10)                                           | • | 1.7 |                | 1.9        | 1.7 |               | 1.9        | 1.7 |               | 1.9       | V        |

| I <sub>VDD</sub>   | Analog Supply Current                               | Sine Wave Input                                     | • |     | 48.1           | 54         |     | 30.6          | 35         |     | 22.7          | 26        | mA       |

| I <sub>OVDD</sub>  | Digital Supply Current<br>(0V <sub>DD</sub> = 1.8V) | Sine Input, 1.75mA Mode<br>Sine Input, 3.5mA Mode   | • |     | 18.8<br>36.7   | 21<br>40   |     | 18.8<br>36.7  | 21<br>40   |     | 18.8<br>36.7  | 21<br>40  | mA<br>mA |

| P <sub>DISS</sub>  | Power Dissipation                                   | Sine Input, 1.75mA Mode<br>Sine Input, 3.5mA Mode   | • |     | 120.4<br>152.6 | 135<br>170 |     | 88.9<br>121.1 | 101<br>135 |     | 74.7<br>106.9 | 85<br>119 | mW<br>mW |

| All Output         | t Modes                                             |                                                     |   |     |                |            |     |               |            |     |               |           |          |

| P <sub>SLEEP</sub> | Sleep Mode Power                                    |                                                     |   |     | 0.5            |            |     | 0.5           |            |     | 0.5           |           | mW       |

| P <sub>NAP</sub>   | Nap Mode Power                                      |                                                     |   |     | 9              |            |     | 9             |            |     | 9             |           | mW       |

| PDIFFCLK           |                                                     | erential Encode Mode Enabled<br>Nap or Sleep Modes) |   |     | 10             |            |     | 10            |            |     | 10            |           | mW       |

# **TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 5)

1 100057 10 Т 1 100056 10 Т 1 100050 10

|                 |                                           |                                                       |    | Ľ          | C2258-       | 12         | LT            | C2257-       | 12         | LT         | C2256-   | 12         |          |

|-----------------|-------------------------------------------|-------------------------------------------------------|----|------------|--------------|------------|---------------|--------------|------------|------------|----------|------------|----------|

| SYMBOL          | PARAMETER                                 | CONDITIONS                                            |    | MIN        | ТҮР          | MAX        | MIN           | ТҮР          | MAX        | MIN        | ТҮР      | MAX        | UNITS    |

| f <sub>S</sub>  | Sampling Frequency                        | (Note 10)                                             | •  | 1          |              | 65         | 1             |              | 40         | 1          |          | 25         | MHz      |

| tL              | ENC Low Time (Note 8)                     | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On | •• | 7.3<br>2.0 | 7.69<br>7.69 | 500<br>500 | 11.88<br>2.00 | 12.5<br>12.5 | 500<br>500 | 19<br>2.00 | 20<br>20 | 500<br>500 | ns<br>ns |

| t <sub>H</sub>  | ENC High Time (Note 8)                    | Duty Cycle Stabilizer Off<br>Duty Cycle Stabilizer On | •  | 7.3<br>2.0 | 7.69<br>7.69 | 500<br>500 | 11.88<br>2.00 | 12.5<br>12.5 | 500<br>500 | 19<br>2.00 | 20<br>20 | 500<br>500 | ns<br>ns |

| t <sub>AP</sub> | Sample-and-Hold<br>Acquisition Delay Time |                                                       |    |            | 0            |            |               | 0            |            |            | 0        |            | ns       |

| SYMBOL            | PARAMETER                       | CONDITIONS                                   | CONDITIONS |     |            |     | UNITS            |

|-------------------|---------------------------------|----------------------------------------------|------------|-----|------------|-----|------------------|

| Digital Da        | ta Outputs (CMOS Modes: Full Da |                                              |            |     | <u> </u>   |     |                  |

| t <sub>D</sub>    | ENC to Data Delay               | $C_L = 5pF$ (Note 8)                         | •          | 1.1 | 1.7        | 3.1 | ns               |

| t <sub>C</sub>    | ENC to CLKOUT Delay             | C <sub>L</sub> = 5pF (Note 8)                | •          | 1   | 1.4        | 2.6 | ns               |

| t <sub>SKEW</sub> | DATA to CLKOUT Skew             | $t_D - t_C$ (Note 8)                         | •          | 0   | 0.3        | 0.6 | ns               |

|                   | Pipeline Latency                | Full Data Rate Mode<br>Double Data Rate Mode |            |     | 5.0<br>5.5 |     | Cycles<br>Cycles |

### TIMING CHARACTERISTICS The e denotes the specifications which apply over the full operating temperature

| range, otherwise specifications are a | at T <sub>A</sub> = 25°C. ( | (Note 5) |

|---------------------------------------|-----------------------------|----------|

|---------------------------------------|-----------------------------|----------|

| SYMBOL            | PARAMETER                | CONDITIONS                                                                     | CONDITIONS |           |     | MAX | UNITS    |

|-------------------|--------------------------|--------------------------------------------------------------------------------|------------|-----------|-----|-----|----------|

| Digital Da        | ata Outputs (LVDS Mode)  |                                                                                |            |           |     |     |          |

| t <sub>D</sub>    | ENC to Data Delay        | $C_L = 5pF$ (Note 8)                                                           |            | 1.1       | 1.8 | 3.2 | ns       |

| t <sub>C</sub>    | ENC to CLKOUT Delay      | $C_L = 5pF$ (Note 8)                                                           | •          | 1         | 1.5 | 2.7 | ns       |

| t <sub>SKEW</sub> | DATA to CLKOUT Skew      | $t_D - t_C$ (Note 8)                                                           | •          | 0         | 0.3 | 0.6 | ns       |

|                   | Pipeline Latency         |                                                                                |            |           | 5.5 |     | Cycles   |

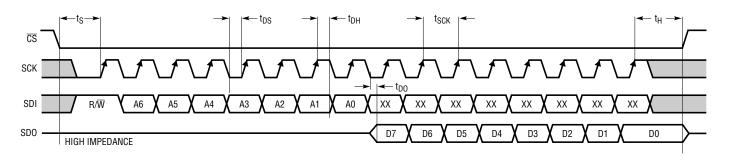

| SPI Port 1        | Fiming (Note 8)          |                                                                                |            |           |     |     |          |

| t <sub>SCK</sub>  | SCK Period               | Write Mode<br>Readback Mode, C <sub>SDO</sub> = 20pF, R <sub>PULLUP</sub> = 2k | •          | 40<br>250 |     |     | ns<br>ns |

| t <sub>S</sub>    | CS to SCK Setup Time     |                                                                                | •          | 5         |     |     | ns       |

| t <sub>H</sub>    | SCK to CS Setup Time     |                                                                                | •          | 5         |     |     | ns       |

| t <sub>DS</sub>   | SDI Setup Time           |                                                                                | •          | 5         |     |     | ns       |

| t <sub>DH</sub>   | SDI Hold Time            |                                                                                | •          | 5         |     |     | ns       |

| t <sub>DO</sub>   | SCK Falling to SDO Valid | Readback Mode, C <sub>SDO</sub> = 20pF, R <sub>PULLUP</sub> = 2k               | •          |           |     | 125 | ns       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All voltage values are with respect to GND with GND and OGND shorted (unless otherwise noted).

**Note 3:** When these pin voltages are taken below GND or above  $V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND or above  $V_{DD}$  without latchup.

**Note 4:** When these pin voltages are taken below GND they will be clamped by internal diodes. When these pin voltages are taken above  $V_{DD}$  they will not be clamped by internal diodes. This product can handle input currents of greater than 100mA below GND without latchup.

**Note 5:**  $V_{DD} = OV_{DD} = 1.8V$ ,  $f_{SAMPLE} = 65MHz$  (LTC2258), 40MHz (LTC2257), or 25MHz (LTC2256), LVDS outputs with internal

termination disabled, differential ENC<sup>+</sup>/ENC<sup>-</sup> =  $2V_{P-P}$  sine wave, input range =  $2V_{P-P}$  with differential drive, unless otherwise noted.

**Note 6:** Integral nonlinearity is defined as the deviation of a code from a best fit straight line to the transfer curve. The deviation is measured from the center of the quantization band.

**Note 7:** Offset error is the offset voltage measured from –0.5 LSB when the output code flickers between 0000 0000 0000 and 1111 1111 1111 in 2's complement output mode.

Note 8: Guaranteed by design, not subject to test.

**Note 9:**  $V_{DD}$  = 1.8V,  $f_{SAMPLE}$  = 65MHz (LTC2258), 40MHz (LTC2257), or 25MHz (LTC2256), ENC<sup>+</sup> = single-ended 1.8V square wave, ENC<sup>-</sup> = 0V, input range =  $2V_{P-P}$  with differential drive, 5pF load on each digital output unless otherwise noted.

Note 10: Recommended operating conditions.

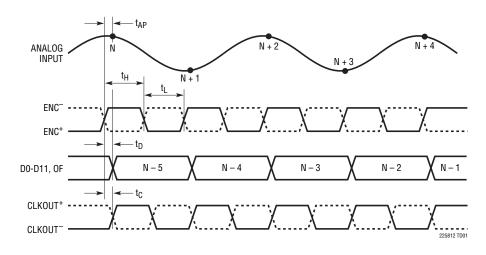

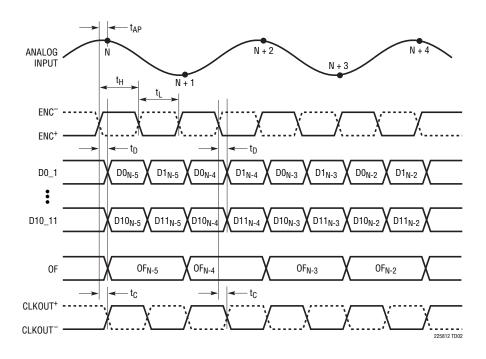

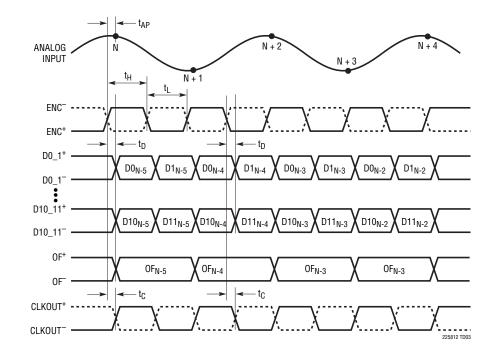

## TIMING DIAGRAMS

Full-Rate CMOS Output Mode Timing All Outputs Are Single-Ended and Have CMOS Levels

Double Data Rate CMOS Output Mode Timing All Outputs Are Single-Ended and Have CMOS Levels

### TIMING DIAGRAMS

Double Data Rate LVDS Output Mode Timing All Outputs Are Differential and Have LVDS Levels

SPI Port Timing (Readback Mode)

SPI Port Timing (Write Mode)

10

225812fd

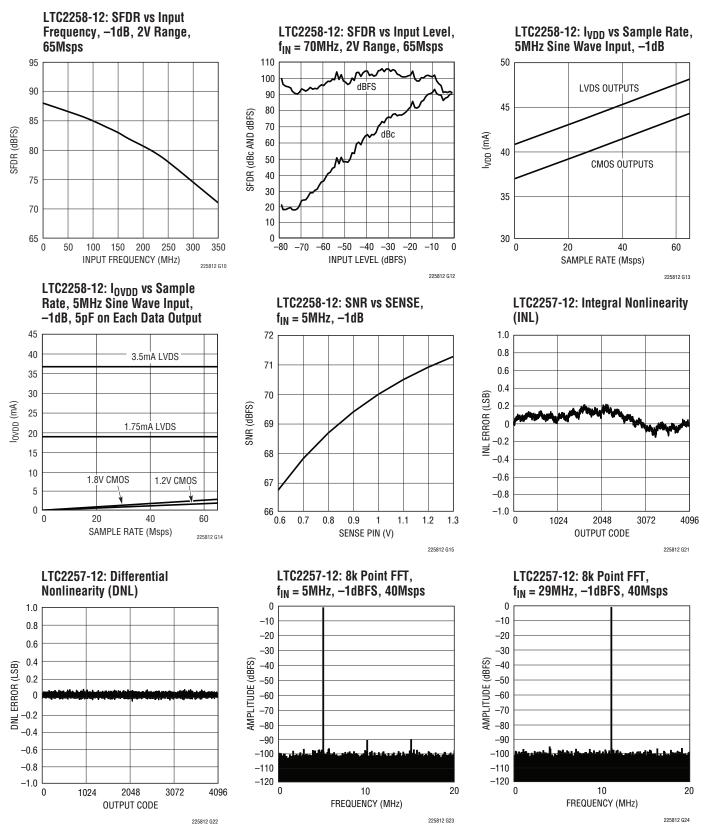

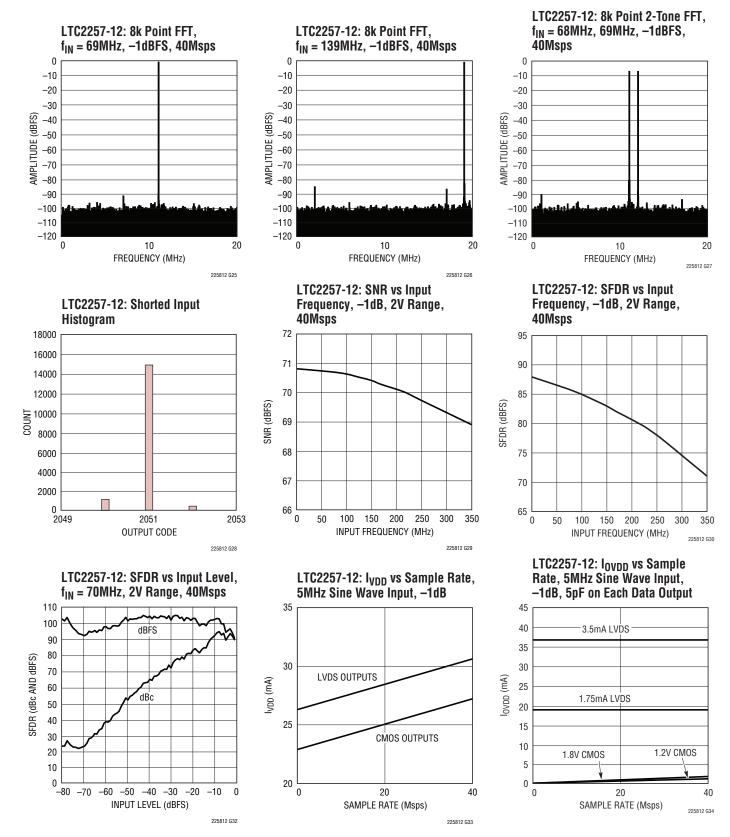

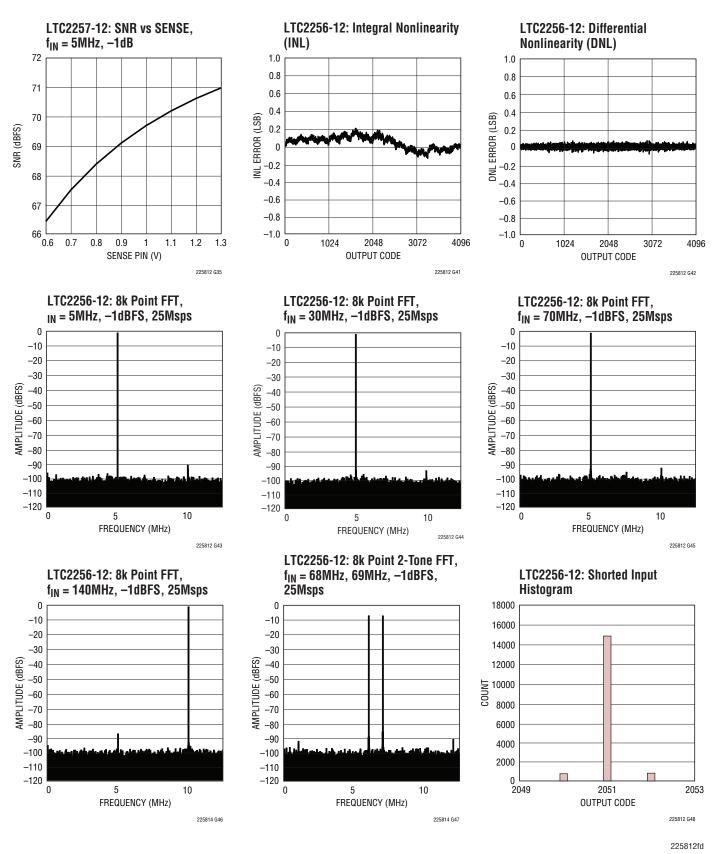

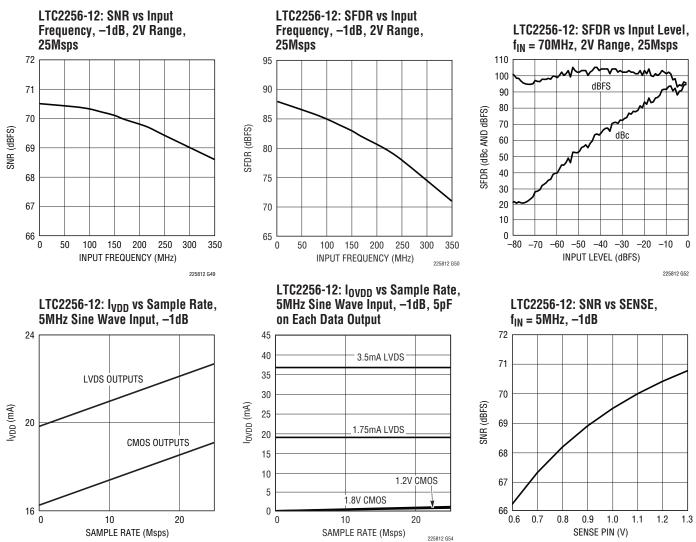

## **TYPICAL PERFORMANCE CHARACTERISTICS**

226112 G53

## PIN FUNCTIONS

## PINS THAT ARE THE SAME FOR ALL DIGITAL OUTPUT MODES

AIN<sup>+</sup> (Pin 1): Positive Differential Analog Input.

A<sub>IN</sub><sup>-</sup> (Pin 2): Negative Differential Analog Input.

GND (Pin 3): ADC Power Ground.

**REFH (Pins 4, 5):** ADC High Reference. Bypass to Pins 6, 7 with a  $2.2\mu$ F ceramic capacitor and to ground with a  $0.1\mu$ F ceramic capacitor.

**REFL (Pins 6, 7):** ADC Low Reference. Bypass to Pins 4, 5 with a  $2.2\mu$ F ceramic capacitor and to ground with a  $0.1\mu$ F ceramic capacitor.

**PAR/SER (Pin 8):** Programming Mode Selection Pin. Connect to ground to enable the serial programming mode.  $\overline{CS}$ , SCK, SDI, SDO become a serial interface that control the A/D operating modes. Connect to V<sub>DD</sub> to enable the parallel programming mode where  $\overline{CS}$ , SCK, SDI become parallel logic inputs that control a reduced set of the A/D operating modes. PAR/SER should be connected directly to ground or the V<sub>DD</sub> of the part and not be driven by a logic signal.

$V_{DD}$  (Pins 9, 10, 40): 1.8V Analog Power Supply. Bypass to ground with 0.1µF ceramic capacitors. Pins 9 and 10 can share a bypass capacitor.

**ENC<sup>+</sup> (Pin 11):** Encode Input. Conversion starts on the rising edge.

**ENC<sup>-</sup> (Pin 12):** Encode Complement Input. Conversion starts on the falling edge.

**CS** (Pin 13): In serial programming mode, (PAR/ $\overline{SER} = 0V$ ),  $\overline{CS}$  is the serial interface chip select input. When  $\overline{CS}$  is low, SCK is enabled for shifting data on SDI into the mode control registers. In the parallel programming mode (PAR/ $\overline{SER} = V_{DD}$ ),  $\overline{CS}$  controls the clock duty cycle stabilizer. When  $\overline{CS}$  is low, the clock duty cycle stabilizer is turned off. When  $\overline{CS}$  is high, the clock duty cycle stabilizer is turned on.  $\overline{CS}$  can be driven with 1.8V to 3.3V logic.

**SCK (Pin 14):** In serial programming mode, (PAR/SER = 0V), SCK is the serial interface clock input. In the

parallel programming mode (PAR/ $\overline{\text{SER}}$  = V<sub>DD</sub>), SCK controls the digital output mode. When SCK is low, the full-rate CMOS output mode is enabled. When SCK is high, the double data rate LVDS output mode (with 3.5mA output current) is enabled. SCK can be driven with 1.8V to 3.3V logic.

**SDI (Pin 15):** In serial programming mode, (PAR/ $\overline{SER}$  = 0V), SDI is the serial interface data input. Data on SDI is clocked into the mode control registers on the rising edge of SCK. In the parallel programming mode (PAR/ $\overline{SER}$  =  $V_{DD}$ ), SDI can be used to power down the part. When SDI is low, the part operates normally. When SDI is high, the part enters sleep mode. SDI can be driven with 1.8V to 3.3V logic.

**SDO (Pin 16):** In serial programming mode, (PAR/SER = 0V), SDO is the optional serial interface data output. Data on SDO is read back from the mode control registers and can be latched on the falling edge of SCK. SDO is an open-drain NMOS output that requires an external 2k pull-up resistor to 1.8V-3.3V. If read back from the mode control registers is not needed, the pull-up resistor is not necessary and SDO can be left unconnected. In the parallel programming mode (PAR/SER = V<sub>DD</sub>), SDO is not used and should not be connected.

OGND (Pin 25): Output Driver Ground.

$OV_{DD}$  (Pin 26): Output Driver Supply. Bypass to ground with a 0.1µF ceramic capacitor.

$V_{CM}$  (Pin 37): Common Mode Bias Output, Nominally Equal to  $V_{DD}/2.\ V_{CM}$  should be used to bias the common mode of the analog inputs. Bypass to ground with a  $0.1\mu F$  ceramic capacitor.

$V_{REF}$  (Pin 38): Reference Voltage Output, Nominally 1.25V. Bypass to ground with a 1µF ceramic capacitor.

**SENSE (Pin 39):** Reference Programming Pin. Connecting SENSE to  $V_{DD}$  selects the internal reference and a ±1V input range. Connecting SENSE to ground selects the internal reference and a ±0.5V input range. An external reference between 0.625V and 1.3V applied to SENSE selects an input range of ±0.8 • V<sub>SENSE</sub>.

225812fr

## PIN FUNCTIONS

#### FULL-RATE CMOS OUTPUT MODE

All Pins Below Have CMOS Output Levels (OGND to  $OV_{DD}$ )

**D0 to D11 (Pins 19-24, 29-34):** Digital Outputs. D11 is the MSB.

CLKOUT<sup>-</sup> (Pin 27): Inverted version of CLKOUT<sup>+</sup>.

**CLKOUT**<sup>+</sup> (**Pin 28**): Data Output Clock. The digital outputs normally transition at the same time as the falling edge of CLKOUT<sup>+</sup>. The phase of CLKOUT<sup>+</sup> can also be delayed relative to the digital outputs by programming the mode control registers.

DNC (Pins 17, 18, 35): Do not connect these pins.

**OF (Pin 36):** Over/Under Flow Digital Output. OF is high when an overflow or underflow has occurred.

#### DOUBLE DATA RATE CMOS OUTPUT MODE

All Pins Below Have CMOS Output Levels (OGND to  $OV_{DD}$ )

**D0\_1 to D10\_11 (Pins 20, 22, 24, 30, 32, 34):** Double Data Rate Digital Outputs. Two data bits are multiplexed onto each output pin. The even data bits (D0, D2, D4, D6, D8, D10) appear when CLKOUT<sup>+</sup> is low. The odd data bits (D1, D3, D5, D7, D9, D11) appear when CLKOUT<sup>+</sup> is high.

CLKOUT<sup>-</sup> (Pin 27): Inverted version of CLKOUT<sup>+</sup>.

**CLKOUT**<sup>+</sup> (**Pin 28**): Data Output Clock. The digital outputs normally transition at the same time as the falling and rising edges of CLKOUT<sup>+</sup>. The phase of CLKOUT<sup>+</sup> can also be delayed relative to the digital outputs by programming the mode control registers.

DNC (Pins 17, 18, 19, 21, 23, 29, 31, 33, 35): Do not connect these pins.

**OF (Pin 36):** Over/Under Flow Digital Output. OF is high when an overflow or underflow has occurred.

#### DOUBLE DATA RATE LVDS OUTPUT MODE

All Pins Below Have LVDS Output Levels. The Output Current Level is Programmable. There is an Optional Internal 100 $\Omega$  Termination Resistor Between the Pins of Each LVDS Output Pair.

**D0\_1<sup>-/</sup>D0\_1<sup>+</sup> to D10\_11<sup>-/</sup>D10\_11<sup>+</sup> (Pins 19/20, 21/22, 23/24, 29/30, 31/32, 33/34):** Double Data Rate Digital Outputs. Two data bits are multiplexed onto each differential output pair. The even data bits (D0, D2, D4, D6, D8, D10) appear when CLKOUT<sup>+</sup> is low. The odd data bits (D1, D3, D5, D7, D9, D11) appear when CLKOUT<sup>+</sup> is high.

**CLKOUT**<sup>-/</sup>**CLKOUT**<sup>+</sup> (**Pins 27/28**): Data Output Clock. The digital outputs normally transition at the same time as the falling and rising edges of CLKOUT<sup>+</sup>. The phase of CLKOUT<sup>+</sup> can also be delayed relative to the digital outputs by programming the mode control registers.

**OF**<sup>-</sup>/**OF**<sup>+</sup> (**Pins 35/36**): Over/Under Flow Digital Output. OF<sup>+</sup> is high when an overflow or underflow has occurred.

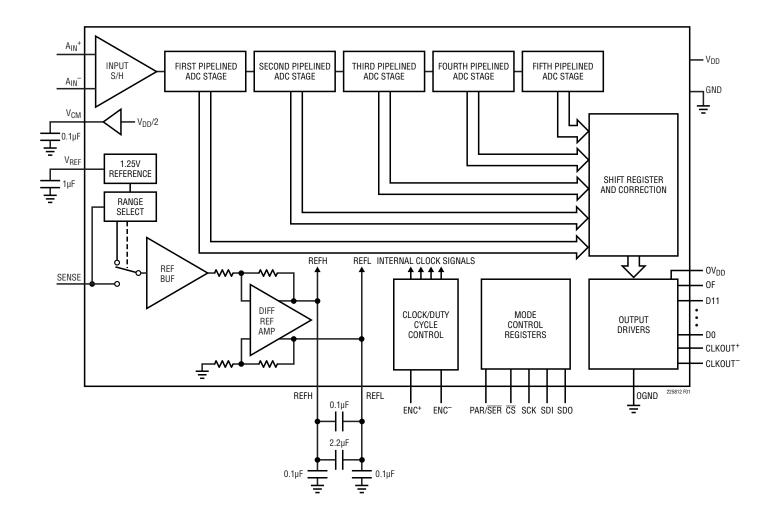

## FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

#### **CONVERTER OPERATION**

The LTC2258-12/LTC2257-12/LTC2256-12 are low power 12-bit 65Msps/40Msps/25Msps A/D converters that are powered by a single 1.8V supply. The analog inputs should be driven differentially. The encode input can be driven differentially or single-ended for lower power consumption. The digital outputs can be CMOS, double data rate CMOS (to halve the number of output lines), or double data rate LVDS (to reduce digital noise in the system.) Many additional features can be chosen by programming the mode control registers through a serial SPI port. See the Serial Programming Mode section.

### ANALOG INPUT

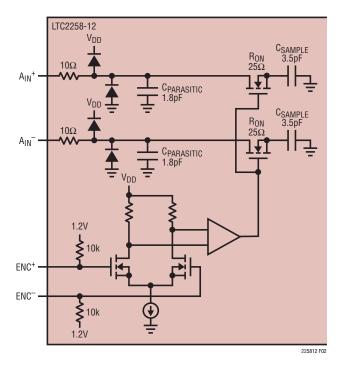

The analog input is a differential CMOS sample-and-hold circuit (Figure 2). The inputs should be driven differentially around a common mode voltage set by the V<sub>CM</sub> output pin, which is nominally V<sub>DD</sub>/2. For the 2V input range, the inputs should swing from V<sub>CM</sub> – 0.5V to V<sub>CM</sub> + 0.5V. There should be 180° phase difference between the inputs.

Figure 2. Equivalent Input Circuit

#### **INPUT DRIVE CIRCUITS**

#### Input filtering

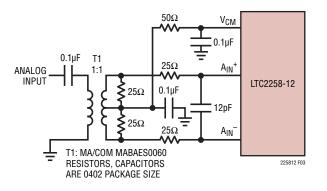

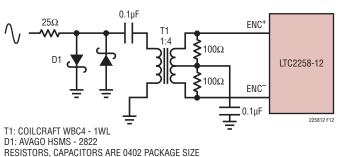

If possible, there should be an RC lowpass filter right at the analog inputs. This lowpass filter isolates the drive circuitry from the A/D sample-and-hold switching, and also limits wideband noise from the drive circuitry. Figure 3 shows an example of an input RC filter. The RC component values should be chosen based on the application's input frequency.

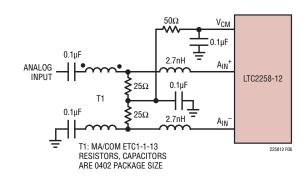

Figure 3. Analog Input Circuit Using a Transformer. Recommended for Input Frequencies from 5MHz to 70MHz

50Ω

0.1uF

25Ω

250

Figure 4. Recommended Front-End Circuit for Input

V<sub>СМ</sub> 0.1µF

AIN

4.7pF

AIN

ITC2258-12

225812 F04

Ŧ

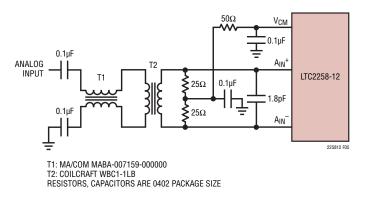

Figure 3 shows the analog input being driven by an RF transformer with a center-tapped secondary. The center tap is biased with  $V_{CM}$ , setting the A/D input at its optimal DC level. At higher input frequencies a transmission line balun transformer (Figures 4 to 6) has better balance, resulting in lower A/D distortion.

Figure 5. Recommended Front-End Circuit for Input Frequencies from 170MHz to 270MHz

0.1ul

T1: MA/COM MABA-007159-000000

RESISTORS, CAPACITORS ARE 0402 PACKAGE SIZE

Frequencies from 70MHz to 170MHz

T2: MA/COM MABAES0060

ANALOG

INPUT

#### **Amplifier Circuits**

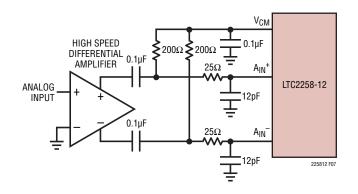

Figure 7 shows the analog input being driven by a high speed differential amplifier. The output of the amplifier is AC coupled to the A/D so the amplifier's output common mode voltage can be optimally set to minimize distortion.

At very high frequencies an RF gain block will often have lower distortion than a differential amplifier. If the gain block is single-ended, then a transformer circuit (Figures 4 to 6) should convert the signal to differential before driving the A/D.

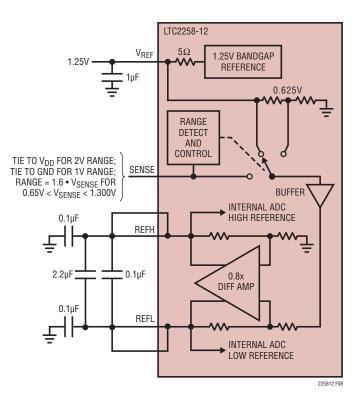

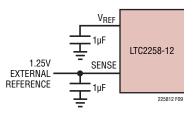

#### Reference

The LTC2258-12/2257-12/2256-12 has an internal 1.25V voltage reference. For a 2V input range using the internal reference, connect SENSE to  $V_{DD}$ . For a 1V input range using the internal reference, connect SENSE to ground. For a 2V input range with an external reference, apply a 1.25V reference voltage to SENSE (Figure 9.)

The input range can be adjusted by applying a voltage to SENSE that is between 0.625V and 1.30V. The input range will then be  $1.6 \bullet V_{SENSE}$ .

The V<sub>REF</sub>, REFH and REFL pins should be bypassed as shown in Figure 8. The 0.1 $\mu$ F capacitor between REFH and REFL should be as close to the pins as possible (not on the back side of the circuit board).

Figure 7. Front-End Circuit Using a High Speed Differential Amplifier

Figure 9. Using an External 1.25V Reference

#### **Encode Input**

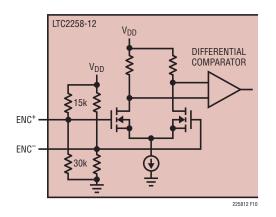

The signal quality of the encode inputs strongly affects the A/D noise performance. The encode inputs should be treated as analog signals—do not route them next to digital traces on the circuit board. There are two modes of operation for the encode inputs: the differential encode mode (Figure 10) and the single-ended encode mode (Figure 11).

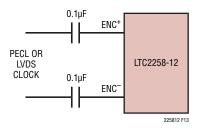

The differential encode mode is recommended for sinusoidal, PECL or LVDS encode inputs (Figures 12, 13). The encode inputs are internally biased to 1.2V through 10k equivalent resistance. The encode inputs can be taken above  $V_{DD}$  (up to 3.6V), and the common mode range is from 1.1V to 1.6V. In the differential encode mode, ENC<sup>-</sup> should stay at least 200mV above ground to avoid falsely triggering the single-ended encode mode. For good jitter performance ENC<sup>+</sup> and ENC<sup>-</sup> should have fast rise and fall times.

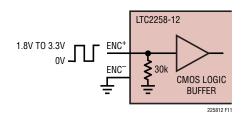

The single-ended encode mode should be used with CMOS encode inputs. To select this mode,  $ENC^-$  is connected to ground and  $ENC^+$  is driven with a square wave encode input.  $ENC^+$  can be taken above  $V_{DD}$  (up to 3.6V) so 1.8V to 3.3V CMOS logic levels can be used. The ENC<sup>+</sup> threshold is 0.9V. For good jitter performance ENC<sup>+</sup> should have fast rise and fall times.

#### **Clock Duty Cycle Stabilizer**

For good performance the encode signal should have a  $50\%(\pm 5\%)$  duty cycle. If the optional clock duty cycle stabilizer circuit is enabled, the encode duty cycle can vary from 30% to 70% and the duty cycle stabilizer will maintain a constant 50% internal duty cycle. If the encode signal changes frequency or is turned off, the duty cycle stabilizer circuit requires one hundred clock cycles to lock onto the input clock. The duty cycle stabilizer is enabled

Figure 10. Equivalent Encode Input Circuit for Differential Encode Mode

Figure 11. Equivalent Encode Input Circuit for Single-Ended Encode Mode

Figure 12. Sinusoidal Encode Drive

Figure 13. PECL or LVDS Encode Drive

by mode control register A2 (serial programming mode), or by  $\overline{\text{CS}}$  (parallel programming mode).

For applications where the sample rate needs to be changed quickly, the clock duty cycle stabilizer can be disabled. If the duty cycle stabilizer is disabled, care should be taken to make the sampling clock have a  $50\%(\pm 5\%)$  duty cycle. The duty cycle stabilizer should not be used below 5Msps.

#### **DIGITAL OUTPUTS**

#### **Digital Output Modes**

The LTC2258-12/LTC2257-12/LTC2256-12 can operate in three digital output modes: full rate CMOS, double data rate CMOS (to halve the number of output lines), or double data rate LVDS (to reduce digital noise in the system). The output mode is set by mode control register A3 (serial programming mode), or by SCK (parallel programming mode). Note that double data rate CMOS cannot be selected in the parallel programming mode.

#### Full-Rate CMOS Mode

In full-rate CMOS mode the 12 digital outputs (D0-D11), overflow (OF), and the data output clocks (CLKOUT<sup>+</sup>, CLKOUT<sup>-</sup>) have CMOS output levels. The outputs are powered by  $OV_{DD}$  and OGND which are isolated from the A/D core power and ground.  $OV_{DD}$  can range from 1.1V to 1.9V, allowing 1.2V through 1.8V CMOS logic outputs.

For good performance the digital outputs should drive minimal capacitive loads. If the load capacitance is larger than 10pF a digital buffer should be used.

#### **Double Data Rate CMOS Mode**

In double data rate CMOS mode, two data bits are multiplexed and output on each data pin. This reduces the number of data lines by six, simplifying board routing and reducing the number of input pins needed to receive the data. The 6 digital outputs (D0\_1, D2\_3, D4\_5, D6\_7, D8\_9, D10\_11), overflow (OF), and the data output clocks (CLKOUT<sup>+</sup>, CLKOUT<sup>-</sup>) have CMOS output levels. The outputs are powered by  $OV_{DD}$  and OGND which are isolated from the A/D core power and ground.  $OV_{DD}$  can range from 1.1V to 1.9V, allowing 1.2V through 1.8V CMOS logic outputs.

For good performance the digital outputs should drive minimal capacitive loads. If the load capacitance is larger than 10pF a digital buffer should be used.

#### **Double Data Rate LVDS Mode**

In double data rate LVDS mode, two data bits are multiplexed and output on each differential output pair. There are 6 LVDS output pairs (D0\_1+/D0\_1- through D10\_11+/D10\_11-) for the digital output data. Overflow (OF+/OF-) and the data output clock (CLKOUT+/CLKOUT-) each have an LVDS output pair.

By default the outputs are standard LVDS levels: 3.5mA output current and a 1.25V output common mode voltage. An external  $100\Omega$  differential termination resistor is required for each LVDS output pair. The termination resistors should be located as close as possible to the LVDS receiver.

The outputs are powered by  $OV_{DD}$  and OGND which are isolated from the A/D core power and ground. In LVDS mode,  $OV_{DD}$  must be 1.8V.

#### Programmable LVDS Output Current

In LVDS mode, the default output driver current is 3.5mA. This current can be adjusted by serially programming mode control register A3. Available current levels are 1.75mA, 2.1mA, 2.5mA, 3mA, 3.5mA, 4mA and 4.5mA.

#### **Optional LVDS Driver Internal Termination**

In most cases using just an external  $100\Omega$  termination resistor will give excellent LVDS signal integrity. In addition, an optional internal  $100\Omega$  termination resistor can be enabled by serially programming mode control register A3. The internal termination helps absorb any reflections caused by imperfect termination at the receiver. When the internal termination is enabled, the output driver current is increased by 1.6x to maintain about the same output voltage swing.

#### **Overflow Bit**

The overflow output bit (OF) outputs a logic high when the analog input is either overranged or underranged. The overflow bit has the same pipeline latency as the data bits.

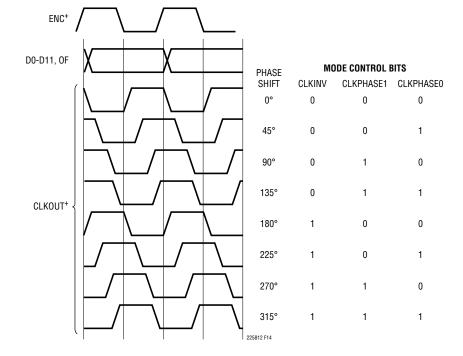

#### Phase Shifting the Output Clock

In full-rate CMOS mode the data output bits normally change at the same time as the falling edge of CLKOUT<sup>+</sup>, so the rising edge of CLKOUT<sup>+</sup> can be used to latch the output data. In double data rate CMOS and LVDS modes the data output bits normally change at the same time as the falling and rising edges of CLKOUT<sup>+</sup>. To allow adequate setup-and-hold time when latching the data, the CLKOUT<sup>+</sup> signal may need to be phase shifted relative to the data output bits. Most FPGAs have this feature; this is generally the best place to adjust the timing.

The LTC2258-12/LTC2257-12/LTC2256-12 can also phase shift the CLKOUT<sup>+</sup>/CLKOUT<sup>-</sup> signals by serially programming mode control register A2. The output clock can be shifted by 0°, 45°, 90° or 135°. To use the phase shifting feature the clock duty cycle stabilizer must be turned on. Another control register bit can invert the polarity of CLKOUT<sup>+</sup> and CLKOUT<sup>-</sup>, independently of the phase shift. The combination of these two features enables phase shifts of 45° up to 315° (Figure 14).

#### DATA FORMAT

Table 1 shows the relationship between the analog input voltage, the digital data output bits and the overflow bit. By default the output data format is offset binary. The 2's complement format can be selected by serially programming mode control register A4.

| A <sub>IN</sub> + – A <sub>IN</sub> <sup>–</sup><br>(2V RANGE) | OF | D11-D0<br>(offset binary) | D11-D0<br>(2's COMPLEMENT) |

|----------------------------------------------------------------|----|---------------------------|----------------------------|

| >+1.000000V                                                    | 1  | 1111 1111 1111            | 0111 1111 1111             |

| +0.999512V                                                     | 0  | 1111 1111 1111            | 0111 1111 1111             |

| +0.999024V                                                     | 0  | 1111 1111 1110            | 0111 1111 1110             |

| +0.000488V                                                     | 0  | 1000 0000 0001            | 0000 0000 0001             |

| V000000V                                                       | 0  | 1000 0000 0000            | 0000 0000 0000             |

| -0.000488V                                                     | 0  | 0111 1111 1111            | 1111 1111 1111             |

| -0.000976V                                                     | 0  | 0111 1111 1110            | 1111 1111 1110             |

| -0.999512V                                                     | 0  | 0000 0000 0001            | 1000 0000 0001             |

| -1.000000V                                                     | 0  | 0000 0000 0000            | 1000 0000 0000             |

| ≤ <b>-1</b> .000000V                                           | 1  | 0000 0000 0000            | 1000 0000 0000             |

Table 1. Output Codes vs Input Voltage

Figure 14. Phase Shifting CLKOUT

225812fc

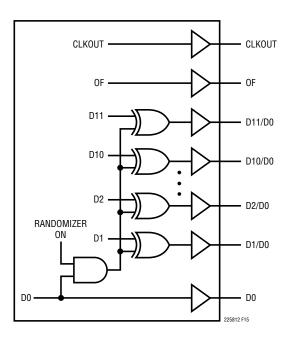

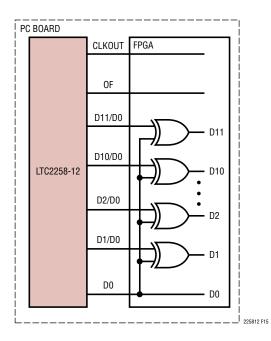

#### **Digital Output Randomizer**

Interference from the A/D digital outputs is sometimes unavoidable. Digital interference may be from capacitive or inductive coupling or coupling through the ground plane. Even a tiny coupling factor can cause unwanted tones in the ADC output spectrum. By randomizing the digital output before it is transmitted off chip, these unwanted tones can be randomized which reduces the unwanted tone amplitude.

The digital output is "randomized" by applying an exclusive-OR logic operation between the LSB and all other data output bits. To decode, the reverse operation is applied—an exclusive-OR operation is applied between the LSB and all other bits. The LSB, OF and CLKOUT outputs are not affected. The output randomizer is enabled by serially programming mode control register A4.

#### **Alternate Bit Polarity**

Another feature that reduces digital feedback on the circuit board is the alternate bit polarity mode. When this mode is enabled, all of the odd bits (D1, D3, D5, D7, D9, D11) are inverted before the output buffers. The even bits (D0, D2, D4, D6, D8, D10), OF and CLKOUT are not affected. This can reduce digital currents in the circuit board ground plane and reduce digital noise, particularly for very small analog input signals.

When there is a very small signal at the input of the A/D that is centered around midscale, the digital outputs toggle between mostly 1s and mostly 0s. This simultaneous switching of most of the bits will cause large currents in the ground plane. By inverting every other bit, the alternate bit polarity mode makes half of the bits transition high while half of the bits transition low. To first order, this cancels current flow in the ground plane, reducing the digital noise.

Figure 15. Functional Equivalent of Digital Output Randomizer

Figure 16. Unrandomizing a Randomized Digital Output Signal

The digital output is decoded at the receiver by inverting the odd bits (D1, D3, D5, D7, D9, D11). The alternate bit polarity mode is independent of the digital output randomizer—either, both or neither function can be on at the same time. When alternate bit polarity mode is on, the data format is offset binary and the 2's complement control bit has no effect. The alternate bit polarity mode is enabled by serially programming mode control register A4.

#### **Digital Output Test Patterns**

To allow in-circuit testing of the digital interface to the A/D, there are several test modes that force the A/D data outputs (OF, D11-D0) to known values:

All 1s: All outputs are 1

All Os: All outputs are 0

Alternating: Outputs change from all 1s to all 0s on alternating samples

Checkerboard: Outputs change from 1010101010101 to 0101010101010 on alternating samples

The digital output test patterns are enabled by serially programming mode control register A4. When enabled, the test patterns override all other formatting modes: 2's complement, randomizer, alternate-bit-polarity.

#### **Output Disable**

The digital outputs may be disabled by serially programming mode control register A3. All digital outputs including OF and CLKOUT are disabled. The high impedance disabled state is intended for long periods of inactivity—it is too slow to multiplex a data bus between multiple converters at full speed.

#### **Sleep and Nap Modes**

The A/D may be placed in sleep or nap modes to conserve power. In sleep mode the entire A/D converter is powered down, resulting in 0.5mW power consumption. Sleep mode is enabled by mode control register A1 (serial programming mode), or by SDI (parallel programming mode). The amount of time required to recover from sleep mode depends on the size of the bypass capacitors on  $V_{\text{REF}}$ , REFH, and REFL. For the suggested values in Figure 8, the A/D will stabilize after 2ms.

In nap mode the A/D core is powered down while the internal reference circuits stay active, allowing faster wake-up than from sleep mode. Recovering from nap mode requires at least 100 clock cycles. If the application demands very accurate DC settling then an additional 50µs should be allowed so the on-chip references can settle from the slight temperature shift caused by the change in supply current as the A/D leaves nap mode. Nap mode is enabled by mode control register A1 in the serial programming mode.

### **DEVICE PROGRAMMING MODES**

The operating modes of the LTC2258-12/LTC2257-12/ LTC2256-12 can be programmed by either a parallel interface or a simple serial interface. The serial interface has more flexibility and can program all available modes. The parallel interface is more limited and can only program some of the more commonly used modes.

#### **Parallel Programming Mode**

To use the parallel programming mode, PAR/SER should be tied to  $V_{DD}$ . The  $\overline{CS}$ , SCK and SDI pins are binary logic inputs that set certain operating modes. These pins can be tied to  $V_{DD}$  or ground, or driven by 1.8V, 2.5V or 3.3V CMOS logic. Table 2 shows the modes set by  $\overline{CS}$ , SCK and SDI.

| Table 2. Parallel Programming | <b>Mode Control Bits</b> | $(PAR/\overline{SER} = V_{DD})$ |

|-------------------------------|--------------------------|---------------------------------|

|-------------------------------|--------------------------|---------------------------------|

| PIN | DESCRIPTION                                                                             |

|-----|-----------------------------------------------------------------------------------------|

| CS  | Clock Duty Cycle Stabilizer Control Bit                                                 |

|     | 0 = Clock Duty Cycle Stabilizer Off                                                     |

|     | 1 = Clock Duty Cycle Stabilizer On                                                      |

| SCK | Digital Output Mode Control Bit                                                         |

|     | 0 = Full-Rate CMOS Output Mode                                                          |

|     | 1 = Double Data Rate LVDS Output Mode<br>(3.5mA LVDS Current, Internal Termination Off) |

| SDI | Power Down Control Bit                                                                  |

|     | 0 = Normal Operation                                                                    |

|     | 1 = Sleep Mode                                                                          |

#### Serial Programming Mode

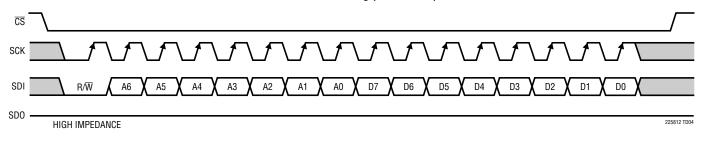

To use the serial programming mode, PAR/SER should be tied to ground. The  $\overline{CS}$ , SCK, SDI and SDO pins become a serial interface that program the A/D mode control registers. Data is written to a register with a 16-bit serial word. Data can also be read back from a register to verify its contents.

Serial data transfer starts when  $\overline{CS}$  is taken low. The data on the SDI pin is latched at the first 16 rising edges of SCK. Any SCK rising edges after the first 16 are ignored. The data transfer ends when  $\overline{CS}$  is taken high again.

The first bit of the 16-bit input word is the R/W bit. The next seven bits are the address of the register (A6:A0). The final eight bits are the register data (D7:D0).

If the  $R/\overline{W}$  bit is low, the serial data (D7:D0) will be written to the register set by the address bits (A6:A0). If the  $R/\overline{W}$  bit is high, data in the register set by the address bits (A6:A0) will be read back on the SDO pin (see the timing

diagrams). During a read back command the register is not updated and data on SDI is ignored.

The SDO pin is an open-drain output that pulls to ground with a 200 $\Omega$  impedance. If register data is read back through SDO, an external 2k pull-up resistor is required. If serial data is only written and read back is not needed, then SDO can be left floating and no pull-up resistor is needed.

Table 3 shows a map of the mode control registers.

#### **Software Reset**

If serial programming is used, the mode control registers should be programmed as soon as possible after the power supplies turn on and are stable. The first serial command must be a software reset which will reset all register data bits to logic 0. To perform a software reset, bit D7 in the reset register is written with a logic 1. After the reset SPI write command is complete, bit D7 is automatically set back to zero.

## Table 3. Serial Programming Mode Register Map REGISTER A0: RESET REGISTER (ADDRESS 00h)

| D7    | D6             | D5                  | D4                  | D3                    | D2                    | D1                   | D0           |

|-------|----------------|---------------------|---------------------|-----------------------|-----------------------|----------------------|--------------|

| RESET | Х              | Х                   | Х                   | Х                     | Х                     | Х                    | Х            |

| 7     | RESET          | Software Reset Bit  |                     |                       |                       |                      |              |

|       | Write Comman   |                     | Registers are Reset | to 00h. This Bit is A | Automatically Set Bad | ck to Zero at the En | d of the SPI |

|       | The Reset Regi | ster is Write Only. |                     |                       |                       |                      |              |

| D7       | D6                                                                                                   | D5      | D4              | D3 | D2 | D1      | D0                                    |

|----------|------------------------------------------------------------------------------------------------------|---------|-----------------|----|----|---------|---------------------------------------|

| Х        | Х                                                                                                    | Х       | Х               | Х  | Х  | PWR0FF1 | PWR0FF0                               |

| Bits 7-2 | Unused, Don't Care                                                                                   | e Bits. | •               | •  |    |         | · · · · · · · · · · · · · · · · · · · |

| Bits 1-0 | <b>PWROFF1:PWROFF0</b><br>00 = Normal Operation<br>01 = Nap Mode<br>10 = Not Used<br>11 = Sleep Mode |         | wn Control Bits |    |    |         |                                       |

#### **REGISTER A2: TIMING REGISTER (ADDRESS 02h)**

| D7       | D6                                                                                                                                    | D5 | D4  | D3     | D2        | D1        | D0  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|----|-----|--------|-----------|-----------|-----|--|--|

| Х        | Х                                                                                                                                     | Х  | Х   | CLKINV | CLKPHASE1 | CLKPHASE0 | DCS |  |  |

| Bits 7-4 | Unused, Don't Care Bits.                                                                                                              |    |     |        |           |           |     |  |  |

| Bit 3    | <b>CLKINV</b> Output Clock Invert Bit<br>0 = Normal CLKOUT Polarity (As Shown in the Timing Diagrams)<br>1 = Inverted CLKOUT Polarity |    |     |        |           |           |     |  |  |

| Bits 2-1 |                                                                                                                                       |    |     |        |           |           |     |  |  |

| Bit 0    | DCS Clock Du<br>0 = Clock Duty Cyc<br>1 = Clock Duty Cyc                                                                              |    | Bit |        |           |           |     |  |  |

#### **REGISTER A3: OUTPUT MODE REGISTER (ADDRESS 03h)**

| D7       | D6                                                                                                                                                                                                                                                                                                                                                              | D5     | D4     | D3       | D2     | D1       | D0       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|----------|--------|----------|----------|

| Х        | ILVDS2                                                                                                                                                                                                                                                                                                                                                          | ILVDS1 | ILVDS0 | TERMON   | OUTOFF | OUTMODE1 | OUTMODE0 |

| Bit 7    | Unused, Don't Car                                                                                                                                                                                                                                                                                                                                               | e Bit. |        |          |        |          |          |

| Bits 6-4 | ILVDS2:ILVDS0 LVDS Output Current Bits<br>000 = 3.5mA LVDS Output Driver Current<br>001 = 4.0mA LVDS Output Driver Current<br>010 = 4.5mA LVDS Output Driver Current<br>011 = Not Used<br>100 = 3.0mA LVDS Output Driver Current<br>101 = 2.5mA LVDS Output Driver Current<br>110 = 2.1mA LVDS Output Driver Current<br>111 = 1.75mA LVDS Output Driver Current |        |        |          |        |          |          |

| Bit 3    | <b>TERMON</b> LVDS Internal Termination Bit<br>0 = Internal Termination Off<br>1 = Internal Termination On. LVDS Output Driver Current is 1.6× the Current Set by ILVDS2:ILVDS0                                                                                                                                                                                 |        |        |          |        |          |          |

| Bit 2    | OUTOFF Output Disable Bit<br>0 = Digital Outputs are Enabled<br>1 = Digital Outputs are Disabled and Have High Output Impedance                                                                                                                                                                                                                                 |        |        |          |        |          |          |

| Bits 1-0 |                                                                                                                                                                                                                                                                                                                                                                 | 0      |        | rol Bits |        |          |          |

REGISTER AA: DATA FORMAT REGISTER (ADDRESS 04h)

| REGISTER A4: DATA FORMAT REGISTER (ADDRESS 0411) |                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                     |                  |          |     |      |          |  |  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------|-----|------|----------|--|--|

| D7                                               | D6                                                                                                                                                                                   | D5                                                                                                                                                                                                                                                                                                                                                                                                  | D4               | D3       | D2  | D1   | DO       |  |  |

| Х                                                | Х                                                                                                                                                                                    | OUTTEST2                                                                                                                                                                                                                                                                                                                                                                                            | OUTTEST1         | OUTTESTO | ABP | RAND | TWOSCOMP |  |  |

| Bit 7-6                                          | Unused, Don't Car                                                                                                                                                                    | Unused, Don't Care Bits.                                                                                                                                                                                                                                                                                                                                                                            |                  |          |     |      |          |  |  |

| Bits 5-3                                         | 000 = Digital Outp<br>001 = All Digital O<br>011 = All Digital O<br>101 = Checkerboa<br>111 = Alternating (                                                                          | OUTTEST2:OUTTEST0Digital Output Test Pattern Bits000 = Digital Output Test Patterns Off001 = All Digital Outputs = 0011 = All Digital Outputs = 1101 = Checkerboard Output Pattern. OF, D11-D0 Alternate Between 1 0101 0101 0101 and 0 1010 1010 1010111 = Alternating Output Pattern. OF, D11-D0 Alternate Between 0 0000 0000 0000 and 1 1111 1111 1111Note: Other Bit Combinations are not Used |                  |          |     |      |          |  |  |

| Bit 2                                            | <b>ABP</b> Alt<br>0 = Alternate Bit Pe<br>1 = Alternate Bit Pe                                                                                                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                   | Node Control Bit |          |     |      |          |  |  |

| Bit 1                                            | 0 = Data Output Ra                                                                                                                                                                   | ta Output Randomiz<br>andomizer Mode Of<br>andomizer Mode Or                                                                                                                                                                                                                                                                                                                                        | f                | t        |     |      |          |  |  |

| Bit 0                                            | <b>TWOSCOMP</b> Two's Complement Mode Control Bit<br>0 = Offset Binary Data Format<br>1 = Two's Complement Data Format<br>Note: ABP = 1 forces the output format to be Offset Binary |                                                                                                                                                                                                                                                                                                                                                                                                     |                  |          |     |      |          |  |  |

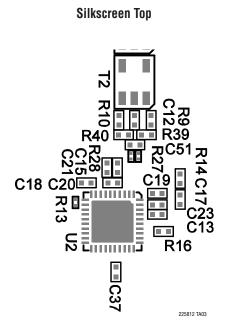

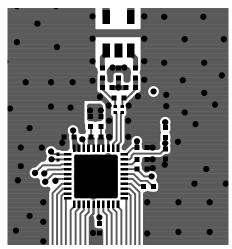

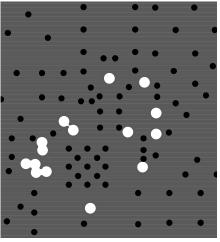

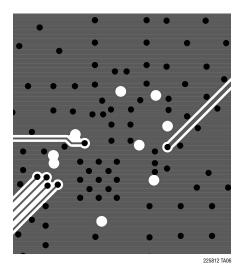

#### **GROUNDING AND BYPASSING**

The LTC2258-12/LTC2257-12/LTC2256-12 requires a printed circuit board with a clean unbroken ground plane. A multilayer board with an internal ground plane is recommended. Layout for the printed circuit board should ensure that digital and analog signal lines are separated as much as possible. In particular, care should be taken not to run any digital track alongside an analog signal track or underneath the ADC.