# Dual Channel 550mA 1MHz Synchronous Step-Up DC/DC Converter

# **FEATURES**

- Two Independent Step-Up Converters

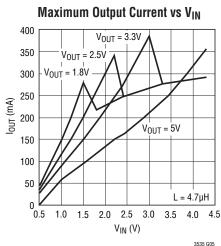

- Each Channel Delivers 3.3V at 100mA from a Single Alkaline/NiMH Cell or 3.3V at 200mA from Two Cells

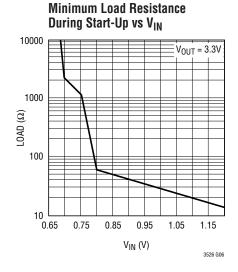

- V<sub>IN</sub> Start-Up Voltage: 680mV

- 1.5V to 5.25V V<sub>OUT</sub> Range

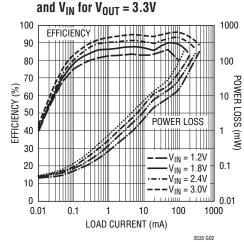

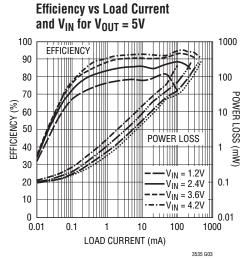

- Up to 94% Efficiency

- Output Disconnect

- 1MHz Fixed Frequency Operation

- V<sub>IN</sub> > V<sub>OUT</sub> Operation

- Integrated Soft-Start

- Current Mode Control with Internal Compensation

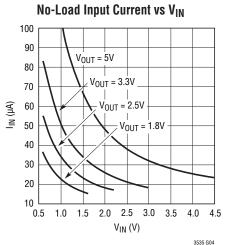

- Burst Mode® Operation with 9µA I<sub>O</sub> Each Channel

- Internal Synchronous Rectifier

- Logic Controlled Shutdown (I<sub>O</sub> < 1µA)</p>

- Anti-Ring Control

- Low Profile (3mm × 3mm × 0.75mm) 12-Lead DFN Package

### **APPLICATIONS**

- Medical Instruments

- Noise Canceling Headphones

- Energy Harvesting

- Bluetooth Headsets

# DESCRIPTION

The LTC®3535 is a dual channel, synchronous, fixed frequency step-up DC/DC converter with output disconnect. Extended battery life in single AA/AAA powered products is realized with a 680mV start-up voltage and operation down to 500mV once started.

A switching frequency of 1MHz minimizes solution footprint by allowing the use of tiny, low profile inductors and ceramic capacitors. The current mode PWM design is internally compensated, reducing external parts count. The LTC3535 features Burst Mode operation at light load conditions allowing it to maintain high efficiency over a wide range of load. Anti-ring circuitry reduces EMI by damping the inductor in discontinuous mode. Additional features include a low shutdown current of under  $1\mu A$  and thermal shutdown.

The LTC3535 is housed in a 3mm  $\times$  3mm  $\times$  0.75mm DFN package.

7, LT, LTC, LTM, Linear Technology, Burst Mode and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

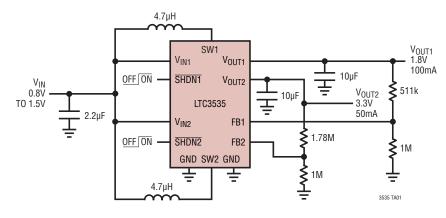

# TYPICAL APPLICATION

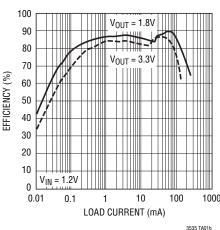

## **Efficiency vs Load Current**

# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| V <sub>IN1</sub> , V <sub>IN2</sub> VoltageSW1, SW2 Voltage | 0.3V to 6V    |

|-------------------------------------------------------------|---------------|

| , 0                                                         |               |

| DC                                                          | 0.3V to 6V    |

| Pulsed <100ns                                               | 0.3V to 7V    |

| SHDN1, SHDN2, FB1, FB2 Voltage                              | 0.3V to 6V    |

| V <sub>OUT1</sub> , V <sub>OUT2</sub>                       | 0.3V to 6V    |

| Operating Temperature Range                                 |               |

| (Notes 2, 5)                                                | 40°C to 85°C  |

| Junction Temperature                                        | 125°C         |

| Storage Temperature Range                                   | 65°C to 150°C |

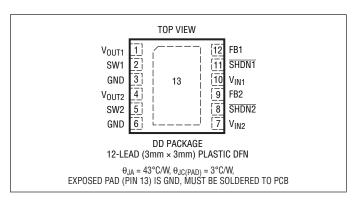

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|------------------|--------------|---------------------------------|-------------------|

| LTC3535EDD#PBF   | LTC3535EDD#TRPBF | LDWV         | 12-Lead (3mm × 3mm) Plastic DFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** (For each channel) The $\bullet$ denotes the specifications which apply over the specified operating temperature range of $-40^{\circ}$ C to 85°C, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{IN} = 1.2V$ , $V_{OUT} = 3.3V$ unless otherwise noted.

| PARAMETER                               | CONDITIONS                                                               |   | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------|--------------------------------------------------------------------------|---|-------|-------|-------|-------|

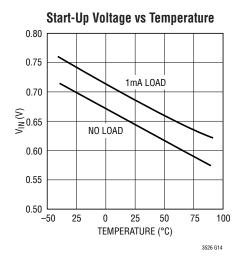

| Minimum Start-Up Input Voltage          | $I_{LOAD} = 1 mA$                                                        |   |       | 0.68  | 8.0   | V     |

| Input Voltage Range                     | After Start-Up. (Minimum Voltage is Load Dependent)                      | • | 0.5   |       | 5     | V     |

| Output Voltage Adjust Range             |                                                                          | • | 1.5   |       | 5.25  | V     |

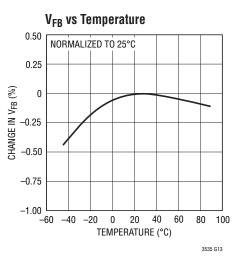

| Feedback Pin Voltage                    |                                                                          | • | 1.165 | 1.195 | 1.225 | V     |

| Feedback Pin Input Current              | V <sub>FB</sub> = 1.30V                                                  |   |       | 1     | 50    | nA    |

| Quiescent Current—Shutdown              | $V_{\overline{SHDN}}$ = 0V, Not Including Switch Leakage, $V_{OUT}$ = 0V |   |       | 0.01  | 1     | μА    |

| Quiescent Current—Active                | Measured on V <sub>OUT</sub> , Non-Switching                             |   |       | 250   | 500   | μΑ    |

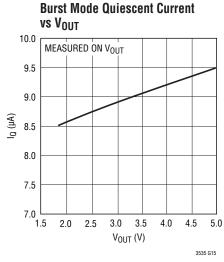

| Quiescent Current—Burst                 | Measured on V <sub>OUT</sub> , FB > 1.230V                               |   |       | 9     | 18    | μА    |

| N-Channel MOSFET Switch Leakage Current | $V_{SW} = 5V$                                                            |   |       | 0.1   | 5     | μА    |

| P-Channel MOSFET Switch Leakage Current | $V_{SW} = 5V$ , $V_{OUT} = 0V$                                           |   |       | 0.1   | 10    | μА    |

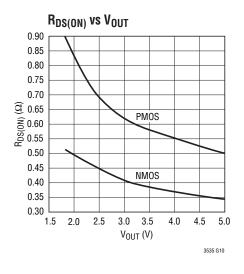

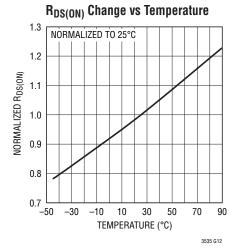

| N-Channel MOSFET Switch On Resistance   | $V_{OUT} = 3.3V$                                                         |   |       | 0.4   |       | Ω     |

| P-Channel MOSFET Switch On Resistance   | $V_{OUT} = 3.3V$                                                         |   |       | 0.6   |       | Ω     |

| N-Channel MOSFET Current Limit          |                                                                          | • | 550   | 750   |       | mA    |

| Current Limit Delay to Output           | (Note 3)                                                                 |   |       | 60    |       | ns    |

| Maximum Duty Cycle                      | V <sub>FB</sub> = 1.15V                                                  | • | 87    | 90    |       | %     |

# **ELECTRICAL CHARACTERISTICS** (For each channel) The $\bullet$ denotes the specifications which apply over the specified operating temperature range of $-40^{\circ}$ C to 85°C, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{IN} = 1.2$ V, $V_{OUT} = 3.3$ V unless otherwise noted.

| PARAMETER                   | CONDITIONS             |   | MIN  | TYP | MAX  | UNITS |

|-----------------------------|------------------------|---|------|-----|------|-------|

| Minimum Duty Cycle          | V <sub>FB</sub> = 1.3V | • |      |     | 0    | %     |

| Switching Frequency         |                        | • | 0.75 | 1   | 1.25 | MHz   |

| SHDN Pin Input High Voltage |                        |   | 0.8  |     |      | V     |

| SHDN Pin Input Low Voltage  |                        |   |      |     | 0.3  | V     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3535 is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:** Specification is guaranteed by design and not 100% tested in production.

**Note 4:** Current measurements are made when the output is not switching.

**Note 5:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may result in device degradation or failure.

**Note 6:** Failure to solder the exposed backside of the package to the PC board ground plane will result in a thermal resistance much higher than 43°C/W.

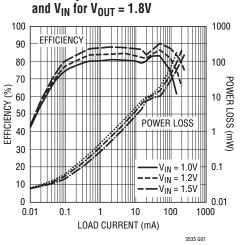

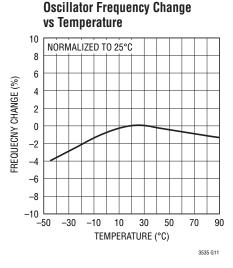

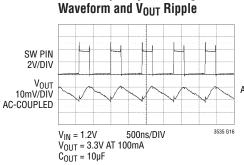

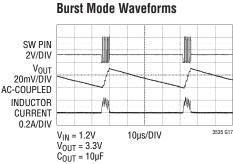

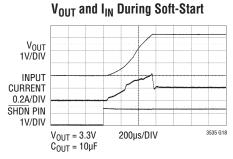

# TYPICAL PERFORMANCE CHARACTERISTICS (Each Channel) $T_A = 25$ °C, unless otherwise noted.

**Efficiency vs Load Current**

**Efficiency vs Load Current**

# TYPICAL PERFORMANCE CHARACTERISTICS (Each Channel) TA = 25°C, unless otherwise noted.

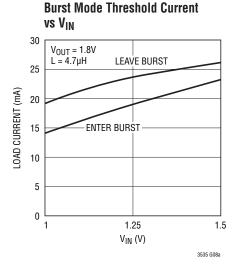

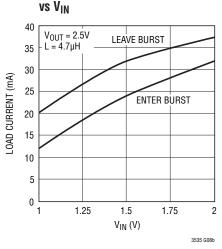

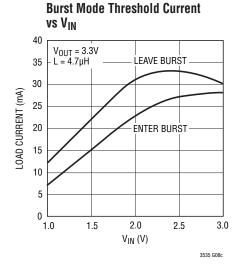

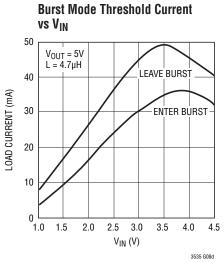

**Burst Mode Threshold Current**

# TYPICAL PERFORMANCE CHARACTERISTICS (Each Channel) $T_A = 25$ °C, unless otherwise noted.

**Fixed Frequency Switching**

# TYPICAL PERFORMANCE CHARACTERISTICS (Each Channel) $T_A = 25$ °C, unless otherwise noted.

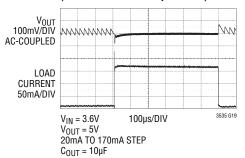

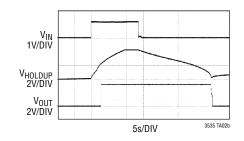

Load Step Response (from Burst Mode Operation)

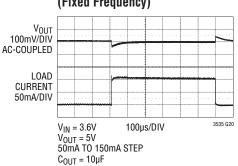

#### Load Step Response (Fixed Frequency)

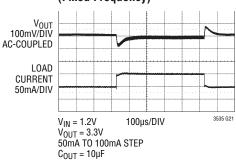

Load Step Response (Fixed Frequency)

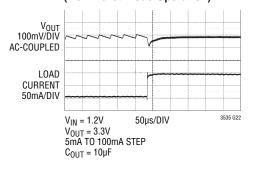

Load Step Response (from Burst Mode Operation)

# PIN FUNCTIONS

$V_{OUT1}$  (Pin 1): Output Voltage Sense and Drain of the Internal Synchronous Rectifier for Channel 1. PCB trace length from  $V_{OUT1}$  to the output filter capacitor (4.7μF minimum) should be as short and wide as possible.

**SW1 (Pin 2):** Switch Pin for Channel 1. Connect inductor between SW1 and  $V_{IN1}$ . Keep PCB trace lengths as short and wide as possible to reduce EMI. If the inductor current falls to zero, or  $\overline{SHDN1}$  is low, an internal anti-ringing switch is connected from SW1 to  $V_{IN1}$  to minimize EMI.

**GND** (Pins 3, 6, Exposed Pad Pin 13): Signal and Power Ground. Provide a short direct PCB path between GND and the (–) side of the input and output capacitors. The exposed pad must be soldered to the PCB ground plane. It serves as another ground connection and as a means of conducting heat away from the die.

$V_{OUT2}$  (Pin 4): Output Voltage Sense and Drain of the Internal Synchronous Rectifier for Channel 2. PCB trace length from  $V_{OUT2}$  to the output filter capacitor (4.7 $\mu$ F minimum) should be as short and wide as possible.

**SW2 (Pin 5):** Switch Pin for Channel 2. Connect inductor between SW2 and  $V_{IN2}$ . Keep PCB trace lengths as short and wide as possible to reduce EMI. If the inductor current falls to zero, or  $\overline{SHDN2}$  is low, an internal anti-ringing switch is connected from SW2 to  $V_{IN2}$  to minimize EMI.

$V_{IN2}$  (Pin 7): Battery Input Voltage for Channel 2. Connect a minimum of  $1\mu F$  ceramic decoupling capacitor from this pin to ground.

**SHDN2** (Pin 8): Logic Controlled Shutdown Input for Channel 2. There is an internal  $4M\Omega$  pull-down on this pin.

SHDN = High: Normal operation.

SHDN = Low: Shutdown, quiescent current < 1µA.

**FB2** (**Pin 9**): Feedback Input to the  $g_m$  Error Amplifier of Channel 2. Connect resistor divider tap to this pin. The output voltage can be adjusted from 1.5V to 5.25V by:  $V_{OUT} = 1.195V \times [1 + (R4/R3)]$

$V_{IN1}$  (Pin 10): Battery Input Voltage for Channel 1. Connect a minimum of  $1\mu F$  ceramic decoupling capacitor from this pin to ground.

**SHDN1** (**Pin 11**): Logic Controlled Shutdown Input for Channel 1. There is an internal  $4M\Omega$  pull-down on this pin.

SHDN = High: Normal operation.

$\overline{SHDN}$  = Low: Shutdown, quiescent current < 1 $\mu$ A.

**FB1 (Pin 12):** Feedback Input to the  $g_m$  Error Amplifier of Channel 1. Connect resistor divider tap to this pin. The output voltage can be adjusted from 1.5V to 5.25V by:  $V_{OUT} = 1.195V \times [1 + (R2/R1)]$ .

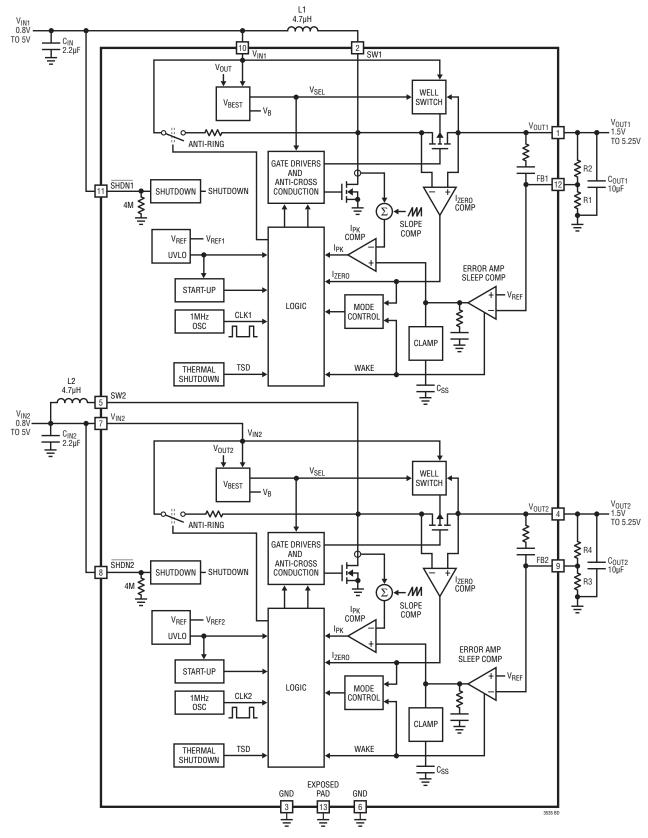

# **BLOCK DIAGRAM**

# **OPERATION** (Refer to Block Diagram)

The LTC3535 is a dual channel 1MHz synchronous boost converter housed in a 12-lead 3mm × 3mm DFN package. Each channel is identical and fully independent. They can operate from the same source, or from different voltage sources.

In addition, their output voltages can be tied together to allow operation of a single output from two different input sources. However, note that the two channels are not designed to current share, so if both input voltages are present either one may be supplying the load.

The following description of operation applies to each channel. Note that references to  $V_{\text{IN}}$  or  $V_{\text{OUT}}$  apply to the corresponding channel.

With a guaranteed ability to start up and operate from inputs less than 0.8V, each channel features fixed frequency, current mode PWM control for exceptional line and load regulation. The current mode architecture with adaptive slope compensation provides excellent transient load response, requiring minimal output filtering. Internal soft-start and internal loop compensation simplifies the design process while minimizing the number of external components.

With its low  $R_{DS(ON)}$  and low gate charge internal N-channel MOSFET switch and P-channel MOSFET synchronous rectifier, the LTC3535 achieves high efficiency over a wide range of load currents. Burst Mode operation maintains high efficiency at very light loads, reducing the quiescent current to just  $9\mu A$  per channel. Operation can be best understood by referring to the Block Diagram.

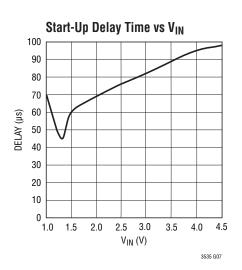

#### LOW VOLTAGE START-UP

The LTC3535 includes an independent start-up oscillator designed to start up at an input voltage of 0.68V (typical). Soft-start and inrush current limiting are provided during start-up, as well as normal mode.

When either  $V_{\text{IN}}$  or  $V_{\text{OUT}}$  for a given channel exceeds 1.3V typical, the channel enters normal operating mode. When

the output voltage exceeds the input by 0.24V, the channel powers itself from  $V_{OUT}$  instead of  $V_{IN}$ . At this point the internal circuitry has no dependency on the  $V_{IN}$  input voltage, eliminating the requirement for a large input capacitor. The input voltage can drop as low as 0.5V. The limiting factor for the application becomes the availability of the power source to supply sufficient energy to the output at low voltages, and maximum duty cycle, which is clamped at 90% typical. Note that at low input voltages, small voltage drops due to series resistance become critical, and greatly limit the power delivery capability of the converter.

#### LOW NOISE FIXED FREQUENCY OPERATION

#### **Soft-Start**

The LTC3535 contains internal circuitry to provide softstart operation. The soft-start circuitry slowly ramps the peak inductor current from zero to its peak value of 750mA (typical) in approximately 0.5ms, allowing start-up into heavy loads. The soft-start circuitry is reset in the event of a shutdown command or a thermal shutdown.

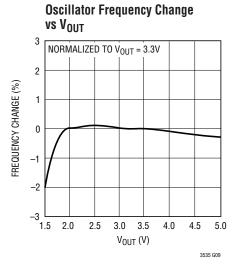

#### Oscillator

An internal oscillator (independent for each channel) sets the switching frequency to 1MHz.

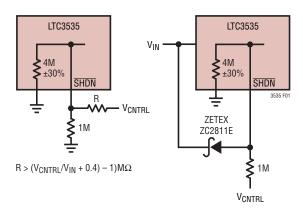

#### Shutdown

Shutdown is accomplished by pulling the  $\overline{SHDN}$  pin below 0.3V and enabled by pulling the  $\overline{SHDN}$  pin above 0.8V. Although  $\overline{SHDN}$  can be driven above  $V_{IN}$  or  $V_{OUT}$  (up to the absolute maximum rating) without damage, the LTC3535 has a proprietary test mode that may be engaged if  $\overline{SHDN}$  is held in the range of 0.5V to 1V higher than the greater of  $V_{IN}$  or  $V_{OUT}$ . If the test mode is engaged, normal PWM switching action is interrupted, which can cause undesirable operation in some applications. Therefore, in applications where  $\overline{SHDN}$  may be driven above  $V_{IN}$ , a resistor divider or other means must be employed to keep the  $\overline{SHDN}$  voltage below ( $V_{IN}$  + 0.4V) to prevent the possibility of

# **OPERATION** (Refer to Block Diagram)

the test mode being engaged. Refer to Figure 1 for two possible implementations.

Figure 1. Recommended Shutdown Circuits When Driving SHDN Above V<sub>IN</sub>

#### **Error Amplifier**

The positive input of the transconductance error amplifier is internally connected to the 1.195V reference and the negative input is connected to FB. Clamps limit the minimum and maximum error amp output voltage for improved large-signal transient response. Power converter control loop compensation is provided internally. An external resistive voltage divider from  $V_{OUT}$  to ground programs the output voltage via FB from 1.5V to 5.25V.

$$V_{OUT} = 1.195V \cdot \left(1 + \frac{R2}{R1}\right)$$

### **Current Sensing**

Lossless current sensing converts the peak current signal of the N-channel MOSFET switch into a voltage that is summed with the internal slope compensation. The summed signal is compared to the error amplifier output to provide a peak current control command for the PWM.

#### **Current Limit**

The current limit comparator shuts off the N-channel MOSFET switch once its threshold is reached. The current limit comparator delay to output is typically 60ns. Peak switch current is limited to approximately 750mA,

independent of input or output voltage, unless  $V_{OUT}$  falls below 0.7V, in which case the current limit is cut in half.

#### **Zero Current Comparator**

The zero current comparator monitors the inductor current to the output and shuts off the synchronous rectifier when this current reduces to approximately 30mA. This prevents the inductor current from reversing in polarity, improving efficiency at light loads.

#### **Synchronous Rectifier**

To control inrush current and to prevent the inductor current from running away when  $V_{OUT}$  is close to  $V_{IN}$ , the P-channel MOSFET synchronous rectifier is only enabled when  $V_{OUT} > (V_{IN} + 0.24V)$ .

#### **Anti-Ringing Control**

The anti-ring circuit connects a resistor across the inductor to prevent high frequency ringing on the SW pin during discontinuous current mode operation. Although the ringing of the resonant circuit formed by L and  $C_{SW}$  (capacitance on SW pin) is low energy, it can cause EMI radiation.

#### **Output Disconnect**

The LTC3535 is designed to allow true output disconnect by eliminating body diode conduction of the internal P-channel MOSFET rectifier. This allows for  $V_{OUT}$  to go to zero volts during shutdown, drawing no current from the input source. It also allows for inrush current limiting at turn-on, minimizing surge currents seen by the input supply. Note that to obtain the advantages of output disconnect, there must not be an external Schottky diode connected between SW and  $V_{OUT}$ . The output disconnect feature also allows  $V_{OUT}$  to be pulled high, without any reverse current into a battery connected to  $V_{\rm IN}$ .

#### Thermal Shutdown

If the die temperature exceeds 160°C, the LTC3535 will go into thermal shutdown. All switches will be off and the soft-start capacitor will be discharged. The device will be enabled again when the die temperature drops by about 15°C.

### **OPERATION** (Refer to Block Diagram)

#### **Burst Mode OPERATION**

Each channel of the LTC3535 will enter Burst Mode operation at light load current and return to fixed frequency PWM mode when the load increases. Refer to the Typical Performance Characteristics to see the output load Burst Mode threshold current vs  $V_{\text{IN}}$ . The load current at which Burst Mode operation is entered can be changed by adjusting the inductor value. Raising the inductor value will lower the load current at which Burst Mode operation is entered.

In Burst Mode operation, the LTC3535 still switches at a fixed frequency of 1MHz, using the same error amplifier and loop compensation for peak current mode control. This control method eliminates any output transient when switching between modes. In Burst Mode operation, energy is delivered to the output until it reaches the nominal regulation value, then the LTC3535 transitions to sleep mode where the outputs are off and the LTC3535 consumes only  $9\mu A$  of quiescent current from  $V_{OUT}$  for

each channel. When the output voltage droops slightly, switching resumes. This maximizes efficiency at very light loads by minimizing switching and quiescent losses. Burst Mode output voltage ripple, which is typically 1% peak-to-peak, can be reduced by using more output capacitance (10 $\mu$ F or greater), or with a small capacitor (10 $\mu$ F to 50 $\mu$ F) connected between V<sub>OLIT</sub> and FB.

As the load current increases, the LTC3535 will automatically leave Burst Mode operation. Note that larger output capacitor values may cause this transition to occur at lighter loads. Once the LTC3535 has left Burst Mode operation and returned to normal operation, it will remain there until the output load is reduced below the burst threshold current.

Burst Mode operation is inhibited during start-up and soft-start and until  $V_{OLIT}$  is at least 0.24V greater than  $V_{IN}$ .

Note that each channel can enter or leave Burst Mode operation independent of the other channel.

# APPLICATIONS INFORMATION

#### $V_{IN} > V_{OUT}$ OPERATION

The LTC3535 will maintain voltage regulation even when the input voltage is above the desired output voltage. Note that the efficiency is much lower in this mode, and the maximum output current capability will be less. Refer to the Typical Performance Characteristics.

#### SHORT-CIRCUIT PROTECTION

The LTC3535 output disconnect feature allows output short circuit while maintaining a maximum internally set current limit. To reduce power dissipation under short-circuit conditions, the peak switch current limit is reduced to 400mA (typical per channel).

#### SCHOTTKY DIODE

Although not recommended, adding a Schottky diode from SW to  $V_{OUT}$  will improve efficiency by about 2%. Note that this defeats the output disconnect and short-circuit protection features.

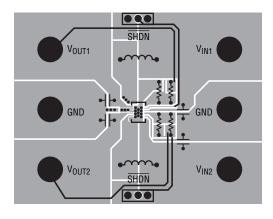

#### **PCB LAYOUT GUIDELINES**

The high speed operation of the LTC3535 demands careful attention to board layout. A careless layout will result in reduced performance. Figure 2 shows the recommended component placement. A large ground pin copper area will help to lower the die temperature. A multilayer board with a separate ground plane is ideal, but not absolutely necessary.

Figure 2. Recommended Component Placement

# APPLICATIONS INFORMATION

#### COMPONENT SELECTION

#### **Inductor Selection**

The LTC3535 can utilize small surface mount chip inductors due to their fast 1MHz switching frequency. Inductor values between 3.3 $\mu$ H and 6.8 $\mu$ H are suitable for most applications. Larger values of inductance will allow slightly greater output current capability (and lower the Burst Mode threshold) by reducing the inductor ripple current. Increasing the inductance above 10 $\mu$ H will increase component size while providing little improvement in output current capability.

The minimum inductance value is given by:

$$L > \frac{V_{IN(MIN)} \bullet (V_{OUT(MAX)} - V_{IN(MIN)})}{Ripple \bullet V_{OUT(MAX)}}$$

where:

Ripple = Allowable inductor current ripple (amps peakpeak)

$V_{IN(MIN)}$  = Minimum input voltage

$V_{OUT(MAX)} = Maximum output voltage$

The inductor current ripple is typically set for 20% to 40% of the maximum inductor current. High frequency ferrite core inductor materials reduce frequency dependent power losses compared to cheaper powdered iron types, improving efficiency. The inductor should have low ESR (series resistance of the windings) to reduce the  $I^2R$  power losses, and must be able to support the peak inductor current without saturating. Molded chokes and some chip inductors usually do not have enough core area to support the peak inductor current of 750mA seen on the LTC3535. To minimize radiated noise, use a shielded inductor. See Table 1 for suggested components and suppliers.

**Table 1. Recommended Inductors**

| VENDOR                                           | PART/STYLE                                                                               |

|--------------------------------------------------|------------------------------------------------------------------------------------------|

| Coilcraft<br>(847) 639-6400<br>www.coilcraft.com | LP04815<br>LPS4012, LPS4018<br>MSS5131<br>MSS4020<br>M0S6020<br>ME3220<br>DS1605, D01608 |

| Coiltronics<br>www.cooperet.com                  | SD10, SD12, SD14, SD18, SD20,<br>SD52, SD3114, SD3118                                    |

| FDK<br>(408) 432-8331<br>www.fdk.com             | MIP3226D4R7M, MIP3226D3R3M<br>MIPF2520D4R7<br>MIPWT3226D3R0                              |

| Murata<br>(714) 852-2001<br>www.murata.com       | LQH43C<br>LQH32C (-53 series)<br>301015                                                  |

| Sumida<br>(847) 956-0666<br>www.sumida.com       | CDRH5D18<br>CDRH2D14<br>CDRH3D16<br>CDRH3D11<br>CR43<br>CMD4D06-4R7MC<br>CMD4D06-3R3MC   |

| Taiyo-Yuden<br>www.t-yuden.com                   | NP03SB<br>NR3015T<br>NR3012T                                                             |

| TDK<br>(847) 803-6100<br>www.component.tdk.com   | VLP<br>VLF, VLCF                                                                         |

| Toko<br>(408) 432-8282<br>www.tokoam.com         | D412C<br>D518LC<br>D52LC<br>D62LCB                                                       |

| Wurth<br>(201) 785-8800<br>www.we-online.com     | WE-TPC type S, M                                                                         |

### **Output and Input Capacitor Selection**

Low ESR (equivalent series resistance) capacitors should be used to minimize the output voltage ripple. Multilayer ceramic capacitors are an excellent choice as they have extremely low ESR and are available in small footprints. A

### APPLICATIONS INFORMATION

4.7µF to 10µF output capacitor is sufficient for most applications. Larger values may be used to obtain extremely low output voltage ripple and improve transient response. X5R and X7R dielectric materials are preferred for their ability to maintain capacitance over wide voltage and temperature ranges. Y5V types should not be used.

The internal loop compensation of the LTC3535 is designed to be stable with output capacitor values of  $4.7\mu F$  or greater (without the need for any external series resistor). Although ceramic capacitors are recommended, low ESR tantalum capacitors may be used as well.

A small ceramic capacitor in parallel with a larger tantalum capacitor may be used in demanding applications that have large load transients. Another method of improving the transient response is to add a small feed-forward capacitor across the top resistor of the feedback divider (from  $V_{OUT}$  to FB). A typical value of 22pF will generally suffice.

Low ESR input capacitors reduce input switching noise and reduce the peak current drawn from the battery. It follows that ceramic capacitors are also a good choice for input decoupling and should be located as close as possible to the device. A 2.2µF input capacitor is sufficient for most applications, although larger values may be used without limitations. Table 2 shows a list of several ceramic capacitor manufacturers. Consult the manufacturers directly for detailed information on their selection of ceramic capacitors.

**Table 2. Capacitor Vendor Information**

| SUPPLIER    | PHONE          | WEBSITE               |  |

|-------------|----------------|-----------------------|--|

| AVX         | (803) 448-9411 | www.avxcorp.com       |  |

| Murata      | (714) 852-2001 | www.murata.com        |  |

| Taiyo-Yuden | (408) 573-4150 | www.t-yuden.com       |  |

| TDK         | (847) 803-6100 | www.component.tdk.com |  |

| Samsung     | (408) 544-5200 | www.sem.samsung.com   |  |

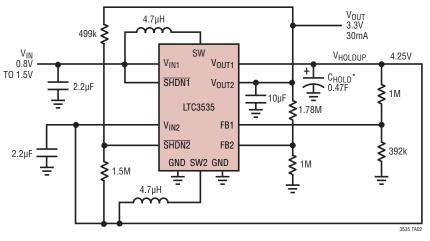

### TYPICAL APPLICATION

Single Cell to 3.3V Converter with 20 Seconds of Holdup with 30mA Load

\*POWERSTOR PA-5R0H474-R

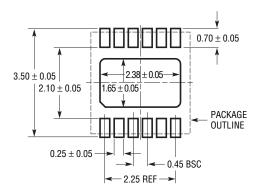

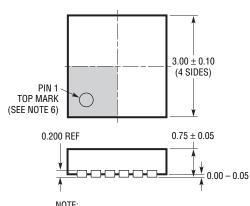

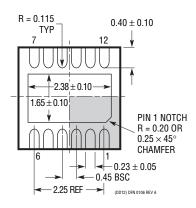

# PACKAGE DESCRIPTION

#### DC Package 12-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1725 Rev A)

#### **RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS APPLY SOLDER MASK TO AREAS THAT ARE NOT SOLDERED

BOTTOM VIEW—EXPOSED PAD

#### NOTE:

- 1. DRAWING IS NOT A JEDEC PACKAGE OUTLINE

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD AND TIE BARS SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# **REVISION HISTORY**

| REV | DATE | DESCRIPTION                                                        | PAGE NUMBER |

|-----|------|--------------------------------------------------------------------|-------------|

| Α   | 9/10 | Updated Applications section                                       | 1           |

|     |      | Updated Pin Configuration                                          | 2           |

|     |      | Updated Note 6                                                     | 3           |

|     |      | Updated Pins 3, 6 and 13 text                                      | 7           |

|     |      | Updated Shutdown section                                           | 9, 10       |

|     |      | Corrected C <sub>HOLD</sub> capacitor value in Typical Application | 13          |

|     |      | Added new Typical Application and Updated Related Parts table      | 16          |