NOLOGY Programmable Hex Voltage Supervisor with EEPROM and Comparator Outputs

#### **FEATURES**

- Supervises 6 Power Supplies

- I<sup>2</sup>C Adjustable UV and OV Trip Points

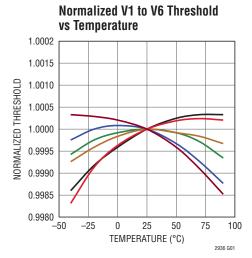

- Guaranteed Threshold Accuracy: ±1% (Maximum)

- I<sup>2</sup>C/SMBus Interface

- Internal EEPROM

- Six Comparator Outputs

- Fast Comparator Response Time: 7.5μs

- 256 Programmable Thresholds per Channel

- Three Range Settings per Channel

- Two General Purpose Inputs

- Three General Purpose Inputs/Outputs

- Programmable Output Delays

- Can Be Powered from 3.3V, or 3.4V to 13.9V

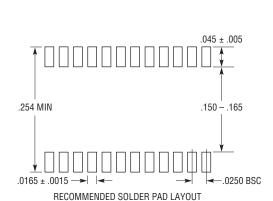

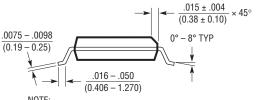

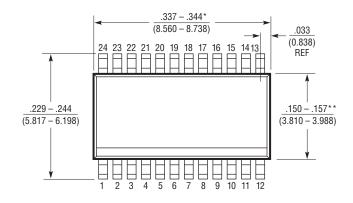

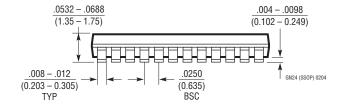

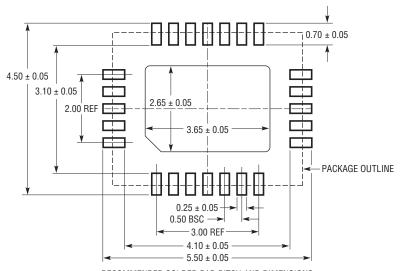

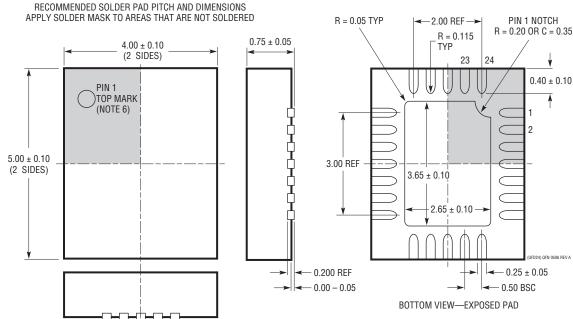

- 24-Pin 4mm × 5mm QFN and SSOP Packages

# **APPLICATIONS**

- High Availability Computer Systems

- Network Servers

- Telecom Equipment

- Data Storage Systems

# DESCRIPTION

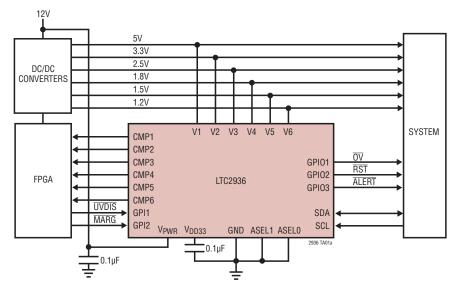

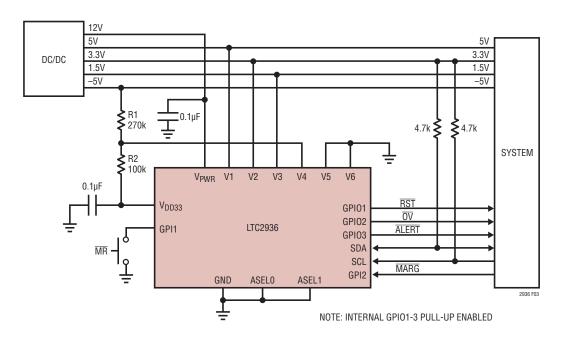

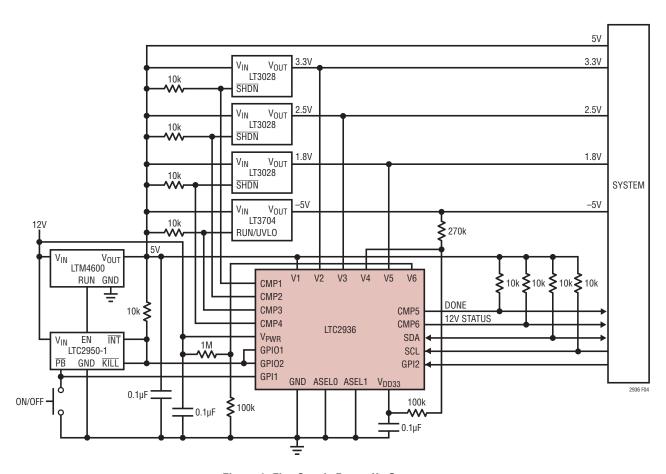

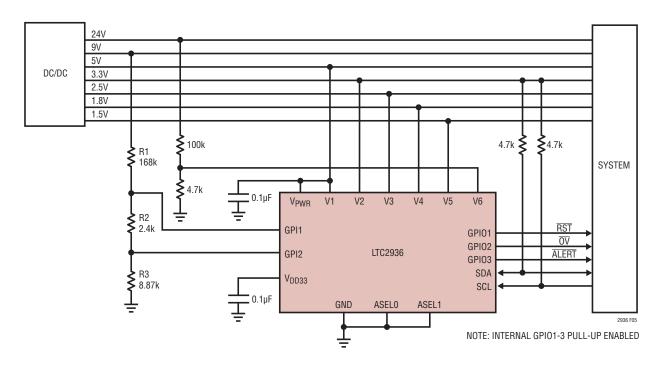

The LTC®2936 is an EEPROM configurable voltage supervisor which can simultaneously monitor up to six power supply voltage inputs. Each voltage detector offers I<sup>2</sup>C programmable overvoltage/undervoltage thresholds in various ranges and increments and a dedicated comparator output.

Two general purpose inputs (GPI) can be configured as programmable manual reset ( $\overline{MR}$ ), UV disable ( $\overline{UVDIS}$ ), margin ( $\overline{MARG}$ ), Write Protect ( $\overline{WP}$ ) or auxiliary comparator (AUXC) inputs. Three general purpose pins (GPIO) can be configured for input or output operation. When configured as an input, a GPIO pin can be mapped to any other GPIO configured as output. The GPIO pins can also be configured as  $\overline{ALERT}$  or fault outputs. Faults can be configured with programmable delay-on-release times. Output type and polarity are also configurable.

Status and history registers log faults and can be polled via the  $I^2C$  interface. A fault snapshot is also backed up in internal EEPROM. All parameters are programmable via the  $I^2C$  interface. Configuration EEPROM supports autonomous operation without additional software.

# TYPICAL APPLICATION

# V1 to V6 Error vs Temperature 1 (%) 0.5 -1 -50 -25 0 25 50 75 100 TEMPERATURE (°C) 2936 TAD11b

# **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2)

| Supply Voltages               |                           |

|-------------------------------|---------------------------|

| V <sub>PWR</sub>              | 0.3V to 14V               |

| V <sub>DD33</sub>             | 0.3V to 3.6V              |

| Digital Input/Output Voltages |                           |

| SDA, SCL, GPI1, GPI2          | 0.3V to 6V                |

| GPI01-GPI03, CMP1-CMP6        | 0.3V to 14V               |

| ASEL0, ASEL1                  | 0.3V to V <sub>DD33</sub> |

| Analog Voltages               |                           |

| V1-V6                         | 0.3V to 6V                |

| Operating Temperature Range       |                |

|-----------------------------------|----------------|

| LTC2936C                          | 0°C to 70°C    |

| LTC2936I                          | 40°C to 85°C   |

| Storage Temperature Range         | 65°C to 150°C* |

| Maximum Junction Temperature      | 125°C*         |

| Lead Temperature Range (Soldering | g, 10 sec)     |

| SSOP Package                      | 300°C          |

|                                   |                |

<sup>\*</sup> See Applications Information section for detailed EEPROM derating information for junction temperatures in excess of 85°C.

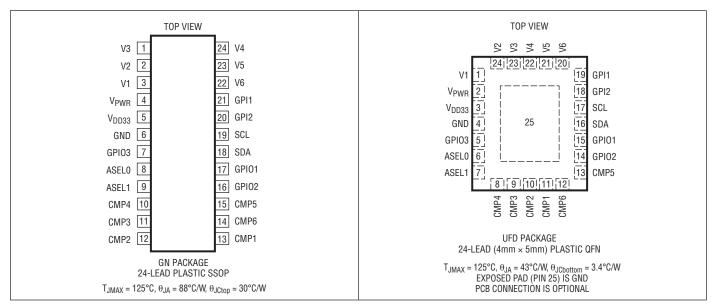

# PIN CONFIGURATION

# ORDER INFORMATION http://www.linear.com/product/LTC2936#orderinfo

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC2936CGN#PBF   | LTC2936CGN#TRPBF  | LTC2936GN     | 24-Lead Plastic SSOP            | 0°C to 70°C       |

| LTC2936IGN#PBF   | LTC2936IGN#TRPBF  | LTC2936GN     | 24-Lead Plastic SSOP            | -40°C to 85°C     |

| LTC2936CUFD#PBF  | LTC2936CUFD#TRPBF | 2936          | 24-Lead (4mm × 5mm) Plastic QFN | 0°C to 70°C       |

| LTC2936IUFD#PBF  | LTC2936IUFD#TRPBF | 2936          | 24-Lead (4mm × 5mm) Plastic QFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ and $V_{PWR} = 12V$ (Note 2).

| SYMBOL              | PARAMETER                                  | CONDITIONS                                                                                                                                                                                                   |   | MIN             | TYP           | MAX                                | UNITS                   |

|---------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------|---------------|------------------------------------|-------------------------|

| Power Supp          | ly Characteristics                         |                                                                                                                                                                                                              |   |                 |               |                                    |                         |

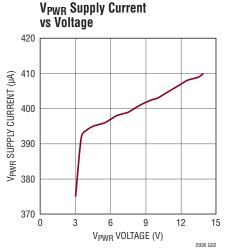

| V <sub>PWR</sub>    | V <sub>PWR</sub> Supply Voltage Range      |                                                                                                                                                                                                              | • | 3.4             |               | 13.9                               | V                       |

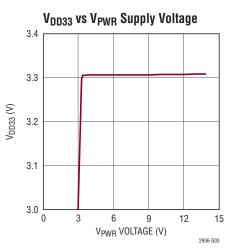

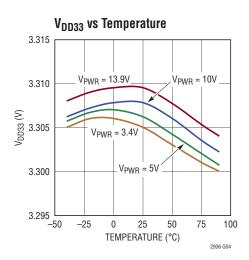

| $V_{DD33}$          | V <sub>DD33</sub> Regulator Output Voltage | I <sub>VDD33</sub> = -1mA                                                                                                                                                                                    | • | 3.23            | 3.3           | 3.37                               | V                       |

| $I_{DD}$            | V <sub>DD33</sub> Regulator Current Limit  | $V_{DD33} = 0V$                                                                                                                                                                                              | • | -10             |               |                                    | mA                      |

| V <sub>DDEXT</sub>  | V <sub>DD33</sub> Supply Voltage Range     | $V_{DD33} = V_{PWR}$                                                                                                                                                                                         | • | 3.13            | 3.3           | 3.47                               | V                       |

| I <sub>PWR</sub>    | V <sub>PWR</sub> Supply Current            | Writing to EEPROM                                                                                                                                                                                            | • |                 |               | 0.7<br>1.5                         | mA<br>mA                |

| I <sub>VDDEXT</sub> | V <sub>DDEXT</sub> Supply Current          | Writing to EEPROM                                                                                                                                                                                            | • |                 |               | 0.7<br>1.5                         | mA<br>mA                |

| Voltage Sup         | ervisor Characteristics                    |                                                                                                                                                                                                              |   | ,               |               |                                    |                         |

| V <sub>RANGE</sub>  | V <i>n</i> Monitoring Range                | Precision Range<br>Low Range<br>Medium Range                                                                                                                                                                 | • | 0.2<br>0.5<br>1 |               | 1.2<br>3<br>5.8                    | V                       |

| V <sub>STEP</sub>   | Vn Threshold Programming Step (LSB)        | Precision Range<br>Low Range<br>Medium Range                                                                                                                                                                 |   |                 | 4<br>10<br>20 |                                    | mV                      |

| V <sub>ERR</sub>    | V <i>n</i> Threshold Accuracy              | Precision Range, $0.6V < Vn < 1.2V$<br>Precision Range, $0.2V < Vn < 0.6V$<br>Low Range, $1.5V < Vn < 3V$<br>Low Range, $0.5V < Vn < 1.5V$<br>Medium Range, $3V < Vn < 5.8V$<br>Medium Range, $1V < Vn < 3V$ | • |                 |               | ±1<br>±6<br>±1<br>±15<br>±1<br>±30 | %<br>mV<br>%<br>mV<br>% |

| R <sub>IN</sub>     | Vn Input Impedance                         | Low and Medium Range and High Range                                                                                                                                                                          | • | 400             | 600           |                                    | kΩ                      |

| I <sub>IN</sub>     | Vn Input Current                           | Precision Range, 1.2V Input                                                                                                                                                                                  | • |                 |               | ±10                                | nA                      |

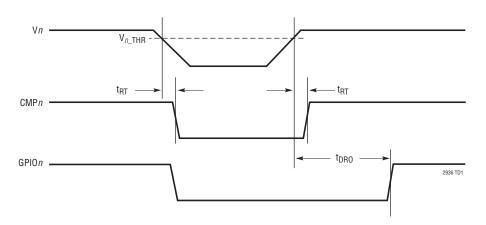

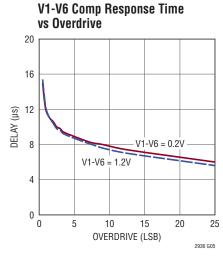

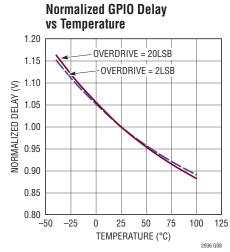

| t <sub>RT</sub>     | Vn Comparator Response Time                | 2 LSB of Overdrive<br>20 LSB of Overdrive                                                                                                                                                                    | • |                 | 15<br>7.5     | 10                                 | μs<br>μs                |

| Manual Res          | et Characteristics                         |                                                                                                                                                                                                              |   |                 |               |                                    | -                       |

| t <sub>MRI</sub>    | Input Pulse Width                          | Active Low                                                                                                                                                                                                   | • | 5               |               |                                    | μs                      |

| t <sub>MRR</sub>    | Glitch Rejection                           |                                                                                                                                                                                                              |   |                 | 1             |                                    | μs                      |

| CMPn Outpu          | ut Characteristics                         |                                                                                                                                                                                                              | · |                 |               |                                    |                         |

| V <sub>OL</sub>     | Low Output Voltage                         | I <sub>SINK</sub> = 3mA                                                                                                                                                                                      | • |                 |               | 0.4                                | V                       |

| I <sub>LEAK</sub>   | Leakage Current                            | V <sub>CMP</sub> = 13.9V                                                                                                                                                                                     | • |                 |               | ±2                                 | μА                      |

| I <sub>PU</sub>     | Internal Pull-up Current                   | V <sub>CMP</sub> = 2V                                                                                                                                                                                        | • | -5              | -15           | -30                                | μА                      |

| GPIn Charac         | cteristics                                 |                                                                                                                                                                                                              |   |                 |               |                                    |                         |

| V <sub>ITH</sub>    | Input Threshold Voltage                    |                                                                                                                                                                                                              | • | 0.6             | 1             | 1.4                                | V                       |

| I <sub>LEAK</sub>   | Leakage Current                            | V <sub>GPI</sub> = 6V                                                                                                                                                                                        | • |                 |               | ±2                                 | μА                      |

| I <sub>PU</sub>     | Internal Pull-up Current                   | V <sub>GPI</sub> = 2V                                                                                                                                                                                        | • | -5              | -15           | -30                                | μА                      |

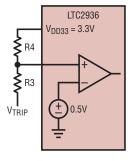

| <b>Auxiliary Co</b> | mparator Characteristics                   |                                                                                                                                                                                                              |   |                 |               |                                    |                         |

| V <sub>ACIN</sub>   | Input Threshold Voltage                    |                                                                                                                                                                                                              | • | 0.49            | 0.5           | 0.51                               | V                       |

| I <sub>ACIN</sub>   | Input Current                              | Input Voltage = 0.5V                                                                                                                                                                                         | • |                 |               | ±10                                | nA                      |

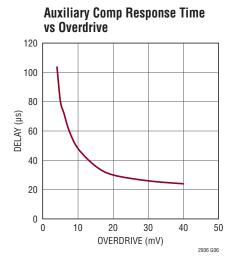

| t <sub>ACRT</sub>   | Response time                              | 40mV Overdrive                                                                                                                                                                                               |   |                 | 25            |                                    | μs                      |

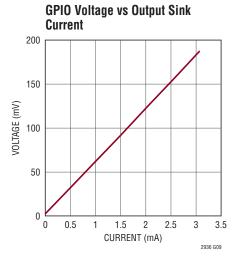

| GPIOn Char          | acteristics                                |                                                                                                                                                                                                              |   |                 |               |                                    |                         |

| V <sub>OL</sub>     | Low Output Voltage                         | I <sub>SINK</sub> = 3mA                                                                                                                                                                                      | • |                 |               | 0.4                                | V                       |

| V <sub>ITH</sub>    | Input Threshold Voltage                    |                                                                                                                                                                                                              | • | 0.6             | 1             | 1.4                                | V                       |

| I <sub>LEAK</sub>   | Leakage Current                            | V <sub>GPI0</sub> = 13.9V                                                                                                                                                                                    | • |                 |               | ±2                                 | μА                      |

| I <sub>PU</sub>     | Internal Pull-up Current                   | V <sub>GPIO</sub> = 2V                                                                                                                                                                                       | • | -5              | -15           | -30                                | μА                      |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ and $V_{PWR} = 12V$ (Note 2).

| SYMBOL                   | PARAMETER                                                                                                     | CONDITIONS                                         |   | MIN            | TYP            | MAX                     | UNITS    |

|--------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---|----------------|----------------|-------------------------|----------|

| t <sub>DRO</sub>         | Programmable Output Delay-On-Release GPIO1_DELAY_ON_RELEASE,                                                  | 000b<br>001b                                       | • | 1              | 0.001<br>1.6   | 0.050<br>2.1            | ms<br>ms |

|                          | GPIO2_DELAY_ON_RELEASE and                                                                                    | 010b                                               |   | 4.5            | 6.4            | 8.3                     | ms       |

|                          | GPIO3_DELAY_ON_RELEASE                                                                                        | 011b                                               | • | 17.9           | 25.6           | 33.3                    | ms       |

|                          |                                                                                                               | 100b<br>  101b                                     | • | 35.8           | 51.2           | 66.6                    | ms       |

|                          |                                                                                                               | 110b                                               |   | 143.3<br>286.6 | 204.8<br>409.6 | 266.3<br>532.6          | ms<br>ms |

|                          |                                                                                                               | 111b                                               | • | 1146           | 1638           | 2130                    | ms       |

| EEPROM Cha               | racteristics                                                                                                  |                                                    |   |                |                |                         |          |

| Retention                | Retention (Notes 5, 6)                                                                                        |                                                    | • | 10             |                |                         | Years    |

| Endurance                | Endurance (Notes 5, 6)                                                                                        |                                                    | • | 10,000         |                |                         | Cycles   |

| t <sub>EEFS</sub>        | Fault Storage Time (Note 4)                                                                                   | Backup Fault Storage Operation                     |   |                | 10             |                         | ms       |

| t <sub>EEPR</sub>        | Programming Time                                                                                              | I <sup>2</sup> C NAK's During STORE_USER Operation |   |                | 100            |                         | ms       |

| t <sub>EERU</sub>        | Restore Time                                                                                                  | RESTORE_USER Command                               |   |                | 1              |                         | ms       |

| <b>Digital Inputs</b>    | SCL, SDA                                                                                                      |                                                    |   |                |                |                         |          |

| V <sub>IH</sub>          | High Level Input Voltage                                                                                      |                                                    | • | 2.0            |                |                         | V        |

| $V_{IL}$                 | Low Level Input Voltage                                                                                       |                                                    | • |                |                | 0.8                     | V        |

| V <sub>HYST</sub>        | Input Hysteresis (Note 4)                                                                                     |                                                    |   |                | 40             |                         | mV       |

| I <sub>LEAK</sub>        | Input Leakage Current                                                                                         | SCL, SDA = GND to 5.5V                             | • | -1             |                | 1                       | μΑ       |

| Digital Output           | SDA                                                                                                           |                                                    |   |                |                |                         |          |

| $V_{0L}$                 | Digital Output Low Voltage                                                                                    | I <sub>SINK</sub> = 3mA                            | • |                |                | 0.4                     | V        |

| <b>Digital Inputs</b>    | ASELO, ASEL1                                                                                                  |                                                    |   |                |                |                         |          |

| V <sub>IH</sub>          | Input High Threshold Voltage                                                                                  |                                                    | • |                |                | V <sub>DD33</sub> – 0.4 | V        |

| $V_{IL}$                 | Input Low Threshold Voltage                                                                                   |                                                    | • | 0.4            |                |                         | V        |

| I <sub>IH,IL</sub>       | High, Low Input Current                                                                                       | $ASELn = 0, V_{DD33}$                              | • | -20            |                | 20                      | μA       |

| I <sub>FLOAT</sub>       | High Z Input Current                                                                                          | 0.5V< ASEL <i>n</i> < V <sub>DD33</sub> - 0.5V     | • | -10            |                | 10                      | μA       |

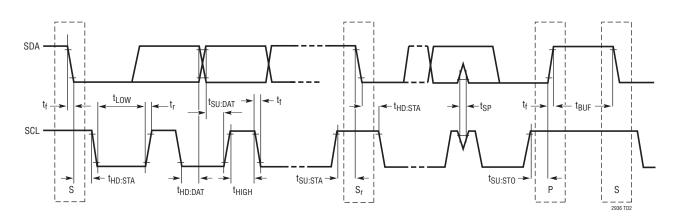

| Serial Bus Tir           | ning Characteristics (Note 3)                                                                                 |                                                    |   |                |                |                         |          |

| f <sub>SCL</sub>         | Serial Clock Frequency                                                                                        |                                                    | • | 10             |                | 400                     | kHz      |

| $t_{LOW}$                | Serial Clock Low Period                                                                                       |                                                    | • | 1.3            |                |                         | μs       |

| t <sub>HIGH</sub>        | Serial Clock High Period                                                                                      |                                                    | • | 0.6            |                |                         | μs       |

| t <sub>BUF</sub>         | Bus Free Time Between Stop and Start                                                                          |                                                    | • | 1.3            |                |                         | μs       |

| t <sub>HD,STA</sub>      | Start Condition Hold Time                                                                                     |                                                    | • | 600            |                |                         | ns       |

| t <sub>SU,STA</sub>      | Start Condition Setup Time                                                                                    |                                                    | • | 600            |                |                         | ns       |

| t <sub>SU,STO</sub>      | Stop Condition Setup Time                                                                                     |                                                    | • | 600            |                |                         | ns       |

| t <sub>HD,DAT</sub>      | Data Hold Time                                                                                                | LTC2936 Receiving Data                             | • | 0              |                |                         | ns       |

|                          |                                                                                                               | LTC2936 Transmitting Data                          | • | 300            |                |                         | ns       |

| t <sub>SU,DAT</sub>      | Data Setup Time                                                                                               |                                                    | • | 100            |                |                         | ns       |

| t <sub>SP</sub>          | Pulse Width of Spike Suppressed                                                                               |                                                    |   |                | 100            |                         | ns       |

| t <sub>TIMEOUT_BUS</sub> | Time Allowed to Complete Any PMBus<br>Command After Which Time SDA Will<br>Be Released and Command Terminated |                                                    |   |                | 32             |                         | ms       |

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime. The LTC2936 is tested with  $T_A = T_{CASE}$ .

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

**Note 3:** Maximum capacitive load,  $C_B$ , for SCL and SDA is 400pF. Data and clock rise time  $(t_r)$  and fall time  $(t_f)$  are:

$(20 + 0.1 \cdot C_B)$  (ns)  $< t_r < 300$ ns, and

$(20 + 0.1 \cdot C_B)$  (ns)  $< t_f < 300$ ns

$C_B$  = capacitance of one bus line in pF SCL and SDA external pull-up voltage,  $V_{IO}$ , is 3V <  $V_{IO}$  < 5.5V.

Note 4: Guaranteed by design, not directly tested.

**Note 5:** EEPROM endurance and retention are guaranteed by design, characterization and correlation with statistical process controls. The minimum retention specification applies for devices whose EEPROM has been cycled less than the minimum endurance specification.

**Note 6:** EEPROM endurance and retention will be degraded when  $T_{\rm d} > 85^{\circ}{\rm C}$ .

# TIMING DIAGRAMS

#### Vn Supervisor Timing

#### I<sup>2</sup>C Timing

# TYPICAL PERFORMANCE CHARACTERISTICS

# PIN FUNCTIONS

**ASELO, ASEL1:**  $I^2C$  Bus Address Select Inputs. Can be connected to ground,  $V_{DD33}$  or can be left unconnected to select 1 out of 9 addresses.

**CMP1-CMP6:** Comparator Open-Drain Outputs. These pins assert low in response to a user-programmable combination of UV and OV conditions on the associated channels. Each output has a 15µA pull-up to V<sub>DD33</sub>.

**Exposed Pad (QFN Package Only):** Ground. The exposed pad may be left open or connected to device ground.

GND: Ground.

**GPI1**, **GPI2**: General Purpose Inputs. Configurable as one of five possibilities (no duplication):

- Manual reset ( $\overline{MR}$ ) input, active low, 15µA pull-up to  $V_{DD33}$

- UV disable (UVDIS), active low, 15μA pull-up to V<sub>DD33</sub>.

Outputs ignore UV faults.

- Margin (MARG), active low, 15µA pull-up to V<sub>DD33</sub>.

Outputs ignore both UV and OV faults.

- Write Protect (WP), active low, 15μA pull-up to V<sub>DD33</sub>.

I<sup>2</sup>C write commands are ignored.

- Hi-Z Auxiliary Comparator (AUXC) Input. Programmable polarity.

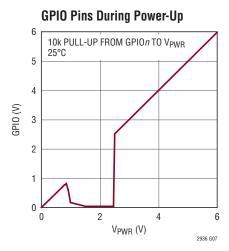

**GPIO1, GPIO2, GPIO3:** General Purpose Input/Output. Each GPIO is configurable as either input, open-drain output, or weak pull-up output. Output polarity is programmable. When configured as outputs, these pins respond to selectable UV conditions, OV conditions,  $\overline{MR}$ , auxiliary comparator output, or other input-configured GPIOn with programmable delay-on-release. These pins can also be configured as  $\overline{ALERT}$  per SMBus standard. When configured as inputs, each pin can be mapped to any other output. These pins have an optional 15µA pull-up to  $V_{DD33}$ . Unused GPIO pins should be tied to  $V_{DD33}$  or have their pull-up enabled.

**SCL:** I<sup>2</sup>C Serial Clock (400kHz Maximum). Needs external pull-up resistor.

**SDA**: I<sup>2</sup>C Serial Data. Needs external pull-up resistor.

**V1-V6:** Voltage Supervisor Input. Programmable thresholds from 0.2V to 1.2V in 4mV increments (precision range), from 0.5V to 3V in 10mV increments (low range) or from 1V to 5.8V in 20mV increments (medium range). See the Applications Information section for information on unused channels.

$V_{DD33}$ : 3.3V Internal Regulator Output. A 100nF capacitor to ground is required. The internal regulator can be disabled by connecting  $V_{PWR}$  to  $V_{DD33}$  and operating from an external 3.3V supply.

**V<sub>PWR</sub>:** Power Supply Input (Internal Regulator Input). Power supply range is 3.4V to 13.9V. Bypass this pin to ground with a 100nF (or greater) capacitor. The internal regulator can be disabled by connecting  $V_{PWR}$  to  $V_{DD33}$  and operating from an external 3.3V supply.

| PIN NAME         | PIN TYPE | PIN (SSOP) | PIN (QFN) |  |  |

|------------------|----------|------------|-----------|--|--|

| V3               | IN       | 1          | 23        |  |  |

| V2               | IN       | 2          | 24        |  |  |

| V1               | IN       | 3          | 1         |  |  |

| V <sub>PWR</sub> | IN       | 4          | 2         |  |  |

| $V_{DD33}$       | OUT/IN   | 5          | 3         |  |  |

| GND              | GND      | 6          | 4, 25     |  |  |

| GPI03            | IN/OUT   | 7          | 5         |  |  |

| ASEL0            | IN       | 8          | 6         |  |  |

| ASEL1            | IN       | 9          | 7         |  |  |

| CMP4             | OUT      | 10         | 8         |  |  |

| CMP3             | OUT      | 11         | 9         |  |  |

| CMP2             | OUT      | 12         | 10        |  |  |

| CMP1             | OUT      | 13         | 11        |  |  |

| CMP6             | OUT      | 14         | 12        |  |  |

| CMP5             | OUT      | 15         | 13        |  |  |

| GPI02            | IN/OUT   | 16         | 14        |  |  |

| GPI01            | IN/OUT   | 17         | 15        |  |  |

| SDA              | IN/OUT   | 18         | 16        |  |  |

| SCL              | IN       | 19         | 17        |  |  |

| GPI2             | IN       | 20         | 18        |  |  |

| GPI1             | IN       | 21         | 19        |  |  |

| V6               | IN       | 22         | 20        |  |  |

| V5               | IN       | 23         | 21        |  |  |

| V4               | IN       | 24         | 22        |  |  |

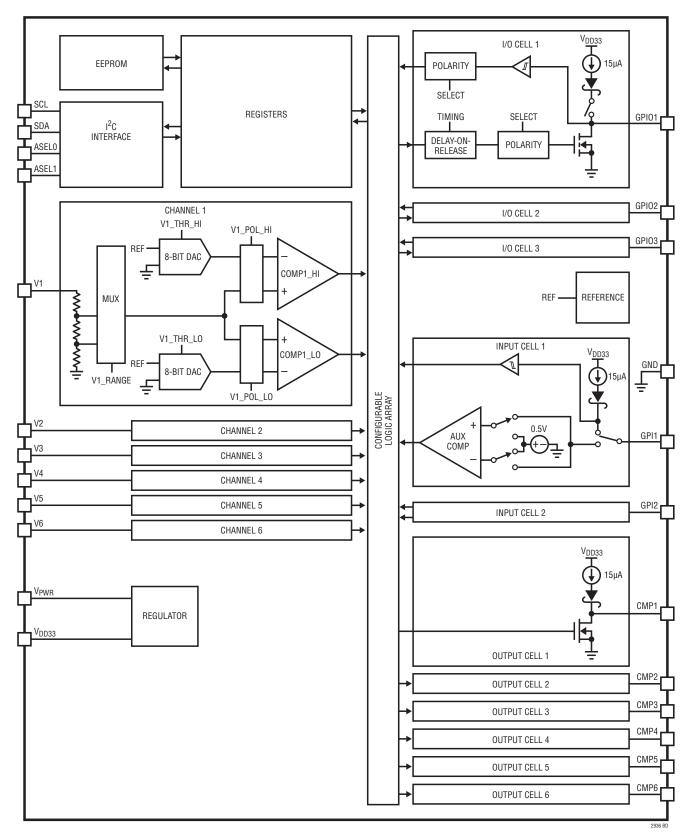

# **BLOCK DIAGRAM**

The LTC2936 can perform the following operations:

- Accept I<sup>2</sup>C bus programming commands.

- Simultaneously monitor up to six inputs with respect to I<sup>2</sup>C bus programmed fault limits and assert/de-assert the associated CMPn outputs in response to OV and/ or UV faults.

- Configure and monitor for OV/UV faults using two independent comparators per channel.

- Configure two general purpose inputs as manual reset (MR), undervoltage disable (UVDIS), margin (MARG), write protect (WP) or auxiliary comparator (AUXC) inputs.

- Configure three general purpose inputs/outputs (GPIOn) to output faults, inputs from GPIn or from other GPIOn.

- Independently select each general purpose output polarity and type (open-drain or weak pull-up).

- Independently select each general purpose output response delay-on-release (with respect to the moment its condition is internally cleared).

- Generate interrupt (ALERT) signals in response to any voltage faults, as well as the logic state of the inputs.

- Store register contents to EEPROM.

- Store voltage and timing fault history to EEPROM.

- Restore EEPROM contents into the operating memory, by I<sup>2</sup>C command and at power-up.

- Report voltage fault status and history.

- Hardware and/or software write-protect the operating memory.

#### THRESHOLD ACCURACY

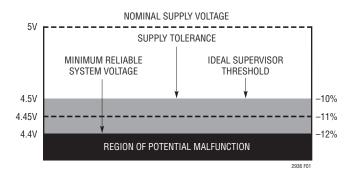

The LTC2936 ±1% threshold accuracy specification improves the reliability of the system over supervisors with wider threshold tolerances. A less accurate voltage supervisor increases the required system voltage margin. This in turn increases the probability of system malfunction.

Consider a  $5V \pm 10\%$  supply: it may vary between 4.5V and 5.5V and the circuitry powered by it must operate reliably within this band. An ideal, perfectly accurate supervisor would generate a reset at exactly 4.5V. The LTC2936 threshold varies  $\pm 1\%$  around the nominal threshold voltage, in the medium range, if the selected value is greater than 3V. The reset threshold band and the power supply tolerance bands should not overlap, in order to prevent false alarms when the power supply actually meets its specified tolerance band (see Figure 1).

$A\pm10\%$  threshold is usually set to 11% below the nominal input voltage, or 4.45V in this example. The threshold is guaranteed to be within the 4.4V to 4.5V band over temperature. To prevent malfunction, the powered system must operate reliably down to 4.4V.

Figure 1. 1% Threshold Accuracy Improves System Reliability

# I<sup>2</sup>C Serial Digital Interface

The LTC2936 communicates with a host (master) using the I<sup>2</sup>C serial bus interface. The Timing Diagram shows the timing relationship of the signals on the bus. The two bus lines, SDA and SCL, must be high when the bus is not in use. External pull-up resistors or current sources are required on these lines.

The LTC2936 is a transmit/receive slave only device. The master device must initiate data transfer on the bus by

generating SCL to allow the transfer. In the event of an OV/UV fault, the LTC2936 can be configured to assert the ALERT output low in order to notify the host.

#### **Slave Address**

The LTC2936 can respond to one of 9 addresses. By connecting the address ASEL0 and ASEL1 inputs to  $V_{DD33}$ , GND, or by floating them, the slave address is determined as shown in the following table. The LTC2936 always responds to the special addresses.

#### LTC2936 Address Look-Up Table

| ASELO         | 0    | Hi-Z | 1    | 0    | Hi-Z | 1    | 0    | Hi-Z | 1    |

|---------------|------|------|------|------|------|------|------|------|------|

| ASEL1         | 0    | 0    | 0    | Hi-Z | Hi-Z | Hi-Z | 1    | 1    | 1    |

| 7-Bit Address | 0x50 | 0x51 | 0x52 | 0x53 | 0x54 | 0x55 | 0x58 | 0x59 | 0x5A |

| 8-Bit Address | 0xA0 | 0xA2 | 0xA4 | 0xA6 | 0xA8 | 0xAA | 0xB0 | 0xB2 | 0xB4 |

#### LTC2936 Special Slave Addresses

| 7-BIT ADDRESS | 8-BIT ADDRESS | DESCRIPTION                                                                      |

|---------------|---------------|----------------------------------------------------------------------------------|

| 0x0C          | 0x19          | Alert Response Address, Independent of the ASEL pin.                             |

| 0x73          | 0xE6          | Global address to which all LTC2936's will respond. Independent of the ASEL pin. |

#### **Communication Protocols**

- S START CONDITION

- Sr REPEATED START CONDITION

- Rd READ (BIT VALUE OF 1)

- Wr WRITE (BIT VALUE OF 0)

- A ACKNOWLEDGE

- A NOT ACKNOWLEDGE

- P STOP CONDITION

- MASTER TO SLAVE

- SLAVE TO MASTER

#### **Send Byte Format**

| 1 | 7             | 1  | 1 | 8            | 1 | 1 |

|---|---------------|----|---|--------------|---|---|

| S | SLAVE ADDRESS | Wr | Α | COMMAND CODE | Α | Р |

#### Write Word Format

|   | 1 | 7             | 1 1 |   | 8            |   | 8             | 1 | 8              | 1 | 1 |   |

|---|---|---------------|-----|---|--------------|---|---------------|---|----------------|---|---|---|

| ſ | S | SLAVE ADDRESS | Wr  | Α | COMMAND CODE | Α | DATA BYTE LOW | Α | DATA BYTE HIGH | Α | Р | Ì |

#### **Read Word Format**

| 1 | 7             | 1  | 1 | 8            | 1 | 1  | 7             | 1  | 1 | 8             | 1 | 8              | 1 | 1 |          |

|---|---------------|----|---|--------------|---|----|---------------|----|---|---------------|---|----------------|---|---|----------|

| S | SLAVE ADDRESS | Wr | Α | COMMAND CODE | Α | Sr | SLAVE ADDRESS | Rd | Α | DATA BYTE LOW | Α | DATA BYTE HIGH | Ā | Р | 2936 F00 |

LINEAR

## **Register Command Set**

| COMMAND<br>FUNCTION | DESCRIPTION                                                                                                                                   | R/W/S<br>(See Note) | DATA LENGTH<br>(BITS) | COMMAND<br>BYTE | DEFAULT VALUE        |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------|----------------------|

| WRITE_PROTECT       | Contains lock key code and write lock.                                                                                                        | R/W                 | 16                    | 0x00            | 1010_1010_1010_1000b |

| GPI_CONFIG          | Configure GPI2 and GPI1 assignment, GPI0 <i>n</i> mapping and MR internal response.                                                           | R/W                 | 16                    | 0x01            | X001_0000_X000_0000b |

| GPI01_CONFIG        | Configure GPIO1 type, delay-on-release and mapping to GPIO2, GPIO3.                                                                           | R/W                 | 16                    | 0x02            | X000_0000_0010_1011b |

| GPI02_3_CONFIG      | Configure GPIO3 type, delay-on-release and mapping to GPIO1 and GPIO2. Configure GPIO2 type, delay-on-release and mapping to GPIO1 and GPIO3. | R/W                 | 16                    | 0x03            | 0010_1011_0010_1011b |

| V1_THR              | Encode high and low voltage thresholds on channel V1.                                                                                         | R/W                 | 16                    | 0x04            | 1110_0110_1011_0100b |

| V2_THR              | Encode high and low voltage thresholds on channel V2.                                                                                         | R/W                 | 16                    | 0x05            | 1000_1001_0110_1000b |

| V3_THR              | Encode high and low voltage thresholds on channel V3.                                                                                         | R/W                 | 16                    | 0x06            | 0101_1101_0100_0100b |

| V4_THR              | Encode high and low voltage thresholds on channel V4.                                                                                         | R/W                 | 16                    | 0x07            | 1001_1001_0111_0101b |

| V5_THR              | Encode high and low voltage thresholds on channel V5                                                                                          | R/W                 | 16                    | 0x08            | 0111_1000_0101_1010b |

| V6_THR              | Encode high and low voltage thresholds on channel V6.                                                                                         | R/W                 | 16                    | 0x09            | 0101_0111_0011_1111b |

| V1_CONFIG           | Encode comparator range, polarity and GPIOn mapping.                                                                                          | R/W                 | 16                    | 0x0A            | XXX0_1100_1000_1001b |

| V2_CONFIG           | Encode comparator range, polarity and GPIOn mapping.                                                                                          | R/W                 | 16                    | 0x0B            | XXX0_1100_1000_1001b |

| V3_CONFIG           | Encode comparator range, polarity and GPIOn mapping.                                                                                          | R/W                 | 16                    | 0x0C            | XXX0_1100_1000_1001b |

| V4_CONFIG           | Encode comparator range, polarity and GPIOn mapping.                                                                                          | R/W                 | 16                    | 0x0D            | XXX0_1101_1000_1001b |

| V5_CONFIG           | Encode comparator range, polarity and GPIOn mapping.                                                                                          | R/W                 | 16                    | 0x0E            | XXX0_1101_1000_1001b |

| V6_CONFIG           | Encode comparator range, polarity and GPIOn mapping.                                                                                          | R/W                 | 16                    | 0x0F            | XXX0_1101_1000_1001b |

| HISTORY_WORD        | Read the fault history. Read only.                                                                                                            | R                   | 16                    | 0x11            | NA                   |

| PADS                | Return the status of the GPI <i>n</i> , GPIO <i>n</i> and CMP <i>n</i> pins.                                                                  | R                   | 16                    | 0x1A            | NA                   |

| CLEAR_HISTORY       | Clear volatile memory history register. Write only.                                                                                           | S                   | 0                     | 0x1B            | NA                   |

| STORE_USER          | Store volatile memory to EEPROM. Write only.                                                                                                  | S                   | 0                     | 0x1C            | NA                   |

| RESTORE_USER        | Restore volatile memory from EEPROM. Write only.                                                                                              | S                   | 0                     | 0x1D            | NA                   |

| BACKUP_WORD         | Read the EEPROM backup of the first fault history.<br>Read only.                                                                              | R                   | 16                    | 0x1E            | NA                   |

| STATUS_WORD         | Read the fault status. Read only.                                                                                                             | R                   | 16                    | 0x1F            | NA                   |

Note: R = Read, W = Write, S = Send Byte.

#### **DETAILED COMMAND REGISTER DESCRIPTIONS**

# WRITE\_PROTECT (Command Byte 0x00)

The WRITE\_PROTECT command provides the ability to prevent any write operations into the volatile memory, if WRITE\_LOCK=1. KEY may be changed when WRITE\_LOCK = 0, or in the same command that sets WRITE LOCK = 1.

When locked, WRITE\_LOCK can only be written to 0 if KEY matches the existing value in memory. For effective protection against false writes, KEY should contain at least one bit set to 1.

Writes to supported commands are ignored when WRITE\_LOCK = 1 or when a GPI*n* input configured for WP is held low. All commands may be read regardless of the WRITE LOCK bit setting.

#### WRITE\_PROTECT Data Contents

| BIT(S)  | SYMBOL     | PURPOSE                                                                                                                                                                                                                                                                                                  |

|---------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15:2] | KEY        | Must match against programmed combination in order to deactivate write lock. Factory default 10_1010_1010_1010b (0x2AAA).                                                                                                                                                                                |

| b[1]    | Reserved   | Ignore                                                                                                                                                                                                                                                                                                   |

| b[0]    | WRITE_LOCK | 0: Unlocked. Writes to volatile memory are permitted. 1: Locked. Writing to volatile memory is not permitted. To unlock, set WRITE_LOCK = 0 with the appropriate key. If a GPIn input is configured for WP, and is low, then reading WRITE_PROTECT will always return WRITE_LOCK = 1. Factory default 0. |

# **GPI\_CONFIG (Command Byte 0x01)**

The GPI\_CONFIG command configures internal response to a manual reset, sets each GPI function, and optionally maps GPI pins configured as Manual Reset ( $\overline{\text{MR}}$ ) or Auxiliary Comparator (AUXC) to one or more GPIO pins.

#### **GPI\_CONFIG Data Contents**

| BIT(S)   | SYMBOL            | OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15]    | Reserved          | Ignore                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| b[14]    | GPI2_MR_RESPONSE  | Effective only if the input GPI2 is MR configured. 0: Disable CLEAR_HISTORY response. 1: Enable CLEAR_HISTORY response on falling edge of GPI2. Factory default 0.                                                                                                                                                                                                                                                                     |

| b[13:11] | GPI2_CONFIG       | 000b: Manual Reset (MR) active low, 15μA pull-up. 001b: Reserved. 010b: Margin (MARG) active low, 15μA pull-up. Overvoltage and undervoltage faults are inhibited. 011b: UV Disable (UVDIS) active low, 15μA pull-up. Undervoltage faults are inhibited. 100b: Write Protect (WP). 101b: Auxiliary Comparator (AUXC) positive input on GPI2. 110b: and 111b: Auxiliary Comparator (AUXC) negative input on GPI2. Factory default 010b. |

| b[10]    | MAP_GPI2_TO_GPI03 | 0: GPI2 input is not mapped to GPIO3. 1: GPI2 input is mapped to GPIO3 if configured as MR or AUXC. Factory default 0.                                                                                                                                                                                                                                                                                                                 |

| b[9]     | MAP_GPI2_TO_GPI02 | 0: GPI2 input is not mapped to GPI02. 1: GPI2 input is mapped to GPI02 if configured as MR or AUXC. Factory default 0.                                                                                                                                                                                                                                                                                                                 |

| b[8]     | MAP_GPI2_TO_GPI01 | 0: GPI2 input is not mapped to GPI01.   1: GPI2 input is mapped to GPI01 if configured as $\overline{\text{MR}}$ or AUXC.   Factory default 0.                                                                                                                                                                                                                                                                                         |

| b[7]     | Reserved          | Ignore                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| b[6]     | GPI1_MR_RESPONSE  | Effective only if the input GPI1 is MR configured. 0: Disable CLEAR_HISTORY response. 1: Enable CLEAR_HISTORY response on falling edge of GPI1. Factory default 0.                                                                                                                                                                                                                                                                     |

| b[5:3]   | GPI1_CONFIG       | 000b: Manual Reset (MR) active low, 15μA pull-up. 001b: Reserved. 010b: Margin (MARG) active low, 15μA pull-up. Overvoltage and undervoltage faults are inhibited. 011b: UV Disable (UVDIS) active low, 15μA pull-up. Undervoltage faults are inhibited. 100b: Write Protect (WP). 101b: Auxiliary Comparator (AUXC) positive input on GPI1. 110b: and 111b: Auxiliary Comparator (AUXC) negative input on GPI1. Factory default 000b. |

| b[2]     | MAP_GPI1_TO_GPI03 | 0: GPI1 input is not mapped to GPI03. 1: GPI1 input is mapped to GPI03 if configured as MR or AUXC. Factory default 0.                                                                                                                                                                                                                                                                                                                 |

| b[1]     | MAP_GPI1_TO_GPI02 | 0: GPI1 input is not mapped to GPI02. 1: GPI1 input is mapped to GPI02 if configured as MR or AUXC. Factory default 0.                                                                                                                                                                                                                                                                                                                 |

| b[0]     | MAP_GPI1_TO_GPI01 | 0: GPI1 input is not mapped to GPI01. 1: GPI1 input is mapped to GPI01 if configured as MR or AUXC. Factory default 0.                                                                                                                                                                                                                                                                                                                 |

# **GPIO1\_CONFIG (Command Byte 0x02)**

The GPIO1\_CONFIG command configures the GPIO1 mapping, delay-on-release time, output type, and polarity. If GPIO1\_TYPE\_AND\_POLARITY is configured as ALERT (100b or 111b), the output is latched and cleared after the

LTC2936 acknowledges the alert response address (see SMBus protocol), HISTORY\_WORD is read, or a CLEAR\_HISTORY command is received. Only one GPIOnpin should be configured as ALERT. GPIOn\_DELAY\_ON\_RELEASE does not apply to a GPIOn pin configured as ALERT.

#### WD\_GPI01\_CONFIG Data Contents

| BIT(S)  | SYMBOL                  | OPERATION                                                                                                                                                                                                                                                                                                                                                                |

|---------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15:8] | Reserved                | Ignore                                                                                                                                                                                                                                                                                                                                                                   |

| b[7]    | MAP_GPI01_T0_GPI03      | 0: GPIO1 input is not mapped to GPIO3. 1: GPIO1 input is mapped to GPIO3. Factory default 0.                                                                                                                                                                                                                                                                             |

| b[6]    | MAP_GPI01_T0_GPI02      | 0: GPIO1 input is not mapped to GPIO2. 1: GPIO1 input is mapped to GPIO2. Factory default 0.                                                                                                                                                                                                                                                                             |

| b[5:3]  | GPI01_DELAY_ON_RELEASE  | 000b: Delay selected is 0. 001b: Delay selected is 1.6ms. 010b: Delay selected is 6.4ms. 011b: Delay selected is 26ms. 100b: Delay selected is 51ms. 101b: Delay selected is 205ms. 110b: Delay selected is 410ms. 111b: Delay selected is 1.64s. Factory default 101b (205ms).                                                                                          |

| b[2:0]  | GPI01_TYPE_AND_POLARITY | 000b: Active H input. 001b: Active L input. 010b: Active H open-drain output. 011b: Active L open-drain output. 100b: Active L open-drain ALERT output. 101b: Active L open-drain Talert output. 101b: Active H, weak pull-up output. 110b: Active L, weak pull-up output. 111b: Active L, weak pull-up ALERT output. Factory default 011b (Active L open-drain output). |

# **GPI02\_3\_CONFIG (Command Byte 0x03)**

The GPIO2\_3\_CONFIG command configures GPIO2 and GPIO3 mapping, delay-on-release time, output type, and polarity. If GPIO2\_TYPE\_AND\_POLARITY is configured as ALERT (100b or 111b), or GPIO3\_TYPE\_AND\_POLARITY is configured as ALERT (100b or 111b), the output is latched,

and is cleared after the LTC2936 acknowledges the alert response address (see SMBus protocol), HISTORY\_WORD is read, or a CLEAR\_HISTORY command is received. Only one GPIOn pin should be configured as ALERT. GPIOn\_DELAY\_ON\_RELEASE does not apply to a GPIOn pin configured as ALERT.

**GPI02\_3\_CONFIG Data Contents**

| u:: :0=_0_00 | III IG Data Contonto    |                                                                                                                                                                                                                                                                                                                                 |

|--------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT(S)       | SYMBOL                  | OPERATION                                                                                                                                                                                                                                                                                                                       |

| b[15]        | MAP_GPI03_T0_GPI02      | 0: GPI03 is not mapped into GPI02. 1: GPI03 is mapped into GPI02. Factory default 0.                                                                                                                                                                                                                                            |

| b[14]        | MAP_GPI03_T0_GPI01      | 0: GPI03 is not mapped into GPI01. 1: GPI03 is mapped into GPI01. Factory default 0.                                                                                                                                                                                                                                            |

| b[13:11]     | GPI03_DELAY_ON_RELEASE  | 000b: Delay selected is 0. 001b: Delay selected is 1.6ms. 010b: Delay selected is 6.4ms. 011b: Delay selected is 26ms. 100b: Delay selected is 51ms. 101b: Delay selected is 205ms. 110b: Delay selected is 410ms. 111b: Delay selected is 1.64s. Factory default 101b (205ms).                                                 |

| b[10:8]      | GPI03_TYPE_AND_POLARITY | 000b: Active H input. 001b: Active L input. 010b: Active H open-drain output. 011b: Active L open-drain output. 100b: Active L open-drain ALERT output. 101b: Active H, weak pull-up output. 110b: Active L, weak pull-up output. 111b: Active L, weak pull-up ALERT output. Factory default 011b (Active L open-drain output). |

| b[7]         | MAP_GPI02_T0_GPI03      | 0: GPI02 is not mapped into GPI03. 1: GPI02 is mapped into GPI03. Factory default 0.                                                                                                                                                                                                                                            |

| b[6]         | MAP_GPI02_T0_GPI01      | 0: GPI02 is not mapped into GPI01. 1: GPI02 is mapped into GPI01. Factory default 0.                                                                                                                                                                                                                                            |

| b[5:3]       | GPI02_DELAY_ON_RELEASE  | 000b: Delay selected is 0. 001b: Delay selected is 1.6ms. 010b: Delay selected is 6.4ms. 011b: Delay selected is 26ms. 100b: Delay selected is 51ms. 101b: Delay selected is 205ms. 110b: Delay selected is 410ms. 111b: Delay selected is 1.64s. Factory default 101b (205ms).                                                 |

| b[2:0]       | GPI02_TYPE_AND_POLARITY | 000b: Active H input. 001b: Active L input. 010b: Active H open-drain output. 011b: Active L open-drain output. 100b: Active L open-drain ALERT output. 101b: Active H, weak pull-up output. 110b: Active L, weak pull-up output. 111b: Active L, weak pull-up ALERT output. Factory default 011b (Active L open-drain output). |

V1\_THR (Command Byte 0x04), V2\_THR (0x05), V3\_THR (0x06), V4\_THR (0x07), V5\_THR (0x08), V6\_THR (0x09)

The Vn\_THR command allows the user to specify the high and low threshold monitoring voltages on each channel.

#### Vn\_THR Data Contents Channels V1 to V6

| BIT(S)  | SYMBOL             | OPERATION                                                                                                                                                                                                                               |

|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15:8] | V <i>n_</i> THR_HI | The COMP <i>n</i> _HI threshold. See the Applications Information section. Factory default settings of 0xE6, 0x89, 0x5D, 0x99, 0x78, 0x57 correspond to 5.5V, 3.64V, 2.76V, 1.98V, 1.65V and 1.32V for channels V1 to V6, respectively. |

| b[7:0]  | Vn_THR_LO          | The COMP <i>n</i> _LO threshold. See the Applications Information section. Factory default settings of 0xB4, 0x68, 0x44, 0x75, 0x5A, 0x3F correspond to 4.5V, 2.98V, 2.26V, 1.62V 1.35V and 1.08V for channels V1 to V6, respectively.  |

V1\_CONFIG (Command Byte 0x0A), V2\_CONFIG (0x0B), V3\_CONFIG (0x0C), V4\_CONFIG (0x0D), V5\_CONFIG (0x0E), V6\_CONFIG (0x0F)

The Vn\_CONFIG command programs V1 through V6 comparator range, polarity and mapping to GPIOn and CMPn.

#### Vn\_CONFIG Data Contents Channels V1 to V6

| BIT(S)   | SYMBOL                | OPERATION                                                                                                                                                                                                                                                                                                          |

|----------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b[15:13] | Reserved              | Ignore                                                                                                                                                                                                                                                                                                             |

| b[12]    | CMP <i>n</i> _LATCH   | 0: CMP <i>n</i> output not latched. 1: CMP <i>n</i> output latched. Factory default 0.                                                                                                                                                                                                                             |

| b[11]    | MAP_COMPn_HI_TO_CMPn  | 0: High comparator not mapped to CMP <i>n</i> . 1: High comparator mapped to CMP <i>n</i> . Factory default 1.                                                                                                                                                                                                     |

| b[10]    | MAP_COMPn_LO_TO_CMPn  | 0: Low comparator not mapped to CMP <i>n</i> . 1: Low comparator mapped to CMP <i>n</i> . Factory default 1.                                                                                                                                                                                                       |

| b[9:8]   | Vn_RANGE              | 00b: Medium Range. 01b: Low Range. 10b and 11b: Precision Range. Factory defaults are 00b on V1-V3 and 01b on V4-V6.                                                                                                                                                                                               |

| b[7]     | Vn_POL_HI             | Controls polarity of COMP <i>n_</i> HI output reported by STATUS_WORD. See STATUS_WORD description for details.  0: Undervoltage. Indicates a fault when the input voltage is below V <i>n_</i> THR_HI.  1: Overvoltage. Indicates a fault when the input voltage is above V <i>n_</i> THR_HI.  Factory default 1. |

| b[6]     | Vn_POL_LO             | Controls polarity of COMP <i>n</i> _LO output reported by STATUS_WORD. See STATUS_WORD description for details.  0: Undervoltage. Indicates a fault when the input voltage is below V <i>n</i> _THR_LO.  1: Overvoltage. Indicates a fault when the input voltage is above V <i>n</i> _THR_LO. Factory default 0.  |

| b[5]     | MAP_COMPn_HI_TO_GPI03 | 0: High comparator not mapped to GPI03. 1: High comparator mapped to GPI03. Factory default 0.                                                                                                                                                                                                                     |

| b[4]     | MAP_COMPn_HI_TO_GPI02 | 0: High comparator not mapped to GPI02. 1: High comparator mapped to GPI02. Factory default 0.                                                                                                                                                                                                                     |

#### Vn\_CONFIG Data Contents Channels V1 to V6

| b[3] | MAP_COMPn_HI_TO_GPI01 | 0: High comparator not mapped to GPI01. 1: High comparator mapped to GPI01. Factory default 1. |

|------|-----------------------|------------------------------------------------------------------------------------------------|

| b[2] | MAP_COMPn_LO_TO_GPI03 | 0: Low comparator not mapped to GPI03. 1: Low comparator mapped to GPI03. Factory default 0.   |

| b[1] | MAP_COMPn_LO_TO_GPI02 | 0: Low comparator not mapped to GPI02. 1: Low comparator mapped to GPI02. Factory default 0.   |

| b[0] | MAP_COMPn_LO_TO_GPI01 | 0: Low comparator not mapped to GPI01. 1: Low comparator mapped to GPI01. Factory default 1.   |

# **HISTORY\_WORD (Command Byte 0x11)**

The HISTORY\_WORD command returns two bytes of information with a summary of the faults since power was applied or HISTORY\_WORD was last cleared. HISTORY\_WORD is located in volatile memory and is automatically updated each time a fault occurs. HISTORY\_WORD is cleared using the CLEAR\_HISTORY command.

#### **HISTORY\_WORD Data Contents**

| BIT(S)   | SYMBOL              | OPERATION                               |

|----------|---------------------|-----------------------------------------|

| b[15:13] | Reserved            | Ignore                                  |

| b[12]    | V6_HI_LATCHED_FAULT | 1: Latched V6_HI_FAULT. 0: No fault.    |

| b[11]    | V6_LO_LATCHED_FAULT | 1: Latched V6_LO_FAULT. 0: No fault.    |

| b[10]    | V5_HI_LATCHED_FAULT | 1: Latched V5_HI_FAULT. 0: No fault.    |

| b[9]     | V5_LO_LATCHED_FAULT | 1: Latched V5_LO_FAULT. 0: No fault.    |

| b[8]     | V4_HI_LATCHED_FAULT | 1: Latched V4_HI_FAULT. 0: No fault.    |

| b[7]     | V4_LO_LATCHED_FAULT | 1: Latched V4_LO_FAULT. 0: No fault.    |

| b[6]     | V3_HI_LATCHED_FAULT | 1: Latched V3_HI_FAULT. 0: No fault.    |

| b[5]     | V3_LO_LATCHED_FAULT | 1: Latched V3_LO_FAULT. 0: No fault.    |

| b[4]     | V2_HI_LATCHED_FAULT | 1: Latched V2_HI_FAULT. 0: No fault.    |

| b[3]     | V2_LO_LATCHED_FAULT | 1: Latched V2_L0_FAULT.<br>0: No fault. |

| b[2]     | V1_HI_LATCHED_FAULT | 1: Latched V1_HI_FAULT. 0: No fault.    |

| b[1]     | V1_LO_LATCHED_FAULT | 1: Latched V1_LO_FAULT. 0: No fault.    |

| b[0]     | Reserved            | Ignore                                  |

#### PADS (Command Byte 0x1A)

The PADS register returns the status of the GPIn, GPIOn and CMPn pads.

#### **PADS Data Contents**

| BIT(S)   | SYMBOL       | OPERATION                                                 |

|----------|--------------|-----------------------------------------------------------|

| b[15:11] | Reserved     | Ignore                                                    |

| b[10]    | GPI2_STATUS  | 0: GPI2 pin is logic low.<br>1: GPI2 pin is logic high.   |

| b[9]     | GPI1_STATUS  | 0: GPI1 pin is logic low.<br>1: GPI1 pin is logic high.   |

| b[8]     | GPIO3_STATUS | 0: GPI03 pin is logic low.<br>1: GPI03 pin is logic high. |

| b[7]     | GPI02_STATUS | 0: GPI02 pin is logic low.<br>1: GPI02 pin is logic high. |

| b[6]     | GPI01_STATUS | 0: GPI01 pin is logic low.<br>1: GPI01 pin is logic high. |

| b[5]     | CMP6_STATUS  | 0: CMP6 pin is logic low.<br>1: CMP6 pin is logic high.   |

| b[4]     | CMP5_STATUS  | 0: CMP5 pin is logic low.<br>1: CMP5 pin is logic high.   |

| b[3]     | CMP4_STATUS  | 0: CMP4 pin is logic low.<br>1: CMP4 pin is logic high.   |

| b[2]     | CMP3_STATUS  | 0: CMP3 pin is logic low.<br>1: CMP3 pin is logic high.   |

| b[1]     | CMP2_STATUS  | 0: CMP2 pin is logic low.<br>1: CMP2 pin is logic high.   |

| b[0]     | CMP1_STATUS  | 0: CMP1 pin is logic low.<br>1: CMP1 pin is logic high.   |

#### CLEAR\_HISTORY (Command Byte 0x1B)

The CLEAR\_HISTORY command clears all the faults logged in the volatile HISTORY\_WORD register. A manual reset performs the same operation if  $GPIn\_MR\_RESPONSE=1$ . Clearing HISTORY\_WORD does not affect the STATUS\_WORD content. Processing of the CLEAR\_HISTORY command typically takes less than 10ms, and the part will not acknowledge other  $I^2C$  operations during that time.

# STORE\_USER (Command Byte 0x1C) RESTORE\_USER (Command Byte 0x1D)

The STORE\_USER and RESTORE\_USER commands access nonvolatile EEPROM memory. Once a command is

stored in EEPROM using STORE\_USER, it will be restored to volatile operating memory with the RESTORE\_USER command or when the part powers up.

# BACKUP\_WORD (Command Byte 0x1E)

After the first fault occurs, HISTORY\_WORD is written to EEPROM for backup. Any subsequent BACKUP\_WORD write following a fault is inhibited until the CLEAR\_HISTORY command is issued. BACKUP\_WORD can be retrieved by sending a RESTORE\_USER command followed by a BACKUP\_WORD read. BACKUP\_WORD can be cleared in EEPROM by sending a CLEAR\_HISTORY command followed by a STORE\_USER command.

# STATUS\_WORD (Command Byte 0x1F)

The STATUS\_WORD command returns two bytes of information with a summary of the current faults. The STATUS\_WORD content is read directly from the comparators and is a snapshot of the current state. STATUS\_WORD

faults may be disabled by setting GPI1\_CONFIG = 010b ( $\overline{MARG}$ ), GPI1\_CONFIG = 011b ( $\overline{UVDIS}$ ), GPI2\_CONFIG = 010b ( $\overline{MARG}$ ) or GPI2\_CONFIG = 011b ( $\overline{UVDIS}$ ) and asserting the appropriate GPIn pin.

#### STATUS\_WORD Data Contents

| BIT(S)   | SYMBOL      | OPERATION                                                                                            |

|----------|-------------|------------------------------------------------------------------------------------------------------|

| b[15:13] | Reserved    | Ignore                                                                                               |

| b[12]    | V6_HI_FAULT | V6_POL_HI = 1 (default). 1: Fault (V6 greater than V6_THR_HI). 0: No fault (V6 less than V6_THR_HI). |

|          |             | V6_POL_HI = 0. 1: Fault (V6 less than V6_THR_HI). 0: No fault (V6 greater than V6_THR_HI).           |

| b[11]    | V6_LO_FAULT | V6_POL_LO = 1. 1: Fault (V6 greater than V6_THR_LO). 0: No fault (V6 less than V6_THR_LO).           |

|          |             | V6_POL_LO = 0 (default). 1: Fault (V6 less than V6_THR_LO). 0: No fault (V6 greater than V6_THR_LO). |

| b[10]    | V5_HI_FAULT | V5_POL_HI = 1 (default). 1: Fault (V5 greater than V5_THR_HI). 0: No fault (V5 less than V5_THR_HI). |

|          |             | V5_POL_HI = 0. 1: Fault (V5 less than V5_THR_HI). 0: No fault (V5 greater than V5_THR_HI).           |

| b[9]     | V5_L0_FAULT | V5_POL_LO = 1. 1: Fault (V5 greater than V5_THR_LO). 0: No fault (V5 less than V5_THR_LO).           |

|          |             | V5_POL_LO = 0 (default). 1: Fault (V5 less than V5_THR_LO). 0: No fault (V5 greater than V5_THR_LO). |

| b[8]     | V4_HI_FAULT | V4_POL_HI = 1 (default). 1: Fault (V4 greater than V4_THR_HI). 0: No fault (V4 less than V4_THR_HI). |

|          |             | V4_POL_HI = 0. 1: Fault (V4 less than V4_THR_HI). 0: No fault (V4 greater than V4_THR_HI).           |

| b[7]     | V4_LO_FAULT | V4_POL_LO = 1.<br>1: Fault (V4 greater than V4_THR_LO).<br>0: No fault (V4 less than V4_THR_LO).     |

|          |             | V4_POL_LO = 0 (default). 1: Fault (V4 less than V4_THR_LO). 0: No fault (V4 greater than V4_THR_LO). |

## STATUS\_WORD Data Contents

| b[6] | V3_HI_FAULT | V3_POL_HI = 1 (default).  1: Fault (V3 greater than V3_THR_HI).  0: No fault (V3 less than V3_THR_HI). |

|------|-------------|--------------------------------------------------------------------------------------------------------|

|      |             | V3_POL_HI = 0. 1: Fault (V3 less than V3_THR_HI). 0: No fault (V3 greater than V3_THR_HI).             |

| b[5] | V3_LO_FAULT | V3_POL_LO = 1. 1: Fault (V3 greater than V3_THR_LO). 0: No fault (V3 less than V3_THR_LO).             |

|      |             | V3_POL_LO = 0 (default). 1: Fault (V3 less than V3_THR_LO). 0: No fault (V3 greater than V3_THR_LO).   |

| b[4] | V2_HI_FAULT | V2_POL_HI = 1 (default). 1: Fault (V2 greater than V2_THR_HI). 0: No fault (V2 less than V2_THR_HI).   |

|      |             | V2_POL_HI = 0. 1: Fault (V2 less than V2_THR_HI). 0: No fault (V2 greater than V2_THR_HI).             |

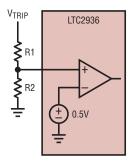

| b[3] | V2_L0_FAULT | V2_POL_LO = 1. 1: Fault (V2 greater than V2_THR_LO). 0: No fault (V2 less than V2_THR_LO).             |