# LTC2946 Wide Range I<sup>2</sup>C Power, Charge and Energy Monitor

#### **FEATURES**

- Rail-to-Rail Input Range: 0V to 100V

- Wide Input Supply Range: 2.7V to 100V

- **Shunt Regulator for Supplies >100V**

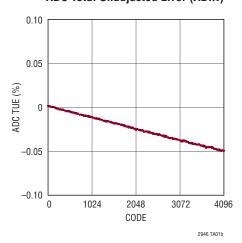

- $\Delta\Sigma$  ADC with Less Than ±0.4% Total **Unadjusted Error**

- 12-Bit Resolution for Current and Voltages

- ±1% Accurate Power and Energy Measurements

- ±0.6% Accurate Current and Charge Measurements

- Additional ADC Input Monitors an External Voltage

- Internal ±5% or External Time Bases

- Continuous Scan and Snapshot Modes

- Stores Minimum and Maximum Values

- Alerts When Limits Exceeded

- Split SDA Pin Eases Opto-Isolation

- Shutdown Mode with  $I_0 < 40 \mu A$

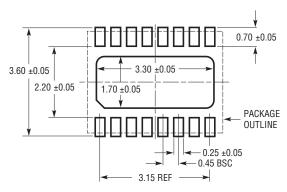

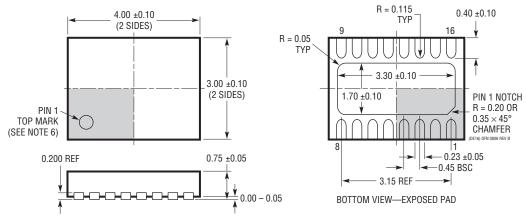

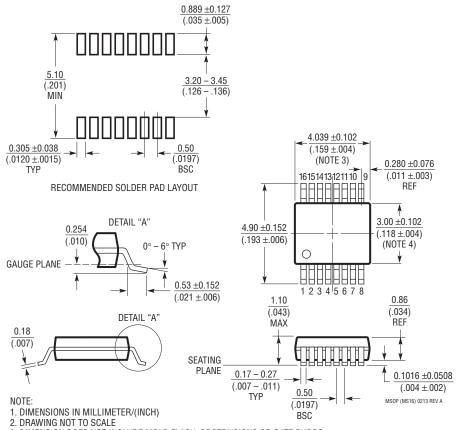

- Available in 4mm × 3mm DFN and 16-Lead **MSOP** Packages

## **APPLICATIONS**

- Telecom Infrastructure

- **Industrial Equipment**

- General Purpose Energy Measurement

#### DESCRIPTION

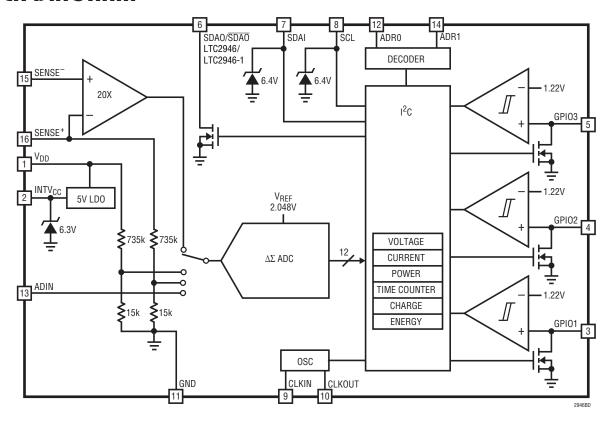

The LTC®2946 is a rail-to-rail system monitor that measures current, voltage, power, charge and energy. It features an operating range of 2.7V to 100V and includes a shunt regulator for supplies above 100V. The current measurement common mode range of OV to 100V is independent of the input supply. A 12-bit ADC measures load current, input voltage and an auxiliary external voltage. Load current and internally calculated power are integrated over an external clock or crystal or internal oscillator time base for charge and energy. An accurate time base allows the LTC2946 to provide measurement accuracy of better than ±0.6% for charge and ±1% for power and energy. Minimum and maximum values are stored and an overrange alert with programmable thresholds minimizes the need for software polling. Data is reported via a standard I<sup>2</sup>C interface.

The LTC2946 I<sup>2</sup>C interface includes separate data input and output pins for use with standard or opto-isolated I<sup>2</sup>C connections. The LTC2946-1 has an inverted data output for use with inverting opto-isolator configurations.

∡, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and Hot Swap is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

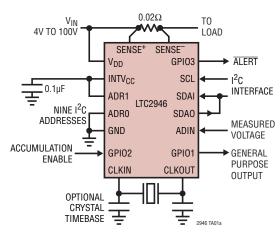

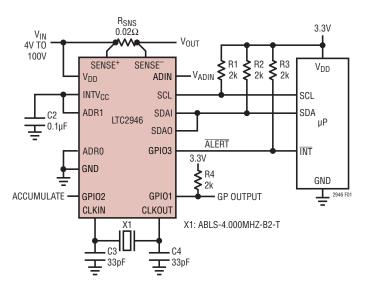

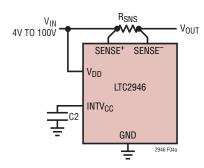

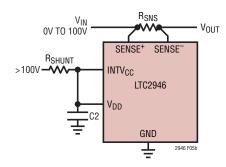

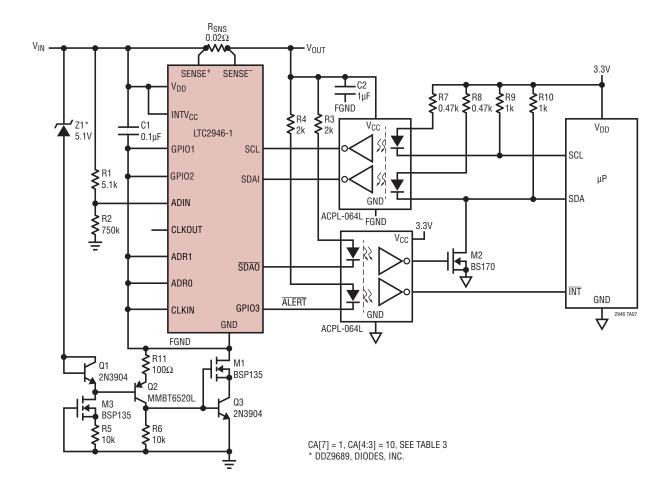

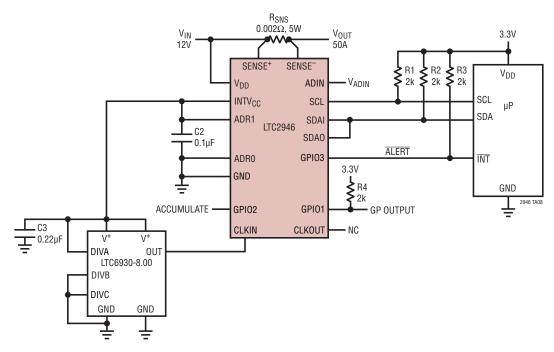

# TYPICAL APPLICATION

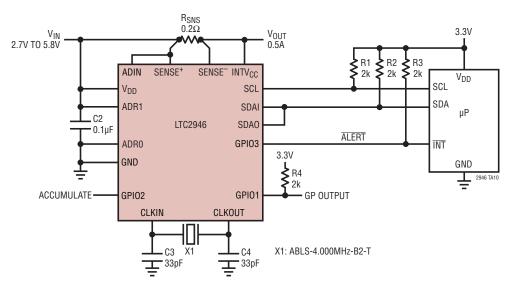

#### Wide Range Power, Charge and Energy Monitor with Onboard ADC and I<sup>2</sup>C

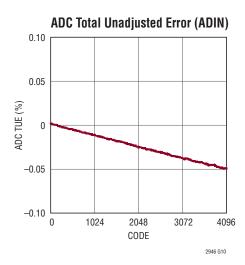

#### **ADC Total Unadjusted Error (ADIN)**

2946fa

# **ABSOLUTE MAXIMUM RATINGS** (Notes 1, 2)

| V <sub>DD</sub> Voltage0.3V to 100\<br>SENSE+ Voltage1V to 100\                    |

|------------------------------------------------------------------------------------|

| SENSE <sup>-</sup> Voltage1V or SENSE <sup>+</sup> - 1V to SENSE <sup>+</sup> + 1\ |

| INTV <sub>CC</sub> Voltage                                                         |

| (Note 3)0.3V to Lesser of 5.8V, $V_{DD}$ + 0.3V                                    |

| ADR1, ADR0, ADIN, SDAO, SDAO, GPI01 TO GPI03                                       |

| Voltages0.3V to 7\                                                                 |

| CLKOUT Voltage0.3V to INTV <sub>CC</sub> + 0.3\                                    |

| CLKIN Voltage0.3V to 5.5\                                                          |

| INTV <sub>CC</sub> Clamp Current35mA                                               |

| SCL, SDAI Voltages (Note 4)          | 0.3V to 5.9V  |

|--------------------------------------|---------------|

| SCL, SDAI Clamp Current              | 5mA           |

| Operating Temperature Range          |               |

| LTC2946C                             | 0°C to 70°C   |

| LTC2946I                             | 40°C to 85°C  |

| LTC2946H                             | 40°C to 125°C |

| LTC2946MP                            | 55°C TO 125°C |

| Storage Temperature Range            | 65°C to 150°C |

| Lead Temperature (Soldering, 10 sec) |               |

| MS Package Only                      | 300°C         |

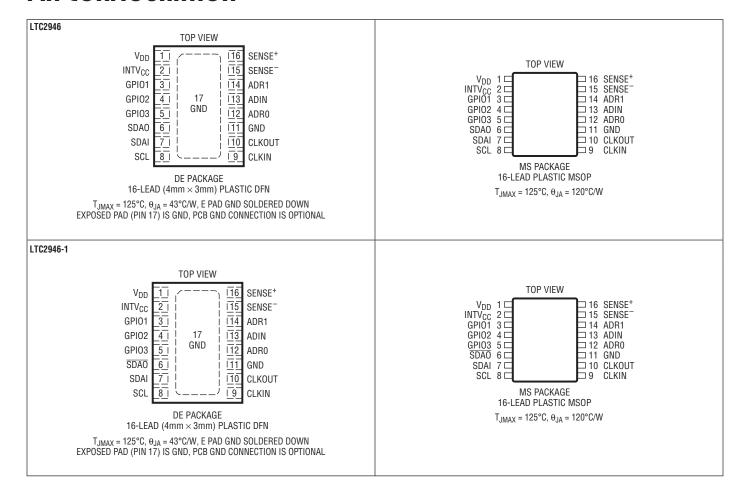

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|--------------|---------------------------------|-------------------|

| LTC2946CDE#PBF    | LTC2946CDE#TRPBF    | 2946         | 16-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC2946IDE#PBF    | LTC2946IDE#TRPBF    | 2946         | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC2946HDE#PBF    | LTC2946HDE#TRPBF    | 2946         | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC2946CDE-1#PBF  | LTC2946CDE-1#TRPBF  | 29461        | 16-Lead (4mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC2946IDE-1#PBF  | LTC2946IDE-1#TRPBF  | 29461        | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 85°C     |

| LTC2946HDE-1#PBF  | LTC2946HDE-1#TRPBF  | 29461        | 16-Lead (4mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC2946CMS#PBF    | LTC2946CMS#TRPBF    | 2946         | 16-Lead Plastic MSOP            | 0°C to 70°C       |

| LTC2946IMS#PBF    | LTC2946IMS#TRPBF    | 2946         | 16-Lead Plastic MSOP            | -40°C to 85°C     |

| LTC2946HMS#PBF    | LTC2946HMS#TRPBF    | 2946         | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LTC2946MPMS#PBF   | LTC2946MPMS#TRPBF   | 2946         | 16-Lead Plastic MSOP            | −55°C to 125°C    |

| LTC2946CMS-1#PBF  | LTC2946CMS-1#TRPBF  | 29461        | 16-Lead Plastic MSOP            | 0°C to 70°C       |

| LTC2946IMS-1#PBF  | LTC2946IMS-1#TRPBF  | 29461        | 16-Lead Plastic MSOP            | -40°C to 85°C     |

| LTC2946HMS-1#PBF  | LTC2946HMS-1#TRPBF  | 29461        | 16-Lead Plastic MSOP            | -40°C to 125°C    |

| LTC2946MPMS-1#PBF | LTC2946MPMS-1#TRPBF | 29461        | 16-Lead Plastic MSOP            | −55°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . $V_{DD}$ is from 4V to 100V, unless otherwise noted. (Note 2)

| SYMBOL                   | PARAMETER                                           | CONDITIONS                                                                  |   | MIN | TYP       | MAX       | UNITS    |

|--------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|---|-----|-----------|-----------|----------|

| Supplies                 |                                                     |                                                                             |   |     |           |           |          |

| $\overline{V_{DD}}$      | V <sub>DD</sub> Input Supply Voltage                |                                                                             | • | 4   |           | 100       | V        |

| $\overline{V_{CC}}$      | INTV <sub>CC</sub> Input Supply Voltage             |                                                                             | • | 2.7 |           | 5.8       | V        |

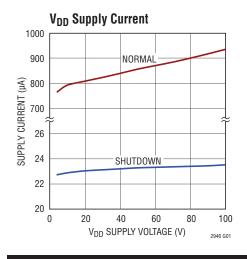

| I <sub>DD</sub>          | V <sub>DD</sub> Supply Current                      | V <sub>DD</sub> = 48V, INTV <sub>CC</sub> Open<br>Shutdown                  | • |     | 0.9<br>15 | 1.3<br>40 | mA<br>μA |

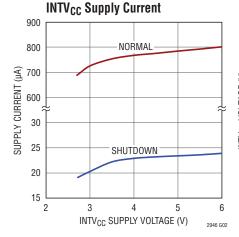

| I <sub>CC</sub>          | INTV <sub>CC</sub> Supply Current                   | INTV <sub>CC</sub> = V <sub>DD</sub> = 5V<br>Shutdown                       | • |     | 0.7<br>15 | 1.0<br>40 | mA<br>μA |

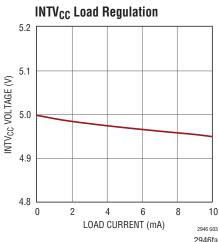

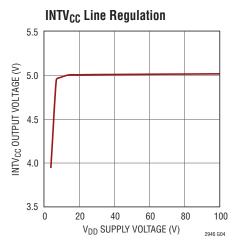

| V <sub>CC(LDO)</sub>     | INTV <sub>CC</sub> Linear Regulator Voltage         | 8V < V <sub>DD</sub> < 100V, I <sub>LOAD</sub> = 0mA                        | • | 4.4 | 5         | 5.4       | V        |

| $\Delta V_{CC(LDO)}$     | INTV <sub>CC</sub> Linear Regulator Load Regulation | 8V < V <sub>DD</sub> < 100V, I <sub>LOAD</sub> = 0mA to 10mA                | • |     | 100       | 200       | mV       |

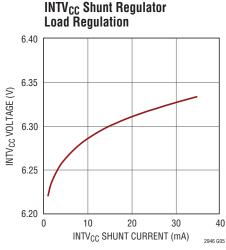

| V <sub>CCZ</sub>         | Shunt Regulator Voltage at INTV <sub>CC</sub>       | V <sub>DD</sub> = 48V, I <sub>CC</sub> = 1mA                                | • | 5.8 | 6.3       | 6.7       | V        |

| $\Delta V_{CCZ}$         | Shunt Regulator Load Regulation                     | $V_{DD} = 48V$ , $I_{CC} = 1mA$ to $35mA$                                   | • |     |           | 250       | mV       |

| V <sub>CC(UVL)</sub>     | INTV <sub>CC</sub> Supply Undervoltage Lockout      | $INTV_{CC}$ Rising, $V_{DD} = INTV_{CC}$                                    | • | 2.3 | 2.6       | 2.69      | V        |

| $V_{\rm DD(UVL)}$        | V <sub>DD</sub> Supply Undervoltage Lockout         | V <sub>DD</sub> Rising, INTV <sub>CC</sub> Open                             | • | 2.4 | 2.8       | 3         | V        |

| V <sub>DDI2C(RST)</sub>  | V <sub>DD</sub> I <sup>2</sup> C Logic Reset        | V <sub>DD</sub> Falling, INTV <sub>CC</sub> Open                            | • | 1.7 | 2.1       |           | V        |

| V <sub>CCI2C(RST)</sub>  | INTV <sub>CC</sub> I <sup>2</sup> C Logic Reset     | INTV <sub>CC</sub> Falling, V <sub>DD</sub> = INTV <sub>CC</sub>            | • | 1.7 | 2.1       |           | V        |

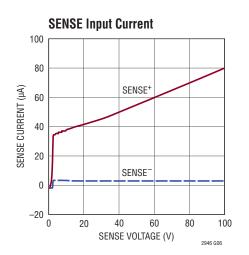

| SENSE Inputs             | ·                                                   |                                                                             |   |     |           |           |          |

| I <sub>SENSE</sub> +(HI) | 48V SENSE+ Input Current                            | SENSE+, SENSE-, V <sub>DD</sub> = 48V<br>Shutdown                           | • |     | 100       | 150<br>1  | μA<br>μA |

| I <sub>SENSE</sub> —(HI) | 48V SENSE <sup>-</sup> Input Current                | SENSE <sup>+</sup> , SENSE <sup>-</sup> , V <sub>DD</sub> = 48V<br>Shutdown | • |     |           | 20<br>1   | μA<br>μA |

| I <sub>SENSE</sub> +(LO) | OV SENSE+ Source Current                            | SENSE+, SENSE- = 0V, V <sub>DD</sub> = 48V<br>Shutdown                      | • |     |           | −10<br>−1 | μA<br>μA |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD}$ is from 4V to 100V, unless otherwise noted. (Note 2)

| SYMBOL                              | PARAMETER                                 | CONDITIONS                                                                                                                                                                               | N                           | IIN T                                  | YP MAX                                                                       | UNITS                                                       |

|-------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------|

| I <sub>SENSE(LO)</sub> <sup>-</sup> | OV SENSE <sup>-</sup> Source Current      | SENSE+, SENSE- = 0V, V <sub>DD</sub> = 48V<br>Shutdown                                                                                                                                   | •                           |                                        | -5<br>-1                                                                     | μ <i>Α</i><br>μ <i>Α</i>                                    |

| ADC (SENSE+,                        | , SENSE <sup>-</sup> = 0V, 100V) (Note 5) | Ondituown                                                                                                                                                                                |                             |                                        |                                                                              | μ                                                           |

| RES                                 | Resolution (No missing codes)             | (Note 7)                                                                                                                                                                                 | •                           | 12                                     |                                                                              | Bits                                                        |

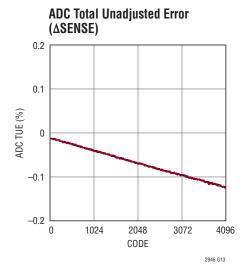

| TUE                                 | Total Unadjusted Error (Note 6)           | ΔSENSE (C-, I-Grade) ΔSENSE (H-, MP-Grade) SENSE+, V <sub>DD</sub> (C-, I-Grade) SENSE+, V <sub>DD</sub> (H-, MP-Grade) ADIN (C-, I-Grade) ADIN (H-, MP-Grade)                           | •                           |                                        | ±0.6<br>±0.7<br>±0.4<br>±0.5<br>±0.3<br>±0.4                                 | %<br>%<br>%                                                 |

| V <sub>FS</sub>                     | Full-Scale Voltage                        | ΔSENSE (C-, I-Grade) ΔSENSE (H-, MP-Grade) SENSE <sup>+</sup> , V <sub>DD</sub> (C-, I-Grade) SENSE <sup>+</sup> , V <sub>DD</sub> (H-, MP-Grade) ADIN (C-, I-Grade) ADIN (H-, MP-Grade) | • 10<br>• 1<br>• 10<br>• 2. | )1.7 10<br>02 10<br>)1.9 10<br>042 2.0 | 02.4 103<br>02.4 103.1<br>02.4 102.8<br>02.4 102.9<br>048 2.054<br>048 2.056 | 3 \ \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\                      |

| LSB                                 | LSB Step Size                             | ΔSENSE<br>SENSE <sup>+</sup> , V <sub>DD</sub><br>ADIN                                                                                                                                   |                             |                                        | 25<br>25<br>).5                                                              | μ\<br>m\<br>m\                                              |

| V <sub>OS</sub>                     | Offset Error                              | ΔSENSE (C-, I-Grade)<br>ΔSENSE (H-, MP-Grade)<br>SENSE <sup>+</sup> , V <sub>DD</sub><br>ADIN                                                                                            | •                           |                                        | ±2.1<br>±3.1<br>±1.5<br>±1.1                                                 | LSE<br>LSE<br>LSE                                           |

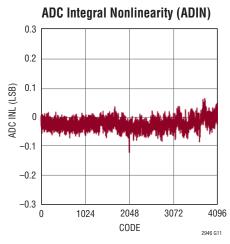

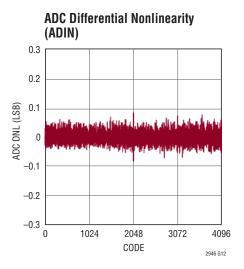

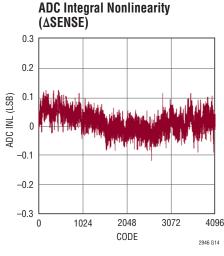

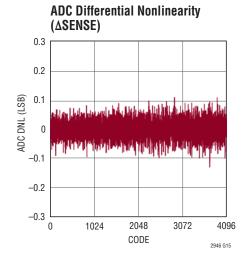

| INL                                 | Integral Nonlinearity                     | ΔSENSE<br>SENSE <sup>+</sup> , V <sub>DD</sub><br>ADIN                                                                                                                                   | •                           |                                        | ±2.5<br>±2<br>±2                                                             | LSE<br>LSE<br>LSE                                           |

| $\sigma_{\tau}$                     | Transition Noise (Note 7)                 | ΔSENSE<br>SENSE <sup>+</sup> , V <sub>DD</sub><br>ADIN                                                                                                                                   |                             | 0                                      | .2<br>).3<br>10                                                              | μV <sub>RMS</sub><br>mV <sub>RMS</sub><br>μV <sub>RMS</sub> |

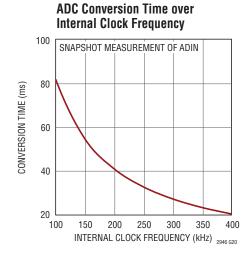

| t <sub>CONV</sub>                   | Conversion Time (Snapshot Mode)           | $\Delta$ SENSE SENSE+, $V_{DD}$ , ADIN                                                                                                                                                   |                             |                                        | 5.6 68.8<br>2.8 34.4                                                         |                                                             |

| R <sub>ADIN</sub>                   | ADIN Input Resistance                     | V <sub>DD</sub> = 48V, ADIN = 3V                                                                                                                                                         | •                           | 3 1                                    | 10                                                                           | MΩ                                                          |

| CLKIN, CLKOU                        | JT, GPIO                                  | ·                                                                                                                                                                                        |                             |                                        |                                                                              | •                                                           |

| V <sub>CLKIN(TH)</sub>              | CLKIN Input Threshold                     |                                                                                                                                                                                          | • (                         | ).7                                    | 1 1.3                                                                        | V                                                           |

| f <sub>CLKIN(MAX)</sub>             | Maximum CLKIN Frequency                   |                                                                                                                                                                                          | • :                         | 25                                     |                                                                              | MHz                                                         |

| I <sub>CLKIN(IN)</sub>              | CLKIN Input Current                       | V <sub>CLKIN</sub> = 5V                                                                                                                                                                  | •                           |                                        | 5 10                                                                         | μA                                                          |

| I <sub>CLKOUT</sub>                 | CLKOUT Output Current                     | V <sub>CLKIN</sub> = 0V, V <sub>CLKOUT</sub> = 0V                                                                                                                                        | • -                         | 70 –1                                  | 100 –130                                                                     | μΑ                                                          |

| V <sub>GPIO(TH)</sub>               | GPIO Input Threshold                      | V <sub>GPIO</sub> Rising                                                                                                                                                                 | • 1                         | .06 1.                                 | .22 1.32                                                                     | V                                                           |

| V <sub>GPIO(HYST)</sub>             | GPIO Input Hysteresis                     |                                                                                                                                                                                          |                             | 3                                      | 36                                                                           | m√                                                          |

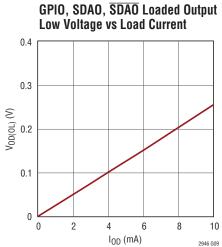

| V <sub>GPIO(OL)</sub>               | GPIO Output Low Voltage                   | I <sub>GPIO</sub> = 8mA                                                                                                                                                                  | •                           | 0.                                     | .15 0.4                                                                      | V                                                           |

| I <sub>GPIO(IN)</sub>               | GPIO Input Leakage Current                | $V_{GPIO} = 5V$                                                                                                                                                                          | •                           |                                        | 0 ±1                                                                         | μΑ                                                          |

| I <sup>2</sup> C Interface (        | $(V_{DD} = 48V)$                          |                                                                                                                                                                                          |                             |                                        |                                                                              |                                                             |

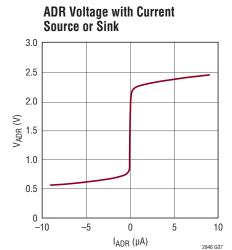

| V <sub>ADR(H)</sub>                 | ADR0, ADR1 Input High Threshold           |                                                                                                                                                                                          | • 1                         | .9 2                                   | 2.4 2.7                                                                      | V                                                           |

| V <sub>ADR(L)</sub>                 | ADR0, ADR1 Input Low Threshold            |                                                                                                                                                                                          | • (                         | 0.3                                    | 0.9                                                                          | V                                                           |

| I <sub>ADR(IN)</sub>                | ADR0, ADR1 Input Current                  | ADR0, ADR1 = 0V, 3V                                                                                                                                                                      | •                           |                                        | ±13                                                                          | μA                                                          |

| I <sub>ADR(IN,Z)</sub>              | Allowable Leakage When Open               |                                                                                                                                                                                          | •                           |                                        | ±7                                                                           | μΑ                                                          |

| V <sub>OD(OL)</sub>                 | SDAO, SDAO, Output Low Voltage            | I <sub>SDAO</sub> , I <sub>SDAO</sub> = 8mA                                                                                                                                              | •                           | 0.                                     | .15 0.4                                                                      | V                                                           |

| I <sub>SDA,SCL(IN)</sub>            | SDAI, SDAO, SDAO, SCL Input Current       | SDAI, SDAO, SDAO, SCL = 5V                                                                                                                                                               | •                           |                                        | 0 ±1                                                                         | μΑ                                                          |

LINEAR TECHNOLOGY

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V_{DD}$ is from 4V to 100V, unless otherwise noted. (Note 2)

| SYMBOL                        | PARAMETER                                     |                                            | MIN | TYP | MAX  | UNITS |     |

|-------------------------------|-----------------------------------------------|--------------------------------------------|-----|-----|------|-------|-----|

| V <sub>SDA,SCL(TH)</sub>      | SDAI, SCL Input Threshold                     |                                            | •   | 1.5 | 1.8  | 2.1   | V   |

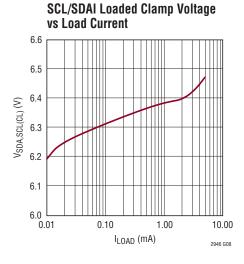

| V <sub>SDA,SCL(CL)</sub>      | SDAI, SCL Clamp Voltage                       | I <sub>SDAI</sub> , I <sub>SCL</sub> = 3mA | •   | 5.9 | 6.4  | 6.9   | V   |

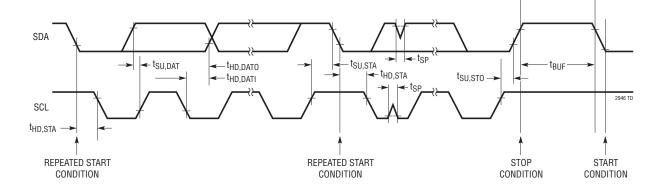

| I <sup>2</sup> C Interface Ti | ming                                          |                                            |     |     |      |       |     |

| f <sub>SCL(MAX)</sub>         | Maximum SCL Clock Frequency                   |                                            | •   | 400 |      |       | kHz |

| $t_{LOW}$                     | SCL LOW Period                                |                                            | •   |     | 0.65 | 1.3   | μs  |

| t <sub>HIGH</sub>             | SCL HIGH Period                               |                                            | •   |     | 50   | 600   | ns  |

| t <sub>BUF(MIN)</sub>         | Bus Free Time Between<br>STOP/START Condition |                                            | •   |     | 0.12 | 1.3   | μs  |

| t <sub>HD,STA(MIN)</sub>      | Hold Time After (Repeated) START<br>Condition |                                            | •   |     | 140  | 600   | ns  |

| t <sub>SU,STA(MIN)</sub>      | Repeated START Condition<br>Setup Time        |                                            | •   |     | 30   | 600   | ns  |

| t <sub>SU,STO(MIN)</sub>      | STOP Condition Setup Time                     |                                            | •   |     | 30   | 600   | ns  |

| t <sub>HD,DATI(MIN)</sub>     | Data Hold Time Input                          |                                            | •   |     | -100 | 0     | ns  |

| t <sub>HD,DATO(MIN)</sub>     | Data Hold Time Output                         |                                            | •   | 300 | 600  | 900   | ns  |

| t <sub>SU,DAT(MIN)</sub>      | Data Setup Time                               |                                            | •   |     | 30   | 100   | ns  |

| t <sub>SP(MAX)</sub>          | Maximum Suppressed Spike Pulse Width          |                                            | •   | 50  | 110  | 250   | ns  |

| t <sub>RST</sub>              | Stuck Bus Reset Time                          | SCL or SDAI Held Low                       | •   | 25  | 33   |       | ms  |

| $C_X$                         | SCL, SDAI Input Capacitance (Note 7)          |                                            |     |     | 5    | 10    | pF  |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive. All voltages are referenced to ground, unless otherwise noted.

**Note 3:** An internal shunt regulator limits the  $INTV_{CC}$  pin to a minimum of 5.8V. Driving this pin to voltages beyond 5.8V may damage the part. This pin can be safely tied to higher voltages through a resistor that limits the current below 35mA.

**Note 4:** Internal clamps limit the SCL and SDAI pins to a minimum of 5.9V. Driving these pins to voltages beyond the clamp may damage the part. The pins can be safely tied to higher voltages through resistors that limit the current below 5mA.

Note 5: ΔSENSE is defined as V<sub>SENSE</sub><sup>+</sup> – V<sub>SENSE</sub><sup>-</sup>

**Note 6:** TUE = (ACTUAL CODE – IDEAL CODE)/4096 • 100% where IDEAL CODE is derived from a straight line passing through Code 0 at 0V and theoretical code of 4096 at  $V_{\rm FS}$ .

Note 7: Guaranteed by design and not subject to test.

# TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

2946fa

# TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

**ADIN:** ADC Input. The onboard ADC measures voltages between 0V and 2.048V with respect to GND or INTV $_{\rm CC}$ . Tie to ground if unused. See Table 3 in the Applications Information section for details.

**ADR1, ADR0:**  $I^2C$  Device Address Inputs. Connecting these pins to INTV<sub>CC</sub>, GND, or leaving the pins open configures one of nine possible addresses. See Table 1 in the Applications Information section for details.

**CLKIN:** Clock Input. Connect to ground to use the internal ±5% clock. For improved accuracy, connect to an external crystal oscillator circuit or drive with an external clock.

**CLKOUT:** Clock Output. Connect to an external crystal oscillator circuit. Leave open if unused.

**EXPOSED PAD:** Exposed Pad may be left open or connected to device ground. For best thermal performance, connect to a large PCB area.

**GND:** Device Ground.

**GPIO1:** General Purpose Input/Output (Open Drain). Configurable to general purpose output or input. Tie to ground if unused. See Table 9 in the Applications Information section for details.

**GPI02:** General Purpose Input/Output (Open Drain). Configurable to general purpose output, input or accumulation enable (ACC) to gate internal accumulators. Tie to ground if unused. See Table 9 in the Applications Information section for details.

**GPIO3:** General Purpose Input/Output (Open <u>Drain</u>). Configurable to general purpose output, input or <u>ALERT</u>. As <u>ALERT</u>, it is pulled to ground when a fault occurs to alert the host controller. A fault alert is enabled by setting the corresponding bit in the ALERT registers, as shown in Tables 5 and 8. Tie to ground if unused. See Table 9 in the Applications Information section for details.

**INTV**<sub>CC</sub>: Internal Low Voltage Supply Input/Output. This pin is used to power internal circuitry. It can be configured as a direct input for a low voltage supply, as a linear regulator from a higher voltage supply connected to V<sub>DD</sub>, or as a shunt regulator. Connect this pin directly to a 2.7V to 5.8V supply if available. When INTV<sub>CC</sub> is powered from an external supply, short the  $V_{DD}$  pin to INTV<sub>CC</sub>. If  $V_{DD}$  is connected to a 4V to 100V supply, INTV<sub>CC</sub> becomes the 5V output of an internal series regulator that can supply up to 10mA to external circuitry. For even higher supply voltages, or if a floating topology is desired, INTV<sub>CC</sub> can be used as a 6.3V shunt regulator. Connect the supply to INTV<sub>CC</sub> through a resistor or current source that limits the shunt regulator current to less than 35mA. An undervoltage lockout circuit disables the ADC when the voltage at this pin drops below 2.5V. Connect a bypass capacitor of 0.1µF or greater from this pin to ground. If an external load is present, for loop stability use a bypass capacitor of 0.22µF or greater.

**SCL:**  $I^2C$  Bus Clock Input. Data at the SDAI pin is shifted in or out on rising edges of SCL. This pin is driven by an open-collector output from a master controller. An external pull-up resistor or current source is required and can be placed between SCL and  $V_{DD}$  or  $INTV_{CC}$ . The voltage at SCL is internally clamped to 6.4V typically.

## PIN FUNCTIONS

**SDAI:**  $I^2C$  Bus Data Input. Used for shifting in address, command or data bits. This pin is driven by an open-collector output from a master controller. An external pull-up resistor or current source is required and can be placed between SDAI and  $V_{DD}$  or INTV<sub>CC</sub>. The voltage at SDAI is internally clamped to 6.4V typically. Tie to SDAO for normal  $I^2C$  operation.

**SDAO:** LTC2946 Only. I<sup>2</sup>C Bus Data Output. Open-drain output used for sending data back to the master controller or acknowledging a write operation. An external pull-up resistor or current source is required. Tie to SDAI for normal I<sup>2</sup>C operation.

**SDAO:** LTC2946-1 Only. Inverted I<sup>2</sup>C Bus Data Output. Open-drain output used for sending data back to the master controller or acknowledging a write operation. Data is inverted for convenience of opto-isolation. An external pull-up resistor or current source is required. The LTC2946-1 cannot be used in nonisolated I<sup>2</sup>C applications without additional components.

**SENSE+:** Supply Voltage and Current Sense Input. Used as a supply and current sense input for internal current sense amplifier. The voltage at this pin is monitored by the onboard ADC with a full-scale input range of 102.4V. See Figure 20 for recommended Kelvin connection.

**SENSE**<sup>-</sup>: Current Sense Input. Connect an external sense resistor between SENSE<sup>+</sup> and SENSE<sup>-</sup>. The differential voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> is monitored by the onboard ADC with a full-scale sense voltage of 102.4mV.

$V_{DD}$ : High Voltage Supply Input. This pin powers an internal series regulator with input voltages ranging from 4V to 100V and produces 5V at INTV<sub>CC</sub> when V<sub>DD</sub> is above 8V. Connect a bypass capacitor of  $0.1\mu F$  or greater from this pin to ground if an external load is present on the INTV<sub>CC</sub> pin. The onboard 12-bit ADC can be configured to monitor the voltage at V<sub>DD</sub> with a full-scale input range of 102.4V.

# **BLOCK DIAGRAM**

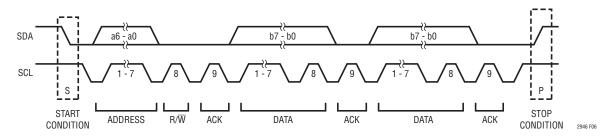

# **TIMING DIAGRAM**

## **OPERATION**

The LTC2946 accurately monitors current, voltage and power of any supply rail from 0V to 100V. An internal linear regulator allows the LTC2946 to operate directly from a 4V to 100V rail, or from an external supply voltage between 2.7V and 5.8V. Quiescent current is less than 1.3mA in normal operation. Enabling shutdown mode via the  $I^2C$  interface reduces the quiescent current to below  $40\mu A$ .

The onboard 12-bit analog-to-digital converter (ADC) runs either continuously or on demand using snapshot mode. There are seven continuous scan modes that can be selected via  $I^2C$ . These modes configure the ADC to repeatedly measure the differential voltage between SENSE<sup>+</sup> and SENSE<sup>-</sup> (full-scale 102.4mV), the voltage at SENSE<sup>+</sup> or  $V_{DD}$  pin (full-scale 102.4V) and the voltage applied to ADIN pin (full-scale 2.048V) at internally set duty cycles. See the Applications Information section for more details. The conversion results are stored in onboard registers.

In snapshot mode, the LTC2946 performs a single measurement of one selected voltage or current. A status bit in the STATUS2 register monitors the ADC's conversion progress; when complete, the conversion result is stored in the corresponding data registers.

The GPIO1 to GPIO3 pins are general purpose inputs or general purpose open-drain outputs. GPIO2 may also be configured as an enabling input for the accumulators. Similarly, GPIO3 may be configured as an ALERT output.

Onboard logic stores the minimum and maximum values for each ADC measurement, calculates power data by digitally multiplying the stored current and voltage data, and optionally triggers an alert by pulling the GPIO3 pin low when the ADC measured value falls outside the programmed window thresholds. The LTC2946 includes accumulators that integrate the measured current and power over time to produce charge and energy values. The accumulators integrate at a rate determined either with an internal trimmed ±5% clock, a precision clock generated from an external crystal, or an external clock. The accumulators can be preset with a value and optionally generate an alert when they overflow.

The LTC2946 includes an I<sup>2</sup>C interface to access the onboard data registers and to program the alert threshold, configuration and control registers. Two three-state pins, ADR1 and ADR0, are decoded to allow nine device addresses (see Table 1). The SDA pin is split into SDAI (input) and SDAO (output, LTC2946) or SDAO (output, LTC2946-1) to facilitate opto-isolation. Tie SDAI and SDAO together for normal, nonisolated I<sup>2</sup>C operation.

# **APPLICATIONS INFORMATION**

The LTC2946 offers a compact and complete solution for high and low side power monitoring with integrated energy and charge accumulators. With an input common mode range of 0V to 100V and a wide input supply operating voltage range from 2.7V to 100V, this device is ideal for a wide variety of power management applications including automotive, industrial and telecom infrastructure. The basic application circuit shown in Figure 1 provides monitoring of high side current with a  $0.02\Omega$  resistor (5.12A full-scale), input voltage (102.4V full-scale) and an external voltage (2.048V full-scale), all using an internal 12-bit ADC.

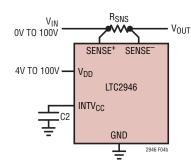

Figure 1. High Side Power, Energy and Charge Monitor Using the LTC2946

2946fa

#### **Data Converter, Multiplier and Accumulator**

The LTC2946 features an onboard, 12-bit  $\Delta\Sigma$  ADC that inherently averages input signal and noise over the conversion time window. The differential voltage between SENSE+ and SENSE- ( $\Delta$ SENSE) is monitored with 25 $\mu$ V/LSB resolution (102.4mV full-scale) to allow accurate measurement of the load current across very low value shunt resistors. The supply voltage at V<sub>DD</sub> or SENSE+ is directly measured with 25 $\mu$ V/LSB resolution (102.4V full-scale). The voltage at the uncommitted ADIN pin can also be measured with 0.5 $\mu$ V/LSB resolution (2.048V full-scale) to allow monitoring of an arbitrary external voltage.

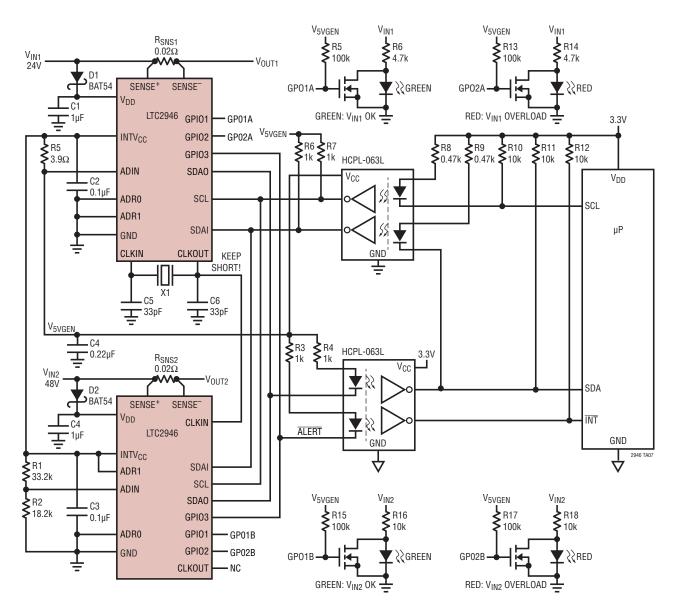

The supply voltage data is derived from V<sub>DD</sub>, SENSE<sup>+</sup> or ADIN depending on the external application circuit. SENSE+ is selected by default as it is normally connected to the supply voltage as shown in Figure 4 (4a to 4c) and Figure 5b. In negative supply voltage systems, such as shown in Figure 5d, V<sub>DD</sub> is used to measure the supply voltage at GND with respect to the device ground. For positive and negative supply voltages of more than 100V, as shown in Figure 5a and Figure 5c, external resistors can be used to divide down the voltage for ADIN to measure the supply voltage. CA[4:3] in the CTRLA register select between  $V_{DD}$ , SENSE<sup>+</sup> and ADIN for supply voltage data. More details can be found in Table 3. A 24-bit power value is generated by digitally multiplying the 12-bit load current data with the 12-bit supply voltage data. 1LSB of power is 1LSB of voltage multiplied by 1LSB of  $\triangle$ SENSE (current). The result is held in the three adjacent POWER registers (Table 2).

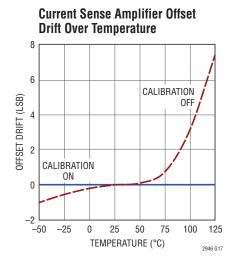

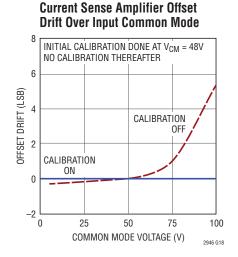

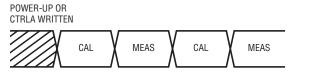

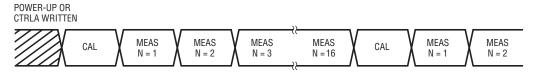

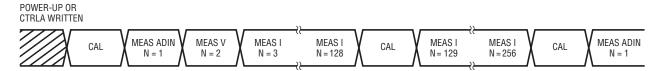

During conversions, the data converter's input is multiplexed to measure four voltages:  $\Delta SENSE$ , the current sense amplifier's offset,  $V_{DD}$  or  $V_{SENSE}^+$ , and  $V_{ADIN}$  at various duty cycle by configuring CA[6:5] and CA[2:0] in the CTRLA register (Table 3). Some configurations are shown in Figure 2 (2a to 2c) to illustrate the various conversion timing sequences. In Figure 2a, it is shown that upon power-up or after an  $I^2C$  write transaction to the CTRLA register the ADC will first measure the current sense amplifier's offset (calibration) and again after every other conversion which can be either  $V_{ADIN}$ , the supply voltage ( $V_{DD}$  or  $V_{SENSE}^+$ ) or the load current ( $\Delta SENSE$ ). Figure 2b shows periodic calibration performed every 16 conversions. In Figure 2c a more specific configuration

is shown where the ADC periodically calibrates the current sense amplifier with other voltages sequenced for conversions in between.

Two factors need to be considered when selecting between these configurations:

- Presence of load current harmonics in sync with the windows when the ADC is not sampling the current. The user can improve measurement accuracy of the load current signal with such harmonics by selecting a higher duty cycle for ΔSENSE. For most complete coverage, the ADC can be configured to continuously measure the current by setting CA[2:0] to 110.

- 2. Increasing the duty cycle for current measurement will result in less frequent updates of the current sense amplifier's offset and the supply voltage values, hence the amount they drift with respect to time and temperature determines the best configuration to use. An on-demand update can also be done with a single I<sup>2</sup>C write transaction to the CTRLA register, which will command new measurements of the current sense amplifier's offset and the supply voltage. The results will be used for offset calibration and for providing the voltage value for the multiplier. For example, if CA[6:5] is set to code 11, and CA[2:0] is set to 110, a new offset and voltage values will be produced two ADC conversions after the I<sup>2</sup>C write transaction. The ADC will continuously measure the current thereafter.

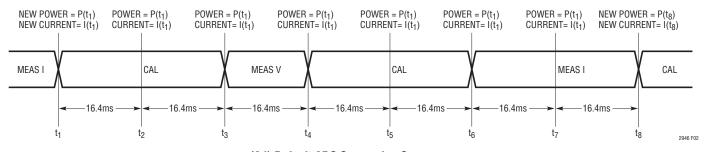

The timing diagram shown in Figure 2d illustrates the sequence in which the power and accumulator data are generated following conversions in the default configuration. At  $t_1$ , the ADC has just finished a conversion of the current ( $\Delta$ SENSE) signal. The time counter is incremented by one count while the new current data at  $t_1$  is added to the charge accumulator. A new power value is generated by multiplying  $I_{(t1)}$  with the previous voltage ( $V_{IN}$ ) data that is then added to the energy accumulator. From  $t_1$  to  $t_3$ , the systematic offset of the current sense amplifier is measured and stored. The ADC then performs a conversion on  $V_{IN}$ . A calibration is done again at  $t_4$  before the ADC converts  $\Delta$ SENSE. The charge and energy accumulators are incremented at  $t_2$ ,  $t_3$ ,  $t_4$ ,  $t_5$ ,  $t_6$  and  $t_7$ , with current and power data from time  $t_1$ . The timer counter will keep track

of the number of accumulations that have occurred. At  $t_8$ , new current and power data becomes available and these values are added to the charge and energy accumulators. For other CA configurations, the charge and energy accumulators behave similarly; during calibration and when not measuring current the last current value will be used for accumulation and calculation of power.

A 12-bit digital word corresponding to each measured voltage is stored in two adjacent registers out of the six total ADC data registers ( $\Delta$ SENSE MSB/LSB, V<sub>IN</sub> MSB/LSB, and ADIN MSB/LSB), with the eight MSBs in the first register and the four LSBs in the second (see Table 2). The lowest 4 bits in the LSB registers are set to 0. These data registers are updated immediately following the corresponding ADC conversion.

The 4-byte time counter keeps track of the elapsed time during which current and power measurements have been added to the charge and energy accumulators, respectively. At 16.395ms per count it will keep counts up to 2.23 years (see Table 15). Dividing the energy/charge by the time in the timer will yield the average power/current over the time interval in the timer. The charge accumulator is a 36-bit register with the most significant 32-bits accessible, hence one charge bit is equivalent to one timer tick of 16 (2<sup>4</sup>) counts of current. Similarly, the energy accumulator is a 48-bit register with the most significant 32-bits accessible, hence one energy bit is equivalent to one timer tick of 65536 (2<sup>16</sup>) counts of power. With current and power at full-scale the charge and energy accumulators are capable of storing 3.2 days of data which translates to several months at nominal current and power levels.

(2a) Current Sense Amplifier Calibrated Every Conversion, CA[6:5] = 00

(2b) Current Sense Amplifier Calibrated Every 16 Conversions, CA[6:5] = 01

(2c) The ADC Conversion Sequence for CA[6:5] = 10 and CA[2:0] = 101

(2d) Default ADC Conversion Sequence

Figure 2

2946fa

Since the accumulators contain multiple bytes of data, a single page read transaction of the accumulators is required to ensure the data is coherent. All the accumulators are writable, allowing them to be preloaded with given values. The LTC2946 can then be configured to generate an overflow alert after a specified amount of energy or charge has been delivered or when a preset amount of time has elapsed.

A snapshot mode is also included which makes a measurement of a single selected voltage (either ΔSENSE, V<sub>DD</sub> or V<sub>SFNSE</sub><sup>+</sup>, or V<sub>ADIN</sub>). To make a snapshot measurement, write the 2-bit code of the desired ADC channel to CA[4:3] and code 111 to CA[2:0] using a write byte command to the CTRLA register. When the write byte command is completed, the ADC converts the selected voltage and the busy bit S2[3] in the STATUS2 register (see Table 10) will be set to indicate that the conversion is in progress. After completing the conversion, the ADC will halt and the busy bit will reset to indicate that the data is ready. An alert may be generated at the end of a snapshot conversion by setting bit AL2[7] in the ALERT2 register (Table 8). To make another snapshot measurement, rewrite the CTRLA register. In snapshot mode, the POWER registers, time counters, charge and energy accumulators are not refreshed.

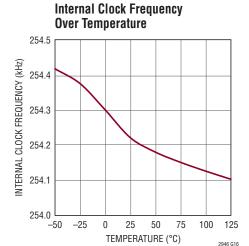

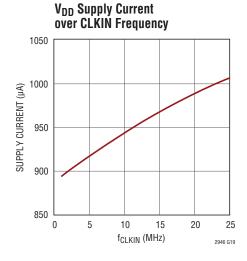

#### Crystal Oscillator/External Clock

Accurately measuring energy/charge by integrating power/ current requires a precise integration period. The on-chip clock of the LTC2946 is trimmed to within ±5%. To enable timekeeping with the on-chip clock, tie CLKIN to GND and leave CLKOUT open. For better accuracy, a crystal oscillator or resonator may be connected to the CLKIN and CLKOUT pins, as shown in Figure 1. Alternately, an external clock between 1MHz and 25MHz may be applied to CLKIN with CLKOUT left unconnected. The clock frequency at CLKIN is divided by 4x the value in the CLK DIV register (see Table 13) to generate an internal clock with targeted frequency of 250kHz for the data converter's delta-sigma modulator. With an external clock or crystal, the sampling frequency of the ADC can be adjusted by configuring the CLK\_DIV register (Register 43h). Limit the sampling clock to between 100kHz and 400kHz and at least 20kHz above or below f<sub>IN</sub>.

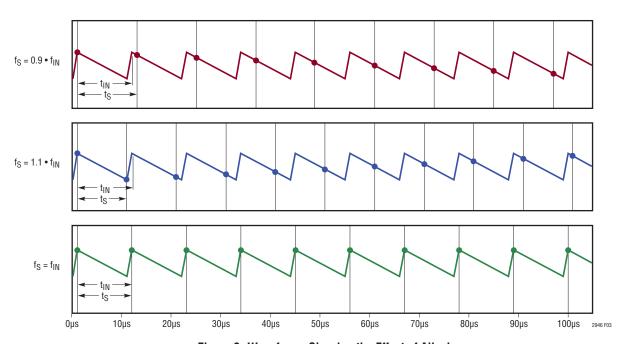

The delta-sigma ADC provides inherent averaging of the input signal such that an anti-aliasing filter is not required in most applications. However, noise ripple ( $f_{IN}$ ) occurring at integer multiples of the modulator sampling frequency ( $f_{S}$ ) can still pose problems. Figure 3 shows how the sampling frequency as a function of the input frequency affects the amount of error. When  $f_{S} = f_{IN}$ , in the worst case the input signal may be sampled entirely at its peak

Figure 3. Waveforms Showing the Effect of Aliasing

LINEAD

(or trough) resulting in an average output value of  $V_{PEAK}$  (or  $V_{TROUGH}$ ). The actual average value of the input is  $\frac{1}{2} \bullet (V_{PEAK} - V_{TROUGH})$ . Slightly adjusting the sampling frequency will remove the error as samples representative of the entire waveform are averaged over the conversion period. This is illustrated in the waveforms corresponding to  $f_S = 0.9f_{IN}$  and  $f_S = 1.1f_{IN}$ . The input can be seen to get sampled at multiple instances between the peak and trough. Averaging sufficient number of samples will then yield the correct result.

#### Flexible Power Supply to LTC2946

The LTC2946 can be externally configured to derive power from a wide range of supplies. The LTC2946 includes an onboard linear regulator to power the low voltage internal circuitry connected to the INTV<sub>CC</sub> pin from high V<sub>DD</sub> voltages. The linear regulator operates with V<sub>DD</sub> voltages from 4V to 100V, and a shunt regulator is available for voltages above 100V. The linear regulator produces a 5V output capable of supplying 10mA at the INTV<sub>CC</sub> pin when V<sub>DD</sub> is greater than 8V. The regulator is disabled when the junction temperature rises above 150°C, and the output is protected against accidental shorts. Bypass capacitors of  $0.1\mu F$ , or greater, at both the V<sub>DD</sub> and INTV<sub>CC</sub> pins are

recommended for optimal transient performance. Note that operation with high  $V_{DD}$  voltages can result in significant power dissipation, and care is required to ensure that the maximum operating junction temperature stays below 125°C. For improved thermal resistance, use the DFN package and solder the exposed pad to a large copper region on the PCB.

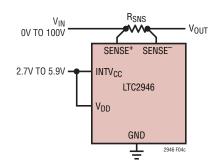

Figure 4a shows the LTC2946 being used to monitor an input supply that ranges from 4V to 100V. No secondary supply is needed since  $V_{DD}$  can be connected directly to the input supply. If the LTC2946 is used to monitor an input supply of 0V to 100V, it can derive power from a wide range secondary supply connected to the  $V_{DD}$  pin as shown in Figure 4b. The SENSE+/- pins can be biased independently of the part's supply voltage. Alternatively, if a low voltage supply is present it can be connected to the INTV<sub>CC</sub> pin, as shown in Figure 4c, to minimize on-chip power dissipation. When INTV<sub>CC</sub> is powered from a secondary supply, connect  $V_{DD}$  to INTV<sub>CC</sub>.

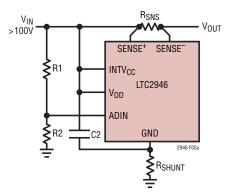

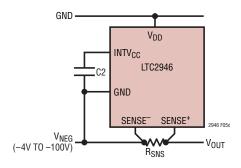

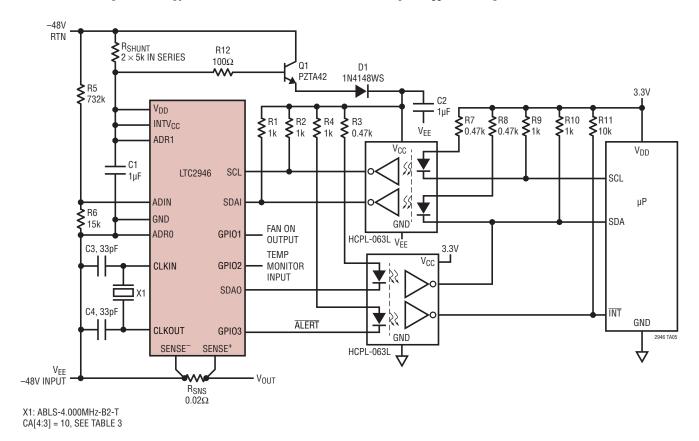

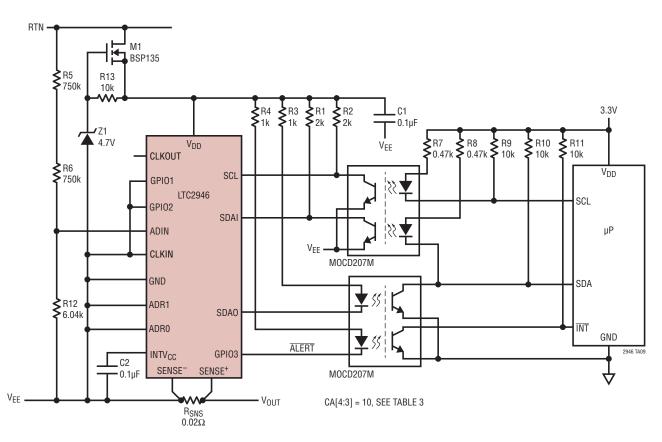

For supply voltages above 100V, the shunt regulator at  $INTV_{CC}$  can be used in both high and low side configurations to provide power to the LTC2946 through an external shunt resistor,  $R_{SHIINT}$ . Figure 5a shows a high side power

(4a) LTC2946 Derives Power from the Supply Being Monitored

(4b) LTC2946 Derives Power from a Wide Range Secondary Supply

(4c) LTC2946 Derives Power from a Low Voltage Secondary Supply

monitor with an input monitoring range beyond 100V in a high side shunt regulator configuration. The device ground is separated from ground through  $R_{SHUNT}$  and clamped at 6.3V below the input supply. Note that due to the different ground levels, the  $\rm I^2C$  signals from the part need to be level shifted for communication with other ground referenced components. The bus voltage is measured with a resistor string connected to ADIN. Set CA[7] in the CTRLA register so that the ADC measures ADIN with reference to  $\rm INTV_{CC}$  instead of GND. The measurement range at ADIN is then from  $\rm INTV_{CC}$  to  $\rm INTV_{CC}-2.048V$ .

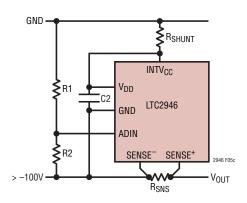

Figure 5b shows a high side rail-to-rail power monitor which derives power from a secondary supply greater than 100V. The voltage at  $INTV_{CC}$  is clamped at 6.3V above ground in a low side shunt regulator configuration to power the part. In low side power monitors, the device

ground and the current sense inputs are connected to the negative terminal of the input supply as shown in Figure 5c. The low side shunt regulator configuration allows operation with input supplies above 100V by clamping the voltage at INTV $_{CC}$ .  $R_{SHUNT}$  should be sized according to the following equation:

$$\frac{V_{S(MAX)} - V_{CCZ(MIN)}}{I_{CC(ABSMAX)}} \le R_{SHUNT} \le \frac{V_{S(MIN)} - V_{CCZ(MAX)}}{I_{CC(MAX)} + I_{LOAD(MAX)}} (1)$$

$$\frac{V_{S(MAX)} - 5.8V}{35mA} \le R_{SHUNT} \le \frac{V_{S(MIN)} - 6.7V}{1mA + I_{LOAD(MAX)}}$$

where  $V_{S(MAX)}$  and  $V_{S(MIN)}$  are the operating maximum and minimum limits of the supply.  $I_{LOAD(MAX)}$  is the maximum external current load that is connected to the shunt regulator. The shunt resistor must also be rated to safely

(5a) LTC2946 Derives Power Through a High Side Shunt Regulator

(5c) LTC2946 Derives Power Through a Low Side Shunt Regulator in a Low Side Current Sense Topology

(5b) LTC2946 Derives Power Through a Low Side Shunt Regulator in a High Side Current Sense Topology

(5d) LTC2946 Derives Power from the Supply Monitored in a Low Side Current Sense Topology

Figure 5

T LINEAR

2946fa

dissipate the worst-case power. As an example, consider the -48V telecom system where the supply operates from -36V to -72V and the shunt regulator is used to supply an external load up to 4mA.  $R_{SHUNT}$  needs to be between 1.9k and 5.9k according to the previous equation, and for reduced power dissipation, a larger resistance is advantageous. The worst-case power dissipated in an  $R_{SHUNT}$  of 5.36k is calculated to be 0.8W. Three 0.5W rated 1.8k resistors in series would suffice for this example.

If the supply input is below 100V, the shunt resistor is not required and  $V_{DD}$  can be connected to GND of the supply as shown in Figure 5d.

#### **Supply Undervoltage Lockout**

During power-up, the internal  $I^2C$  logic and the ADC are enabled when either  $V_{DD}$  or  $INTV_{CC}$  rises above its undervoltage lockout threshold. During power-down, the ADC is disabled when  $V_{DD}$  and  $INTV_{CC}$  fall below their respective undervoltage lockout thresholds. The internal  $I^2C$  logic is reset when  $V_{DD}$  and  $INTV_{CC}$  fall below their respective  $I^2C$  reset thresholds.

#### Shutdown Mode

The LTC2946 includes a low quiescent current shutdown mode, controlled by bit CB[6] in the CTRLB register (Table 4). Setting CB[6] puts the part in shutdown mode, powering down the ADC, internal reference and onboard linear regulator. The internal I<sup>2</sup>C bus remains active, and although the ADR1 and ADR0 pins are disabled, the device will retain the most recently programmed I<sup>2</sup>C bus address. All onboard registers retain their contents and can be accessed through the I<sup>2</sup>C interface. To re-enable ADC conversions, reset bit CB[6] in the CTRLB register. The analog circuitry will power up and all registers will retain their contents.

The onboard linear regulator is disabled in shutdown mode to conserve power. If the onboard linear regulator is used to power external I<sup>2</sup>C bus related circuitry such as optocouplers or pull-ups, I<sup>2</sup>C communication will be lost when the part is shut down. The LTC2946 would then have to be reset by cycling its power to come out of shutdown. If

low  $l_Q$  mode is not required, ensure bit CB[6] in the CTRLB register is masked off during software development. It is recommended that external regulators be used in such applications if powering down the LTC2946 is desirable. As an added layer of protection against this scenario, bit CB[4] in the CTRLB register can be set during system configuration to enable the LTC2946 to automatically exit shutdown mode when the  $l^2C$  lines are low for more than 33ms (which can be a result of accidental shutdown of the LTC2946's linear regulator powering the  $l^2C$ ). The user can elect to be alerted of this event by setting bit AL2[3] in the ALERT2 register (Table 8). Quiescent current drops below  $40\mu A$  in shutdown mode with the internal regulator disabled.

#### **Configuring the GPIO Pins**

The LTC2946 has three GPIO pins configurable through the GPIO\_CFG register (Table 9) to be used as general purpose input/output pins. As general purpose inputs, GPIO1 through GPIO3 can be either active HIGH or LOW. In addition, GPIO2 can also be used as an accumulation enable input by writing bits CB[3:2] = [10] to allow integration of the time counter, charge and energy accumulators. GPIO1 through GPIO3 have comparators monitoring the voltage on these pins with a threshold of 1.22V, the results of which may be read from bits S2[6:4] in the STATUS2 register, as shown in Table 10. An alert may be generated when GPIO1 or GPIO2 are active as inputs by setting bits AL2[6] and AL2[5], respectively, in the ALERT2 register.

GPIO1-3 can be pulled low as general purpose outputs, which are otherwise high impedance. GPIO3 is by default an ALERT output that pulls low when an alert event is present. To pull GPIO3 (ALERT) low in the absence of an alert event, set GC[7] of the GPIO3\_CTRL register (Table 12). Clearing this bit will release the GPIO3 (ALERT). GC[7] does not have an effect on GPIO3 if it is not configured as an ALERT output. Likewise, GC[6] does not affect GPIO3 if it is not configured as a general purpose output. GC[7] is set whenever an alert event occurs irrespective of GPIO3's configuration. Reset GC[7] before reconfiguring GPIO3 to ALERT.

#### I<sup>2</sup>C Reset

The accumulators can be programmed to reset themselves after the host reads the last byte (3Fh) of the accumulator data by writing bits CB[1:0] to [01] in the CTRLB register (Table 4). This feature removes the need to issue a reset command after polling the LTC2946 for accumulated data. The accumulators will continue to accumulate after the reset. To reset the accumulators without such read command, write bits CB[1:0] to [10]. The accumulators will stay reset if CB[1:0] = [10]. All registers are reset when CB[1:0] = [11], and these bits will then auto-reset to [00].

The ADC sequencing configuration is preserved through the I<sup>2</sup>C reset, regardless of the CTRLA register having reset. To change the sequencing configuration after such resets, rewrite the CTRLA register.

## Storing Minimum and Maximum Values

The LTC2946 compares each measurement including the calculated power with the stored values in the respective MIN and MAX registers for each parameter (Table 2). If the new conversion is beyond the stored minimum or maximum values, the MIN or MAX registers are updated with the new values. The MIN and MAX of the registers are refreshed at the end of their respective ADC conversions in continuous scan modes and snapshot mode. They are also refreshed if the ADC registers are written via the I<sup>2</sup>C bus with values beyond the stored values. To initiate a new peak hold cycle, write all 1's to the MIN registers and all 0's to the MAX registers via the I<sup>2</sup>C bus. These registers will be updated when the next respective ADC conversion is done.

The LTC2946 also includes MIN and MAX threshold registers (Table 2) for the measured parameters including the calculated power. At power-up, the maximum thresholds are set to all 1's, and minimum thresholds are set to all O's, effectively disabling them. The thresholds can be reprogrammed to any desired value via the I<sup>2</sup>C bus.

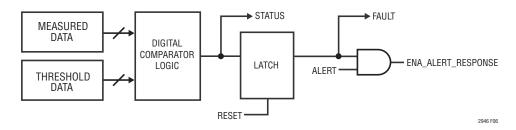

#### **Fault Alert and Resetting Faults**

As soon as a measured quantity falls below the minimum threshold or exceeds the maximum threshold, the LTC2946 sets the corresponding flag in the STATUS1 (Table 6) register and latches it into the FAULT1 (Table 7) register (see Figure 6). Other events such as GPIO state change, stuck bus wake-up and accumulator overflow have their present status in the STATUS2 (Table 10) register and any fault is latched in the FAULT2 (Table 11) register. The GPIO3 pin is pulled low if the appropriate bit in the ALERT1 (Table 5) and ALERT2 (Table 8) registers is set and it is configured as ALERT output. More details on the alert behavior can be found in the Alert Response Protocol section.

An active fault indication can be reset by writing zeros to the corresponding FAULT register bits or setting bit CB[5] in the CTRLB register. If bit CB[5] is set, reading the FAULT1 or FAULT2 register will cause the corresponding register to reset. All FAULT register bits are also cleared if the V<sub>DD</sub> and INTV<sub>CC</sub> fall below their respective I<sup>2</sup>C logic reset threshold. Note that faults that are still present, as indicated in the STATUS1 and STATUS2 registers, will immediately reappear.

When accumulators (time, charge and energy) overflow, the corresponding bits in the STATUS2 register are set and will stay set. The accumulator overflow bits in the FAULT2 register will reappear after they have been cleared via I<sup>2</sup>C since the STATUS2 register continues to indicate overflow faults.

Figure 6. LTC2946 Fault Alert Generation Blocks

2946fa

If it is necessary to clear accumulator overflow fault(s), the recommended procedure is:

- 1. Read the accumulators

- 2. Store these values in an external memory

- 3. Issue a reset to the accumulators by writing bits CB[1:0] to [10]. Then disable reset by writing bits CB[1:0] to [00].

- 4. Write the stored values back to the accumulators

Steps 2 and 4 can be skipped if there is no need to continue the accumulation from present values.

#### I<sup>2</sup>C Interface

The LTC2946 includes an I<sup>2</sup>C/SMBus-compatible interface to provide access to the onboard registers. Figure 6 shows a general data transfer format using the I<sup>2</sup>C bus.

The LTC2946 is a read/write slave device and supports the SMBus read byte, write byte, read word and write word protocols. The LTC2946 also supports extended read and write commands that allow reading or writing more than two bytes of data. When using the read/write word or extended read and write commands, the bus master issues an initial register address and the internal register address

Figure 7. General Data Transfer Over I<sup>2</sup>C

| S | ADDRESS     | W | Α | COM | MAND                           | Α   | DATA  | Α   | P |          |                                                              |

|---|-------------|---|---|-----|--------------------------------|-----|-------|-----|---|----------|--------------------------------------------------------------|

|   | 1 1 0 a3:a0 | 0 | 0 | ХХ  | b5:b0                          | 0   | b7:b0 | 0   |   | 2946 F08 |                                                              |

|   | FROM MAST   |   |   |     | A: ACKN<br>Ā: NOT A<br>R: READ | ACK | NOWLE | DGI | , | 2010100  | W: WRITE BIT (LOW<br>S: START CONDITION<br>P: STOP CONDITION |

Figure 8. LTC2946 Serial Bus SDA Write Byte Protocol

| S | ADDRESS     | W | Α | COMMAND   | Α | DATA  | Α | DATA  | Α   | Р     |

|---|-------------|---|---|-----------|---|-------|---|-------|-----|-------|

|   | 1 1 0 a3:a0 | 0 | 0 | X X b5:b0 | 0 | b7:b0 | 0 | b7:b0 | 0   |       |

|   |             |   |   |           |   |       |   |       | 294 | 6 F09 |

Figure 9. LTC2946 Serial Bus SDA Write Word Protocol

| S | ADDRESS     | W | Α | COMMAND   | Α | DATA  | Α | DATA  | Α | <br>DATA  | Α   | Р     |

|---|-------------|---|---|-----------|---|-------|---|-------|---|-----------|-----|-------|

|   | 1 1 0 a3:a0 | 0 | 0 | X X b5:b0 | 0 | b7:b0 | 0 | b7:b0 | 0 | <br>b7:b0 | 0   |       |

|   |             |   |   |           |   |       |   |       |   |           | 294 | 6 F10 |

| Figure 10. LTC2 | 946 Serial E | Bus SDA Writ | e Page Protocol |

|-----------------|--------------|--------------|-----------------|

|-----------------|--------------|--------------|-----------------|

| S | ADDRESS     | W | Α | COMMAND   | Α | S | ADDRESS     | R | Α | DATA  | Ā   | P     |

|---|-------------|---|---|-----------|---|---|-------------|---|---|-------|-----|-------|

|   | 1 1 0 a3:a0 | 0 | 0 | X X b5:b0 | 0 |   | 1 1 0 a3:a0 | 1 | 0 | b7:b0 | 1   |       |

|   |             |   |   |           |   |   |             |   |   |       | 204 | C E11 |

Figure 11. LTC2946 Serial Bus SDA Read Byte Protocol

| S | ADDRESS     | W | Α | COMMAND   | Α | S | ADDRESS     | R | Α | DATA  | Α | DATA  | Ā | Р |

|---|-------------|---|---|-----------|---|---|-------------|---|---|-------|---|-------|---|---|

|   | 1 1 0 a3:a0 | 0 | 0 | X X b5:b0 | 0 |   | 1 1 0 a3:a0 | 1 | 0 | b7:b0 | 0 | b7:b0 | 1 |   |

Figure 12. LTC2946 Serial Bus SDA Read Word Protocol

| s | ADDRESS     | W | Α | COMMAND   | Α | S | ADDRESS     | R | Α | DATA  | Α | DATA  | <br>DATA  | Ā | Р |

|---|-------------|---|---|-----------|---|---|-------------|---|---|-------|---|-------|-----------|---|---|

|   | 1 1 0 a3:a0 | 0 | 0 | X X b5:b0 | 0 |   | 1 1 0 a3:a0 | 1 | 0 | b7:b0 | 0 | b7:b0 | <br>b7:b0 | 1 |   |

Figure 13. LTC2946 Serial Bus SDA Read Page Protocol Protocol

pointer automatically increments by 1 after each byte of data is read or written. After the register address reaches 43h, it will roll over to 00h and continue incrementing. A STOP condition resets the register address pointer to 00h. The data formats for the above commands are shown in Figure 7 through Figure 13. Note that only the read byte command is available to the E7 and E8 (MFR\_SPECIAL\_ID) registers (Table 2).

### I<sup>2</sup>C Device Addressing

Nine distinct  $I^2C$  bus addresses are configurable using the three-state pins ADR0 and ADR1, as shown in Table 1.

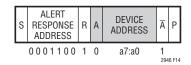

ADR0 and ADR1 should be tied to INTV<sub>CC</sub>, to GND, or left floating (NC) to configure the lower four address bits. During low power shutdown, the address select state is latched into memory powered from standby supply. Address bits a6, a5 and a4 are permanently set to 110b and the least significant bit is the R/ $\overline{W}$  bit. In addition, all LTC2946 devices will respond to a common mass write address 1100\_110b; this allows the bus master to write to several LTC2946s simultaneously, regardless of their individual address settings. The LTC2946 will also respond to the standard ARA address 0001\_100b if the GPI03 ( $\overline{ALERT}$ ) pin is asserted. See the Alert Response Protocol section for more details. The LTC2946 will not respond to the ARA address if no alerts are pending.

#### **START and STOP Conditions**

When the  $I^2C$  bus is idle, both SCL and SDA are in the HIGH state. A bus master signals the beginning of a transmission with a START condition by transitioning SDA from high to low while SCL stays high. When the master has finished communicating with the slave, it issues a STOP condition by transitioning SDA from LOW to high while SCL stays high. The bus is then free for another transmission.

#### Stuck-Bus Reset

The LTC2946 I<sup>2</sup>C interface features a stuck-bus reset timer to prevent it from holding the bus lines low indefinitely if the SCL signal is interrupted during a transfer. The timer starts when either SCL or SDAI is low, and resets when both SCL and SDAI are pulled high. If either SCL or SDAI are low for over 33ms, the stuck-bus timer will expire, and

the internal I<sup>2</sup>C interface and the SDAO pin pull-down logic will be reset to release the bus. Normal communication will resume at the next START command.

#### **Acknowledge**

The acknowledge signal is used for handshaking between the master and the slave to indicate that the last byte of data was received. The master always releases the SDA line during the acknowledge clock pulse. The LTC2946 will pull the SDA line low on the 9th clock cycle to acknowledge receipt of the data. If the slave fails to acknowledge by leaving SDA high, then the master can abort the transmission by generating a STOP condition. When the master is receiving data from the slave, the master must acknowledge the slave by pulling down the SDA line during the 9th clock pulse to indicate receipt of a data byte. After the last byte has been received by the master, it will leave the SDA line high (not acknowledge) and issue a STOP condition to terminate the transmission.

#### Write Protocol

The master begins a write operation with a START condition followed by the seven-bit slave address and the  $R/\overline{W}$  bit set to zero. After the addressed LTC2946 acknowledges the address byte, the master then sends a command byte that indicates which internal register the master wishes to write. The LTC2946 acknowledges this and then latches the lower six bits of the command byte into its internal register address pointer. The master then delivers the data byte and the LTC2946 acknowledges once more and writes the data into the internal register pointed to by the register address pointer. If the master continues sending additional data bytes with a write word or extended write command, the additional data bytes will be acknowledged by the LTC2946, the register address pointer will automatically increment by one, and data will be written as previously stated. The write operation terminates and the register address pointer resets to 00h when the master sends a STOP condition.

#### **Read Protocol**

The master begins a read operation with a START condition followed by the 7-bit slave address and the R/W bit set to zero. After the addressed LTC2946 acknowledges

20

the address byte, the master then sends a command byte that indicates which internal register the master wishes to read. The LTC2946 acknowledges this and then latches the lower six bits of the command byte into its internal register address pointer. The master then sends a repeated START condition followed by the same 7-bit address with the R/W bit now set to 1. The LTC2946 acknowledges and sends the contents of the requested register. The transmission terminates when the master sends a STOP condition. If the master acknowledges the transmitted data byte, as in a read word command, the LTC2946 will send the contents of the next register. If the master keeps acknowledging, the LTC2946 will keep incrementing the register address pointer and sending out data bytes. The read operation terminates and the register address pointer resets to 00h when the master sends a STOP condition.

#### **Alert Response Protocol**

When any of the fault bits in the FAULT1 and FAULT2 register are set, a bus alert is generated if the appropriate bit in the ALERT1 or ALERT2 register has been set and GPIO3 is configured as an ALERT output. This allows the bus master to select which faults will generate alerts. At power-up, both ALERT registers are cleared (no alerts enabled) and the GPIO3 (ALERT) pin is high. If an alert is enabled, the corresponding fault causes the GPIO3 (ALERT) pin to pull low. The bus master responds to the alert in accordance with the SMBus alert response protocol by broadcasting the alert response address 0001 100b, and the LTC2946 replies with its own address and releases its GPIO3 (ALERT) pin, as shown in Figure 14. The GPIO3 (ALERT) line is also released if CB[7] is set and the LTC2946 is addressed (see Table 4) by any message. The GPIO3 (ALERT) signal is not pulled low again until the FLT registers indicate a different fault has occurred or the original fault is cleared and it occurs again. Note that this means repeated or continuing faults will not generate additional alerts until the associated FLT register bits have been cleared.

Figure 14. LTC2946 Serial Bus SDA Alert Response Protocol

If two or more LTC2946s on the same bus are generating alerts when the ARA is broadcast, the bus master will repeat the alert response protocol until the GPIO3  $(\overline{ALERT})$  line is released. Standard I<sup>2</sup>C arbitration causes the device with the highest priority (lowest address) to reply first and the device with the lowest priority (highest address) to reply last.

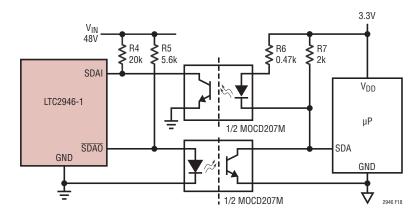

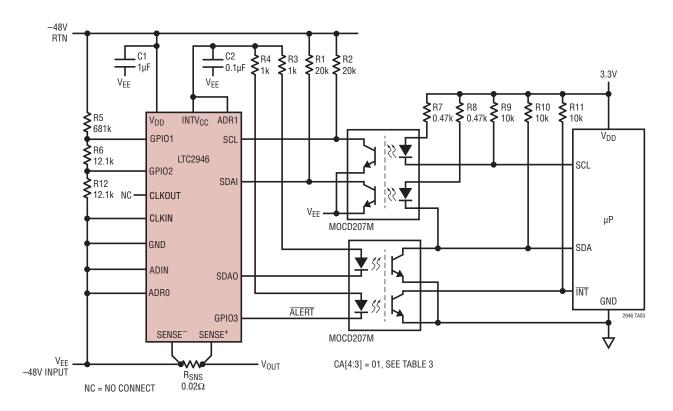

# Opto-Isolating the I<sup>2</sup>C Bus

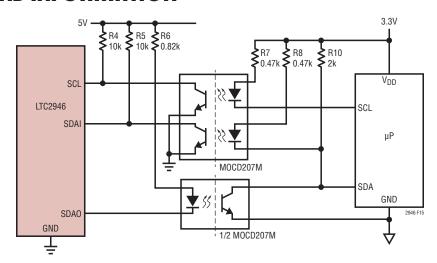

Opto-isolating a standard I<sup>2</sup>C device is complicated by the bidirectional SDA pin. The LTC2946/LTC2946-1 minimize this problem by splitting the standard I<sup>2</sup>C SDA line into SDAI (input) and SDAO (output, LTC2946) or SDAO (inverted output, LTC2946-1). The SCL is an input-only pin and does not require special circuitry to isolate. For conventional nonisolated I<sup>2</sup>C applications, use the LTC2946 and tie the SDAI and SDAO pins together to form a standard I<sup>2</sup>C SDA pin.

Low speed isolated interfaces that use standard opendrain opto-isolators can use the LTC2946 with the SDAI and SDAO pins separated, as shown in Figure 15. Connect SDAI to the output of the incoming opto-isolator with a pull-up resistor to INTV<sub>CC</sub> or a local 5V supply; connect SDAO to the cathode of the outgoing opto-isolator with a current-limiting resistor in series with the anode. The input and output must be connected together on the isolated side of the bus to allow the LTC2946 to participate in I<sup>2</sup>C arbitration. Note that maximum I<sup>2</sup>C bus speed will generally be limited by the speed of the opto-couplers used in this application.

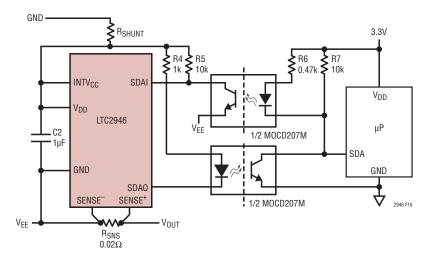

The shunt regulators can supply up to 34mA of current to drive opto-isolator and pull-up resistors, as shown in Figure 16 and Figure 17. For identical SDAI/SCL pull-up resistors the maximum load is:

$$I_{LOAD(MAX)} = V_{CCZ(MAX)} \cdot \left(\frac{2}{R5} + \frac{1}{R4}\right)$$

$$I_{LOAD(MAX)} = 6.7V \cdot \left(\frac{2}{R5} + \frac{1}{R4}\right)$$

(2)

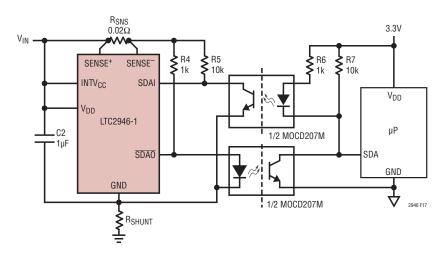

R<sub>SHUNT</sub> can then be calculated using Equation 1. Note that both LTC2946 and LTC2946-1 can be used in the shunt

2946fa

Figure 15. Opto-Isolation of a 10kHz I<sup>2</sup>C Interface Between LTC2946 and Microcontroller

Figure 16. Low Speed 10kHz Opto-Isolators Powered from Low Side Shunt Regulator (SCL Omitted for Clarity)

Figure 17. Low Speed 10kHz Opto-Isolators Powered from High Side Shunt Regulator (SCL Omitted for Clarity)

LINEAR TECHNOLOGY

regulator applications mentioned. Figure 18 shows an alternate connection for use with low speed opto-couplers and the LTC2946-1. This circuit uses a limited-current pull-up on the internally clamped SDAI pin and clamps the  $\overline{\text{SDAO}}$  pin with the input diode of the outgoing optoisolator, removing the need to use INTV<sub>CC</sub> for biasing in the absence of an auxiliary low voltage supply. For proper clamping:

$$\frac{V_{S(MAX)} - V_{SDA,SCL(MIN)}}{I_{SDA,SCL(MAX)}} \le R4 \le \frac{V_{S(MAX)} - V_{SDA,SCL(MAX)}}{I_{SDA,SCL(MIN)}}$$

(3)

$$\frac{V_{S(MAX)} - 5.9V}{5mA} \le R4 \le \frac{V_{S(MAX)} - 6.9V}{0.5mA}$$

As an example, a supply that operates from 36V to 72V would require the value of R4 to be between 13k and 58k.

The LTC2946-1 must be used in this application to ensure that the SDAO signal polarity is correct.

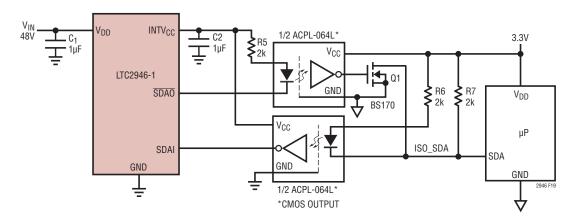

The LTC2946-1 can also be used with high speed optocouplers with push-pull outputs and inverted logic as shown in Figure 19. The incoming opto-isolator draws power from the INTV $_{CC}$ , and the data output is connected directly to the SDAI pin with no pull-up required. Ensure the current drawn does not exceed the 10mA maximum capability of the INTV $_{CC}$  pin. The  $\overline{\text{SDAO}}$  pin is connected to the cathode of the outgoing opto-coupler with a current limiting resistor connected back to INTV $_{CC}$ . An additional discrete N-channel MOSFET is required at the output of the outgoing opto-coupler to provide the open-drain pull-down that the I $^2$ C bus requires. Finally, the input of the incoming opto-isolator is connected back to the output as in the low speed case.

Figure 18. Opto-Isolation of a 1.5kHz I<sup>2</sup>C Interface Between LTC2946-1 and Microcontroller (SCL Omitted for Clarity)

Figure 19. Opto-Isolation of a I<sup>2</sup>C Interface with Low Power, High Speed Opto-Couplers (SCL Omitted for Clarity)

2946fa

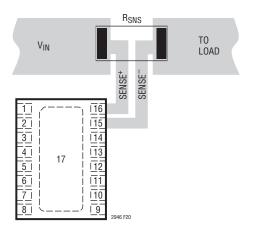

#### **Layout Considerations**

A Kelvin connection between the sense resistor  $R_{SNS}$  and the LTC2946 is recommended to achieve accurate current sensing (Figure 20). The recommended minimum trace width for 1oz copper foil is 0.02" per amp to ensure the trace stays at a reasonable temperature. Using 0.03" per amp or wider is preferred. Note that 1oz copper exhibits a sheet resistance of about  $530\mu\Omega$  per square. In very high current applications where the sense resistor can dissipate significant power, the PCB layout should include good thermal management techniques such as extra vias and wide metal area.

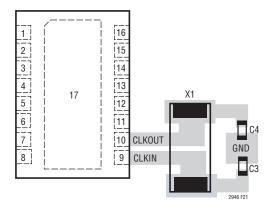

The crystal oscillator's clock amplitude is sensitive to parasitics such as stray capacitance on the CLKOUT pin and coupling between the CLKIN and CLKOUT pins. It is recommended that the CLKIN and CLKOUT traces from the LTC2946 to the crystal oscillator network be as short as practical with the load capacitors placed next to the crystal, as shown in Figure 21. To minimize stray capacitances, avoid large ground planes and digital signals near the crystal network.

Figure 20. Recommended Layout for Kelvin Connection

#### **Design Example**

Given a  $20m\Omega$  sense resistor, calculate the weight value per LSB for the current, power, charge and energy registers:

Current =  $25\mu V/LSB/R_{SNS}$

= 1.25mA/LSB

Voltage = 25mV/LSB

(SENSE+/V<sub>DD</sub> is sensing the voltage)

Power = 1.25mA/LSB • 25mV/LSB

$=31.25\mu\text{W/LSB}$

Time = 16.39543ms/LSB (default configuration

250kHz target frequency)

Charge = 1.25mA/LSB • 16 • 16.384ms/LSB

$= 327.9086 \mu C/LSB$

Energy =  $31.25\mu W \cdot 65536 \cdot 16.39543ms$

= 33.578mJ/LSB

Figure 21. Recommended Layout for Crystal Oscillator

Table 1. LTC2946 Device Addressing

| DESCRIPTION    | HEX DEVICE<br>ADDRESS | BINARY DEVICE ADDRESS |    |    |    |    |    |    |     | LTC2946<br>Address Pins |      |

|----------------|-----------------------|-----------------------|----|----|----|----|----|----|-----|-------------------------|------|

|                | h                     | a6                    | a5 | a4 | a3 | a2 | a1 | a0 | R/W | ADR1                    | ADRO |

| Mass Write     | CC                    | 1                     | 1  | 0  | 0  | 1  | 1  | 0  | 0   | Х                       | Х    |

| Alert Response | 19                    | 0                     | 0  | 0  | 1  | 1  | 0  | 0  | 1   | Х                       | Х    |

| 0              | CE                    | 1                     | 1  | 0  | 0  | 1  | 1  | 1  | Х   | Н                       | L    |

| 1              | D0                    | 1                     | 1  | 0  | 1  | 0  | 0  | 0  | Х   | NC                      | Н    |