**Dual Output PolyPhase** Step-Down DC/DC Voltage Mode Controller with Digital Power System Management

DESCRIPTION

### **FEATURES**

- PMBus/I<sup>2</sup>C Compliant Serial Interface

- Monitor Voltage, Current, Temperature and Faults

POWER BY

- Program Voltage, Soft-Start/Stop, Sequencing, Margining, AVP and UV/OV/OC Limits

- **3**  $V \leq VINSNS \leq 38V, 0.5V \leq V_{OUT} \leq 5.25V$

- ±0.5% Output Voltage Error

ANALOG DEVICES

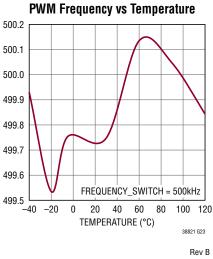

- Programmable PWM Frequency or External Clock Synchronization from 250kHz to 1.25MHz

- Accurate PolyPhase<sup>®</sup> Current Sharing

- Internal EEPROM with Fault Logging and ECC

- IC Supply Range: 3V to 13.2V

- **Resistor or Inductor DCR Current Sensing**

- Power Good Output Voltage Monitor

- **Optional Resistor Programming for Key Parameters**

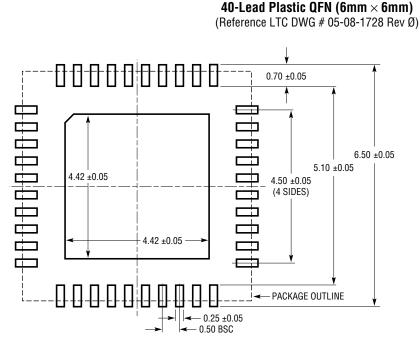

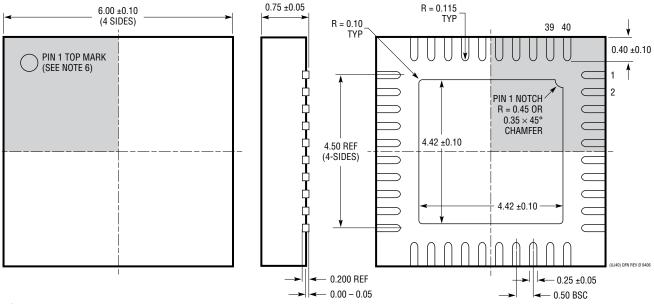

- 40-Pin (6mm × 6mm) QFN Package

- AEC-Q100 Qualified for Automotive Applications

### **APPLICATIONS**

- High Current Distributed Power Systems

- Servers, Network and Storage Equipment

- Intelligent Energy Efficient Power Regulation

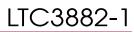

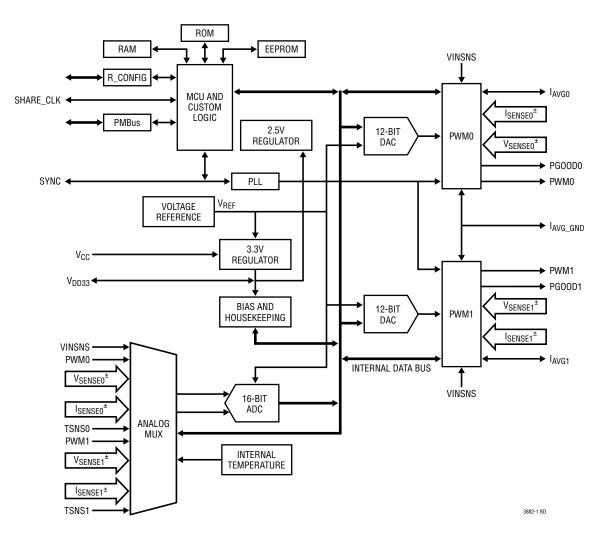

The LTC®3882-1 is a dual, PolyPhase DC/DC synchronous step-down switching regulator controller with PMBus compliant serial interface. It uses a constant frequency, leading-edge modulation, voltage mode architecture for excellent transient response and output regulation. Each PWM channel can produce output voltages from 0.5V to 5.25V using a wide range of 3.3V compatible power stages, including power blocks, DrMOS or discrete FET drivers. Up to four LTC3882-1 devices can operate in parallel for 2-, 3-, 4-, 6- or 8-phase operation.

System configuration and monitoring is supported by the LTpowerPlay<sup>™</sup> software tool. The LTC3882-1 serial interface can read back input voltage, output voltage and current, temperature and fault status. Most operating parameters can be set via the digital interface or stored in internal EEPROM for use at power up. Switching frequency and phase, output voltage and device address can also be set using external configuration resistors.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 5396245, 5859606, 6144194, 6937178, 7420359 and 7000125

# TABLE OF CONTENTS

| Features                                                                                                                            |            |

|-------------------------------------------------------------------------------------------------------------------------------------|------------|

| Applications                                                                                                                        | 1          |

| Typical Application                                                                                                                 | 1          |

| Description<br>Absolute Maximum Ratings                                                                                             | ]          |

| Absolute Maximum Ratings                                                                                                            | 4          |

| Order Information                                                                                                                   |            |

| Pin Configuration                                                                                                                   | 4          |

| Electrical Characteristics                                                                                                          | Ⴢ          |

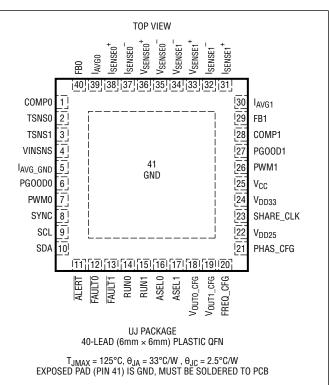

| Typical Performance Characteristics                                                                                                 | 9<br>₁ว    |

| Pin Functions<br>Block Diagram                                                                                                      | . IJ<br>15 |

|                                                                                                                                     |            |

| Test Circuit                                                                                                                        |            |

| Timing Diagram<br>Operation                                                                                                         |            |

| Overview                                                                                                                            |            |

| Main Control Loop                                                                                                                   |            |

| Power-Up and Initialization                                                                                                         | 10         |

| Soft-Start                                                                                                                          | 20         |

| Soft-Start<br>Time-Based Output Sequencing                                                                                          | 20         |

| Output Ramping Control                                                                                                              | 20         |

| Voltage-Based Output Sequencing                                                                                                     | 20         |

| Minimum Output Disable Times                                                                                                        | 21         |

| Output Short Cycle                                                                                                                  | 21         |

| Light Load Current Operation                                                                                                        | .21        |

| Switching Frequency and Phase                                                                                                       | .21        |

| PolyPhase Load Sharing                                                                                                              | .22        |

| Active Voltage Positioning                                                                                                          | .22        |

| Input Supply Monitoring                                                                                                             | .22        |

| Output Voltage Sensing and Monitoring                                                                                               | .22        |

| Output Current Sensing and Monitoring                                                                                               | .22        |

| External and Internal Temperature Sense                                                                                             | .23        |

| Resistor Configuration Pins<br>Internal EEPROM with CRC and ECC                                                                     | .23        |

| Internal EEPROM with CRC and ECC                                                                                                    | . 24       |

| Fault Detection                                                                                                                     | .24        |

| Input Supply Faults                                                                                                                 | .24        |

| Hardwired PWM Response to V <sub>OUT</sub> Faults                                                                                   | .24        |

| Power Good Indication (Master)                                                                                                      | .25        |

| Power Good Indication (Slave)<br>Hardwired PWM Response to I <sub>OUT</sub> Faults<br>Hardwired PWM Response to Temperature Faults. | .25        |

| Hardwired PWIM Response to Tout Faults                                                                                              | .25        |

| Hardwired PWW Response to Timing Faults.                                                                                            | . 20       |

| Hardwired PWM Response to Timing Faults                                                                                             | .20        |

| External Faults                                                                                                                     | .20        |

| Fault Handling<br><u>Status</u> Registers and <b>ALERT</b> Masking                                                                  | 20.        |

| FAULT Pin I/O                                                                                                                       | .20        |

| Fault Logging                                                                                                                       | 28         |

| Factory Default Operation                                                                                                           | .20        |

| Serial Interface                                                                                                                    | 32         |

| Serial Bus Addressing                                                                                                               | 32         |

| Serial Bus Timeout                                                                                                                  | .36        |

| Serial Communication Errors                                                                                                         | .36        |

|                                                                                                                                     | -          |

| PMBus Command Summary                                                                 | . 37 |

|---------------------------------------------------------------------------------------|------|

| PMBus Commands                                                                        | .37  |

| Data Formats                                                                          | . 37 |

| Data Formats                                                                          | . 42 |

| Efficiency Considerations                                                             | . 42 |

| PWM Frequency and Inductor Selection                                                  | . 42 |

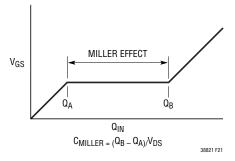

| PWM Frequency and Inductor Selection<br>Power MOSFET Selection                        | .43  |

| MOSFET Driver Selection                                                               | .44  |

| Using PWM Protocols                                                                   | .44  |

| CIN Selection                                                                         | .44  |

| C <sub>IN</sub> Selection<br>C <sub>OUT</sub> Selection<br>Feedback Loop Compensation | .45  |

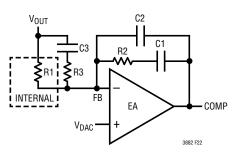

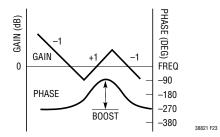

| Feedback Loop Compensation                                                            | .46  |

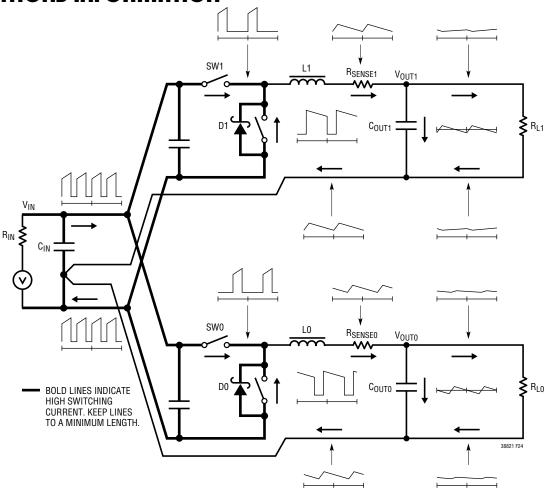

| PCB Layout Considerations                                                             | . 47 |

| Output Current Sensing                                                                | .48  |

| Output Voltage Sensing                                                                | .50  |

| Soft-Start and Stop                                                                   | . 51 |

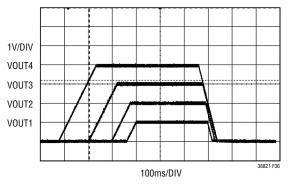

| Time-Based Output Sequencing and Ramping                                              | . 51 |

| Voltage-Based Output Sequencing                                                       | . 52 |

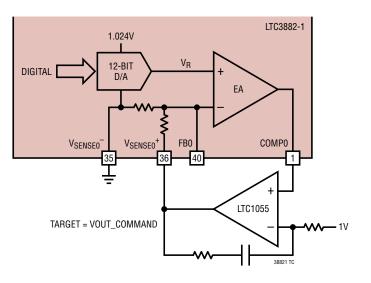

| Using Output Voltage Servo                                                            | .54  |

| Using AVP                                                                             | .54  |

| PWM Frequency Synchronization                                                         | .55  |

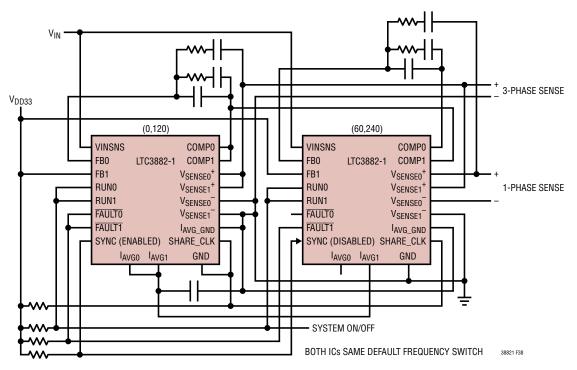

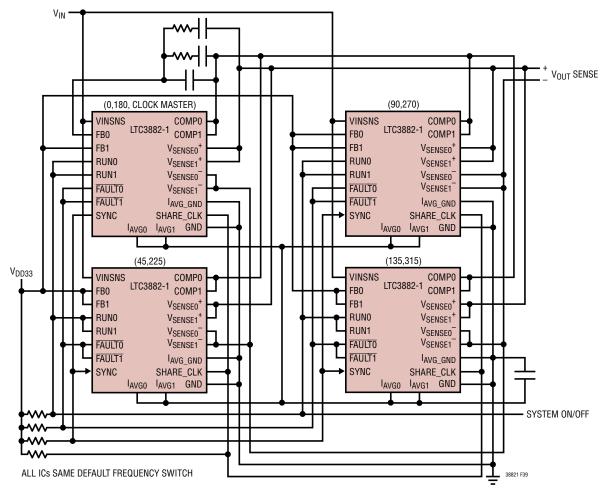

| PolyPhase Operation and Load Sharing                                                  | .56  |

| External Temperature Sense                                                            | .60  |

| Resistor Configuration Pins                                                           | .60  |

| Internal Regulator Outputs                                                            | .62  |

| IC Junction Temperature                                                               | .62  |

| Derating EEPROM Retention at Temperature                                              | .63  |

| Configuring Open-Drain Pins                                                           | .63  |

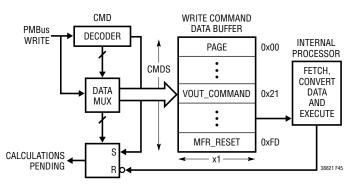

| PMBus Communication and Command Processing.                                           | 64   |

| Status and Fault Log Management                                                       | .65  |

| LTpowerPlay – An Interactive Digital Power GUI                                        | . 65 |

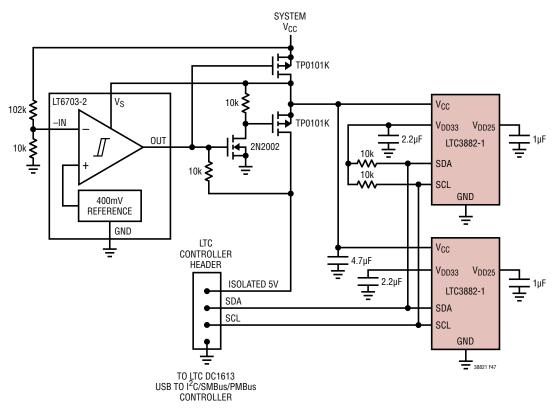

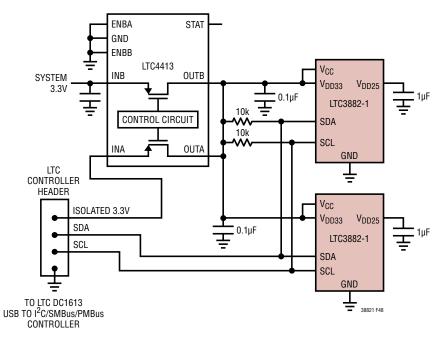

| Interfacing to the DC1613                                                             | .66  |

| Design Example PMBus COMMAND DETAILS                                                  | .66  |

| PMBus COMMAND DETAILS                                                                 | . 69 |

| Addressing and Write Protect                                                          | .69  |

| PAGE                                                                                  | .69  |

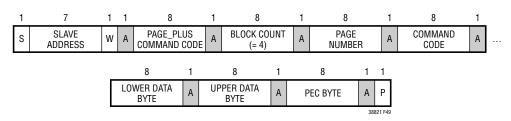

| PAGE_PLUS_WRITE                                                                       | . 69 |

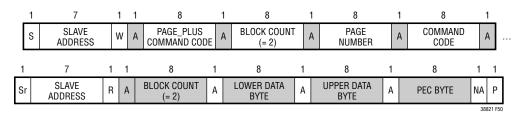

| PAGE_PLUS_READ                                                                        | .70  |

| WRITE_PROTECT                                                                         |      |

| MFR_ADDRESS                                                                           | .71  |

| MFR_RAIL_ADDRESS                                                                      | .71  |

| General Device Configuration                                                          | . /1 |

| PMBUS_REVISION                                                                        | . /1 |

| CAPABILITY                                                                            | . /1 |

| On, Off and Margin Control                                                            | . 72 |

| ÓN_OFF_CONFIG                                                                         | . /2 |

| MFR_CONFIG_ALL_LTC3882-1                                                              | . /2 |

| OPERATION.                                                                            | . /3 |

| MFR_RESET                                                                             | . /3 |

| PWM Configuration                                                                     | . /4 |

| FREQUENCY_SWITCH                                                                      | . 74 |

Rev B

# TABLE OF CONTENTS

| MFR PWM CONFIG LTC3882-1           | 75 |

|------------------------------------|----|

| MFR_CHAN_CONFIG_LTC3882-1          |    |

| MFR_PWM_MODE_LTC3882-1             |    |

| Input Voltage and Limits           |    |

| VIN ON                             | 78 |

| VIN_OFF                            |    |

| VIN_OV_FAULT_LIMIT                 | 78 |

| VIN UV WARN LIMIT                  |    |

| Output Voltage and Limits          |    |

| VOUT MODE                          | 79 |

| VOUT_COMMAND                       | 79 |

| MFR VOUT MAX                       |    |

| VOUT_MAX                           |    |

| MFR_VOUT_AVP                       | 80 |

| VOUT_MARGIN_HIGH                   |    |

| VOUT_MARGIN_LOW                    | 80 |

| VOUT_OV_FAULT_LIMIT                | 80 |

| VOUT_OV_WARN_LIMIT                 | 81 |

| VOUT_UV_WARN_LIMIT                 |    |

| VOUT_UV_FAULT_LIMIT                |    |

| Output Current and Limits          | 82 |

| IOUT_CAL_GAIN                      | 82 |

| MFR_IOUT_CAL_GAIN_TC               | 02 |

| IOUT_OC_FAULT_LIMIT                | 02 |

| IOUT_OC_WARN_LIMIT                 | 02 |

| Output Timing, Delays, and Ramping |    |

| MFR RESTART DELAY                  | 00 |

| TON DELAY                          |    |

| TON RISE                           |    |

| TON_MAX_FAULT_LIMIT                | 84 |

| VOUT_TRANSITION_RATE               |    |

| TOFF DELAY                         |    |

| TOFF FALL                          |    |

| TOFF_MAX_WARN_LIMIT                |    |

| External Temperature and Limits    | 85 |

| MFR TEMP 1 GAIN                    | 85 |

| MFR_TEMP_1_OFFSET                  |    |

| OT FAULT LIMIT                     |    |

| OT_WARN_LIMIT                      |    |

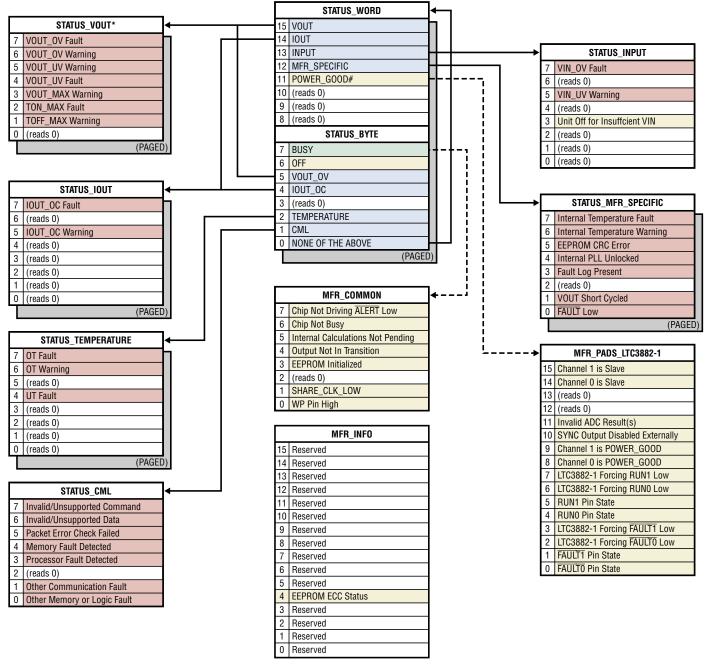

| Status Reporting                   |    |

| STATUS_BYTE                        | 86 |

| ŬT_FAŬĒT_LIMIT                     | 86 |

| STATUS_WORD                        | 87 |

| STATUS VOUT                        |    |

| STATUS IOUT                        |    |

| STATUS INPUT                       |    |

| STATUS TEMPERATURE                 | 88 |

| STATUS CML                         | 88 |

| STATUS_CML<br>STATUS_MFR_SPECIFIC  |    |

| MFR PADS LTC3882-1                 |    |

| MFR_COMMON                         | 90 |

|                                    |    |

| MFR_INFO                               |            |

|----------------------------------------|------------|

| _ CLEAR_FAULTS                         |            |

| Telemetry                              |            |

| READ_VIN                               |            |

| MFR_VIN_PEAK                           |            |

| READ_VOUT                              |            |

| MFR_VOUT_PEAK                          |            |

| READ_IOUT<br>MFR IOUT PEAK             |            |

| READ_POUT                              |            |

| READ_TEMPERATURE_1                     | 22<br>22   |

| MFR TEMPERATURE 1 PEAK                 | 92<br>92   |

| READ_TEMPERATURE_2                     |            |

| MFR TEMPERATURE 2 PEAK                 |            |

| READ_DUTY_CYCLE                        |            |

| READ FREQUENCY                         |            |

| MFR_CLEAR_PEAKS                        | 93         |

| Fault Response and Communication       | 94         |

| VIN OV FAULT RESPONSE                  | 94         |

| VOUT_OV_FAULT_RESPONSE                 | 95         |

| VOUT_UV_FAULT_RESPONSE                 | 95         |

| IOUT_OC_FAULT_RESPONSE                 |            |

| OT_FAULT_RESPONSE                      |            |

| UT_FAULT_RESPONSE                      |            |

| MFR_OT_FAULT_RESPONSE                  |            |

| TON_MAX_FAULT_RESPONSE                 |            |

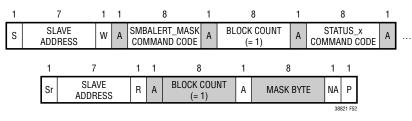

| MFR_RETRY_DELAY<br>SMBALERT MASK       |            |

| MFR_FAULT_PROPAGATE_LTC3882-1          | 9090<br>00 |

| MFR_FAULT_RESPONSE                     |            |

| MFR FAULT LOG                          |            |

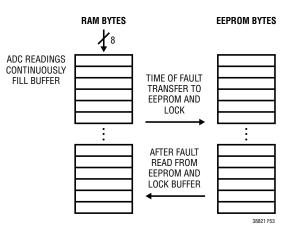

| Fault Log Operation                    |            |

| MFR_FAULT_LOG_CLEAR                    |            |

| EEPROM User Access                     |            |

| STORE_USER_ALL                         |            |

| RESTORE_USER_ALL                       | 102        |

| MFR_COMPARE_USER_ALL                   |            |

| MFR_FAULT_LOG_STORE                    | 103        |

| MFR_EE_xxxx                            |            |

| USER_DATA_0x                           |            |

| Unit Identification                    |            |

| MFR_ID                                 | 103        |

| MFR_MODEL                              |            |

| MFR_SERIAL                             |            |

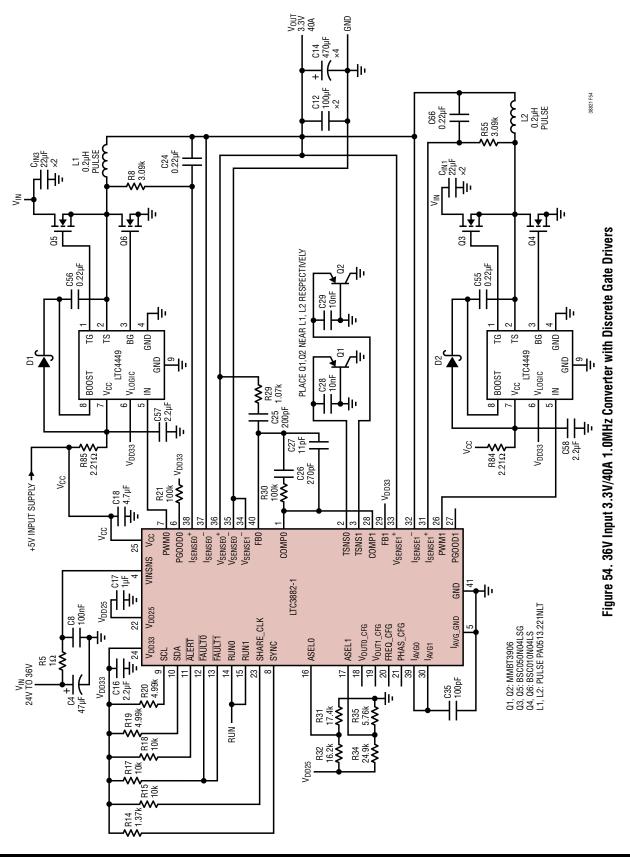

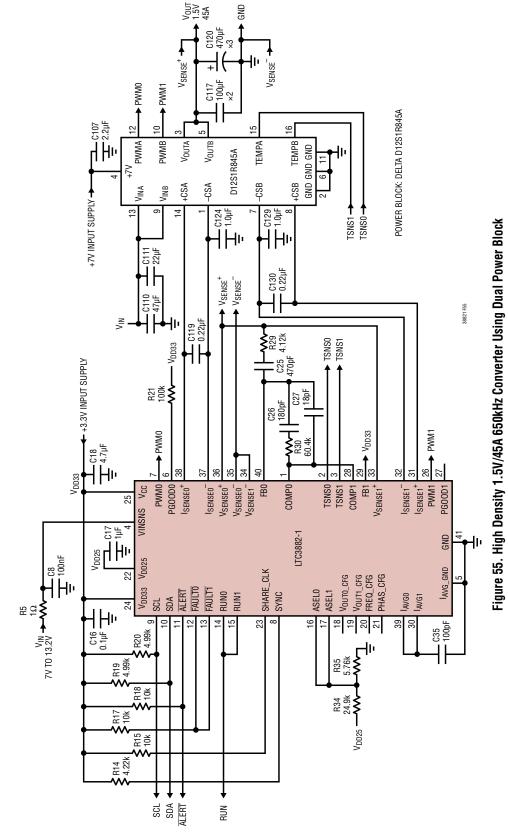

| MFR_SPECIAL_ID<br>Typical Applications | 103<br>104 |

| Package Description                    | 104<br>106 |

| Revision History                       | 100        |

| Typical Application                    | 107        |

| Related Parts                          | 108        |

|                                        |            |

### **ABSOLUTE MAXIMUM RATINGS**

(Note 1)

| V <sub>CC</sub> Supply Voltage0.3V to 15V<br>VINSNS Voltage0.3V to 40V                               |

|------------------------------------------------------------------------------------------------------|

| V <sub>SENSE</sub> <i>n</i> <sup>-</sup> 0.3V to 1V                                                  |

| $V_{\text{SENSE}n^+}$ , $I_{\text{SENSE}n^+}$ , $I_{\text{SENSE}n^-}$                                |

| FB <i>n</i> , COMP <i>n</i> , TSNS <i>n</i> , I <sub>AVG GND</sub> , I <sub>AVGn</sub> –0.3V to 3.6V |

| SYNC, FAULTIN, PGOOD n, SHARE_CLK0.3V to 3.6V                                                        |

| SCL, SDA, RUN <i>n</i> , ALERT–0.3V to 5.5V                                                          |

| ASEL <i>n</i> , VOUT <i>n</i> _CFG, FREQ_CFG,                                                        |

| PHAS_CFG0.3V to 2.75V                                                                                |

| PWM <i>n</i> , V <sub>DD25</sub> (Note 13)                                                           |

| V <sub>DD33</sub> (Note 14)                                                                          |

| Operating Junction Temperature                                                                       |

| (Notes 2, 3)40°C to 125°C*                                                                           |

| Storage Temperature Range65°C to 150°C*                                                              |

\*See Derating EEPROM Retention at Temperature in the Applications Information section for junction temperatures in excess of 125°C.

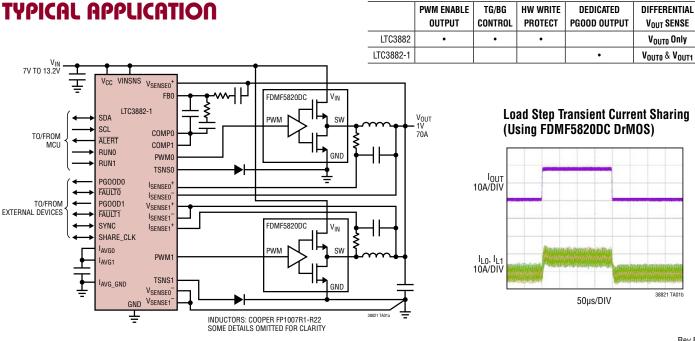

### PIN CONFIGURATION

### **ORDER INFORMATION**

| LEAD FREE FINISH      | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION                            | TEMPERATURE RANGE |  |  |  |

|-----------------------|---------------------|---------------|------------------------------------------------|-------------------|--|--|--|

| LTC3882EUJ-1#PBF      | LTC3882EUJ-1#TRPBF  | LTC3882UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN                | -40°C to 125°C    |  |  |  |

| LTC3882IUJ-1#PBF      | LTC3882IUJ-1#TRPBF  | LTC3882UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN –40°C to 125°C |                   |  |  |  |

| AUTOMOTIVE PRODUCTS** |                     |               |                                                |                   |  |  |  |

| LTC3882EUJ-1#WPBF     | LTC3882EUJ-1#WTRPBF | LTC3882UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN                | -40°C to 125°C    |  |  |  |

| LTC3882IUJ-1#WPBF     | LTC3882IUJ-1#WTRPBF | LTC3882UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN                | -40°C to 125°C    |  |  |  |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

\*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_J = 25^{\circ}C$  (Note 2).  $V_{CC} = 5V$ ,  $V_{SENSE0}^+ = V_{SENSE1}^+ = 1.8V$ ,  $V_{SENSE0}^- = V_{SENSE1}^- = I_{AVG\_GND} = GND = 0V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL                   | PARAMETER                                                            | CONDITIONS                                                                                                            |   | MIN      | ТҮР          | MAX      | UNITS       |

|--------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---|----------|--------------|----------|-------------|

| IC Supply                | 1                                                                    | -                                                                                                                     |   |          |              |          |             |

| V <sub>CC</sub>          | V <sub>CC</sub> Voltage Range                                        | V <sub>DD33</sub> = Internal LDO                                                                                      |   | 4.5      |              | 13.8     | V           |

| V <sub>DD33_EXT</sub>    | V <sub>DD33</sub> Voltage Range                                      | $V_{CC} = V_{DD33}$ (Note 6)                                                                                          | • | 3        |              | 3.6      | V           |

| V <sub>UVLO</sub>        | Undervoltage Lockout Threshold                                       | V <sub>DD33</sub> Rising<br>Hysteresis                                                                                |   |          | 42           | 3        | V<br>mV     |

| IQ                       | IC Operating Current                                                 |                                                                                                                       |   |          | 32           |          | mA          |

| t <sub>INIT</sub>        | Controller Initialization Time                                       | Delay from RESTORE_USER_ALL, MFR_RESET or V <sub>DD33</sub> > V <sub>UVLO</sub> Until TON_DELAY Can Begin             |   |          | 35           |          | ms          |

| V <sub>DD33</sub> Linear | Regulator                                                            |                                                                                                                       |   |          |              |          |             |

| V <sub>DD33</sub>        | V <sub>DD33</sub> Regulator Output Voltage                           | $V_{CC} \ge 4.5V$                                                                                                     |   | 3.2      | 3.3          | 3.4      | V           |

| I <sub>DD33</sub>        | V <sub>DD33</sub> Current Limit                                      | V <sub>DD33</sub> = 2.8V<br>V <sub>DD33</sub> = 0V                                                                    |   |          | 85<br>40     |          | mA<br>mA    |

| V <sub>DD25</sub> Linear | Regulator                                                            |                                                                                                                       |   |          |              |          |             |

| V <sub>DD25</sub>        | V <sub>DD25</sub> Regulator Output Voltage                           |                                                                                                                       |   | 2.25     | 2.5          | 2.75     | V           |

| I <sub>DD25</sub>        | V <sub>DD25</sub> Current Limit                                      |                                                                                                                       |   |          | 95           |          | mA          |

| PWM Control              | Loops                                                                |                                                                                                                       |   |          |              |          |             |

| VINSNS                   | V <sub>IN</sub> Sense Voltage Range                                  |                                                                                                                       |   | 3        |              | 38       | V           |

| R <sub>VINSNS</sub>      | VINSNS Input Resistance                                              |                                                                                                                       |   |          | 278          |          | kΩ          |

| V <sub>OUT_R0</sub>      | Range 0 Maximum V <sub>OUT</sub><br>Range 0 Set Point Error (Note 7) | $0.6V \le V_{OUT} \le 5V$<br>$0.6V \le V_{OUT} \le 5V$                                                                |   | -0.5     | 5.25<br>±0.2 | 0.5      | V<br>%<br>% |

|                          | Range 0 Set Point Resolution                                         |                                                                                                                       |   | 0.0      | 1.375        | 0.0      | mV          |

| V <sub>OUT_R1</sub>      | Range 1 Maximum V <sub>OUT</sub><br>Range 1 Set Point Error (Note 7) | $0.6V \le V_{OUT} \le 2.5V$<br>$0.6V \le V_{OUT} \le 2.5V$                                                            |   | -0.5     | 2.65<br>±0.2 | 0.5      | V<br>%<br>% |

|                          | Range 1 Set Point Resolution                                         |                                                                                                                       |   |          | 0.6875       | 0.0      | mV          |

| IVSENSE                  | V <sub>SENSE</sub> Input Current                                     | V <sub>SENSE</sub> <sup>+</sup> = 5.5V<br>V <sub>SENSE</sub> <sup>-</sup> = 0V                                        |   |          | 235<br>335   |          | μA<br>μA    |

| VLINEREG                 | V <sub>CC</sub> Line Regulation, No Output Servo                     | $4.5V \le V_{CC} \le 13.2V$ (See Test Circuit)                                                                        |   | -0.02    |              | 0.02     | %/V         |

| AVP                      | AVP $\Delta V_{OUT}$                                                 | AVP = 10%, VOUT_COMMAND = 1.8V,<br>I <sub>SENSE</sub> Differential Step 3mV to 12mV<br>with IOUT_OC_WARN_LIMIT = 15mV |   | -118     | -108         | -96      | mV          |

| A <sub>V(OL)</sub>       | Error Amplifier Open-Loop Voltage Gain                               |                                                                                                                       |   |          | 87           |          | dB          |

| SR                       | Error Amplifier Slew Rate                                            |                                                                                                                       |   |          | 9.5          |          | V/µs        |

| f <sub>0dB</sub>         | Error Amplifier Bandwidth                                            | (Note 12)                                                                                                             |   |          | 30           |          | MHz         |

| I <sub>COMP</sub>        | Error Amplifier Output Current                                       | Sourcing<br>Sinking                                                                                                   |   |          | -2.6<br>34   |          | mA<br>mA    |

| R <sub>VSFB</sub>        | Resistance Between V <sub>SENSE</sub> <sup>+</sup> and FB            | Range 0<br>Range 1                                                                                                    |   | 52<br>37 | 67<br>49     | 83<br>61 | kΩ<br>kΩ    |

| VISENSE                  | I <sub>SENSE</sub> Differential Input Range                          |                                                                                                                       |   |          | ±70          |          | mV          |

| IISENSE                  | I <sub>SENSE</sub> <sup>±</sup> Input Current                        | $0V \le V_{PIN} \le 5.5V$                                                                                             |   | -1       | ±0.1         | 1        | μA          |

| I <sub>AVG_VOS</sub>     | I <sub>AVG</sub> Current Sense Offset                                | Referred to I <sub>SENSE</sub> Inputs                                                                                 | • | -600     | ±175         | 650      | μV<br>μV    |

| V <sub>SIOS</sub>        | Slave Current Sharing Offset                                         | Referred to I <sub>SENSE</sub> Inputs                                                                                 | • | -800     | ±300         | 700      | μV<br>μV    |

| f <sub>SYNC</sub>        | SYNC Frequency Error                                                 | $250$ kHz $\leq f_{SYNC} \leq 1.25$ MHz                                                                               | • | -10      |              | 10       | %           |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_J = 25^{\circ}C$  (Note 2).  $V_{CC} = 5V$ ,  $V_{SENSE0}^+ = V_{SENSE1}^+ = 1.8V$ ,  $V_{SENSE0}^- = V_{SENSE1}^- = I_{AVG\_GND} = GND = 0V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL                  | PARAMETER                                                                                                  | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                |   | MIN                  | ТҮР                                  | MAX               | UNITS                        |

|-------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|--------------------------------------|-------------------|------------------------------|

| Input Voltage Su        | pervisor                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                              |

| V <sub>ON_TOL</sub>     | Input ON/OFF Threshold Error                                                                               | $15V \le V_{IN}ON \le 35V$                                                                                                                                                                                                                                                                                                                                                |   | -2                   |                                      | 2                 | %                            |

| N <sub>VON</sub>        | Input ON/OFF Threshold Resolution                                                                          |                                                                                                                                                                                                                                                                                                                                                                           |   |                      | 143                                  |                   | m۷                           |

| Output Voltage S        | Supervisors                                                                                                |                                                                                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                              |

| V <sub>UVOV_R0</sub>    | Range O Maximum Threshold<br>Range O Error<br>Range O Threshold Resolution                                 | $2V \le V_{OUT} \le 5V$ (Falling for UV and Rising for OV)                                                                                                                                                                                                                                                                                                                | • | -1                   | 5.5<br>11                            | 1                 | V<br>%<br>mV                 |

| <u></u>                 | Range 0 Threshold Hysteresis                                                                               |                                                                                                                                                                                                                                                                                                                                                                           | _ |                      | 0.75                                 | 54                | mV                           |

| V <sub>UVOV_R1</sub>    | Range 1 Maximum Threshold<br>Range 1 Error<br>Range 1 Threshold Resolution<br>Range 1 Threshold Hysteresis | $1V \leq V_{OUT} \leq 2.5V$ (Falling for UV and Rising for OV)                                                                                                                                                                                                                                                                                                            | • | -1                   | 2.75<br>5.5                          | 1<br>27           | V<br>%<br>mV<br>mV           |

| <b>Output Current S</b> | upervisors                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                              |

| VILIM_TOL               | Output Current Limit Tolerance<br>I <sub>SENSE</sub> <sup>+</sup> – I <sub>SENSE</sub> <sup>-</sup>        | $\begin{array}{l} 15mV < I_{SENSE}^+ - I_{SENSE}^- \leq 30mV \\ 30mV < I_{SENSE}^+ - I_{SENSE}^- \leq 50mV \\ 50mV < I_{SENSE}^+ - I_{SENSE}^- \leq 70mV \end{array}$                                                                                                                                                                                                     | • | -1.7<br>-2.5<br>-5.2 |                                      | 1.7<br>2.5<br>5.2 | mV<br>mV<br>mV               |

| N <sub>ILIM</sub>       | I <sub>SENSE</sub> <sup>+</sup> – I <sub>SENSE</sub> <sup>–</sup> Threshold Resolution                     | 1LSB                                                                                                                                                                                                                                                                                                                                                                      |   |                      | 0.4                                  |                   | mV                           |

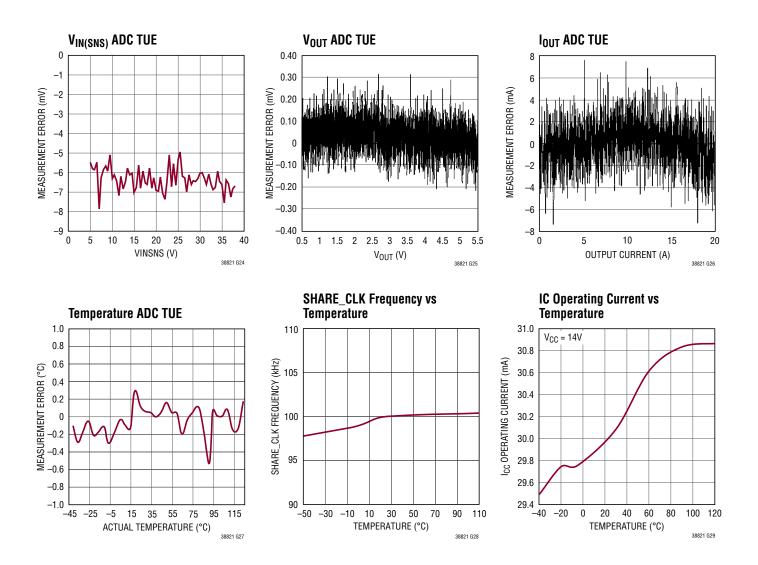

| ADC Readback T          | elemetry (Note 8)                                                                                          |                                                                                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   | ·                            |

| N <sub>VIN</sub>        | VINSNS Readback Resolution                                                                                 | (Note 9)                                                                                                                                                                                                                                                                                                                                                                  |   |                      | 10                                   |                   | Bits                         |

| V <sub>IN_TUE</sub>     | VINSNS Total Unadjusted Readback Error                                                                     | $4.5V \le VINSNS \le 38V$                                                                                                                                                                                                                                                                                                                                                 | • |                      |                                      | 0.5<br>2          | %                            |

| N <sub>DC</sub>         | PWM Duty Cycle Resolution                                                                                  | (Note 9)                                                                                                                                                                                                                                                                                                                                                                  |   |                      | 10                                   |                   | Bits                         |

| DC <sub>TUE</sub>       | PWM Duty Cycle Total Unadjusted<br>Readback Error                                                          | PWM Duty Cycle = 12.5%                                                                                                                                                                                                                                                                                                                                                    |   | -2                   |                                      | 2                 | %                            |

| N <sub>VOUT</sub>       | V <sub>OUT</sub> Readback Resolution                                                                       |                                                                                                                                                                                                                                                                                                                                                                           |   |                      | 244                                  |                   | μV                           |

| V <sub>OUT_TUE</sub>    | V <sub>OUT</sub> Total Unadjusted Readback Error                                                           | $0.6V \leq V_{OUT} \leq 5.5V$ , Constant Load                                                                                                                                                                                                                                                                                                                             | • | -0.5                 | ±0.2                                 | 0.5               | %                            |

| N <sub>ISENSE</sub>     | I <sub>OUT</sub> Readback Resolution<br>LSB Step Size (at I <sub>SENSE</sub> *)                            | $ \begin{array}{l} (\text{Note 9}) \\ 0\text{mV} \leq  I_{\text{SENSE}^+} - I_{\text{SENSE}^-}  < 16\text{mV} \\ 16\text{mV} \leq  I_{\text{SENSE}^+} - I_{\text{SENSE}^-}  < 32\text{mV} \\ 32\text{mV} \leq  I_{\text{SENSE}^+} - I_{\text{SENSE}^-}  < 63.9\text{mV} \\ 63.9\text{mV} \leq  I_{\text{SENSE}^+} - I_{\text{SENSE}^-}  \leq 70\text{mV} \\ \end{array} $ |   |                      | 10<br>15.625<br>31.25<br>62.5<br>125 |                   | Bits<br>μV<br>μV<br>μV<br>μV |

| ISENSE_TUE              | I <sub>OUT</sub> Total Unadjusted Readback Error                                                           | $  _{SENSE}^+ -  _{SENSE}^-  \ge 6mV$ , $0V \le V_{OUT} \le 5.5V$                                                                                                                                                                                                                                                                                                         |   | -1                   |                                      | 1                 | %                            |

| I <sub>SENSE_OS</sub>   | I <sub>OUT</sub> Zero-Code Offset Voltage                                                                  |                                                                                                                                                                                                                                                                                                                                                                           |   |                      | ±32                                  |                   | μV                           |

| N <sub>TEMP</sub>       | Temperature Resolution                                                                                     |                                                                                                                                                                                                                                                                                                                                                                           |   |                      | 0.25                                 |                   | 0°                           |

| T <sub>EXT_TUE</sub>    | External Temperature Total Unadjusted<br>Readback Error                                                    | TSNS0, TSNS1 ≤ 1.85V (Note 10)<br>MFR_PWM_MODE_LTC3882-1[6] = 0<br>MFR_PWM_MODE_LTC3882-1[6] = 1                                                                                                                                                                                                                                                                          | • | -3<br>-7             |                                      | 3<br>7            | 0°<br>0°                     |

| T <sub>INT_TUE</sub>    | Internal Temperature Total Unadjusted<br>Readback Error                                                    | Internal Diode (Note 10)                                                                                                                                                                                                                                                                                                                                                  |   |                      | ±1                                   |                   | °C                           |

| t <sub>CONVERT</sub>    | Update Rate                                                                                                | (Note 11)                                                                                                                                                                                                                                                                                                                                                                 |   |                      | 90                                   |                   | ms                           |

| Internal EEPRON         | A (Notes 4, 6)                                                                                             |                                                                                                                                                                                                                                                                                                                                                                           |   |                      |                                      |                   |                              |

| Endurance               | Number of Write Operations                                                                                 | $0^{\circ}C \le T_J \le 85^{\circ}C$ During All Write Operations                                                                                                                                                                                                                                                                                                          |   | 10,000               |                                      |                   | Cycles                       |

| Retention               | Stored Data Retention                                                                                      | T <sub>J</sub> ≤ 125°C                                                                                                                                                                                                                                                                                                                                                    |   | 10                   |                                      |                   | Years                        |

| Mass Write Time         | STORE_USER_ALL Execution Duration                                                                          | $0^{\circ}C \le T_{J} \le 85^{\circ}C$ During All Write Operations                                                                                                                                                                                                                                                                                                        |   |                      | 0.2                                  | 2                 | S                            |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_J = 25^{\circ}C$  (Note 2).  $V_{CC} = 5V$ ,  $V_{SENSE0}^+ = V_{SENSE1}^+ = 1.8V$ ,  $V_{SENSE0}^- = V_{SENSE1}^- = I_{AVG\_GND} = GND = 0V$ ,  $f_{SYNC} = 500$ kHz (externally driven) unless otherwise specified.

| SYMBOL               | PARAMETER                                                                                         | PARAMETER CONDITIONS                                                                                                                                                                                                                                                                                 |   |                |         | MAX         | UNITS                                        |

|----------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|---------|-------------|----------------------------------------------|

| Digital Inputs       | s (SCL, SDA, RUN <i>n</i> , FAULT <i>n</i> , SYNC, SHARE_(                                        | CLOCK)                                                                                                                                                                                                                                                                                               |   |                |         |             | <u>.                                    </u> |

| V <sub>IH</sub>      | Input High Voltage                                                                                | SCL, SDA, RUNO, RUN1, FAULTO, FAULT1<br>SYNC, SHARE_CLK                                                                                                                                                                                                                                              | • | 1.35<br>1.8    |         |             | V<br>V                                       |

| V <sub>IL</sub>      | Input Low Voltage                                                                                 | SCL, SDA, RUNO, RUN1, FAULTO, FAULT1<br>SYNC, SHARE_CLK                                                                                                                                                                                                                                              | • |                |         | 0.8<br>0.6  | V<br>V                                       |

| V <sub>HYST</sub>    | Input Hysteresis                                                                                  | SCL, SDA                                                                                                                                                                                                                                                                                             |   |                | 80      |             | mV                                           |

| C <sub>IN</sub>      | Input Capacitance                                                                                 | SCL, SDA, RUNO, RUN1, FAULTO, FAULT1, SYNC, SHARE_CLK (Note 12)                                                                                                                                                                                                                                      |   |                |         | 10          | pF                                           |

| t <sub>FILT</sub>    | Input Digital Filter Delay                                                                        | FAULTO, FAULT1<br>RUNO, RUN1                                                                                                                                                                                                                                                                         |   |                | 3<br>10 |             | μs<br>µs                                     |

| Digital Outpu        | its (SCL, SDA, RUN <i>n</i> , FAULT <i>n</i> , SYNC, SHARE                                        | _CLOCK, ALERT, PWM <i>n</i> , PGOOD <i>n</i> )                                                                                                                                                                                                                                                       |   |                |         |             |                                              |

| V <sub>OL</sub>      | Output Low Voltage                                                                                | I <sub>SINK</sub> = 3mA; SDA, SCL, RUN <u>0, RUN1, FAULT0,</u><br>FAULT1, SYNC, SHARE_CLK, ALERT,<br>I <sub>SINK</sub> = 2mA; PWM <i>n</i> , PGOOD <i>n</i>                                                                                                                                          | • |                | 0.2     | 0.4<br>0.3  | V<br>V                                       |

| V <sub>OH</sub>      | PWM <i>n</i> Output High Voltage                                                                  | $I_{\text{SOURCE}} = 2\text{mA}$                                                                                                                                                                                                                                                                     | • | 2.7            |         | 0.0         | V                                            |

| ILKG                 | Output Leakage Current                                                                            | $\begin{array}{l} \text{OV} \leq \text{PWM0, PWM1, PG00D0, PG00D1} \leq \text{V}_{\text{DD33}} \\ \text{OV} \leq \text{FAULT0, FAULT1, SYNC, SHARE_CLK} \leq 3.6\text{V} \\ \text{OV} \leq \text{RUN0, RUN1} \leq 5.5\text{V} \\ \text{OV} \leq \text{SCL, SDA, ALERT} \leq 5.5\text{V} \end{array}$ |   | -1<br>-5<br>-5 |         | 1<br>5<br>5 | μΑ<br>μΑ<br>μΑ                               |

| t <sub>R0</sub>      | PWM <i>n</i> Output Rise Time                                                                     | $C_{LOAD} = 30pF, 10\% \text{ to } 90\%$                                                                                                                                                                                                                                                             | • | 0              | 5       | 0           | ns                                           |

| t <sub>FO</sub>      | PWM <i>n</i> Output Fall Time                                                                     | $C_{1 \text{ (AD)}} = 30 \text{ pF}, 90\% \text{ to } 10\%$                                                                                                                                                                                                                                          |   |                | 4       |             | ns                                           |

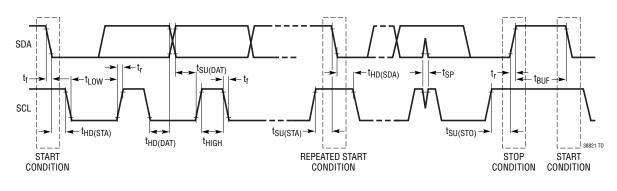

| Serial Bus Ti        |                                                                                                   |                                                                                                                                                                                                                                                                                                      | ļ |                |         |             |                                              |

| f <sub>SMB</sub>     | Serial Bus Operating Frequency                                                                    |                                                                                                                                                                                                                                                                                                      |   | 10             |         | 400         | kHz                                          |

| t <sub>BUF</sub>     | Bus Free Time Between Stop and Start                                                              |                                                                                                                                                                                                                                                                                                      | • | 1.3            |         |             | μs                                           |

| t <sub>HD,STA</sub>  | Hold Time After (Repeated) Start<br>Condition. After This Period, the First<br>Clock Is Generated |                                                                                                                                                                                                                                                                                                      | • | 0.6            |         |             | μs                                           |

| t <sub>SU,STA</sub>  | Repeated Start Condition Setup Time                                                               |                                                                                                                                                                                                                                                                                                      | • | 0.6            |         |             | μs                                           |

| t <sub>SU,STO</sub>  | Stop Condition Setup Time                                                                         |                                                                                                                                                                                                                                                                                                      | • | 0.6            |         |             | μs                                           |

| t <sub>HD,DAT</sub>  | Data Hold Time:<br>Receiving Data<br>Transmitting Data                                            |                                                                                                                                                                                                                                                                                                      | • | 0<br>0.3       |         | 0.9         | ns<br>µs                                     |

| t <sub>SU,DAT</sub>  | Input Data Setup Time                                                                             |                                                                                                                                                                                                                                                                                                      |   | 100            |         |             | ns                                           |

| t <sub>TIMEOUT</sub> | Clock Low Timeout                                                                                 |                                                                                                                                                                                                                                                                                                      |   | 25             |         | 35          | ms                                           |

| t <sub>LOW</sub>     | Serial Clock Low Period                                                                           |                                                                                                                                                                                                                                                                                                      |   | 1.3            |         | 10000       | μs                                           |

| t <sub>HIGH</sub>    | Serial Clock High Period                                                                          |                                                                                                                                                                                                                                                                                                      |   | 0.6            |         |             | μs                                           |

# **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3882-1 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3882-1E is guaranteed to meet performance specifications from 0°C to 85°C. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3882-1I is guaranteed over the full -40°C to 125°C operating junction temperature  $T_J$  is calculated in °C from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the formula:

$T_J = T_A + (P_D \bullet \theta_{JA})$

where  $\theta_{JA}$  is the package thermal impedance. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. Refer to the Applications Information section.

**Note 3:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

**Note 4:** EEPROM endurance, retention and mass write times are guaranteed by design, characterization and correlation with statistical process controls. Minimum retention applies only for devices cycled less than the minimum endurance specification. EEPROM read commands (e.g. RESTORE\_USER\_ALL) are valid over the entire specified operating junction temperature range. **Note 5:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to GND unless otherwise specified.

**Note 6:** Minimum EEPROM endurance, retention and mass write time specifications apply when writing data with  $3.15V \le V_{DD33} \le 3.45V$ . EEPROM read commands are valid over the entire specified  $V_{DD33}$  operating range.

**Note 7:** Specified V<sub>OUT</sub> error with AVP = 0% requires servo mode to be set with MFR\_PWM\_MODE\_LTC3882-1 command bit 6. Performance is guaranteed by testing the LTC3882-1 in a feedback loop that servos V<sub>OUT</sub> to a specified value.

**Note 8:** ADC tested with PWMs disabled. Comparable capability demonstrated by in-circuit evaluations. Total Unadjusted Error includes all gain and linearity errors, as well as offsets.

**Note 9:** Internal 32-bit calculations using 16-bit ADC results are limited to 10-bit resolution by PMBus Linear 11-bit data format.

**Note 10:** Limits guaranteed by TSNS voltage and current measurements during test, including ADC readback.

**Note 11:** Data conversion is done in round robin fashion. All inputs signals are continuously scanned in sequence resulting in a typical conversion latency of 90ms.

Note 12: Guaranteed by design.

**Note 13:** Do not apply a voltage or current source directly to these pins. They should only be connected to passive RC loads, otherwise permanent damage may occur.

**Note 14:** Do not apply a voltage source to this pin unless shorted to  $V_{CC}$ . See Electrical Characteristics for applicable limits beyond which permanent damage may occur.

Rev B

70

**Regulated Output vs Temperature** 1.8000 VOUT COMMAND = 1.8V DIGITAL SERVO OFF 1.7995 1.7990 Vout (V) 1.7985 1.7980 1.7975 1.7970 , -40 -20 0 60 80 100 120 20 40 TEMPERATURE (°C) 38821 G01a

VOUT\_COMMAND DNL

WM FREQUENCY (kHz)

For more information www.analog.com

### PIN FUNCTIONS

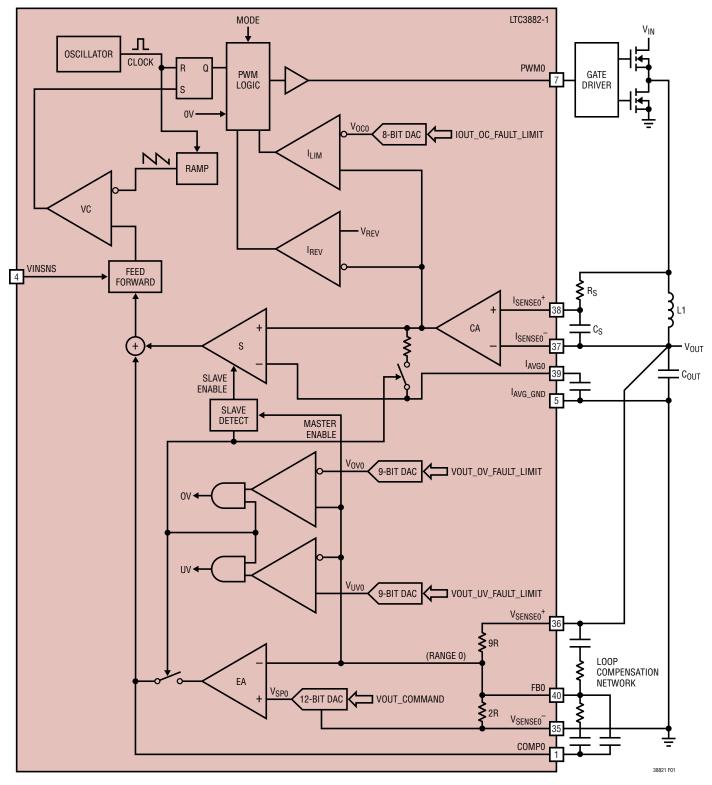

**COMPO/COMP1 (Pin 1/Pin 28):** Error Amplifier Outputs. PWM duty cycle increases with this control voltage. These are true low impedance outputs and cannot be directly connected together when active. For PolyPhase operation, wiring FB to  $V_{DD33}$  will three-state the error amplifier output of that channel, making it a slave. PolyPhase control is then implemented in part by connecting all slave COMP pins together to one master error amplifier output.

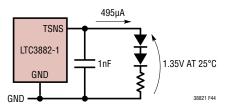

**TSNS0/TSNS1 (Pin 2/Pin 3):** External Temperature Sense Inputs. The LTC3882-1 supports two methods of calculation of external temperature based on forward-biased P/N junctions between these pins and GND.

**VINSNS (Pin 4):**  $V_{IN}$  Supply Sense. Connect to the  $V_{IN}$  power supply to provide line feedforward compensation. A change in  $V_{IN}$  immediately modulates the input to the PWM comparator and inversely changes the pulse width to provide excellent transient line regulation and fixed modulator voltage gain. An external lowpass filter can be added to this pin to prevent noisy signals from affecting the loop gain.

$I_{AVG\_GND}$  (Pin 5):  $I_{AVG}$  Ground Reference. The same  $I_{AVG\_GND}$  should be shared between all channels of a PolyPhase rail and connected to system ground at a single point.  $I_{AVG\_GND}$  may be wired directly to GND on ICs that do not share phases with other chips.

**PGOOD/PGOOD1 (Pin 6/Pin 27):** Power Good Indicator Open-Drain Outputs. These outputs are driven low through a 30µs filter when the respective channel output is below its programmed UV fault limit or above its programmed OV fault limit. If used, a pull-up resistor is required in the application. Operating voltage range is GND to V<sub>DD33</sub>.

**PWM0/PWM1 (Pin 7/Pin 26):** PWM Three-State Control Outputs. These pins provide single-wire PWM switching control for each channel to an external gate driver, DrMOS or power block. Operating voltage range is GND to V<sub>DD33</sub>.

**SYNC (Pin 8):** External Clock Synchronization Input and Open-Drain Output. If desired, an external clock can be applied to this pin to synchronize the internal PWM channels. If the LTC3882-1 is configured as a clock master, this pin will also pull to ground at the selected PWM switching

frequency with a 125ns pulse width. A pull-up resistor to 3.3V is required in the application if SYNC is driven by any LTC3882-1. Minimize the capacitance on this line to ensure its time constant is fast enough for the application.

**SCL (Pin 9):** Serial Bus Clock Input. A pull-up resistor to 3.3V is required in the application.

**SDA (Pin 10):** Serial Bus Data Input and Output. A pull-up resistor to 3.3V is required in the application.

**ALERT (Pin 11):** Open-Drain Status Output. This pin may be connected to the system SMBALERT wire-AND interrupt signal and should be left open if not used. If used, a pull-up resistor is required in the application. Operating voltage range is GND to V<sub>DD33</sub>.

**FAULTO**/**FAULT1** (Pin 12/Pin 13): Programmable Digital Inputs and Open-Drain Outputs for Fault Sharing. Used for channel-to-channel fault communication and propagation. These pins should be left open if not used. If used, a pull-up resistor to 3.3V is required in the application.

**RUN0/RUN1 (Pin 14/Pin 15):** Run Control Inputs and Open-Drain Outputs. A voltage above 2V is required on these pins to enable the respective PWM channel. The LTC3882-1 will drive these pins low under certain reset/ restart conditions regardless of any PMBus command settings. A pull-up resistor to 3.3V is required in the application.

**ASELO/ASEL1 (Pin 16/Pin 17):** Serial Bus Address Select Pins. Connect optional 1% resistor dividers between  $V_{DD25}$ and GND to these pins to select the serial bus interface address. Refer to the Applications Information section for more detail.

$V_{OUT0\_CFG}/V_{OUT1\_CFG}$  (Pin 18/Pin 19): Output Voltage Configuration Pins. Connect optional 1% resistor dividers between V<sub>DD25</sub> and GND to these pins to select the output voltage for each channel. Refer to the Applications Information section for more detail.

**FREQ\_CFG (Pin 20):** Frequency Configuration Pin. Connect an optional 1% resistor divider between  $V_{DD25}$  and GND to this pin to configure PWM switching frequency. Refer to the Applications Information section for more detail.

### PIN FUNCTIONS

**PHAS\_CFG (Pin 21):** Phase Configuration Pin. Connect an optional 1% resistor divider between  $V_{DD25}$  and GND to this pin to configure the phase of each PWM channel relative to SYNC. Refer to the Applications Information section for more detail.

$V_{DD25}$  (Pin 22): Internal 2.5V Regulator Output. Bypass this pin to GND with a low ESR 1µF capacitor. Do not load this pin with external current beyond that required for local LTC3882-1 configuration pins, if any.

**SHARE\_CLK (Pin 23):** Share Clock Open-Drain Output (bussed). Share Clock, nominally 100kHz, is used to sequence multiple rails in a power system utilizing more than one LTC PSM controller. A pull-up resistor is required in the application. Minimize the capacitance on this line to ensure the time constant is fast enough for the application. Operating voltage range is GND to V<sub>DD33</sub>.

$V_{DD33}$  (Pin 24): Internal 3.3V Regulator Output. Bypass this pin to GND with a low ESR 2.2µF capacitor. The LTC3882-1 may also be powered from an external 3.3V rail attached to this pin, if also shorted to V<sub>CC</sub>. Do not overload this pin with external system current. Local pull-up resistors for the LTC3882-1 itself may be powered from V<sub>DD33</sub>. Refer to the Applications Information section for more detail.

$V_{CC}$  (Pin 25): 3.3V Regulator Input. Bypass this pin to GND with a capacitor (0.1µF to 1µF ceramic) in close proximity to the IC.

**V**<sub>SENSE0</sub><sup>-/</sup>**V**<sub>SENSE1</sub><sup>-</sup> (Pin 35/Pin 34): Negative Output Voltage Sense Inputs. These pins must still be properly connected on slave channels for accurate output current telemetry.

**VSENSED**<sup>+</sup>/**VSENSE1**<sup>+</sup> (**Pin 36**/**Pin 33**): Positive Output Voltage Sense Inputs. These pins must still be properly connected on slave channels for accurate output current telemetry.

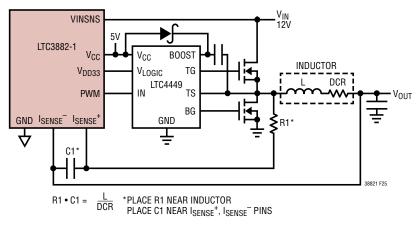

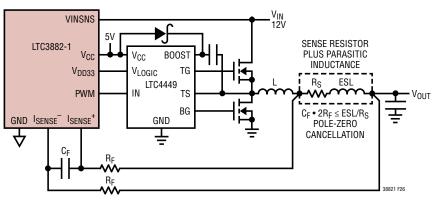

**I**<sub>SENSE0</sub><sup>-/I</sup><sub>SENSE1</sub><sup>-</sup> (**Pin 37/Pin 32**): Current Sense Amplifier Inputs. The (–) inputs to the amplifiers are normally connected to the low side of a DCR sensing network or output current sense resistor for each phase.

**I**<sub>SENSE0</sub><sup>+</sup>/**I**<sub>SENSE1</sub><sup>+</sup> (**Pin 38/Pin 31**): Current Sense Amplifier Inputs. The (+) inputs are normally connected to the high side of an output current sense resistor or the R-C midpoint of a parallel DCR sense circuit.

$I_{AVG0}/I_{AVG1}$  (Pin 39/Pin 30): Average Current Control Pins. A capacitor connected between these pins and  $I_{AVG\_GND}$ stores a voltage proportional to the average output current of the master channel. PolyPhase control is then implemented in part by connecting all slave  $I_{AVG}$  pins together to the master  $I_{AVG}$  output. This pin should be left open on channels that control single-phase outputs. Operating voltage range is GND to 2.1V.

**FB0/FB1 (Pin 40/Pin 29):** Error Amplifier Inverting Inputs. These pins provide an internally scaled version of the output voltage for use in loop compensation. Refer to the Applications Information section for additional details on compensating the output voltage control loop with external components.

**GND (Exposed Pad Pin 41):** Ground. All small-signal and compensation components should connect to this pad. *The exposed pad must be soldered to a suitable PCB copper ground plane for proper electrical operation and to obtain the specified package thermal resistance.*

### **BLOCK DIAGRAM**

### TEST CIRCUIT (Channel O Example)

# TIMING DIAGRAM

# OPERATION

#### Overview

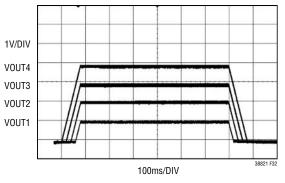

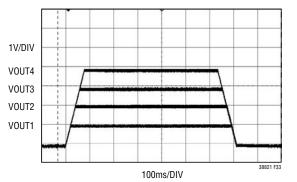

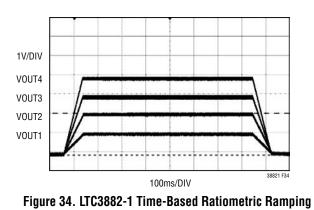

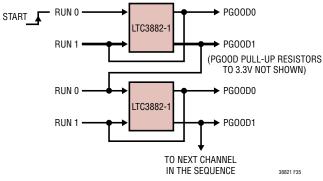

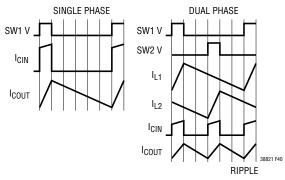

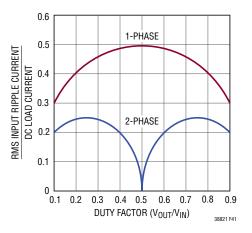

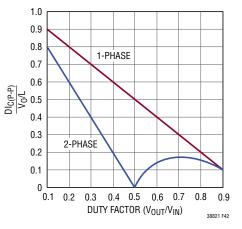

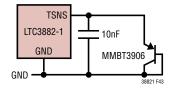

The LTC3882-1 is a dual channel/dual phase, constant frequency analog voltage mode controller for DC/DC stepdown applications. It features a PMBus compliant digital interface for monitoring and control of important power system parameters. The chip operates from an IC power supply between 3V and 13.2V and is intended for conversion from V<sub>IN</sub> between 3V and 38V to output voltages between 0.5V and 5.25V. It is designed to be used in a switching architecture with external FET drivers, including higher level integrations such as non-isolated power blocks. Major features include: