### LTC3315B

### Dual 5V, 2A Synchronous Step-Down DC/DCs in 2mm × 2mm LQFN

### FEATURES

- Dual Outputs Each with 2A Output Current

- High Efficiency:  $19m\Omega$  NMOS and  $75m\Omega$  PMOS

- Wide Bandwidth, Fast Transient Response

- Switching Frequency Synchronizable Up to 10MHz

- V<sub>IN</sub> Range: 2.25V to 5.5V

- V<sub>OUT</sub> Range: 0.5V to V<sub>IN</sub>

- V<sub>OUT</sub> Accuracy: ±1%

- Low Ripple Burst Mode<sup>®</sup> Operation

- Peak Current Mode Control

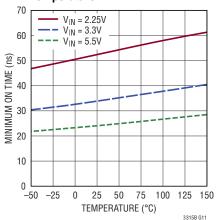

- Minimum On-Time: 25ns

- Safely Tolerates Inductor Saturation in Overload

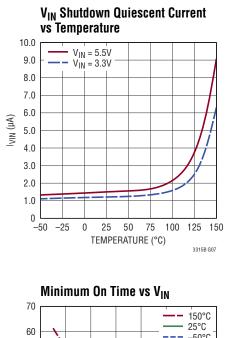

- Shutdown Current: 1.2µA

- Precision 400mV Enable Thresholds

- Internal Soft-Start and Compensation

- Power Good Output

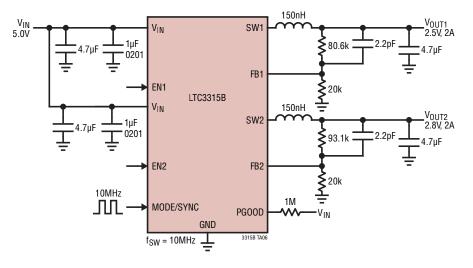

- Low Profile, Thermally Enhanced 12-Lead 2mm × 2mm × 0.74mm LQFN Package

- AEC-Q100 Qualified for Automotive Applications

### **APPLICATIONS**

- Servers, Telecom Supplies, Optical Networking

- Distributed DC Power Systems (POL)

- **FPGA**, ASIC, μP Core Supplies

- Industrial/Automotive/Communications

### DESCRIPTION

The LTC®3315B features dual 2A monolithic synchronous step-down converters operating from a 2.25V to 5.5V input supply in one package for space-constrained applications with demanding performance requirements. Using constant frequency, peak current mode control at switching frequencies up to 10MHz with a minimum ontime as low as 25ns, both bucks achieve high efficiency and fast transient response in a very small application footprint.

The LTC3315B operates in forced continuous or pulse skip mode for low noise or in Burst Mode<sup>®</sup> operation for high efficiency at light loads. The common buck switching frequency is 6MHz and can be synchronized to an external oscillator via the MODE/SYNC pin.

The LTC3315B can regulate outputs as low as 500mV. Other features include precision enable thresholds, a PGOOD signal, output overvoltage protection, thermal shutdown, output short-circuit protection, and up to 100% duty cycle operation for low dropout. The LTC3315B is available in a compact 2mm × 2mm LQFN package.

All registered trademarks and trademarks are the property of their respective owners.

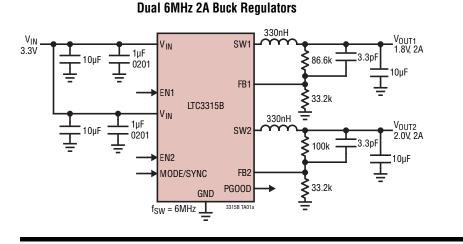

### TYPICAL APPLICATION

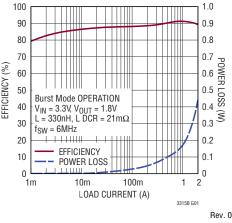

#### Efficiency vs Load Current

### **ABSOLUTE MAXIMUM RATINGS**

| (Note ' | 1) |

|---------|----|

|---------|----|

| $\label{eq:VIN} \begin{array}{c} -0.3 \text{V to 6V} \\ \text{EN1, EN2} \\ -0.3 \text{V to Lesser of } (\text{V}_{\text{IN}} + 0.3 \text{V}) \text{ or 6V} \\ \text{FB1, FB2} \\ -0.3 \text{V to Lesser of } (\text{V}_{\text{IN}} + 0.3 \text{V}) \text{ or 6V} \\ \text{MODE/SYNC} \\ -0.3 \text{V to Lesser of } (\text{V}_{\text{IN}} + 0.3 \text{V}) \text{ or 6V} \\ \end{array}$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PG00D0.3V to 6V                                                                                                                                                                                                                                                                                                                                                                         |

| I <sub>PG00D</sub> 5mA                                                                                                                                                                                                                                                                                                                                                                  |

| Operating Junction Temperature (Notes 2, 3):                                                                                                                                                                                                                                                                                                                                            |

| LTC3315BE–40°C to 125°C                                                                                                                                                                                                                                                                                                                                                                 |

| LTC3315BI–40°C to 125°C                                                                                                                                                                                                                                                                                                                                                                 |

| LTC3315BJ–40°C to 150°C                                                                                                                                                                                                                                                                                                                                                                 |

| LTC3315BH40°C to 150°C                                                                                                                                                                                                                                                                                                                                                                  |

| LTC3315BMP55°C to 150°C                                                                                                                                                                                                                                                                                                                                                                 |

| Storage Temperature Range65°C to 150°C                                                                                                                                                                                                                                                                                                                                                  |

| Maximum Reflow (Package Body) Temperature 260°C                                                                                                                                                                                                                                                                                                                                         |

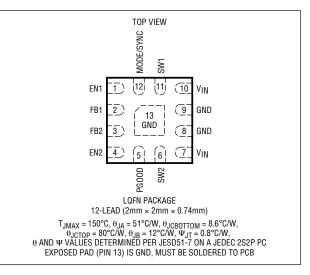

### PIN CONFIGURATION

### **ORDER INFORMATION**

|                                                                                 |                                                           | PART M  | ARKING*              | PACKAGE                                          | MSL           | TEMPERATURE RANG    |  |

|---------------------------------------------------------------------------------|-----------------------------------------------------------|---------|----------------------|--------------------------------------------------|---------------|---------------------|--|

| TAPE AND REEL (MINI)                                                            | TAPE AND REEL                                             | DEVICE  | FINISH CODE          | TYPE                                             | RATING        | (SEE NOTE 2)        |  |

| LTC3315BEV#TRMPBF                                                               | LTC3315BEV#TRPBF                                          |         |                      |                                                  |               | -40°C to 125°C      |  |

| LTC3315BIV#TRMPBF                                                               | LTC3315BIV#TRPBF                                          |         |                      | LQFN (Laminate<br>Package with QFN               | MSL 3         | -40°C to 125°C      |  |

| LTC3315BJV#TRMPBF                                                               | LTC3315BJV#TRPBF                                          | LHFZ e4 | -40°C to 150°C       |                                                  |               |                     |  |

| LTC3315BHV#TRMPBF                                                               | LTC3315BHV#TRPBF                                          |         |                      | Footprint)                                       |               | -40°C to 150°C      |  |

| LTC3315BMPV#TRMPBF                                                              | LTC3315BMPV#TRPBF                                         |         |                      |                                                  |               | -55°C to 150°C      |  |

| AUTOMOTIVE PRODUCTS*                                                            | **                                                        |         |                      |                                                  |               |                     |  |

| TC3315BEV#WTRMPBF                                                               | LTC3315BEV#WTRPBF                                         |         | e4                   | LQFN (Laminate<br>Package with QFN<br>Footprint) | MSL 3         | -40°C to 125°C      |  |

| LTC3315BIV#WTRMPBF                                                              | LTC3315BIV#WTRPBF                                         | LHFZ    |                      |                                                  |               | -40°C to 125°C      |  |

| TC3315BJV#WTRMPBF                                                               | LTC3315BJV#WTRPBF                                         |         |                      |                                                  |               | -40°C to 150°C      |  |

| LTC3315BHV#WTRMPBF                                                              | LTC3315BHV#WTRPBF                                         |         |                      |                                                  |               | -40°C to 150°C      |  |

| <ul> <li>Contact the factory for parallel ranges. *Pad or ball finis</li> </ul> | arts specified with wider op<br>h code is per IPC/JEDEC J |         | ure • Recor<br>Proce | nmended LGA and BG/<br>dures                     | A PCB Assembl | y and Manufacturing |  |

• Device temperature grade is indicated by a label on the shipping container.

TRM = 500 pieces.

- LGA and BGA Package and Tray Drawings

- Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

\*\*Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #W suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Notes 2, 3). V<sub>IN</sub> = 3.3V unless otherwise specified.

| PARAMETER                                   | CONDITIONS |   | MIN  | ТҮР | MAX | UNITS  |

|---------------------------------------------|------------|---|------|-----|-----|--------|

| Input Supply                                |            |   |      |     |     |        |

| Operating Supply Voltage (V <sub>IN</sub> ) |            | • | 2.25 |     | 5.5 | V      |

|                                             |            |   |      |     |     | Rev. 0 |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Notes 2, 3). V<sub>IN</sub> = 3.3V unless otherwise specified.

| PARAMETER                                                                               | CONDITIONS                                                                    |         | MIN                   | TYP         | MAX        | UNITS    |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------|-----------------------|-------------|------------|----------|

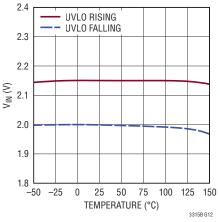

| V <sub>IN</sub> Undervoltage Lockout<br>V <sub>IN</sub> Undervoltage Lockout Hysteresis | V <sub>IN</sub> Rising                                                        | •       | 2.05                  | 2.15<br>150 | 2.25       | V<br>mV  |

| V <sub>IN</sub> Quiescent Current in Shutdown                                           |                                                                               |         |                       | 1.2         | 2          | μA       |

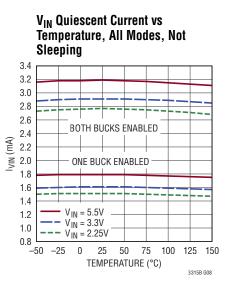

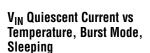

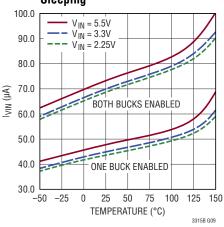

| V <sub>IN</sub> Quiescent Current with One Buck Enabled                                 | Burst Mode, Buck in Regulation, Sleeping<br>All Modes, Not Sleeping (Note 4)  |         |                       | 45<br>1.6   | 70<br>2.5  | μA<br>mA |

| V <sub>IN</sub> Quiescent Current with Both Bucks Enabled                               | Burst Mode, Bucks in Regulation, Sleeping<br>All Modes, Not Sleeping (Note 4) |         |                       | 70<br>2.9   | 110<br>4.4 | μA<br>mA |

| Enable Threshold<br>Enable Threshold Hysteresis                                         | V <sub>EN</sub> Rising                                                        | •       | 375                   | 400<br>50   | 425        | mV<br>mV |

| EN Pin Leakage                                                                          | V <sub>EN</sub> = 5.5V                                                        |         |                       |             | ±20        | nA       |

| Voltage Regulation, Buck 1 and Buck 2                                                   |                                                                               |         |                       |             |            |          |

| Regulated Feedback Voltage (V <sub>FB</sub> )                                           |                                                                               |         | 495                   | 500         | 505        | mV       |

| Feedback Voltage Line Regulation                                                        | $2.25V \le V_{IN} \le 5.5V$                                                   |         |                       | 0.015       | 0.05       | %/V      |

| Feedback Pin Input Current                                                              | V <sub>FB</sub> = 500mV                                                       |         |                       |             | ±20        | nA       |

| PMOS Current Limit (I <sub>LIM</sub> )                                                  | Current out of SW, $V_{OUT}/V_{IN} \le 0.2$                                   |         | 2.9                   | 3.2         | 3.5        | A        |

| NMOS Current Limit (I <sub>VALLEY</sub> )                                               | Current out of SW                                                             |         | 2.4                   | 2.7         | 3.0        | A        |

| NMOS Reverse Current Limit                                                              | Current into SW, Forced Continuous                                            |         | 0.5                   | 1           | 1.6        | A        |

| PMOS ON-Resistance                                                                      |                                                                               |         |                       | 75          |            | mΩ       |

| NMOS ON-Resistance                                                                      |                                                                               |         |                       | 19          |            | mΩ       |

| SW Leakage Current                                                                      | Shutdown, V <sub>IN</sub> = 5.5V                                              |         |                       |             | ±200       | nA       |

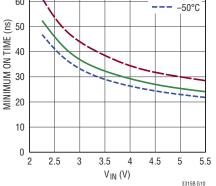

| Minimum On Time                                                                         | V <sub>IN</sub> = 5.5V                                                        |         |                       | 25          | 45         | ns       |

| Maximum Duty Cycle                                                                      |                                                                               |         | 100                   |             |            | %        |

| Overtemperature Shutdown (OT)<br>Overtemperature Shutdown Hysteresis                    | Temperature Rising (Note 5)                                                   |         |                       | 165<br>5    |            | 0°<br>0° |

| Power Good/Soft-Start                                                                   |                                                                               | · · · · |                       |             |            |          |

| PGOOD Rising Threshold<br>PGOOD Hysteresis                                              | As a Percentage of the Regulated $V_{\mbox{OUT}}$                             | •       | 97<br>0.6             | 98<br>1.1   | 99<br>1.6  | %        |

| Overvoltage Rising Threshold<br>Overvoltage Hysteresis                                  | As a Percentage of the Regulated $V_{OUT}$                                    | •       | 107<br>1              | 110<br>2.2  | 114<br>3.5 | %<br>%   |

| PGOOD Delay                                                                             |                                                                               |         |                       | 120         |            | μs       |

| PGOOD Leakage Current                                                                   | V <sub>PG00D</sub> = 5.5V                                                     |         |                       |             | 20         | nA       |

| PGOOD Pull-Down Resistance                                                              | V <sub>PG00D</sub> = 0.1V                                                     |         |                       | 10          | 20         | Ω        |

| Soft-Start Time                                                                         | (Note 6)                                                                      |         | 0.25                  | 1           | 3          | ms       |

| Oscillator and MODE/SYNC                                                                |                                                                               |         |                       |             |            |          |

| Internal Oscillator Frequency (f <sub>SW</sub> )                                        |                                                                               |         | 5.55                  | 6           | 6.45       | MHz      |

| Synchronization Frequency Range                                                         |                                                                               |         | 3                     |             | 10         | MHz      |

| Minimum SYNC High or Low Pulse Width                                                    |                                                                               |         | 40                    |             |            | ns       |

| SYNC Level High on MODE/SYNC<br>SYNC Level Low on MODE/SYNC                             |                                                                               | •       | 1.2                   |             | 0.4        | V<br>V   |

| MODE/SYNC No Clock Detect Time                                                          |                                                                               |         |                       | 10          |            | μs       |

| MODE/SYNC Pin Threshold                                                                 | For Programming Pulse Skipping Mode<br>For Programming Burst Mode             | •       | V <sub>IN</sub> – 0.1 |             | 0.1        | VV       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The LTC3315B is tested under pulsed load conditions such that  $T_J \approx T_A.$  The LTC3315BE is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design,

### **ELECTRICAL CHARACTERISTICS**

characterization, and correlation with statistical process controls. The LTC3315BI is guaranteed over the –40°C to 125°C operating junction temperature range, the LTC3315BJ and the LTC3315BH are guaranteed over the –40°C to 150°C operating junction temperature range, and the LTC3315BMP is guaranteed over the –55°C to 150°C operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance, and other environmental factors. The junction temperature (T<sub>A</sub> in °C) is calculated from ambient temperature (T<sub>A</sub> in °C) and power dissipation (P<sub>D</sub> in Watts) according to the formula:

$T_{II} = T_A + (P_D \bullet \theta_{IA})$

where  $\theta_{JA}$  (in °C/W) is the package thermal impedance. See High Temperature Considerations section for more details.

**Note 3:** The LTC3315B includes overtemperature protection which protects the device during momentary overload conditions. Junction temperatures will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** Static current, switches not switching. Actual current will be higher due to gate charge losses at the switching frequency.

**Note 5:** Overtemperature shutdown is not tested in production.

**Note 6:** The soft-start time is the time from the start of switching until the FB pin reaches 475mV.

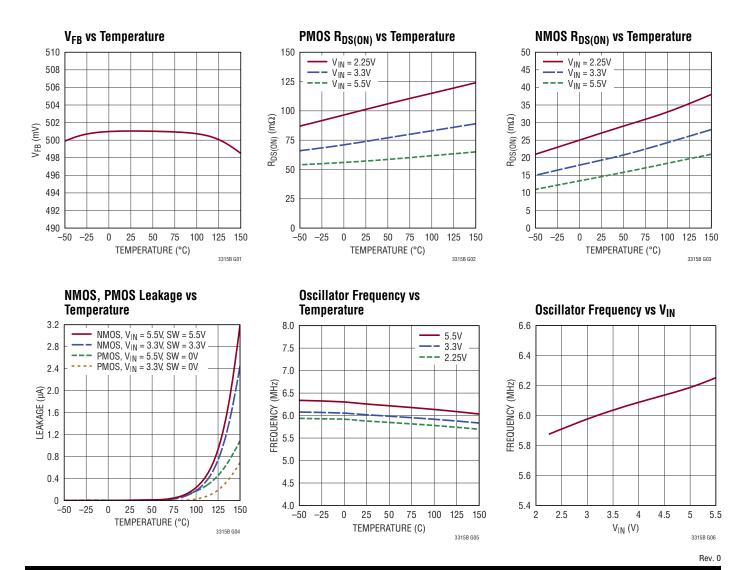

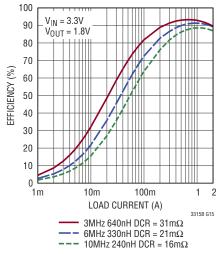

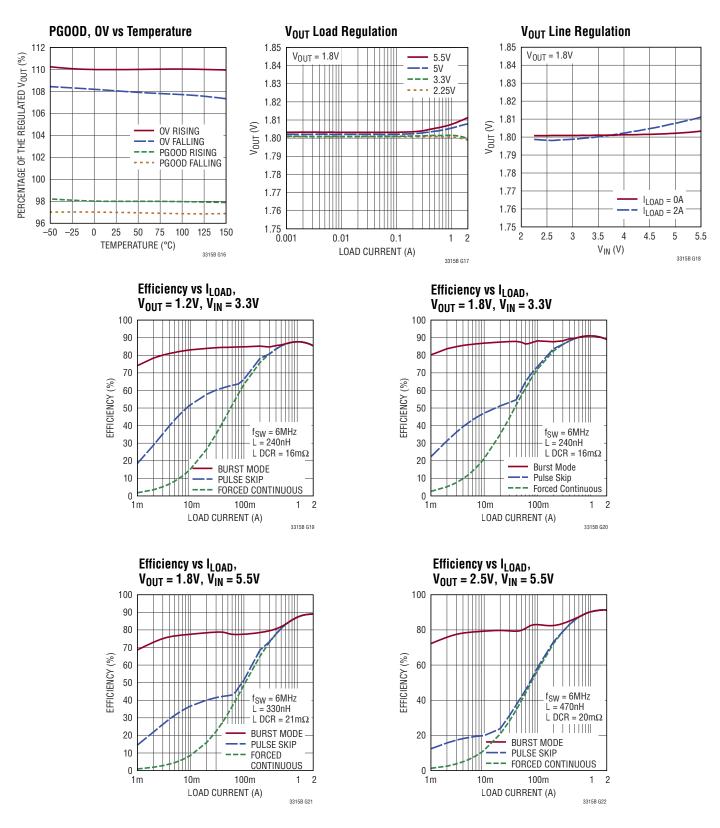

**TYPICAL PERFORMANCE CHARACTERISTICS**  $T_A = 25^{\circ}C$ ,  $V_{IN} = 3.3V$ , unless otherwise noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{IN} = 3.3V$ , unless otherwise noted.

**EN Threshold vs Temperature** 420 EN RISING 410 EN FALLING 400 390 380 V<sub>EN</sub> (mV) 370 360 350 340 330 320 100 -50 -25 0 25 50 75 125 150 TEMPERATURE (°C) 3315B G13

Minimum On Time vs Temperature

**Current Limit vs Temperature**

PMOS

NMOS

3.4

3.3

(¥) 3.2 3.1 3.0 4

LD 2.9

CURRENT CURREN

2.6

2.5

-50

-25

**UVLO** Threshold vs Temperature

Efficiency vs I<sub>LOAD</sub> Syncing, Forced Continuous

Rev. 0

25 50 75 100

TEMPERATURE (°C)

125 150

3315B G14

0

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{IN} = 3.3V$ , unless otherwise noted.

### **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{IN} = 3.3V$ , unless otherwise noted.

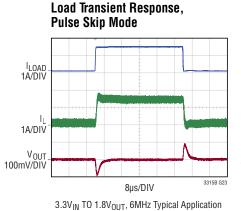

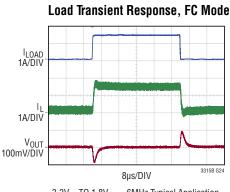

$3.3V_{IN}$  TO  $1.8V_{OUT},$  6MHz Typical Application C\_{OUT} = 10µF, L = 330nH LOAD STEP: 0.1A TO 1.5A IN 5A/1uS

$3.3V_{IN}$  TO  $1.8V_{OUT},$  6MHz Typical Application C\_{OUT} = 10µF, L = 330nH LOAD STEP: 0.1A TO 1.5A IN 5A/1uS

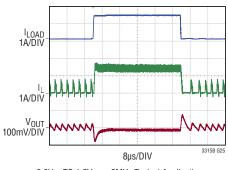

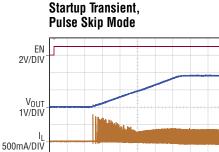

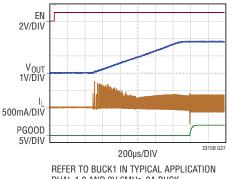

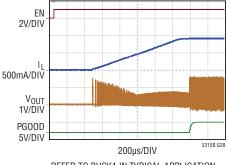

#### Load Transient Response, **Burst Mode**

$3.3V_{IN}$  TO  $1.8V_{OUT},$  6MHz Typical Application C\_{OUT} = 10µF, L = 330nH LOAD STEP: 0.1A TO 1.5A IN 5A/1uS

PGOOD 5V/DIV 3315B G26 200µs/DIV REFER TO BUCK1 IN TYPICAL APPLICATION

DUAL 1.8 AND 2V 6MHz, 2A BUCK REGULATORS, V<sub>IN</sub> = 3.3V

Startup Transient, Forced Continuous Mode

DUAL 1.8 AND 2V 6MHz, 2A BUCK REGULATORS, V<sub>IN</sub> = 3.3V

#### Startup Transient, Burst Mode

**REFER TO BUCK1 IN TYPICAL APPLICATION** DUAL 1.8 AND 2V 6MHz, 2A BUCK REGULATORS, VIN = 3.3V

### PIN FUNCTIONS

**EN1 (Pin 1):** Enable Input for Buck Regulator 1. Active high. The EN1 pin has a precision threshold and an optional external resistor divider from  $V_{\rm IN}$  or another supply programs when Buck Regulator 1 is enabled. If the precision threshold is not required, drive EN1 to  $V_{\rm IN}$  to enable. Do not float.

**FB1 (Pin 2):** Feedback Input for Buck Regulator 1. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. The LTC3315B regulates FB1 to 500mV (typical). A phase lead capacitor connected between  $V_{OUT1}$  and FB1 may be used to optimize transient response.

**FB2 (Pin 3):** Feedback Input for Buck Regulator 2. Program the output voltage and close the control loop by connecting this pin to the middle node of a resistor divider between the output and ground. The LTC3315B regulates FB2 to 500mV (typical). A phase lead capacitor connected between  $V_{OUT2}$  and FB2 may be used to optimize transient response.

**EN2 (Pin 4):** Enable Input for Buck Regulator 2. Active high. The EN2 pin has a precision threshold and an optional external resistor divider from  $V_{IN}$  or another supply programs when Buck Regulator 2 is enabled. If the precision threshold is not required, drive EN2 to  $V_{IN}$  to enable. Do not float.

**PGOOD (Pin 5):** Power Good Output. Open drain output. When the regulated output voltage of either enabled switching regulator falls below its PGOOD threshold or rises above its overvoltage threshold, this pin is driven low. When both buck regulators are disabled PGOOD is driven low.

**SW2 (Pin 6):** Switch Node for Buck Regulator 2. Connect an inductor to this pin with a short, wide trace.

$V_{IN}$  (Pin 7, Pin 10): Input Supply Pins. The V<sub>IN</sub> pins supply current to internal circuitry and to each buck's PMOS power switch. Connect both V<sub>IN</sub> pins together with a short, wide trace and bypass to GND with low ESR capacitors located as close as possible to the pins.

**GND (Pin 8, Pin 9, Exposed Pad Pin 13):** Ground. Connect the exposed pad to a continuous ground plane on the printed circuit board directly under the LTC3315B for electrical contact and rated thermal performance. Additionally, Pin 8 and Pin 9 should be shorted to the exposed pad with a wide trace.

**SW1 (Pin 11):** Switch Node for Buck Regulator 1. Connect an inductor to this pin with a short, wide trace.

**MODE/SYNC (Pin 12):** Mode Selection and External Clock Synchronization Input. Ground this pin to enable pulseskipping mode. For higher efficiency at light loads, tie this pin to  $V_{IN}$  to enable Burst Mode. For fast transient response and constant frequency operation over a wide load range, float this pin to enable forced continuous mode. Drive MODE/SYNC with an external clock to synchronize both buck converters to the applied frequency. When syncing, the operating mode is forced continuous. The slope compensation is automatically adapted to the external clock frequency. In the absence of an external clock both buck converters will switch at the default switching frequency.

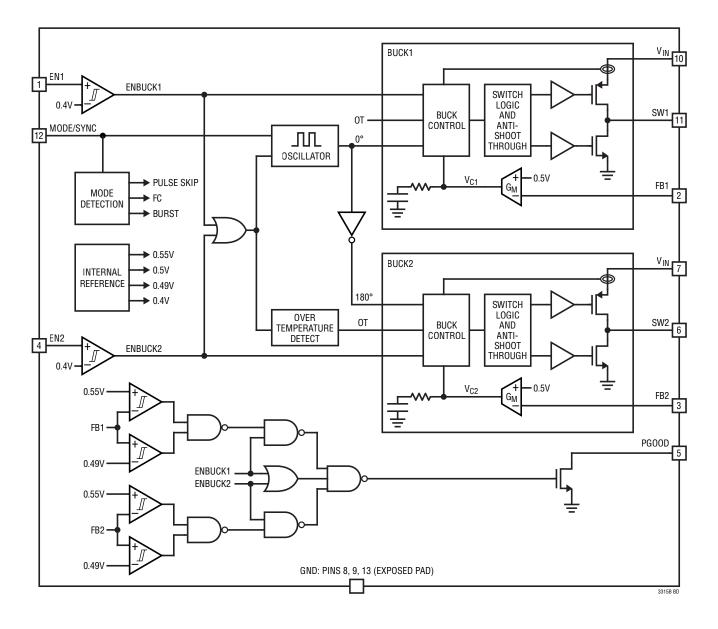

### **BLOCK DIAGRAM**

9

### OPERATION

#### **Buck Switching Regulators**

The LTC3315B is a 5V dual 2A monolithic, constant frequency, peak current mode step-down DC/DC converter. The synchronous buck switching regulators are internally compensated and require only external feedback resistors to set the output voltage.

An internal oscillator, which can be externally synchronized, turns on the internal PMOS power switch at the beginning of each clock cycle. Current in the inductor ramps up until the PMOS current comparator trips and turns off the PMOS. The peak inductor current, IPFAK, at which the PMOS turns off is controlled by an internal V<sub>C</sub> voltage which the error amplifier regulates by comparing the voltage on the feedback (FB) pin with an internal 500mV reference. An increase in the load current causes a reduction in the feedback voltage relative to the reference, causing the error amplifier to raise the  $V_{\rm C}$  voltage (and IPEAK) until the average inductor current matches the new load current. When the PMOS turns off, the NMOS turns on and ramps down the inductor current for the remainder of the clock cycle or, if in pulse skipping mode or Burst Mode, until the inductor current falls to zero. If an overload condition results in excessive current flowing through the NMOS, the next clock cycle will be skipped until the current returns to a safe level.

Each buck switching regulator has its own SW, FB, and EN pins. The buck input supplies are internally connected, but each  $V_{IN}$  pin should have its own input bypass capacitor (see Applications Information). The enable pins have precision 400mV thresholds which may be used to provide event-based power-up sequencing by connecting the enable pin to the output of another buck through a resistor divider. If the EN pin of a buck is low, that buck is in shutdown and in a low quiescent current state. If both EN pins are low, both bucks are in shutdown, the SW pins are high impedance, and the quiescent current of the LTC3315B is 1µA (typical). If either EN pin is above the enable threshold of 400mV its respective buck is enabled.

Both buck regulators have forward and reverse inductor current limiting, soft-start to limit inrush current during start-up, and short-circuit protection. When both bucks are disabled and either buck is subsequently enabled, there is a 400 $\mu$ s (typical) delay while internal circuitry powers up followed by a 100 $\mu$ s (typical) no start time before switching commences and the soft-start ramp begins. If a second buck is then enabled, it will also have a 100 $\mu$ s (typical) no start time. If the second buck is enabled within 400 $\mu$ s of the first buck, it will wait until the expiry of the 400 $\mu$ s to begin its no start time.

The buck switching regulators are switched 180° out of phase with respect to each other. The phase determines the fixed edge of the switching sequence, which is when the PMOS turns on. The PMOS off (NMOS on) phase is subject to the regulated duty cycle of each buck.

#### **Mode Selection**

The buck switching regulators operate in three different modes set by the MODE/SYNC pin: pulse skipping mode (when the MODE/SYNC pin is set low), forced continuous PWM mode (when the MODE/SYNC pin is floating), and Burst Mode (when the MODE/SYNC pin is set high). The MODE/SYNC pin sets the operating mode for both buck switching regulators.

In pulse skipping mode, the oscillator operates continuously and positive SW transitions are aligned to the clock. Negative inductor current is disallowed and during light loads switch pulses are skipped to regulate the output.

In forced continuous mode, the oscillator runs continuously, no pulses are skipped, and switching occurs in every cycle. To maintain regulation, the inductor current is allowed to reverse under light load conditions. This mode allows the buck to run at a fixed frequency with minimal output ripple. In forced continuous mode if the inductor current reaches –1A (typical, 1A into the SW pin) the NMOS will turn off for the remainder of the cycle to limit the current.

In Burst Mode operation, at light loads, the output capacitor is charged to a voltage slightly higher than its regulation point. The regulator then goes into a sleep state, during which time the output capacitor provides the load current. In sleep most of the regulator's circuitry is powered down, helping to conserve input power. When the output voltage drops below its programmed value, the circuitry is powered back on and another burst cycle begins.

### OPERATION

The sleep time decreases as load current increases. In Burst Mode operation, the regulator will burst at light loads whereas at higher loads it will operate in constant frequency PWM mode.

#### Synchronizing the Oscillator to an External Clock

Selection of the operating frequency is a trade-off between efficiency and component size. High frequency operation allows the use of smaller inductor and capacitor values and improves transient response. Operation at lower frequencies improves efficiency by reducing switching losses but requires larger inductance and/or capacitance values to maintain low output voltage ripple. The LTC3315B operates at a default frequency of 6MHz.

The LTC3315B's internal oscillator is synchronized through an internal PLL circuit to an external frequency by applying a square wave clock signal to the MODE/SYNC pin. During synchronization, the Buck 1 PMOS turn-on is locked to the rising edge of the external frequency source. Buck 2 will be 180° out of phase with respect to Buck 1. While syncing, the buck switching regulators operate in forced continuous mode. The synchronization frequency range is 3MHz to 10MHz.

After detecting an external clock on the SYNC pin, the internal PLL starts up at the default frequency. The internal PLL then gradually adjusts its operating frequency to match the frequency and phase of the SYNC signal.

When the external clock is removed the LTC3315B will detect the absence of the external clock within approximately 10µs. During this time it will continue to provide clock cycles. Once the external clock removal has been detected, the oscillator will gradually adjust its operating frequency back to the default.

#### Power Failure Reporting Via PGOOD Pin

Power failure faults are reported via the PGOOD pin. Both buck switching regulators have an internal power good (PGOOD) signal and if a buck is enabled its internal PGOOD signal must be high for the PGOOD pin to be high. When the regulated output voltage of an enabled buck rises above 98% of its programmed value, the PGOOD signal transitions high. If the regulated output voltage subsequently falls below 97% of its programmed value, the PGOOD signal is pulled low. If either enabled buck's internal PGOOD signal stays low for greater than 120µs, then the PGOOD pin is pulled low, indicating to a microprocessor that a power fault has occurred. The 120µs filter time prevents the pin from being pulled low during a transient event. In addition, whenever PGOOD transitions high there will be a 120µs assertion delay.

The LTC3315B also reports overvoltage conditions at the PGOOD pin. If either enabled buck regulator's output voltage rises above 110% of its programmed value, the PGOOD pin is pulled low after 120µs. Similarly, if all enabled outputs that are overvoltage subsequently fall below 107.8% of their programmed value, the PGOOD pin transitions high again after 120µs.

An error condition that pulls the PGOOD pin low is not latched. When the error condition goes away, the PGOOD pin is released and is pulled high if no other error condition exists. PGOOD is also pulled low in the following scenarios: if neither buck switching regulator is enabled, if  $V_{\rm IN}$  is below the UVLO threshold, or if the LTC3315B is over temperature (see below).

#### **Output Overvoltage Protection**

During an output overvoltage event, when the FB pin voltage is greater than 110% of its regulated value, the LTC3315B PMOS will be turned off immediately.

An output overvoltage event should not happen under normal operating conditions.

#### **Overtemperature Protection**

To prevent thermal damage, the LTC3315B incorporates an overtemperature (OT) function. When the LTC3315B die temperature reaches 165°C (typical, not tested) all enabled buck switching regulators are shut down and remain in shutdown until the die temperature falls to 160°C (typical, not tested).

### OPERATION

#### Output Voltage Soft-Start

Soft starting the output prevents current surge on the input supply and/or output voltage overshoot. During soft-start, the output voltage will proportionally track an internal voltage ramp. An active pull-down circuit discharges that internal voltage in the case of fault conditions. The ramp will restart when the fault is cleared. Fault conditions that initiate the soft-start ramp are the  $V_{IN}$  voltage falling too low or thermal shutdown.

Recovery from an output short-circuit (see below) may involve another soft-start cycle if the FB voltage falls more than 120mV (typical) below regulation. During such a recovery, the FB voltage will quickly charge up to 120mV (typical) and then follow the soft-start ramp until regulation is reached.

### **Dropout Operation**

As the input supply voltage approaches the output voltage, the duty cycle increases toward 100%. Further reduction of the supply voltage forces the PMOS to remain on for more than one cycle, eventually reaching 100% duty cycle. The output voltage will then be determined by the input voltage minus the DC voltage drop across the internal PMOS and the inductor.

### Low Supply Operation

The LTC3315B is designed to operate down to an input supply voltage of 2.25V. An important thermal design consideration is that the  $R_{DS(ON)}$  of the power switches increases at low input. Consider the worst case LTC3315B power dissipation and die junction temperature at the lowest input voltage.

#### **Output Short-Circuit Protection and Recovery**

The peak inductor current level at which the current comparator shuts off the PMOS is controlled by the error amplifier. When the output current increases, the error amplifier raises the internal V<sub>C</sub> voltage until the average inductor current matches the load current. The LTC3315B clamps the maximum internal V<sub>C</sub> voltage, thereby limiting the peak inductor current.

When the output is shorted to ground, the inductor current decays very slowly during the downslope because the voltage across the inductor is low. To keep the inductor current in control a secondary limit is imposed on the valley of the inductor current. If the inductor current measured through the NMOS remains greater than  $I_{VALLEY}$  at the end of the cycle, the PMOS will be held off. Subsequent switching cycles will be skipped until the inductor current falls below  $I_{VALLEY}$ .

## **APPLICATIONS INFORMATION**

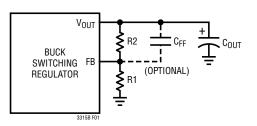

#### Buck Switching Regulator Output Voltage and Feedback Network

The output voltage of the buck switching regulators is programmed by a resistor divider connected from the switching regulator's output to ground and is given by:

$$V_{OUT} = V_{FB} \left( 1 + \frac{R2}{R1} \right)$$

(1)

as shown in Figure 1 where  $V_{FB} = 500$ mV. Typical values for R1 range from  $40k\Omega$  to  $1M\Omega$ . 1% resistors are recommended to maintain output voltage accuracy. The buck regulator transient response may improve with an optional phase lead capacitor  $C_{FF}$  that helps cancel

Figure 1. Feedback Components

the pole created by the feedback resistors and the input capacitance of the FB pin. Experimentation with capacitor values between 2pF and 22pF may improve transient response. The values used in the typical application circuits are a good starting point.

#### **Operating Frequency Selection and Trade-Offs**

Selection of the operating frequency is a trade-off between efficiency, component size, transient response, and input voltage range. The LTC3315B can operate at frequencies between 3MHz and 10MHz.

The advantage of high frequency operation is that smaller inductor and capacitor values may be used. Higher switching frequencies allow for higher control loop bandwidth and, therefore, faster transient response. The disadvantages of higher switching frequencies are lower efficiency, because of increased switching losses, and a smaller input voltage range, because of minimum switch on-time limitations.

The minimum on-time of the buck regulator imposes a minimum operating duty cycle. The highest switching frequency ( $f_{SW(MAX)}$ ) for a given application can be calculated as follows:

$$f_{SW(MAX)} = \frac{V_{OUT}}{t_{ON(MIN)} \bullet V_{IN(MAX)}}$$

(2)

where  $V_{IN(MAX)}$  is the maximum input voltage,  $V_{OUT}$  is the output voltage and  $t_{ON(MIN)}$  is the minimum top switch on-time. This equation shows that a slower switching frequency might be necessary to accommodate a high  $V_{IN}/V_{OUT}$  ratio.

The LTC3315B is capable of a maximum duty cycle of 100%, therefore, the  $V_{IN}$ -to- $V_{OUT}$  dropout is limited by the  $R_{DS(ON)}$  of the PMOS, the inductor DCR, and the load current.

#### Inductor Selection and Maximum Output Current

Considerations in choosing an inductor are inductance, RMS current rating, saturation current rating, DCR, and core loss.

Select the inductor value based on the following equations:

$$L \ge \frac{V_{OUT}}{0.6A \bullet f_{SW}} \bullet \left(1 - \frac{V_{OUT}}{V_{IN(MAX)}}\right) \text{ for } \frac{V_{OUT}}{V_{IN(MAX)}} \le 0.5 \quad (3)$$

$$L \ge \frac{V_{\text{IN(MAX)}}}{2.4\text{A} \cdot f_{\text{SW}}} \text{ for } \frac{V_{\text{OUT}}}{V_{\text{IN(MAX)}}} > 0.5$$

(4)

where  $f_{SW}$  is the switching frequency and  $V_{IN(MAX)}$  is the maximum applied input voltage.

To avoid overheating of the inductor, choose an inductor with an RMS current rating that is greater than the maximum expected output load of the application. Overload and short-circuit conditions need to be taken into consideration.

In addition ensure that the saturation current rating (typically labeled  $I_{SAT}$ ) is either higher than 3.5A, the maximum current limit of the LTC3315B, or higher than the maximum expected load plus half the inductor ripple:

$$I_{SAT} > I_{LOAD(MAX)} + \frac{1}{2}\Delta I_{L}$$

(5)

where  $I_{LOAD(MAX)}$  is the maximum output load current for the application and  $\Delta I_L$  is the inductor ripple current calculated as:

$$\Delta I_{L} = \frac{V_{OUT}}{L \bullet f_{SW}} \bullet \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(6)

To keep the efficiency high, choose an inductor with the lowest series resistance (DCR) and a core material intended for high frequency applications. Table 1 shows recommended inductors from several manufacturers.

#### **Input Capacitors**

Bypass the input of the LTC3315B with at least two ceramic capacitors, one near each V<sub>IN</sub> pin for best performance. Connect the ground of each capacitor to a wide PCB trace on the top layer of the PCB that connects pins 8 and 9 with the exposed pad. These capacitors should be 0603 or 0805 in size. Smaller 0201 capacitors can also be placed as close as possible to the LTC3315B directly on the traces leading from  $V_{IN}$  (Pin 7) and GND (Pin 8) and on the traces leading from V<sub>IN</sub> (Pin 10) and GND (Pin 9) to reduce input noise with minimal (if at all) increase in application footprint. See the layout section for more detail. X7R or X5R capacitors are recommended for best performance across temperature and input voltage variations (see Table 2). Note that larger input capacitance is required when a lower switching frequency is used. If the input power source has high impedance, or if there

#### Table 1. Recommended Inductors

| MANUFACTURER     | FAMILY         | L (nH)    | MAX IDC (A) | MAX DCR (m $\Omega$ ) | SIZE IN mm (L × W × H) |

|------------------|----------------|-----------|-------------|-----------------------|------------------------|

| Murata           | DFE18SAN_G0    | 240, 470  | 3.3 - 4.9   | 30 - 54               | 1.6 × 0.8 × 1.0        |

| Murata           | DFE201210S     | 110, 470  | 4.8 - 8.8   | 12 - 32               | 2.0 × 1.2 × 1.0        |

| Murata           | DFE201210U     | 240 - 680 | 3.6 - 6.5   | 25 - 60               | 2.0 × 1.2 × 1.0        |

| Murata           | DFE201610E     | 240 - 680 | 4.3 - 6.3   | 20 - 43               | 2.0 × 1.6 × 1.0        |

| Murata           | DFE252010F     | 220 - 820 | 4.5 - 7.2   | 16 - 40               | 2.5 × 2.0 × 1.0        |

| Vishay           | IHHP-0806AB-01 | 220 - 470 | 3.6-5.2     | 16 - 35               | 2.0 × 1.6 × 1.2        |

| Vishay           | IHHP-1008AB-01 | 220 - 470 | 4.5 - 6.5   | 10.5 - 26             | 2.5 × 2.0 × 1.2        |

| NIC              | NPMH0805       | 240 - 470 | 3.3 - 4.5   | 28 - 42               | 2.0 × 1.2 × 1.0        |

| NIC              | NPMH0806       | 240 - 470 | 3.5 - 4.7   | 23 - 42               | 2.0 × 1.6 × 1.0        |

| NIC              | NPMH1008       | 240 - 680 | 4.5 - 8.0   | 18 - 40               | 2.5 × 2.0 × 1.0        |

| XFRMS            | XFHCL43LT      | 220 - 470 | 3.8 - 7.0   | 13 - 25               | 2.5 × 2.0 × 1.2        |

| WURTH ELECTRONIK | WE-PMCI-0806   | 240 - 680 | 3.4 - 5.4   | 19 -45                | 2.0 × 1.6 × 1.0        |

| WURTH ELECTRONIK | WE-LQS-2512    | 160 - 680 | 3.5 - 6.4   | 16 - 35               | 2.5 × 2.0 × 1.2        |

is significant inductance due to long wires or cables, additional bulk capacitance may be necessary. This can be provided with an electrolytic capacitor. A ceramic input capacitor combined with trace or cable inductance forms a high quality (underdamped) tank circuit. If the LTC3315B circuit is plugged in to a live supply, the input voltage can ring to twice its nominal value, possibly exceeding the voltage rating. This situation is easily avoided (see Linear Technology Application Note 88).

| MANUFACTURER     | URL                |  |  |

|------------------|--------------------|--|--|

| AVX              | www.avxcorp.com    |  |  |

| Murata           | www.murata.com     |  |  |

| TDK              | www.tdk.com        |  |  |

| Taiyo Yuden      | www.t-yuden.com    |  |  |

| Samsung          | www.samsungsem.com |  |  |

| Wurth Elektronik | www.we-online.com  |  |  |

|                  |                    |  |  |

#### Table 2. Ceramic Capacitor Manufacturers

#### Output Capacitor, Output Ripple, and Loop Response

The output capacitor has two essential functions. Along with the inductor, it filters the square wave generated by the LTC3315B at the SW pin to produce the DC output. In this role it determines the output ripple; thus, low impedance at the switching frequency is important. The second function is to store energy in order to satisfy transient loads and to stabilize the LTC3315B's control loop. The LTC3315B is internally compensated and designed to operate at a high bandwidth for fast transient response capability. The selection of  $C_{OUT}$  affects the bandwidth of the system, but the transient response is also affected by  $V_{OUT}$ ,  $V_{IN}$ ,  $f_{SW}$  and other factors. A good place to start is with an output capacitance value of approximately:

$$C_{OUT} = \frac{80\mu F \bullet MHz}{f_{SW}} \sqrt{\frac{500mV}{V_{OUT}}}$$

(7)

where  $C_{OUT}$  is the recommended output capacitor value and  $f_{SW}$  is the switching frequency. A lower value of output capacitor saves space and cost, but transient performance will suffer and loop stability must be verified. Ceramic capacitors have very low equivalent series resistance (ESR) and provide the best output ripple and transient performance. Use X5R or X7R ceramic capacitors. (see Table 2). Even better output ripple and transient performance can be achieved by using low-ESL reverse geometry or three terminal ceramic capacitors.

During a load step, the output capacitor must instantaneously supply the current to support the load until the feedback loop increases the switch current enough to support the load. The time required for the feedback loop to respond is dependent on the compensation components and the output capacitor size. Typically, 3 to 4 cycles are required to respond to a load step, but only in the first cycle does the output drop linearly. Although affected by  $V_{OUT}$ ,  $V_{IN}$ ,  $f_{SW}$ ,

$t_{ON(MIN)},$  the equivalent series inductance (ESL) of the output capacitor, and other factors, the output droop,  $V_{DROOP},$  is usually about 3 times the linear drop of the first cycle:

$$V_{\text{DROOP}} = \frac{3 \cdot \Delta I_{\text{OUT}}}{C_{\text{OUT}} \cdot f_{\text{SW}}}$$

(8)

where  $\Delta I_{OUT}$  is the load step.

Transient performance and control loop stability can be improved with a higher  $C_{OUT}$  and/or the addition of a feedforward capacitor,  $C_{FF}$ , placed between  $V_{OUT}$  and FB. Capacitor  $C_{FF}$  provides phase lead compensation by creating a high frequency zero which improves the phase margin and the high-frequency response. The values used in the typical application circuits are a good starting point. LTpowerCAD<sup>®</sup> is a useful tool to help optimize  $C_{FF}$  and  $C_{OUT}$  for the desired transient performance.

Applying a load transient and monitoring the response of the system or using a network analyzer to measure the actual loop response are two ways to experimentally verify transient performance and control loop stability, and to optimize  $C_{FF}$  and  $C_{OUT}$ .

When using the load transient response method to stabilize the control loop, apply an output current pulse going from 20% to 100% of full load current having a very fast rise time. This will produce a transient on the output voltage. Monitor  $V_{OUT}$  for overshoot or ringing that might indicate a stability problem (see Application Note 149).

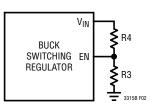

#### Using the Precision Enable Threshold

The LTC3315B has precision threshold enable pins for each buck regulator to enable or disable each buck. When both are forced low, the device enters into a low current shutdown mode.

The rising threshold of both EN comparators is 400mV, with 50mV of hysteresis. The EN pins can be tied to  $V_{IN}$  if the shutdown feature is not used. Adding a resistor divider from  $V_{IN}$  to an EN pin to ground programs the LTC3315B to regulate that output only when  $V_{IN}$  is above a desired voltage.

Typically, this threshold,  $V_{IN(EN)},$  is used in situations where the input supply is current limited, or has a

Figure 2. EN Divider

relatively high source resistance. A switching regulator draws near constant power from its input source, so source current increases as source voltage drops. This looks like a negative resistance load to the source and can cause the source to current limit or latch low under low source voltage conditions. The  $V_{IN(EN)}$  threshold prevents the regulator from operating at source voltages where problems may occur. Referring to Figure 2, this threshold can be adjusted by setting the values of R3 and R4 such that they satisfy the following equation:

$$V_{IN(EN)} = 400 \text{mV} \cdot \left(1 + \frac{\text{R4}}{\text{R3}}\right)$$

(9)

The buck regulator will remain off until V<sub>IN</sub> is above V<sub>IN(EN)</sub>. The buck regulator will remain enabled until V<sub>IN</sub> falls to 0.875 • V<sub>IN(EN)</sub> and EN is 350mV.

Alternatively a resistor divider from the output of one buck to the EN pin of the second buck to ground provides event based power-up sequencing as the first buck reaching regulation enables the second buck. Replace  $V_{IN(EN)}$  in Equation 9 with the desired output voltage of the first buck (e.g. 90% of the regulated value) at which the second buck is enabled.

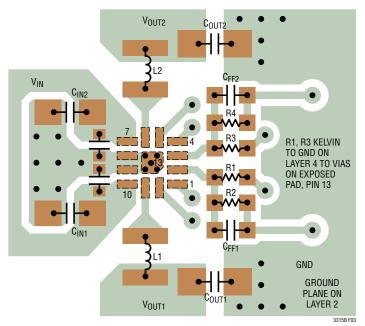

#### **PCB** Considerations

The LTC3315B is a high performance IC designed for high efficiency and fast transient response. For optimal results carefully consider the layout of the PCB board and follow the below list to ensure proper operation. See Figure 3 for a recommended PCB layout.

Connect the exposed pad of the package (Pin 13) directly to a large, unbroken ground plane under the application circuit on the layer closest to the surface layer to minimize thermal and electrical impedance. Additionally, short the exposed pad to ground

Figure 3. Recommended LTC3315B PCB Layout

pins 8 and 9 on the top layer. See the Analog Devices Application Note, *Application Notes for Thermally Enhanced Leaded Plastic Packages* for the proper size and layout of the thermal vias and solder stencils.

- 2. Both of the input supply pins should have local decoupling capacitors with their grounded pins connecting on the top layer to the ground plane around pin 8, pin 9, and the exposed pad. These capacitors provide the AC current to the internal power MOSFETs and their drivers. Large, switched currents flow in these capacitors and it is important to minimize inductance from these capacitors by choosing a small case size such as 0603 and placing them close to the V<sub>IN</sub> pins of the LTC3315B. To further minimize inductance and input noise, smaller 0201 capacitors can be placed as close as possible to the LTC3315B directly on the traces leading from V<sub>IN</sub> (Pin 7) and GND (Pin 8) and on the traces leading from V<sub>IN</sub> (Pin 10) and GND (Pin 9) minimal (if at all) increase in application footprint.

- 3. The switching power traces connecting SW1 and SW2 to their respective inductors should be minimized to reduce radiated EMI and parasitic coupling. Due to the large voltage swing on the switching nodes, high input impedance sensitive nodes, such as the feedback

nodes, should be kept far away or shielded from the switching nodes or poor performance could result.

4. The GND side of the switching regulator output capacitors connects directly to the thermal ground plane of the IC. Minimize the trace length from the output capacitor to the inductor(s)/pin(s).

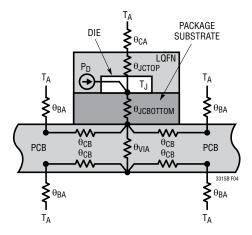

#### **High Temperature Considerations**

A thermal representation of the LTC3315B thermally enhanced LQFN package is shown in Figure 4 with the silicon die and thermal metrics identified. The current source represents power loss P<sub>D</sub> on the die; node voltages represent temperatures; electrical impedances represent conductive thermal impedances  $\theta_{JCBOTTOM}$ ,  $\theta_{JCTOP}$ ,  $\theta_{VIA}$ ,  $\theta_{CB}$ , and convective thermal impedances  $\theta_{CA}$  and  $\theta_{BA}$ . The junction temperature, T<sub>J</sub>, is calculated from the ambient temperature, T<sub>A</sub>, as:

$$\Gamma_{\rm J} = T_{\rm A} + P_{\rm D} \bullet \Theta_{\rm JA} \tag{11}$$

where, neglecting the  $\theta_{JCTOP}$  +  $\theta_{CA}$  path:

$$\Theta_{JA} \approx \Theta_{JCB} + \left(\frac{\Theta_{CB} + \Theta_{BA}}{2}\right) || \left(\frac{\Theta_{CB} + \Theta_{BA}}{2} + \Theta_{VIA}\right) \quad (12)$$

where  $\theta_{JCB} = \theta_{JCBOTTOM} = 10^{\circ}$ C/W. The value of  $\theta_{JA} = 51^{\circ}$ C/W reported in the Pin Configuration section corresponds to JEDEC standard 2S2P test PCB, which does not have good thermal vias, i.e.,  $\theta_{VIA}$  is relatively high. Assuming, somewhat arbitrarily but not unreasonably, that  $\theta_{VIA} \sim (\theta_{CB} + \theta_{BA})/2$ , and back calculating it is seen that  $(\theta_{CB} + \theta_{BA})/2 = \theta_{VIA} \approx 60^{\circ}$ C/W for such a board. The importance of thermal vias becomes clear observing that if the test PCB had low-thermal-resistance vias, the  $\theta_{JA}$  would have been reduced by up to 10°C/W, which is

an improvement of up to 20%. Similarly, having more ground planes that are larger, uninterrupted and higher-copper-weight improves  $\theta_{CB} + \theta_{BA}$ , which has a dominant effect on  $\theta_{JA}$ , given the low value of  $\theta_{JCBOTTOM}$  of the package. The maximum load current should be derated as the ambient temperature approaches the maximum junction rating. Power dissipation within the LTC3315B is estimated by calculating the total power loss from an efficiency measurement and subtracting the inductor loss.

Figure 4. Multi-Layer PCB with Thermal Vias Acts as a Heat Sink

### TYPICAL APPLICATIONS

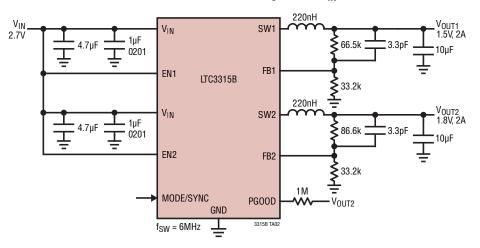

Dual 1.5V and 1.8V 2MHz, 6A Buck Regulators,  $V_{\text{IN}}$  = 2.7V

### **TYPICAL APPLICATIONS**

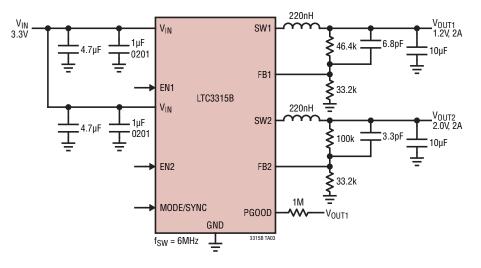

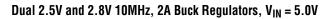

Dual 1.2V and 2.0V 6MHz, 2A Buck Regulators,  $V_{\text{IN}}$  = 3.3V

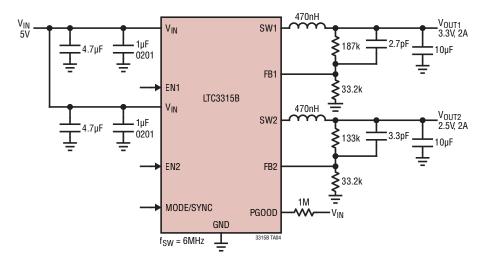

### TYPICAL APPLICATIONS

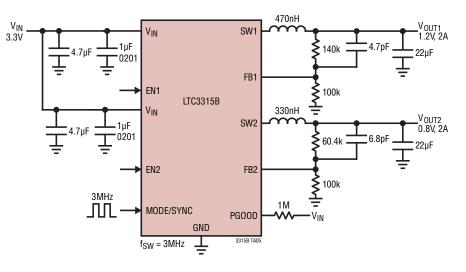

Dual 1.2V and 0.8V 3MHz, 2A Buck Regulators,  $V_{\text{IN}}$  = 3.3V

### PACKAGE DESCRIPTION

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Rev. 0