## Dual, Low Noise, Inductorless Step-Down DC/DC Converter

### **FEATURES**

- 2.7V to 5.5V Input Voltage Range

- No Inductors

- Typical Efficiency 50% Higher than LDOs

- Spread Spectrum Operation

- Low Input and Output Noise

- Shutdown Disconnects Load from V<sub>IN</sub>

- Dual Adjustable Independent Outputs (Range: 0.9V to 1.6V)

- Output Current: 250mA Each Output

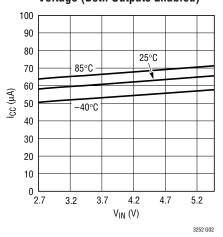

- Low Operating Current: I<sub>IN</sub> = 60μA Typ (35μA with One Output Enabled)

- Low Shutdown Current: I<sub>IN</sub> = 0.01µA Typ

- Soft-Start Limits Inrush Current at Turn On

- Short Circuit and Over Temperature Protected

- Available in 4mm × 3mm 12-Pin DFN Package

## **APPLICATIONS**

- Handheld Electronic Devices

- Cellular Phones

- Low Voltage Logic Supplies

- DSP Power Supplies

- 3.3V to 1.5V Conversion

### DESCRIPTION

The LTC®3252 is a switched capacitor step-down DC/DC converter that produces two adjustable regulated outputs from a single 2.7V to 5.5V input. The part uses switched capacitor fractional conversion to achieve a typical efficiency increase of 50% over that of a linear regulator. No inductors are required.

A unique constant frequency, spread spectrum architecture provides a very low noise regulated output as well as low noise at the input. The part also has Burst Mode® operation to provide high efficiency at low output currents, as well as ultralow current shutdown.

Low operating currents ( $60\mu A$  with both outputs enabled,  $35\mu A$  with one output enabled) and low external parts count make the LTC3252 ideally suited for space-constrained battery-powered applications. The part is short-circuit and overtemperature protected and is available in a tiny  $4mm \times 3mm$  12-pin DFN package.

(7), LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a registered trademark of Linear Technology Corporation.

## TYPICAL APPLICATION

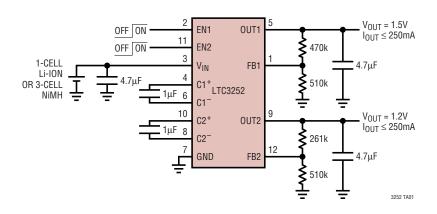

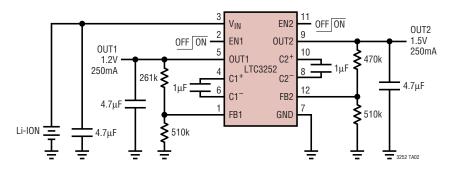

#### 1.5V and 1.2V Output Voltages with Shutdown

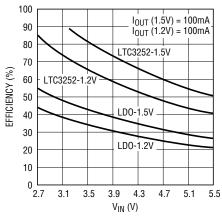

#### 1.5V/1.2V Efficiency vs Input Voltage

3252 TA01a

3252f

## **ABSOLUTE MAXIMUM RATINGS**

(Notes 1, 6)

| ·                                                      |

|--------------------------------------------------------|

| V <sub>IN</sub> to GND0.3V to 6.0V                     |

| EN1, EN2, FB1, FB2 to GND $-0.3V$ to $(V_{IN} + 0.3V)$ |

| I <sub>OUT1</sub> , I <sub>OUT2</sub> (Note 3)         |

| Operating Ambient Temperature Range                    |

| (Note 2)40°C to 85°C                                   |

| Storage Temperature Range65°C to 125°C                 |

| Lead Temperature (Soldering, 10 sec)300°C              |

|                                                        |

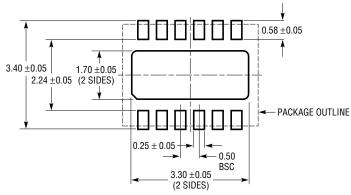

## PACKAGE/ORDER INFORMATION

| TOP VIEW                                                                                                                                      | 12 FB2             | ORDER PART<br>NUMBER |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|

|                                                                                                                                               | EN2<br>C2+<br>OUT2 | LTC3252EDE           |

| OUT1 5                                                                                                                                        |                    | DE PART<br>MARKING   |

| 12-LEAD (4mm × 3mm) PLA<br>EXPOSED PAD IS GROU<br>(MUST BE SOLDERED TO<br>T <sub>JMAX</sub> = 125°C, θ <sub>JA</sub> = 40°C/W, θ <sub>J</sub> | IND<br>PCB)        | 3252                 |

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{IN} = 3.6V$ ,  $V_{OUT1} = V_{OUT2} = 1.5V$ ,  $C1 = C2 = 1\mu F$ ,  $Cin = C_{OUT1} = C_{OUT2} = 4.7\mu F$  (all capacitors ceramic) unless otherwise noted.

| SYMBOL              | PARAMETER                                     | CONDITIONS                                                                                                              |   | MIN  | TYP        | MAX  | UNITS             |

|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---|------|------------|------|-------------------|

| $V_{IN}$            | Min Operating Voltage                         | (Note 4)                                                                                                                | • | 2.7  |            |      | V                 |

|                     | Max Operating Voltage                         |                                                                                                                         | • |      |            | 5.5  | V                 |

| I <sub>VIN</sub>    | Operating Current,<br>Both Outputs Enabled    | $I_{OUT} = 0$ mA, $V_{EN1} = V_{IN}$ , $V_{EN2} = V_{IN}$ , $2.7$ V $\leq V_{IN} \leq 5.5$ V                            | • |      | 60         | 100  | μА                |

|                     | Operating Current,<br>One Output Enabled      | $I_{OUT} = 0$ mA, $V_{EN1} = 0$ , $V_{EN2} = V_{IN}$ or $V_{EN1} = V_{IN}$ , $V_{EN2} = 0$ , $2.7V \le V_{IN} \le 5.5V$ | • |      | 35         | 60   | μА                |

|                     | Shutdown Current                              | $V_{M0} = 0V, V_{M1} = 0V, 2.7V \le V_{IN} \le 5.5V$                                                                    | • |      | 0.01       | 1    | μΑ                |

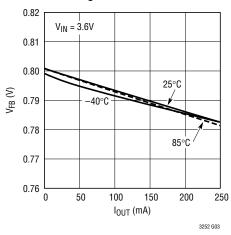

| $V_{FB1}, V_{FB2}$  | Feedback Voltage                              | $I_{OUT} = 0$ mA, $2.7$ V $\leq V_{IN} \leq 5.5$ V                                                                      | • | 0.78 | 0.8        | 0.82 | V                 |

| I <sub>OUT1</sub>   | Output Current                                | $V_{EN1} = V_{IN}$                                                                                                      | • | 250  |            |      | mA                |

| I <sub>OUT2</sub>   | Output Current                                | $V_{EN2} = V_{IN}$                                                                                                      | • | 250  |            |      | mA                |

| I <sub>FB</sub>     | FB1, FB2 Input Current                        | $V_{FB1} = V_{FB2} = 0.85V$                                                                                             | • | -50  |            | 50   | nA                |

| V <sub>RIPPLE</sub> | Output Ripple (OUT1 or OUT2)                  | I <sub>OUT</sub> = 250mA                                                                                                |   |      | 10         |      | mV <sub>P-P</sub> |

|                     | Spread Spectrum Frequency Range               | f <sub>MIN</sub> Switching Frequency<br>f <sub>MAX</sub> Switching Frequency                                            | • | 0.8  | 1.0<br>1.6 | 2.0  | MHz<br>MHz        |

| V <sub>IH</sub>     | EN1, EN2 Input High Voltage                   | $2.7V \le V_{IN} \le 5.5V$                                                                                              | • | 1.2  | 0.8        |      | V                 |

| $V_{IL}$            | EN1, EN2 Input Low Voltage                    | $2.7V \le V_{IN} \le 5.5V$                                                                                              | • |      | 0.8        | 0.4  | V                 |

| I <sub>IH</sub>     | EN1, EN2 Input High Current                   | EN1 = V <sub>IN</sub> , EN2 = V <sub>IN</sub>                                                                           | • | -1   |            | 1    | μА                |

| I <sub>IL</sub>     | EN1, EN2 Input Low Current                    | EN1 = 0V, EN2 = 0V                                                                                                      | • | -1   |            | 1    | μΑ                |

| t <sub>ON</sub>     | Turn On Time                                  | $R_{OUT} = 3\Omega$                                                                                                     |   |      | 0.8        |      | ms                |

| OUT1, OUT2          | Load Regulation (Referred to FB pin)          |                                                                                                                         |   |      | 0.08       |      | mV/mA             |

|                     | Line Regulation                               | $0 \le I_{OUT1} \le 250 \text{mA} \text{ or } 0 \le I_{OUT2} \le 250 \text{mA}$                                         |   |      | 0.2        |      | %/V               |

| R <sub>OL</sub>     | Open Loop Output Impedance,<br>(OUT1 or OUT2) | V <sub>IN</sub> = 3.0V, I <sub>OUT</sub> = 200mA, V <sub>FB</sub> = 0.74V (Note 5)                                      | • |      | 1          | 1.4  | Ω                 |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LTC3252EDE is guaranteed to meet specified performance from  $0^{\circ}$ C to  $70^{\circ}$ C. Specifications over the  $-40^{\circ}$ C and  $85^{\circ}$ C operating temperature range are assured by design characterization and correlation with statistical process control.

Note 3: Based on long-term current density limitations.

Note 4: Minimum operating voltage required for regulation is:

$$V_{IN} > 2 \cdot (V_{OUT(MIN)} + R_{OL} \cdot I_{OUT})$$

**Note 5:** Output not in regulation;  $R_{OL} = (V_{IN}/2 - V_{OUT})/I_{OUT}$ .

**Note 6:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

## TYPICAL PERFORMANCE CHARACTERISTICS

#### No Load Supply Current vs Supply Voltage (One Output Enabled)

#### No Load Supply Current vs Supply Voltage (Both Outputs Enabled)

#### FB Voltage vs Load Current

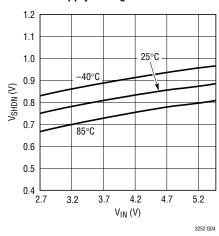

## EN1/EN2 Input Threshold Voltage vs Supply Voltage

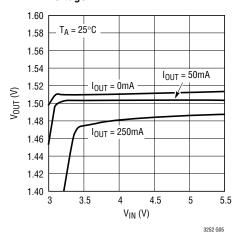

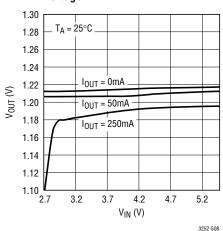

#### 1.5V Output Voltage vs Supply Voltage

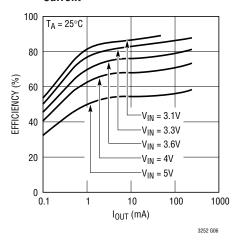

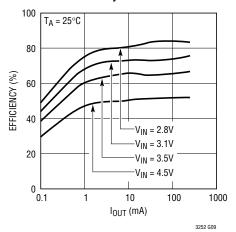

#### 1.5V Output Efficiency vs Output Current

## TYPICAL PERFORMANCE CHARACTERISTICS

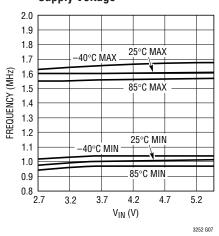

#### Oscillator Max/Min Frequency vs Supply Voltage

## 1.2V Output Voltage vs Supply Voltage

#### 1.2V Efficiency vs Load Current

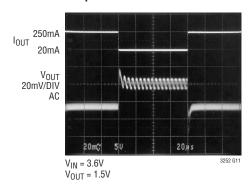

## Output Current Transient Response

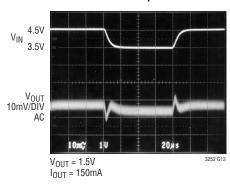

#### **Line Transient Response**

## PIN FUNCTIONS

**FB1 (Pin 1):** Feedback Input Pin 1. An output divider should be connected from OUT1 to FB1 to program the output voltage.

**EN1 (Pin 2):** Input Enable Pin 1. When EN1 is high, OUT1 is enabled. When EN1 is low OUT1 is shut down.

$V_{IN}$  (Pin 3): Input Supply Voltage. Operating  $V_{IN}$  may be between 2.7V and 5.5V. Bypass  $V_{IN}$  with  $a \ge 4.7 \mu F$  (1 $\mu F$  min) low ESR ceramic capacitor to GND ( $C_{IN}$ ).

C1+ (Pin 4): Flying Capacitor 1 Positive Terminal (C1).

**OUT1 (Pin 5):** Regulated Output Voltage 1. OUT1 is disconnected from  $V_{IN}$  when in shutdown. Bypass OUT1 with a low ESR ceramic capacitor to GND ( $C_{01}$ ). See Output Capacitor Selection section for size requirements.

C1<sup>-</sup> (Pin 6): Flying Capacitor 1 Negative Terminal (C1).

**GND (Pin 7):** Ground. Connect to a ground plane for best performance.

LINEAR

## PIN FUNCTIONS

**C2**<sup>-</sup> (**Pin 8**): Flying Capacitor 2 Negative Terminal (C2).

**OUT2** (Pin 9): Regulated Output Voltage 2. OUT2 is disconnected from  $V_{IN}$  when in shutdown. Bypass OUT2 with a low ESR ceramic capacitor to GND ( $C_{02}$ ). See Output Capacitor Selection section for size requirements.

C2+ (Pin 10): Flying Capacitor 2 Positive Terminal (C2).

**EN2 (Pin 11):** Input Enable Pin 2. When EN2 is high, OUT2 is enabled. When EN2 is low OUT2 is shut down.

**FB2** (**Pin 12**): Feedback Input Pin 2. An output divider should be connected from OUT2 to FB2 to program the output voltage.

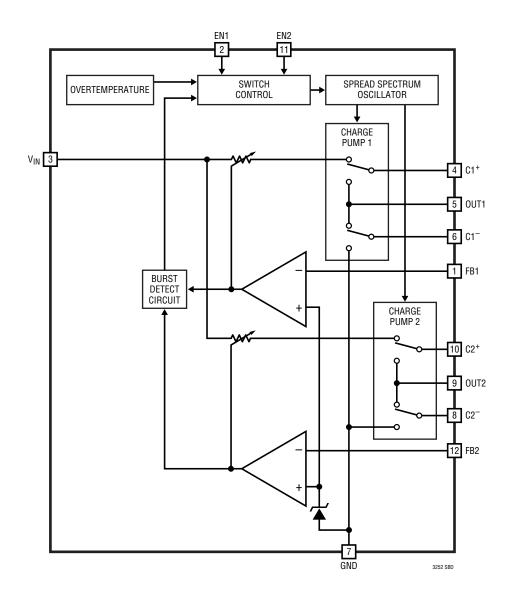

## SIMPLIFIED BLOCK DIGRAM

The LTC3252 has two switched capacitor charge pumps to step down  $V_{IN}$  to two regulated output voltages. The two charge pumps operate 180° out of phase to reduce input ripple. Regulation is achieved by sensing each output voltage through an external resistor divider and modulating the charge pump output current based on the error signal. A 2-phase nonoverlapping clock activates the two charge pumps running them out of phase from each other. On the first phase of the clock current is transferred from  $V_{IN}$ , through the external flying capacitor 1, to OUT1 via the switches of charge pump 1. Not only is current being delivered to OUT1 on the first phase, but the flying capacitor is also being charged up. On the second phase of the clock, flying capacitor 1 is connected from OUT1 to ground, transferring the charge stored during the first phase of the clock to OUT1 via the switches of charge pump 1. Charge pump 2 operates in the same manner to supply current to OUT2, but with the phases of the clock reversed relative to charge pump 1. Using this method of switching, only half of the output current for each output is delivered from V<sub>IN</sub>, thus achieving a 50% increase in efficiency over a conventional LDO. A spread spectrum oscillator, which utilizes random switching frequencies between 1MHz and 1.6MHz, sets the rate of charging and discharging of the flying capacitors. This architecture achieves extremely low output noise. Input noise is significantly reduced compared to conventional charge pumps. The outputs also have a low current burst mode to improve efficiency even at light loads.

In shutdown mode all circuitry is turned off and the LTC3252 draws only leakage current from the  $V_{\text{IN}}$  supply. Furthermore, OUT1 and OUT2 are disconnected from  $V_{\text{IN}}$ . The EN1 and EN2 pins are CMOS inputs with threshold voltages of approximately 0.8V to allow regulator control with low voltage logic levels. The LTC3252 is in shutdown when a logic low is applied to both enable pins. Since the mode pins are high impedance CMOS inputs, they should never be allowed to float. Always drive the enable pins with valid logic levels.

#### **Short-Circuit/Thermal Protection**

The LTC3252 has built-in short-circuit current limiting as well as over temperature protection. During short-circuit conditions, internal circuitry automatically limits each output to approximately 500mA of current. If fault conditions (such as shorted outputs) cause excessive self heating on chip such that the junction temperature exceeds approximately 160°C, the thermal shutdown circuitry will disable the charge pumps. The IC resumes operation once the junction temperature drops back to approximately 155°C. The LTC3252 will cycle in and out of thermal shutdown without latchup or damage until the overstress condition is removed. Long term overstress ( $I_{OUT1}$  or  $I_{OUT2} > 400$ mA, and/or  $I_{J} > 125$ °C) should be avoided as it can degrade the performance or shorten the life of the part.

#### **Soft-Start**

To prevent excessive current flow at  $V_{IN}$  during start-up, the LTC3252 has built-in soft-start circuitry on each output. When an output is enabled, the soft-start circuitry increases the amount of current available from the output linearly over a period of approximately 500 $\mu$ s. The soft-start circuitry is disabled shortly after the output achieves regulation.

#### **Spread Spectrum Operation**

Switching regulators can be particularly troublesome where electromagnetic interference (EMI) is concerned. Switching regulators operate on a cycle-by-cycle basis to transfer power to an output. In most cases, the frequency of operation is either fixed or is a constant based on the output load. This method of conversion creates large components of noise at the frequency of operation (fundamental) and multiples of the operating frequency (harmonics).

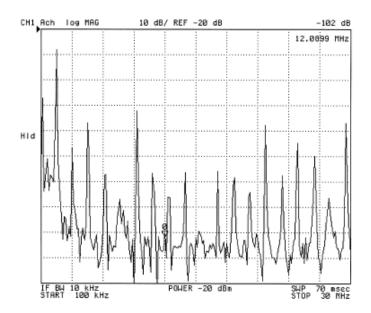

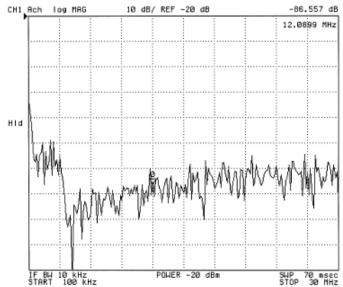

Unlike conventional buck converters, the LTC3252's internal oscillator is designed to produce a clock pulse whose period is random on a cycle-by-cycle basis but fixed between 1MHz and 1.6MHz. This has the benefit of spreading the switching noise over a range of frequencies, thus significantly reducing the peak noise. Figures 1 and 2 show how the spread spectrum feature of the LTC3252 significantly reduces the peak harmonic noise and virtually elliminates harmonics compared to a conventional buck converter.

Spread spectrum operation is always enabled but is most effective when the LTC3252's outputs are out of Burst Mode operation and the oscillator is running continuously (see the Low Current Burst Mode Operation section).

#### **Low Current Burst Mode Operation**

To improve efficiency at low output currents, a Burst Mode operation function is included in the LTC3252. An output current sense is used to detect when the required output current of both outputs drop below an internally set

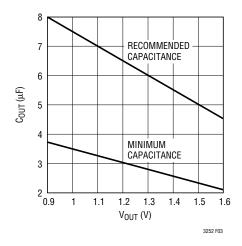

threshold (30mA typ). When this occurs, the part shuts down the internal oscillator and goes into a low current operating state. The LTC3252 will remain in the low current operating state until either output has dropped enough to require another burst of current. The LTC3252 resumes continuous operation when the load on one or both outputs exceeds the internally set threshold. Unlike traditional charge pumps where the burst current is highly dependant on many factors (i.e., supply, switch strength, capacitor selection, etc.), the LTC3252's burst current is set by the burst threshold and hysteresis. This means that the output ripple voltage in Burst Mode operation is relatively consistent and is typically about 12mV with a 4.7µF output capacitor on a 1.5V output. The ripple voltage amplitude is a direct function of the output capacitor size. Burst Mode operation ripple voltage does increase slightly at lower output voltages due to the increase in loop gain. Users can counteract output voltage ripple increase through the use of a slightly larger output capacitor. See Recommended Output Capacitance guidelines of Figure 3.

Figure 1. Conventional Buck Input Noise

Figure 2. LTC3252 Input Noise

#### **Output Capacitor Selection**

The style and value of capacitors used with the LTC3252 determine several important parameters such as regulator control loop stability, output ripple and charge pump strength.

The switching nature of the LTC3252 minimizes output noise significantly but not completely. What small ripple that exists at an output is controlled by the value of output capacitor directly. Increasing the size of the output capacitor will proportionately reduce the output ripple. The ESR (equivalent series resistance) of the output capacitor plays the dominant role in output noise. When the LTC3252 switches between clock phases there is a period where all switches are turned off. This "blanking period" shows up as a spike at the output and is a direct function of the output current times the ESR value. To reduce output noise and ripple, it is suggested that a low ESR ( $<0.08\Omega$ ) ceramic capacitor be used for the output capacitor. Tantalum and aluminum capacitors are not recommended because of their high ESR.

Both the style and value of the output capacitors can significantly affect the stability of the LTC3252. As shown in the Simplified Block Diagram, the LTC3252 uses a control loop to adjust the strength of each charge pump to match the current required at the output. The error signal of each loop is stored directly on each output capacitor. Thus the output capacitors also serve to form the dominant pole in each control loop. Figure 3 is a graph of the recommended output capacitance, and minimum capaci-

Figure 3. Output Capacitance vs Output Voltage

tance required for good transient response (see the Ceramic Capacitor Selection Guidelines section).

Likewise excessive ESR on the output capacitor will tend to degrade the loop stability of the LTC3252. The closed loop output impedance of the LTC3252 is approximately:

$$R_0 = 0.08\Omega \bullet \frac{V_{OUT}}{0.8V}$$

For example, with the output programmed to 1.5V, the  $R_0$  is 0.15 $\Omega$ , which produces a 38mV output change for a 250mA load current step. For stability and good load transient response it is important for the output capacitor to have 0.1 $\Omega$  or less of ESR. Ceramic capacitors typically have exceptional ESR and combined with a tight board layout should yield excellent stability and load transient performance.

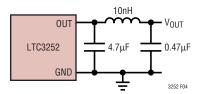

Further output noise reduction can be achieved by filtering the LTC3252 outputs through a very small series inductor as shown in Figure 4. A 10nH inductor will reject the fast output transients caused by the blanking period, thereby presenting a nearly constant output voltage. For economy the 10nH inductor can be fabricated on the PC board with about 1cm (0.4") of PC board trace.

Figure 4. 10nH Inductor Used for Additional Output Noise Reduction

#### **VIN Capacitor Selection**

The low noise, dual phase architecture used by the LTC3252 makes input noise filtering much less demanding than conventional charge pump regulators. The LTC3252 input current will transition between  $I_{OUT1}/2$  and  $I_{OUT2}/2$  for each half cycle of the oscillator. The blanking period described in the  $V_{OUT}$  section also effects the input. For this reason it is recommended that a low ESR 4.7  $\mu F$  (1  $\mu F$  min) or greater ceramic capacitor be used for  $C_{IN}$  (see the Ceramic Capacitor Selection Guidelines section). Aluminum and tantalum capacitors can be used but are not recommended because of their high ESR.

3252f

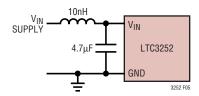

Further input noise reduction can be achieved by filtering the input through a very small series inductor as shown in Figure 5. A 10nH inductor will reject the fast input transients caused by the blanking period, thereby presenting a nearly constant load to the input supply. For economy the 10nH inductor can be fabricated on the PC board with about 1cm (0.4") of PC board trace.

Figure 5. 10nH Inductor Used for Additional Input Noise Reduction

#### Flying Capacitor Selection

Warning: A polarized capacitor such as tantalum or aluminum should never be used for the flying capacitors since their voltages can reverse upon start-up of the LTC3252. Ceramic capacitors should always be used for the flying capacitors.

The flying capacitors control the strength of the charge pump. In order to achieve the rated output current it is necessary for the flying capacitor to have at least  $0.4\mu F$  of capacitance over operating temperature with a 2V bias (see the Ceramic Capacitor Selection Guidelines). If 100mA or less of current is required from an output then its associated flying capacitor minimum can be reduced to  $0.15\mu F$ .

### **Ceramic Capacitor Selection Guidelines**

Capacitors of different materials lose their capacitance with higher temperature and voltage at different rates. For example, a ceramic capacitor made of X7R material will retain most of its capacitance from  $-40^{\circ}$ C to  $85^{\circ}$ C whereas a Z5U or Y5V style capacitor will lose considerable capacitance over that range (60% to 80% loss typical). Z5U and Y5V capacitors may also have a very strong voltage coefficient causing them to lose an additional 60% or more of their capacitance when the rated voltage is applied. Therefore, when comparing different capacitors it is often more appropriate to compare the amount of achievable capacitance for a given case size rather than

discussing the specified capacitance value. For example, over rated voltage and temperature conditions, a  $4.7\mu F$ , 10V, Y5V ceramic capacitor in a 0805 case may not provide any more capacitance than a  $1\mu F$ , 10V, X7R available in the same 0805 case. In fact, over bias and temperature range, the  $1\mu F$ , 10V, X7R will provide more capacitance than the  $4.7\mu F$ , 10V, Y5V. The capacitor manufacturer's data sheet should be consulted to determine what value of capacitor is needed to ensure minimum capacitance values are met over operating temperature and bias voltage.

Below is a list of ceramic capacitor manufacturers and how to contact them:

| AVX         | www.avxcorp.com |

|-------------|-----------------|

| Kemet       | www.kemet.com   |

| Murata      | www.murata.com  |

| Taiyo Yuden | www.t-yuden.com |

| Vishay      | www.vishay.com  |

|             |                 |

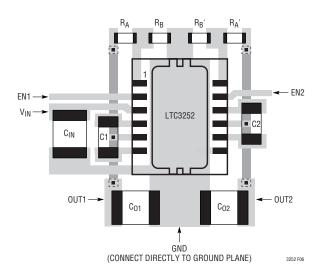

## **Layout Considerations**

Due to the high switching frequency and transient currents produced by the LTC3252 careful board layout is necessary for optimal performance. A true ground plane and short connections to all capacitors will improve performance and ensure proper regulation under all conditions. Figure 7 shows the suggested layout configuration. Note the exposed paddle of the package is ground (GND) and must be soldered to the PCB ground.

The flying capacitor pins C1+, C1-, C2+ and C2- will have very high edge rate wave forms. The large dv/dt on these pins can couple energy capacitively to adjacent printed circuit board runs. Magnetic fields can also be generated if the flying capacitors are not close to the LTC3252 (i.e., the loop area is large). To decouple capacitive energy transfer, a Faraday shield may be used. This is a grounded PC trace between the sensitive node and the LTC3252 pins. For a high quality AC ground, it should be returned to a solid ground plane that extends all the way to the LTC3252. Keep the FB traces away from or shielded from the flying capacitor traces or degraded performance could result.

#### Thermal Management

To reduce the maximum junction temperature, a good thermal connection to the PC board is recommended. Soldering the exposed paddle of the IC to the PCB and maintaining a solid ground plane under the device on one or more layers of the PC board, the thermal resistance of the package can be as small as 40°C/W. By applying the suggested thermal management techniques the IC junction temperature should never exceed 125°C even under worst case operating conditions.

#### **Power Efficiency**

The power efficiency  $(\eta)$  of the LTC3252 is approximately 50% higher than a conventional linear regulator. This occurs because the input current for a 2-to-1 step-down charge pump is approximately half the output current. For an ideal 2-to-1 step-down charge pump the power efficiency is given by:

$$\eta \equiv \frac{P_{OUT}}{P_{IN}} = \frac{V_{OUT} \bullet I_{OUT}}{V_{IN} \bullet \frac{1}{2} I_{OUT}} = \frac{2V_{OUT}}{V_{IN}}$$

The switching losses and quiescent current of the LTC3252 are designed to minimize efficiency loss over the entire output current range, causing only a couple % error from the theoretical efficiency. For example with  $V_{\text{IN}}=3.6V$ ,

Figure 6. Suggested Layout for the LTC3252

$I_{OUT1}$  = 150mA and OUT1 regulating at 1.5V the measured efficiency is 80.6% which is in close agreement with the theoretical 83.3% calculation.

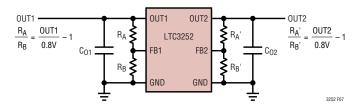

# Programming the LTC3252 Output Voltages (FB1 and FB2 Pin)

Each output of the LTC3252 is programmed to an arbitrary voltage via an external resistive divider. Figure 7 shows the required voltage divider connection. The voltage divider ratio is given by the expression:

$$\frac{R_A}{R_B} = \frac{OUT}{0.8V} - 1$$

Typical values for total voltage divider resistance can range from several  $k\Omega s$  up to  $1M\Omega$ .

The user may want to consider load regulation when setting the desired output voltage. The closed loop output impedance of the LTC3252 is approximately:

$$R_0 = 0.08\Omega \cdot \frac{OUT}{0.8V}$$

For a 1.5V output,  $R_0$  is 0.15 $\Omega$ , which produces a 38mV output change for a 250mA load current step. Thus, the user may want to target an unloaded output voltage slightly higher than desired to compensate for the output load conditions. The output may be programmed for regulation voltages of 0.9V to 1.6V.

Since the LTC3252 employs a 2-to-1 charge pump architecture, it is not possible to achieve output voltages greater than half the available input voltage. The minimum  $V_{\text{IN}}$  supply required for regulation can be determined by the following equation:

$$V_{IN} (MIN) \le 2 \cdot (V_{OUT} (MIN) + I_{OUT} \cdot R_{OL})$$

Figure 7. Programming the LTC3252

LINEAR

## TYPICAL APPLICATION

#### Li-Ion to 1.5V/1.2V Outputs

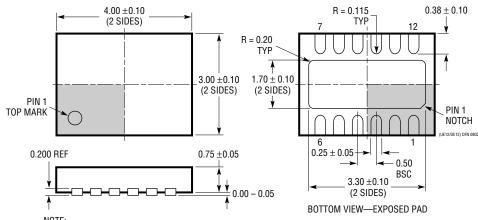

## PACKAGE DESCRIPTION

#### **DE/UE Package** 12-Lead Plastic DFN (4mm × 3mm)

(Reference LTC DWG # 05-08-1695)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

- NOTE:

- 1. DRAWING PROPOSED TO BE A VARIATION OF VERSION

- (WGED) IN JEDEC PACKAGE OUTLINE MO-229 2. ÀLL DIMENSIONS ARE IN MILLIMETERS

- 3. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 4. EXPOSED PAD SHALL BE SOLDER PLATED