LTC2704

## Quad 12-, 14- and 16-Bit Voltage Output SoftSpan DACs with Readback

## FEATURES

- Six Programmable Output Ranges: Unipolar: 0V to 5V, 0V to 10V Bipolar: ±5V, ±10V, ±2.5V, -2.5V to 7.5V

- Serial Readback of All On-Chip Registers

- 1LSB INL and DNL Over the Industrial Temperature Range (LTC2704-14/LTC2704-12)

- Force/Sense Outputs Enable Remote Sensing

- Glitch Impulse: < 2nV-sec

- Outputs Drive ±5mA

- Pin Compatible 12-, 14- and 16-Bit Parts

- Power-On and Clear to Zero Volts

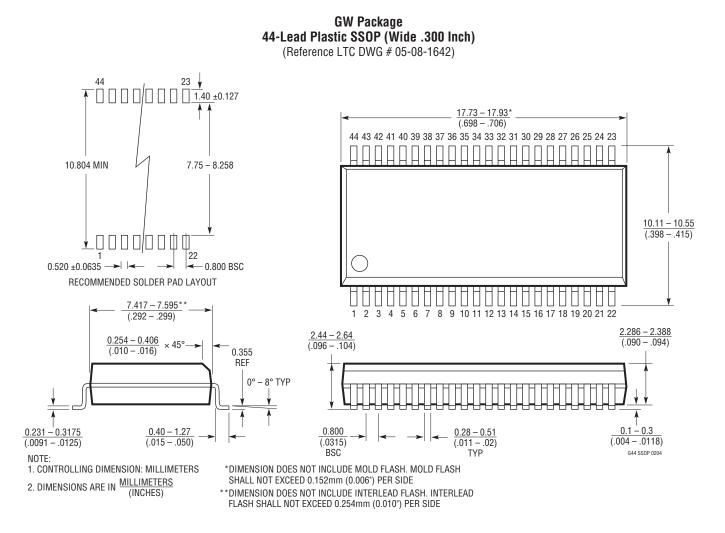

- 44-Lead SSOP Package

## **APPLICATIONS**

- Process Control and Industrial Automation

- Direct Digital Waveform Generation

- Software Controlled Gain Adjustment

- Automated Test Equipment

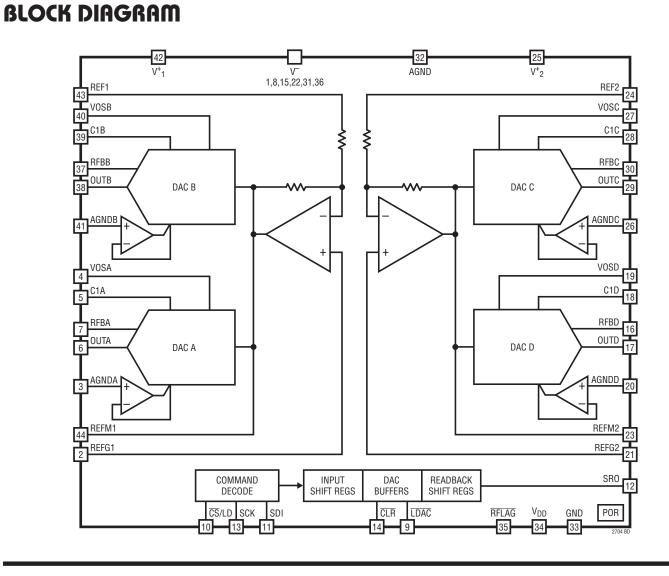

## DESCRIPTION

The LTC<sup>®</sup>2704-16/LTC2704-14/LTC2704-12 are serial input, 12-, 14- or 16-bit, voltage output SoftSpan<sup>TM</sup> DACs that operate from 3V to 5V logic and  $\pm$ 5V to  $\pm$ 15V analog supplies. SoftSpan offers six output spans—two unipolar and four bipolar—fully programmable through the 3-wire SPI serial interface. INL is accurate to 1LSB (2LSB for the LTC2704-16). DNL is accurate to 1LSB for all versions.

Readback commands allow verification of any on-chip register in just one 24- or 32- bit instruction cycle. All other commands produce a "rolling readback" response from the LTC2704, dramatically reducing the needed number of instruction cycles.

A Sleep command allows any combination of DACs to be powered down. There is also a reset flag and an offset adjustment pin for each channel.

∠ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. SoftSpan is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

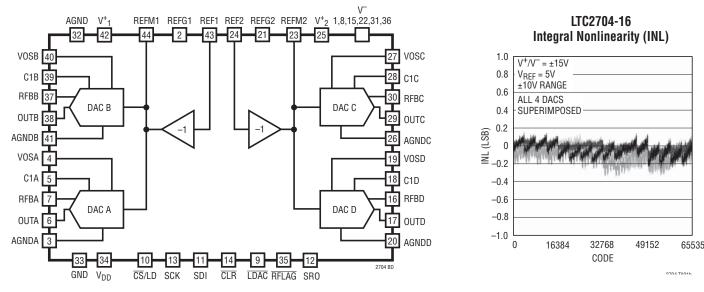

## **BLOCK DIAGRAM**

####

| (NOTE 1)                                                                       |

|--------------------------------------------------------------------------------|

| Total Supply Voltage $V_{1}^{+}$ , $V_{2}^{+}$ to $V^{-}$ 0.3V to 36V          |

| V <sup>+</sup> 1, V <sup>+</sup> 2, REF1, REF2, REFM1, REFM2,                  |

| OUTx, RFBx, V <sub>OSx</sub> to GND, AGND,                                     |

| AGNDx, C1x, REFG1, REFG218V                                                    |

| GND, AGND, AGNDx, C1x, REFG1, REFG2 to V <sup>+</sup> 1,                       |

| V <sup>+</sup> <sub>2</sub> , V <sup>−</sup> , REF1, REF2, REFM1, REFM2, OUTx, |

| RFBx, V <sub>OSx</sub>                                                         |

| OUTA, RFBA, V <sub>OSA</sub> , OUTB, RFBB, VOSB, REF1,                         |

| REFM1 to GND, AGND $V^ 0.3V$ to $V_{1}^+ + 0.3V$                               |

| OUTC, RFBC, V <sub>OSC</sub> , OUTD, RFBD, V <sub>OSD</sub> , REF2, REFM2      |

| to GND, AGND $V^ 0.3V$ to $V^+_2 + 0.3V$                                       |

| V <sub>DD</sub> , Digital Inputs/Outputs to GND0.3V to 7V                      |

| Digital Inputs/Outputs to V <sub>DD</sub> 0.3V                                 |

| GND, AGNDx, REFG1, REFG2 to AGND±0.3V                                          |

| C1x to AGNDx±0.3V                                                              |

| V <sup>-</sup> to Any Pin0.3V                                                  |

| Maximum Junction Temperature 150°C                                             |

| Operating Temperature Range                                                    |

| LTC2704C                                                                       |

| LTC2704I40°C to 85°C                                                           |

| Storage Temperature Range–65°C to 150°C                                        |

| Lead Temperature (Soldering, 10 sec)                                           |

|                                                                                |

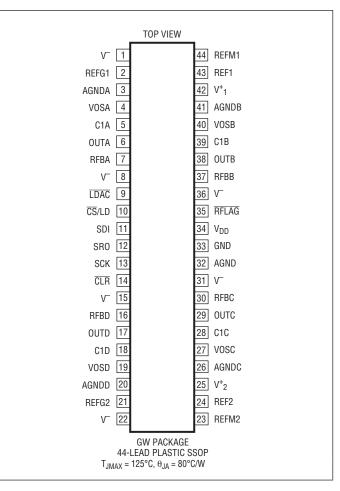

# PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING  | PACKAGE DESCRIPTION  | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|----------------------|-------------------|

| LTC2704CGW-16#PBF | LTC2704CGW-16#TRPBF | LTC2704CGW-16 | 44-Lead Plastic SSOP | 0°C to 70°C       |

| LTC2704IGW-16#PBF | LTC2704IGW-16#TRPBF | LTC2704IGW-16 | 44-Lead Plastic SSOP | -40°C to 85°C     |

| LTC2704CGW-14#PBF | LTC2704CGW-14#TRPBF | LTC2704CGW-14 | 44-Lead Plastic SSOP | 0°C to 70°C       |

| LTC2704IGW-14#PBF | LTC2704IGW-14#TRPBF | LTC2704IGW-14 | 44-Lead Plastic SSOP | -40°C to 85°C     |

| LTC2704CGW-12#PBF | LTC2704CGW-12#TRPBF | LTC2704CGW-12 | 44-Lead Plastic SSOP | 0°C to 70°C       |

| LTC2704IGW-12#PBF | LTC2704IGW-12#TRPBF | LTC2704IGW-12 | 44-Lead Plastic SSOP | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

**ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ ,  $V_1^+ = V_2^+ = 15V$ ,  $V_{-}^- = -15V$ ,  $V_{DD} = 5V$ , REF1 = REF2 = 5V, AGND = AGNDx = REFG1 = REFG2 = GND = 0V.

|                 |                                            |                                                                                                                                                                                                                                                                                       |   | LTC      |                      | I-12                         |       | C2704                        | I-14                         | LTC2704-16 |                |                                            |                      |

|-----------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|----------------------|------------------------------|-------|------------------------------|------------------------------|------------|----------------|--------------------------------------------|----------------------|

| SYMBOL          | PARAMETER                                  | CONDITIONS                                                                                                                                                                                                                                                                            |   | MIN T    | YP                   | MAX                          | MIN   | ТҮР                          | MAX                          | MIN        | ТҮР            | MAX                                        | UNITS                |

| Accuracy        |                                            |                                                                                                                                                                                                                                                                                       |   |          |                      |                              |       |                              |                              |            |                |                                            |                      |

|                 | Resolution                                 |                                                                                                                                                                                                                                                                                       | • | 12       |                      |                              | 14    |                              |                              | 16         |                |                                            | Bits                 |

|                 | Monotonicity                               |                                                                                                                                                                                                                                                                                       | • | 12       |                      |                              | 14    |                              |                              | 16         |                |                                            | Bits                 |

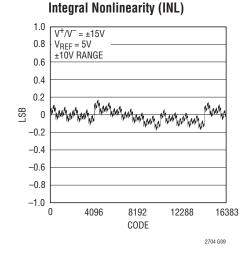

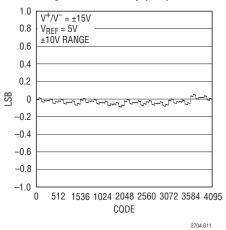

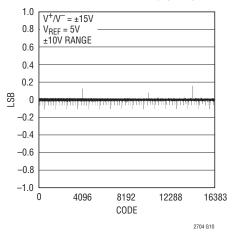

| INL             | Integral Nonlinearity                      | V <sub>REF</sub> = 5V                                                                                                                                                                                                                                                                 | • |          |                      | ±1                           |       |                              | ±1                           |            |                | ±2                                         | LSB                  |

| DNL             | Differential Nonlinearity                  | V <sub>REF</sub> = 5V                                                                                                                                                                                                                                                                 | • |          |                      | ±1                           |       |                              | ±1                           |            |                | ±1                                         | LSB                  |

| GE              | Gain Error                                 | V <sub>REF</sub> = 5V                                                                                                                                                                                                                                                                 | • | ±(       | ).5                  | ±2                           |       | ±1                           | ±5                           |            | ±4             | ±20                                        | LSB                  |

|                 | Gain Temperature<br>Coefficient            | $\Delta$ Gain/ $\Delta$ Temperature                                                                                                                                                                                                                                                   | • | ±        | :2                   |                              |       | ±2                           |                              |            | ±2             |                                            | ppm/°C               |

| V <sub>OS</sub> | Unipolar Zero-Scale<br>Error               | $\begin{array}{l} \mbox{Span} = 0\mbox{V to 5V}, \mbox{T}_A = 25\mbox{°C}\\ \mbox{Span} = 0\mbox{V to 10V}, \mbox{T}_A = 25\mbox{°C}\\ \mbox{Span} = 0\mbox{V to 5V}\\ \mbox{Span} = 0\mbox{V to 10V} \end{array}$                                                                    | • | ±1<br>±1 | 80<br>00<br>40<br>50 | ±200<br>±300<br>±400<br>±600 |       | ± 80<br>±100<br>±140<br>±150 | ±200<br>±300<br>±400<br>±600 |            | ±140           | $\pm 200 \\ \pm 300 \\ \pm 400 \\ \pm 600$ | μV<br>μV<br>μV<br>μV |

|                 | V <sub>OS</sub> Temperature<br>Coefficient | OV to 5V Range<br>OV to 10V Range                                                                                                                                                                                                                                                     | • |          | :2<br>:2             |                              |       | ±2<br>±2                     |                              |            | ±2<br>±2       |                                            | μV/°C<br>μV/°C       |

| BZE             | Bipolar Zero<br>Error                      | All Bipolar Ranges                                                                                                                                                                                                                                                                    | • | ±0       | .25                  | ±1<br>±2                     |       | ±0.5                         | ±2<br>±2.5                   |            | ±2             | ±8<br>±12                                  | LSB<br>LSB           |

| PSRR            | Power Supply<br>Rejection Ratio            | $V_{DD} = 5V \pm 10\%$ (Note 3)<br>$V_{DD} = 3V \pm 10\%$ (Note 3)<br>0V to 10V Range, Code = 0                                                                                                                                                                                       |   | ±0.      | 003<br>006           |                              | ±     | :0.013<br>:0.025             | 0.05                         |            | ±0.05<br>±0.1  |                                            | LSB/V<br>LSB/V       |

|                 |                                            | $V^+/V^- = \pm 15V \pm 10\%$ (Note 2)<br>$V^+/V^- = \pm 5V \pm 10\%$ , $V_{REF} = 2V$ (Note 2)                                                                                                                                                                                        | • |          |                      | ±0.06<br>±0.05               | 1     | :0.005<br>±0.01              | ±0.25<br>±0.13               |            | ±0.02<br>±0.04 |                                            | LSB/V<br>LSB/V       |

| Analog Oı       | utputs (Note 4)                            |                                                                                                                                                                                                                                                                                       |   |          |                      |                              |       |                              |                              |            |                |                                            |                      |

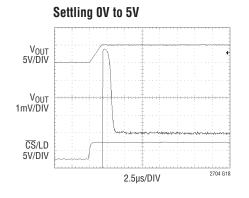

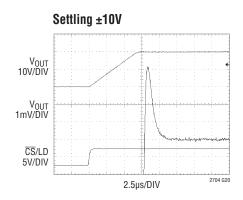

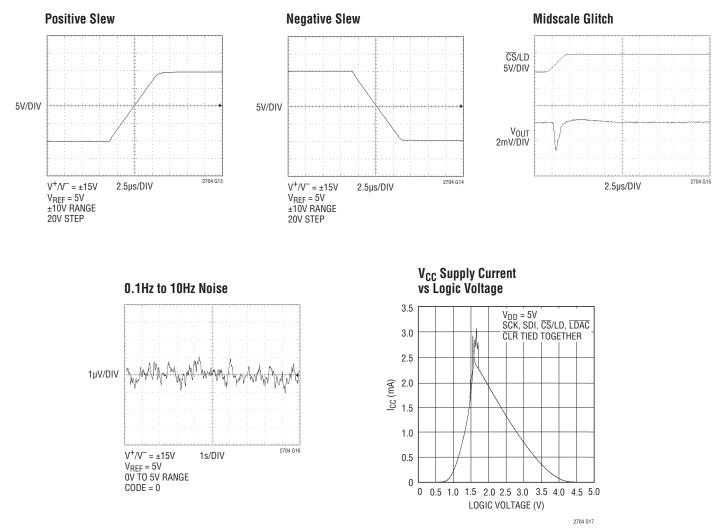

|                 | Settling Time                              | 0V to 5V Range, 5V Step, to ±1LSB<br>0V to 10V or ±5V Range,<br>10V Char to 11 CP                                                                                                                                                                                                     |   |          | 3                    |                              |       | 3.5                          |                              |            | 4              |                                            | μs                   |

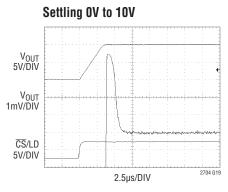

|                 |                                            | 10V Step, to ±1LSB<br>±10V Range, 20V Step, to ±1LSB                                                                                                                                                                                                                                  |   |          | 5<br>8               |                              |       | 5.5<br>9                     |                              |            | 6<br>10        |                                            | μs<br>μs             |

|                 | Output Swing                               | $V^+/V^- = \pm 15V$ , $V_{REF} = \pm 7.25V$ ,<br>OV to 10V Range, $I_{LOAD} = \pm 3mA$ (Note 2)                                                                                                                                                                                       | • | -14.3    |                      | 14.3                         | -14.3 |                              | 14.3                         | -14.3      |                | 14.3                                       | V                    |

|                 |                                            | $V^+/V^- = \pm 5V$ , $V_{REF} = \pm 2.25V$ ,<br>OV to 10V Range, $I_{LOAD} = \pm 2.5mA$ (Note 2)                                                                                                                                                                                      | • | -4.5     |                      | 4.5                          | -4.5  |                              | 4.5                          | -4.5       |                | 4.5                                        | V                    |

|                 | Load Current                               | $V^+/V^- = \pm 10.8V$ to $\pm 16.5V$ , $V_{REF} = \pm 5V$ ,<br>OV to 10V Range, $V_{OUT} = \pm 10V$ (Note 2)                                                                                                                                                                          | • |          |                      | ±5<br>±4                     |       |                              | ±5<br>±4                     |            |                | ±5<br>±4                                   | mA<br>mA             |

|                 |                                            | $V^+/V^- = \pm 4.5V$ to $\pm 16.5V$ , $V_{REF} = \pm 2V$ ,<br>OV to 10V Range, $V_{OUT} = \pm 4V$ (Note 2)                                                                                                                                                                            | • |          |                      | ±3<br>±2.7                   |       |                              | ±3<br>±2.7                   |            |                | ±3<br>±2.7                                 | mA<br>mA             |

|                 | Load Regulation                            | $V^+/V^- = \pm 15V$ , $V_{REF} = 5V$ ,<br>OV to 10V Range, Code = 0, $\pm 5$ mA Load<br>(Note 2)                                                                                                                                                                                      | • |          |                      | ±0.005                       |       |                              | ±0.01                        |            |                | ±0.04                                      | LSB/mA               |

|                 |                                            | $V^+/V^- = \pm 5V$ , $V_{REF} = 2V$ ,<br>OV to 10V Range, Code = 0, $\pm 3$ mA Load<br>(Note 2)                                                                                                                                                                                       | • |          |                      | ±0.01                        |       |                              | ±0.013                       |            |                | ±0.05                                      | LSB/mA               |

|                 | Output<br>Impedance                        | V <sub>REF</sub> = 5V, 0V to 10V Range,<br>Code = 0, ±5mA Load                                                                                                                                                                                                                        | • |          |                      | 0.015                        |       |                              | 0.006                        |            |                | 0.006                                      | Ω                    |

| I <sub>SC</sub> | Short-Circuit<br>Current                   | $\label{eq:V-V-} V^- = \pm 16.5 \text{V}, \ V_{\text{REF}} = 5 \text{V}, \ \pm 10 \text{V} \ \text{Range} \\ \text{Code} = 0, \ V_{\text{OUT}} \ \text{Shorted to V}^+ \ (\text{Note 2}) \\ \text{Code} = \text{Full Scale}, \ V_{\text{OUT}} \ \text{Shorted to V}^- \\ \end{array}$ | • | -36      |                      | 38                           | -36   |                              | 38                           | -36        |                | 38                                         | mA<br>mA             |

|                 |                                            | $\label{eq:V+V-} \begin{array}{l} V^+/V^- = \pm 5.5V, \ V_{REF} = 2V, \ \pm 10V \ Range \\ Code = 0, \ V_{OUT} \ Shorted \ to \ V^+ \ (Note \ 2) \\ Code = Full \ Scale, \ V_{OUT} \ Shorted \ to \ V^- \end{array}$                                                                  | • | -36      |                      | 38                           | -36   |                              | 38                           | -36        |                | 38                                         | mA<br>mA             |

|                 | 1                                          | 1                                                                                                                                                                                                                                                                                     | 1 |          |                      |                              | 1     |                              |                              | 1          |                |                                            | 270                  |

**ELECTRICAL CHARACTERISTICS** temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ ,  $V_1^+ = V_2^+ = 15V$ ,  $V_{-}^- = -15V$ ,  $V_{DD} = 5V$ , REF1 = REF2 = 5V, AGND = AGNDx = REFG1 = REFG2 = GND = 0V.

|        |                            |                             |   | LTC2704-12 |          |      | LTC2704-14 |          |     | LTC2704-16 |          |     |              |

|--------|----------------------------|-----------------------------|---|------------|----------|------|------------|----------|-----|------------|----------|-----|--------------|

| SYMBOL | PARAMETER                  | CONDITIONS                  |   | MIN        | ТҮР      | MAX  | MIN        | ТҮР      | MAX | MIN        | ТҮР      | MAX | UNITS        |

| SR     | Slew Rate                  |                             | • | 2.2<br>2.0 | 3<br>2.8 |      | 2.2<br>2.0 | 3<br>2.8 |     | 2.2<br>2.0 | 3<br>2.8 |     | V/µs<br>V/µs |

|        | Capacitive Load<br>Driving | Within Maximum Load Current |   | 1000       |          | 1000 |            | 1000     |     |            | pF       |     |              |

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ ,  $V_{1}^{+} = V_{2}^{+} = 15V$ ,  $V_{-}^{-} = -15V$ ,  $V_{DD} = 5V$ , REF1 = REF2 = 5V, AGND = AGNDx = REFG1 = REFG2 = GND = 0V.

| SYMBOL                                | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CONDITIONS                                                                                                                                                              |   | MIN                  | ТҮР          | MAX           | UNITS                                  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|--------------|---------------|----------------------------------------|

| Reference Input                       | is in the second s |                                                                                                                                                                         |   |                      |              |               |                                        |

|                                       | REF1, REF2 Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sup>+</sup> /V <sup>-</sup> = ±15V, 0V to 5V Span (Note 2)                                                                                                           |   | -14.5                |              | 14.5          | V                                      |

| Resistances                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                         |   |                      |              |               |                                        |

| R <sub>REF1</sub> , R <sub>REF2</sub> | Reference Input Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                         |   | 5                    | 7            |               | kΩ                                     |

| R <sub>FBx</sub>                      | Output Feedback Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                         | ٠ | 7                    | 10           |               | kΩ                                     |

| R <sub>VOSX</sub>                     | Offset Adjust Input Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                         |   | 700                  | 1000         |               | kΩ                                     |

| AC Performance                        | e (Note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                         |   |                      |              |               |                                        |

|                                       | Glitch Impulse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0V to 5V Range, Midscale Transition                                                                                                                                     |   |                      | 2            |               | nV-s                                   |

|                                       | Crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10V Step on V <sub>OUTA</sub><br>DAC B: 0V to 5V Range, Full Scale<br>DAC B: 0V to 10V Range, Full Scale                                                                |   |                      | 2<br>3       |               | nV-s<br>nV-s                           |

|                                       | Digital Feedthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ±10V Range, Midscale                                                                                                                                                    |   |                      | 0.2          |               | nV-s                                   |

|                                       | Multiplying Feedthrough Error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0V to 10V Range, V <sub>REF</sub> = ±5V, 10kHz Sine Wave                                                                                                                |   |                      | 0.35         |               | mV <sub>P-P</sub>                      |

|                                       | Multiplying Bandwidth                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Span = 0V to 5V, Full Scale<br>Span = 0V to 10V, Full Scale                                                                                                             |   |                      | 300<br>250   |               | kHz<br>kHz                             |

|                                       | Output Noise Voltage Density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10kHz<br>Span = 0V to 5V, Midscale<br>Span = 0V to 10V, Midscale                                                                                                        |   |                      | 30<br>50     |               | nV/√Hz<br>nV/√Hz                       |

|                                       | Output Noise Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0.1Hz to 10Hz<br>Span = 0V to 5V, Midscale<br>Span = 0V to 10V, Midscale                                                                                                |   |                      | 0.8<br>1.2   |               | μV <sub>RMS</sub><br>μV <sub>RMS</sub> |

| Power Supply                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                         |   |                      |              |               |                                        |

| I <sub>DD</sub>                       | Supply Current, V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Digital Inputs = 0V or V <sub>DD</sub>                                                                                                                                  |   |                      | 0.5          | 2             | μA                                     |

| I <sub>S</sub>                        | Supply Current, V <sup>+</sup> /V <sup>-</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $V^+/V^- = \pm 15V, \pm 10\%; V_{REF} = 5V, V_{OUT} = 0V (Note 2)$<br>$V^+/V^- = \pm 5V, \pm 10\%; V_{REF} = 2V, V_{OUT} = 0V (Note 2)$<br>Sleep Mode—All DACs (Note 4) | • |                      | 17.5<br>17.0 | 20<br>18<br>1 | mA<br>mA<br>mA                         |

| V <sub>DD</sub>                       | Logic Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                         | • | 2.7                  |              | 5.5           | V                                      |

| V+1/V+2                               | Positive Analog Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                         | • | 4.5                  |              | 16.5          | V                                      |

| V-                                    | Negative Analog Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                         |   | -16.5                |              | -4.5          | V                                      |

| Digital Inputs/O                      | utputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                         |   |                      |              |               |                                        |

| V <sub>IH</sub>                       | Digital Input High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>DD</sub> = 2.7V to 5.5V<br>V <sub>DD</sub> = 2.7V to 3.3V                                                                                                        | • | 2.4<br>2.0           |              |               | V<br>V                                 |

| V <sub>IL</sub>                       | Digital Input Low Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>DD</sub> = 2.7V to 5.5V<br>V <sub>DD</sub> = 4.5V to 5.5V                                                                                                        | • |                      |              | 0.6<br>0.8    | V<br>V                                 |

| V <sub>OH</sub>                       | Digital Output High Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I <sub>0H</sub> = 200μA                                                                                                                                                 | • | V <sub>CC</sub> -0.4 |              |               | V                                      |

| V <sub>OL</sub>                       | Digital Output Low Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I <sub>0L</sub> = 200μA                                                                                                                                                 | • |                      |              | 0.4           | V                                      |

| I <sub>IN</sub>                       | Digital Input Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                         |   |                      | 0.001        | ±1            | μA                                     |

**ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are  $T_A = 25^{\circ}C$ ,  $V_1^+ = V_2^+ = 15V$ ,  $V_{-} = -15V$ ,  $V_{DD} = 5V$ , REF1 = REF2 = 5V, AGND = AGNDx = REFG1 = REFG2 = GND = 0V.

| SYMBOL          | PARAMETER                 | CONDITIONS                    |  | MIN | ТҮР | MAX | UNITS |

|-----------------|---------------------------|-------------------------------|--|-----|-----|-----|-------|

| C <sub>IN</sub> | Digital Input Capacitance | V <sub>IN</sub> = 0V (Note 3) |  |     |     | 5   | pF    |

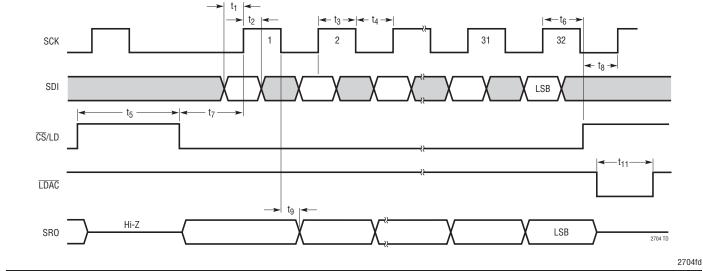

## TIMING CHARACTERISTICS

The • denotes specifications which apply over the full operating temperature

range, otherwise specifications are at  $T_A = 25^{\circ}C$ .

| SYMBOL                           | PARAMETER                       | CONDITIONS                        |   | MIN | ТҮР | MAX | UNITS |

|----------------------------------|---------------------------------|-----------------------------------|---|-----|-----|-----|-------|

| $V_{DD} = 4.5V$ to $\frac{1}{2}$ | 5.5V                            |                                   |   |     |     |     |       |

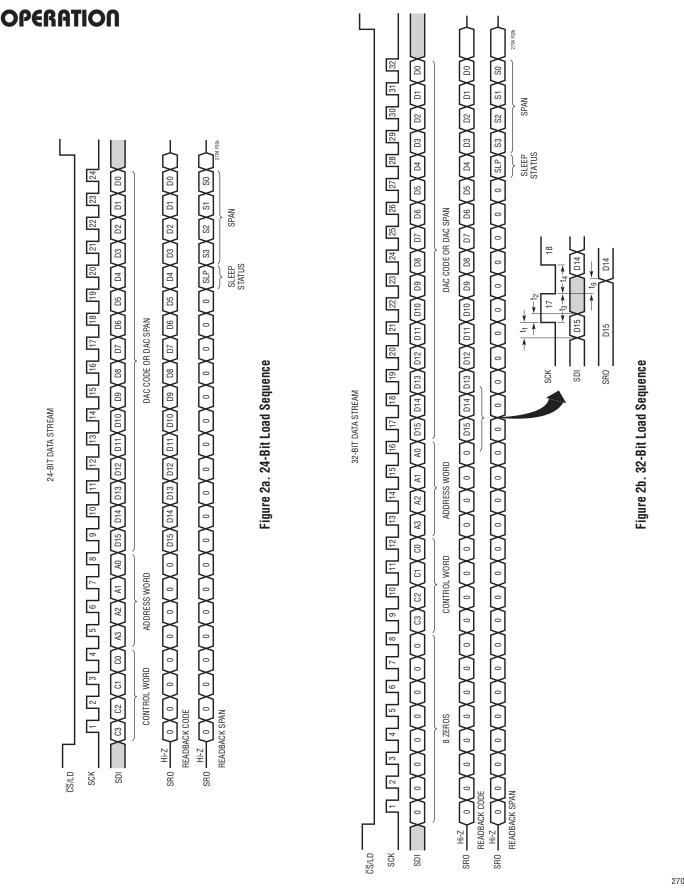

| t <sub>1</sub>                   | SDI Valid to SCK Setup          |                                   |   | 7   |     |     | ns    |

| t <sub>2</sub>                   | SDI Valid to SCK Hold           |                                   | ٠ | 7   |     |     | ns    |

| t <sub>3</sub>                   | SCK High Time                   |                                   | ٠ | 11  |     |     | ns    |

| t <sub>4</sub>                   | SCK Low Time                    |                                   | ٠ | 11  |     |     | ns    |

| t <sub>5</sub>                   | CS/LD Pulse Width               |                                   | • | 9   |     |     | ns    |

| t <sub>6</sub>                   | LSB SCK High to CS/LD High      |                                   |   | 0   |     |     | ns    |

| t <sub>7</sub>                   | CS/LD Low to SCK Positive Edge  |                                   | ٠ | 12  |     |     | ns    |

| t <sub>8</sub>                   | CS/LD High to SCK Positive Edge |                                   | ٠ | 12  |     |     | ns    |

| tg                               | SRO Propagation Delay           | C <sub>LOAD</sub> = 10pF          | ٠ |     |     | 18  | ns    |

| t <sub>10</sub>                  | CLR Pulse Width                 |                                   | ٠ | 50  |     |     | ns    |

| t <sub>11</sub>                  | LDAC Pulse Width                |                                   |   | 15  |     |     | ns    |

| t <sub>12</sub>                  | CLR Low to RFLAG Low            | C <sub>LOAD</sub> = 10pF (Note 3) | • |     |     | 50  | ns    |

| t <sub>13</sub>                  | CS/LD High to RFLAG High        | C <sub>LOAD</sub> = 10pF (Note 3) | ٠ |     |     | 40  | ns    |

|                                  | SCK Frequency                   | 50% Duty Cycle (Note 5)           | • |     |     | 40  | MHz   |

| $V_{DD} = 2.7V$ to 3             | 3.3V                            | •                                 |   |     |     |     |       |

| t <sub>1</sub>                   | SDI Valid to SCK Setup          |                                   |   | 9   |     |     | ns    |

| t <sub>2</sub>                   | SDI Valid to SCK Hold           |                                   | ٠ | 9   |     |     | ns    |

| t <sub>3</sub>                   | SCK High Time                   |                                   | • | 15  |     |     | ns    |

| t4                               | SCK Low Time                    |                                   | • | 15  |     |     | ns    |

| t <sub>5</sub>                   | CS/LD Pulse Width               |                                   | ٠ | 12  |     |     | ns    |

| t <sub>6</sub>                   | LSB SCK High to CS/LD High      |                                   | • | 0   |     |     | ns    |

| t <sub>7</sub>                   | CS/LD Low to SCK Positive Edge  |                                   |   | 12  |     |     | ns    |

| t <sub>8</sub>                   | CS/LD High to SCK Positive Edge |                                   |   | 12  |     |     | ns    |

| tg                               | SRO Propagation Delay           | C <sub>LOAD</sub> = 10pF          | • |     |     | 26  | ns    |

| t <sub>10</sub>                  | CLR Pulse Width                 |                                   | • | 90  |     |     | ns    |

| t <sub>11</sub>                  | LDAC Pulse Width                |                                   | ٠ | 20  |     |     | ns    |

| t <sub>12</sub>                  | CLR Low to RFLAG Low            | C <sub>LOAD</sub> = 10pF          | • |     |     | 70  | ns    |

| t <sub>13</sub>                  | CS/LD High to RFLAG High        | C <sub>LOAD</sub> = 10pF          | • |     |     | 60  | ns    |

|                                  | SCK Frequency                   | 50% Duty Cycle (Note 5)           | • |     |     | 25  | MHz   |

|                                  |                                 | •                                 |   |     |     |     |       |

Note 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The notation  $V^+$  is used to denote both  $V^+_1$  and  $V^+_2$  when the same

Note 4: Measured in unipolar OV to 5V mode.

Note 5: When using SRO, maximum SCK frequency f<sub>MAX</sub> is limited by SRO propagation delay as follows:

$$f_{MAX} = \left(\frac{1}{2(t_9 + t_S)}\right)$$

, where  $t_s$  is the setup time of the receiving device.

voltage is applied to both pins.

Note 3: Guaranteed by design, not subject to test.

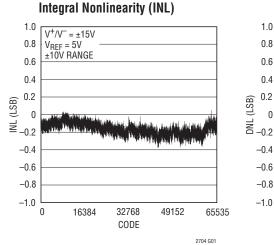

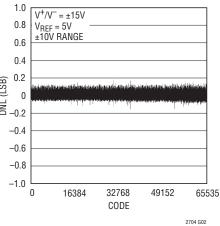

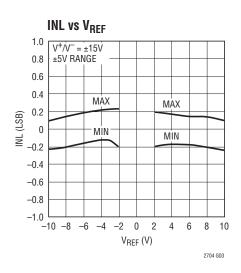

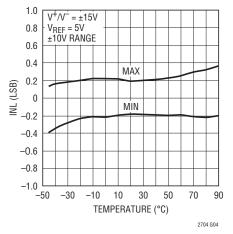

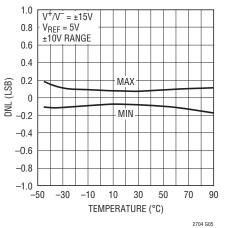

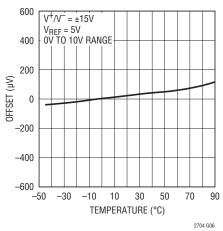

# **TYPICAL PERFORMANCE CHARACTERISTICS**

#### LTC2704-16

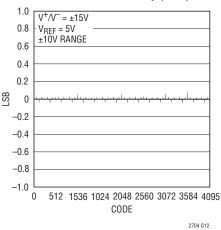

**Differential Nonlinearity (DNL)**

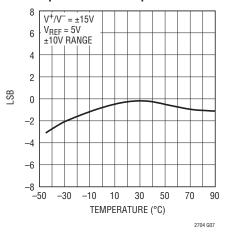

#### INL vs Temperature

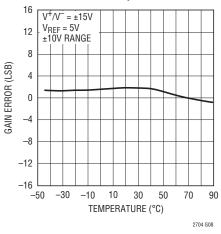

**DNL vs Temperature**

**Offset vs Temperature**

Bipolar Zero vs Temperature

**Gain Error vs Temperature**

## **TYPICAL PERFORMANCE CHARACTERISTICS**

#### LTC2704-16

LTC2704-14

#### LTC2704-12

Integral Nonlinearity (INL)

#### **Differential Nonlinearity (DNL)**

#### **Differential Nonlinearity (DNL)**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

### LTC2704-16/LTC2704-14/LTC2704-12

## PIN FUNCTIONS

**V<sup>-</sup> (Pins 1, 8, 15, 22, 31, 36):** Analog Negative Supply, Typically –15V. –4.5V to –16.5V Range.

**REFG1 (Pin 2):** Reference 1 Ground. High impedance input, does not carry supply currents. Tie to clean analog ground.

**AGNDA (Pin 3):** DAC A Signal Ground. High impedance input, does not carry supply currents. Tie to clean analog ground.

**VOSA (Pin 4):** Offset Adjust for DAC A. Nominal input range is  $\pm 5V$ . V<sub>OS</sub>(DAC A) = -0.01• V(VOSA) [OV to 5V,  $\pm 2.5V$  modes]. See Operation section.

**C1A (Pin 5):** Feedback Capacitor Connection for DAC A Output. This pin provides direct access to the negative input of the channel A output amplifier.

**OUTA (Pin 6):** DAC A Voltage Output Pin. For best load regulation, this open-loop amplifier output is connected to RFBA as close to the load as possible.

RFBA (Pin 7): DAC A Output Feedback Resistor Pin.

**LDAC** (Pin 9): Asynchronous DAC Load Input. When LDAC is a logic low, all DACs are updated.

## PIN FUNCTIONS

**CS/LD (Pin 10):** Synchronous Chip Select and Load Pin.

**SDI (Pin 11):** Serial Data Input. Data is clocked in on the rising edge of the serial clock when  $\overline{CS}/LD$  is low.

**SRO (Pin 12):** Serial Readback Data Output. Data is clocked out on the falling edge of SCK. Readback data begins clocking out after the last address bit A0 is clocked in.

SCK (Pin 13): Serial Clock.

**CLR** (Pin 14): Asynchronous Clear Pin. When this pin is low, all code and span B2 registers are cleared to zero. All DAC outputs are cleared to zero volts.

**RFBD (Pin 16):** DAC D Voltage Output Feedback Resistor Pin.

**OUTD (Pin 17):** DAC D Voltage Output Pin. For best load regulation, this open-loop amplifier output is connected to RFBD as close to the load as possible.

**C1D (Pin 18):** Feedback Capacitor Connection for DAC D Output. This pin provides direct access to the negative input of the channel D output amplifier.

**VOSD (Pin 19):** Offset Adjust for DAC D. Nominal input range is  $\pm 5V$ . V<sub>OS</sub>(DAC D) =  $-0.01 \cdot V(VOSD)$  [OV to 5V,  $\pm 2.5V$  modes]. See Operation section.

**AGNDD (Pin 20):** DAC D Signal Ground. High impedance input, does not carry supply currents. Tie to clean analog ground.

**REFG2 (Pin 21):** Reference 2 Ground. High impedance input, does not carry supply currents. Tie to clean analog ground.

**REFM2 (Pin 23):** Reference 2 Inverting Amp Output. The gain from REF2 to REFM2 is -1. Can swing to within 0.5V of the analog supplies V<sup>+</sup>/V<sup>-</sup>.

REF2 (Pin 24): DAC C and DAC D Reference Input.

$V^+{}_2$  (Pin 25): Analog Positive Supply for DACs C and D. Typically 15V. 4.5V to 16.5V Range. Can be different from  $V^+{}_1.$

**AGNDC (Pin 26):** DAC C Signal Ground. High impedance input, does not carry supply currents. Tie to clean analog ground.

**VOSC (Pin 27):** Offset Adjust for DAC C. Nominal input range is  $\pm 5V$ . V<sub>OS</sub>(DAC C) = -0.01• V(VOSC) [OV to 5V,  $\pm 2.5V$  modes]. See Operation section.

**C1C (Pin 28):** Feedback Capacitor Connection for DAC C Output. This pin provides direct access to the negative input of the channel C output amplifier.

**OUTC (Pin 29):** DAC C Voltage Output Pin. For best load regulation, this open-loop amplifier output is connected to RFBC as close to the load as possible.

RFBC (Pin 30): DAC C Output Feedback Resistor Pin.

**AGND (Pin 32):** Analog Ground Pin. Tie to clean analog ground.

**GND (Pin 33):** Ground Pin. Tie to clean analog ground.

V<sub>DD</sub> (Pin 34): Logic Supply. 2.7V to 5.5V Range.

**RFLAG** (Pin 35): Reset Flag Pin. An active low output is asserted when there is a power on reset or a clear event. Returns high when an update command is executed.

RFBB (Pin 37): DAC B Output Feedback Resistor Pin.

**OUTB (Pin 38):** DAC B Voltage Output Pin. For best load regulation, this open-loop amplifier output is connected to RFBB as close to the load as possible.

**C1B (Pin 39):** Feedback Capacitor Connection for DAC B Output. This pin provides direct access to the negative input of the channel B output amplifier.

**VOSB (Pin 40):** Offset Adjust for DAC B. Nominal input range is  $\pm 5V$ . V<sub>OS</sub>(DAC B) =  $-0.01 \cdot V(VOSB)$  [OV to 5V,  $\pm 2.5V$  modes]. See Operation section.

**AGNDB (Pin 41):** DAC B Signal Ground. High impedance input, does not carry supply currents. Tie to clean analog ground.

$V_1^+$  (Pin 42): Analog Positive Supply for DACs A DND B. Typically 15V. 4.5V to 16.5V Range. Can be different from V<sub>2</sub><sup>+</sup>.

REF1 (Pin 43): DAC A and DAC B Reference Input.

**REFM1 (Pin 44):** Reference 1 Inverting Amp Output. The gain from REF1 to REFM1 is -1. Can swing to within 0.5V of the analog supplies V<sup>+</sup>/V<sup>-</sup>.

## TIMING DIAGRAM

# OPERATION

## SERIAL INTERFACE

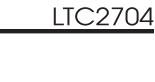

When the  $\overline{\text{CS}}/\text{LD}$  pin is taken low, the data on the SDI pin is loaded into the shift register on the rising edge of the clock signal (SCK pin). The minimum (24-bit wide) loading sequence required for the LTC2704 is a 4-bit command word (C3 C2 C1 C0), followed by a 4-bit address word (A3 A2 A1 A0) and 16 data (span or code) bits, MSB first. Figure 1 shows the SDI input word syntax to use when writing a code or span. If a 32-bit input sequence is needed, the first eight bits must be zeros, followed by the same sequence as for a 24-bit wide input. Figure 2 shows the input and readback sequences for both 24-bit and 32-bit operations.

When  $\overline{\text{CS}}/\text{LD}$  is low, the Serial Readback Output (SRO) pin is an active output. The readback data begins after the command (C3-C0) and address (A3-A0) words have been shifted into SDI. For a 24-bit load sequence, the 16 readback bits are shifted out on the falling edges of clocks 8-23, suitable for shifting into a microprocessor on the rising edges of clocks 9-24. For a 32-bit load sequence, add 8 to these clock cycle counts; see Figure 2b.

When  $\overline{CS}/LD$  is high, the SRO pin presents a high impedance (three-state) output. At the beginning of a load sequence, when  $\overline{CS}/LD$  is taken low, SRO outputs a logic low until the readback data begins.

When the asynchronous load pin,  $\overline{\text{LDAC}}$ , is taken low, all DACs are updated with code and span data (data in B1 buffers is copied into B2 buffers).  $\overline{\text{CS}/\text{LD}}$  must be high during this operation. The use of  $\overline{\text{LDAC}}$  is functionally identical to the "Update B1->B2" commands.

The codes for the command word (C3-C0) are defined in Table 1; Table 2 defines the codes for the address word (A3-A0).

## READBACK

Each DAC has two pairs of double-buffered digital registers, one pair for DAC code and the other for the output span (four buffers per DAC). Each double-buffered pair comprises two registers called buffer 1 (B1) and buffer 2 (B2). B1 is the holding buffer. When data is shifted into B1 via a write operation, DAC outputs are not affected. The contents of B2 can only be changed by copying the contents of B1 into B2 via an update operation (B1 and B2 can be changed together, see commands 0110-1001 in Table 1). The contents of B2 (DAC code or DAC span) directly control the DAC output voltage or the DAC output range.

Additionally each DAC has one readback register associated with it. When a readback command is issued to a DAC, the contents of one of its four buffers is copied into its readback register and serially shifted out onto the SRO pin. Figure 2 shows the loading and readback sequences. In the 16-bit data field (D15-D0 for the LTC2704-16, see Figure 2a) of any write or update command, the readback pin (SRO) shifts out the contents of the buffer which was specified in the preceding command. This "rolling readback" mode of operation can be used to reduce the number of operations, since any command can be verified during succeeding commands with no additional overhead. Table 1 shows the location (readback pointer) of the data which will be output from SRO during the next instruction.

For readback commands, the data is shifted out during the readback instruction itself (on the 16 falling SCK edges immediately after the last address bit is shifted in on SDI).

When programming the span of a DAC, the span bits are the last four bits shifted in; and when checking the span of a DAC using SRO, the span bits are likewise the last four bits shifted out. Table 3 shows the span codes.

When span information is read back on SRO, the sleep status of the addressed DAC is also output. The sleep status bit, SLP, occurs sequentially just before the four span bits. The sequence is shown in Figures 2a and 2b. See Table 4 for SLP codes. Note that SLP is an output bit only; sleep is programmed by using command code 1110 along with the desired address. Any update command, including the use of LDAC, wakes the addressed DAC(s).

# OPERATION

## **OUTPUT RANGES**

The LTC2704 is a quad DAC with software-programmable output ranges. SoftSpan provides two unipolar output ranges (0V to 5V and 0V to 10V), and four bipolar ranges ( $\pm 2.5V$ ,  $\pm 5V$ ,  $\pm 10V$  and -2.5V to 7.5V). These ranges are obtained when an external precision 5V reference and analog supplies of  $\pm 12V$  to  $\pm 15V$  are used. When a reference voltage of 2V and analog supplies of  $\pm 5V$  are used,

the SoftSpan ranges become: 0V to 2V, 0V to 4V,  $\pm$ 1V,  $\pm$ 2V,  $\pm$ 4V and -1V to 3V. The output ranges are linearly scaled for references other than 2V and 5V (appropriate analog supplies should be used within the range  $\pm$ 5V to  $\pm$ 15V). Each of the four DACs can be programmed to any one of the six output ranges. DAC outputs can swing to  $\pm$ 10V on  $\pm$ 10.8V supplies ( $\pm$ 12V supplies with  $\pm$ 10% tolerance) while sourcing or sinking 5mA of load current.

| Table | 1. | Command | Co | des |  |

|-------|----|---------|----|-----|--|

| -     |    |         |    |     |  |

| CODE |    |    |    |                                                 | READBACK POINTER—                 | READBACK POINTER—               |

|------|----|----|----|-------------------------------------------------|-----------------------------------|---------------------------------|

| C3   | C2 | C1 | CO | COMMAND                                         | CURRENT INPUT WORD W <sub>0</sub> | NEXT INPUT WORD W <sub>+1</sub> |

| 0    | 0  | 1  | 0  | Write to B1 Span DAC n                          | Set by Previous Command           | B1 Span DAC n                   |

| 0    | 0  | 1  | 1  | Write to B1 Code DAC n                          | Set by Previous Command           | B1 Code DAC n                   |

| 0    | 1  | 0  | 0  | Update B1→B2 DAC n                              | Set by Previous Command           | B2 Span DAC n                   |

| 0    | 1  | 0  | 1  | Update B1→B2 All DACs                           | Set by Previous Command           | B2 Code DAC n                   |

| 0    | 1  | 1  | 0  | Write to B1 Span DAC n<br>Update B1→B2 DAC n    | Set by Previous Command           | B2 Span DAC n                   |

| 0    | 1  | 1  | 1  | Write to B1 Code DAC n<br>Update B1→B2 DAC n    | Set by Previous Command           | B2 Code DAC n                   |

| 1    | 0  | 0  | 0  | Write to B1 Span DAC n<br>Update B1→B2 All DACs | Set by Previous Command           | B2 Span DAC n                   |

| 1    | 0  | 0  | 1  | Write to B1 Code DAC n<br>Update B1→B2 All DACs | Set by Previous Command           | B2 Code DAC n                   |

| 1    | 0  | 1  | 0  | Read B1 Span DAC n                              | B1 Span                           | DAC n                           |

| 1    | 0  | 1  | 1  | Read B1 Code DAC n                              | B1 Code                           | DAC n                           |

| 1    | 1  | 0  | 0  | Read B2 Span DAC n                              | B2 Span                           | DAC n                           |

| 1    | 1  | 0  | 1  | Read B2 Code DAC n                              | B2 Code                           | DAC n                           |

| 1    | 1  | 1  | 0  | Sleep DAC n (Note 1)                            | Set by Previous Command           | B2 Span DAC n                   |

| 1    | 1  | 1  | 1  | No Operation                                    | Set by Previous Command           | B2 Code DAC n                   |

Codes not shown are reserved and should not be used.

Note 1: Normal operation can be resumed by issuing any update  $B1 \rightarrow B2$  command to the sleeping DAC.

#### Table 2. Address Codes

| A3 | A2 | A1 | A0 | n        | <b>READBACK POINTER n</b> |

|----|----|----|----|----------|---------------------------|

| 0  | 0  | 0  | 0  | DAC A    | DAC A                     |

| 0  | 0  | 1  | 0  | DAC B    | DAC B                     |

| 0  | 1  | 0  | 0  | DAC C    | DAC C                     |

| 0  | 1  | 1  | 0  | DAC D    | DAC D                     |

| 1  | 1  | 1  | 1  | All DACs | DAC A                     |

|    |    |    |    |          |                           |

Codes not shown are reserved and should not be used.

#### Table 3. Span Codes

| Table      | 0. OP |    | ucs |                       |

|------------|-------|----|-----|-----------------------|

| <b>S</b> 3 | S2    | S1 | SO  | SPAN                  |

| 0          | 0     | 0  | 0   | Unipolar 0V to 5V     |

| 0          | 0     | 0  | 1   | Unipolar 0V to 10V    |

| 0          | 0     | 1  | 0   | Bipolar –5V to 5V     |

| 0          | 0     | 1  | 1   | Bipolar –10V to 10V   |

| 0          | 1     | 0  | 0   | Bipolar –2.5V to 2.5V |

| 0          | 1     | 0  | 1   | Bipolar –2.5V to 7.5V |

Codes not shown are reserved and should not be used.

2704 F01

SPAN

SO

s3 X s2 X s1 )

0

0

0

0

0

0 X 0 X 0

CO X A3 X A2 X A1 X A0 )

C3 🗙 C2 🗙 C1 )

LTC2704-12 LTC2704-14 LTC2704-16 (WRITE SPAN)

ADDRESS WORD

CONTROL WORD

12 ZEROS

D LSB

PI

X C3 X C2 X C1 X C0 X A3 X A2 X A1 X A0 X D15 X D14 X D13 X D12 X D11 X D10 X D9 X D8 X D7 X D6 X D5 X D4 X D3 X D2 X

0

0

00

5

C0 A3 A2 A1 A0 X013 X012 X011 X010 X 09 X 08 X 07 X 06 X 05 X 04 X 03 X 02 X

SB

16-BIT CODE

ADDRESS WORD

CONTROL WORD

LTC2704-16 (WRITE CODE) 2 ZEROS

14-BIT CODE

0

0

0

DO LSB

Б

D2 )

D6 X D5 X D4 X D3

D8

A0 X D11 X D10 X D9 X

A2 A1

C0 X A3 X

c3 ( c2 ( c1 )

LTC2704-12 (WRITE CODE)

MSB

ADDRESS WORD

CONTROL WORD

SDI {

C3 X C2 X C1

LTC2704-14 (WRITE CODE) 12-BIT CODE

ADDRESS WORD

CONTROL WORD

4 ZEROS

# LTC2704

# OPERATION

## Examples

- 1. Using a 24-bit loading sequence, load DAC A with the unipolar range of 0V to 10V, output at zero volts and all other DACs with the bipolar range of  $\pm$ 10V, outputs at zero volts. Note all DAC outputs should change at the same time.

- a) <u>CS</u>/LD↓

- b) Clock SDI = 0010 1111 0000 0000 0000 0011

- c) CS/LD↑

B1-Range of all DACs set to bipolar  $\pm 10V$ .

d) <del>CS</del>/LD↓

Clock SDI = 0010 0000 0000 0000 0000 0001

e) <u>CS</u>/LD↑

B1-Range of DAC A set to unipolar OV to 10V.

- f) CS/LD↓ Clock SDI = 0011 1111 1000 0000 0000 0000

- g) <u>CS</u>/LD↑

B1-Code of all DACs set to midscale.

h) <del>CS</del>/LD↓

Clock SDI = 0011 0000 0000 0000 0000 0000

i) CS/LD↑ B1-Code of I

B1-Code of DAC A set to zero code. i)  $\overline{CS}/LD\downarrow$

Clock SDI = 0100 1111 XXXX XXXX XXXX XXXX XXXX  $\overrightarrow{K}$

Update all DACs B1s into B2s for both Code and Range.

I) Alternatively steps j and k could be replaced with  $\overrightarrow{\text{LDAC}}$   $\neg \Box$  .

Using a 32-bit load sequence, load DAC C with bipolar ±2.5V and its output at zero volts. Use readback to check B1 contents before updating the DAC output (i.e., before copying B1 contents into B2).

- a)  $\overline{\text{CS}}/\text{LD}\downarrow$  (Note that after power-on, the Code in B1 is zero)

- b) Clock SDI = 0000 0000 0011 0100 1000 0000 0000 0000

- c)  $\overline{\text{CS}}/\text{LD}\uparrow$

B1-Code of DAC C set to midscale setting.

- d) <u>CS</u>/LD↓

- e) Read Data out on SRO = 1000 0000 0000 0000 Verifies that B1-Code DAC C is at midscale setting.

- f) <u>CS</u>/LD↑

B1-Range of DAC C set to Bipolar ±2.5V range.

g) <del>CS</del>/LD↓

Data Out on SRO = 0000 0000 0000 0100 Verifies that B1-Range of DAC C set to Bipolar ±2.5V Range.

- <u>CS</u>/LD↑

- h) CS/LD↓ Clock SDI = 0000 0000 0100 0100 xxxx xxxx xxxx xxxx

- i) <u>CS</u>/LD↑

Update DAC C B1 into B2 for both Code and Range

j) Alternatively steps h and i could be replaced with  $\overrightarrow{\text{LDAC}} \, \square \overline{}$  .

## System Offset Adjustment

Many systems require compensation for overall system offset, which may be an order of magnitude or more greater than the excellent offset of the LTC2704.

The LTC2704 has individual offset adjust pins for each of the four DACs. VOSA, VOSB, VOSC and VOSD are referred to their corresponding signal grounds, AGNDA, AGNDB, AGNDC and AGNDD. For noise immunity and ease of adjustment, the control voltage is attenuated to the DAC output:

$V_{OS} = -0.01 \bullet V(VOSx)$  [OV to 5V, ±2.5V spans]

$V_{OS}$  = -0.02  $\bullet$  V(VOSx) [0V to 10V, ±5V, -2.5V to 7.5V spans]

$V_{OS} = -0.04 \bullet V(VOSx) [\pm 10V span]$

The nominal input range of these pins is  $\pm 5V$ ; other reference voltages of up to  $\pm 15V$  may be used if needed.

The VOSx pins have an input impedance of  $1M\Omega.$  To preserve the settling performance of the LTC2704, these pins

# OPERATION

should be driven with a Thevenin-equivalent impedance of  $10k\Omega$  or less. If not used, they should be shorted to their respective signal grounds, AGNDx.

## **POWER-ON RESET AND CLEAR**

When power is first applied to the LTC2704, all DACs power-up in 5V unipolar mode (S3 S2 S1 S0 = 0000). All internal DAC registers are reset to 0 and the DAC outputs are zero volts.

When the  $\overline{\text{CLR}}$  pin is taken low, a system clear results. The command and address shift registers, and the code and configuration B2 buffers, are reset to 0; the DAC outputs are all reset to zero volts. The B1 buffers are left intact, so that any subsequent "Update B1 $\rightarrow$ B2" command (including the use of  $\overline{\text{LDAC}}$ ) restores the addressed DACs to their respective previous states.

If  $\overline{\text{CLR}}$  is asserted during an operation, i.e., when  $\overline{\text{CS}}/\text{LD}$  is low, the operation is aborted. Integrity of the relevant input (B1) buffers is not guaranteed under these conditions, therefore the contents should be checked using readback or replaced.

The  $\overline{\text{RFLAG}}$  pin is used as a flag to notify the system of a loss of data integrity. The  $\overline{\text{RFLAG}}$  output is asserted low at power-up, system clear, or if the logic supply V<sub>DD</sub> dips

below approximately 2V; and stays asserted until any valid update command is executed.

## **SLEEP MODE**

When a sleep command (C3 C2 C1 C0 = 1110) is issued, the addressed DAC or DACs go into power-down mode. DACs A and B share a reference inverting amplifier as do DACs C and D. If either DAC A or DAC B (similarly for DACs C and D) is powered down, its shared reference inverting amplifier remains powered on. When both DAC A and DAC B are powered down together, their shared reference inverting amplifier is also powered down (similarly for DACs C and D). To determine the sleep status of a particular DAC, a direct read span command is performed by addressing the DAC and reading its status on the readback pin SRO. The fifth LSB is the sleep status bit (see Figures 2a and 2b). Table 4 shows the sleep status bit's functionality.

Table 4. Readback Sleep Status Bit

| SLP | STATUS              |

|-----|---------------------|

| 0   | DAC n Awake         |

| 1   | DAC n in Sleep Mode |

# **APPLICATIONS INFORMATION**

## Overview

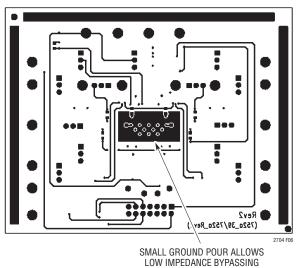

The LTC2704 is a highly integrated device, greatly simplifying design and layout as compared to a design using multiple current output DACs and separate amplifiers. A similar design using four separate current output DACs would require six precision op amps, compensation capacitors, bypass capacitors for each amplifier, several times as much PCB area and a more complicated serial interface. Still, it is important to avoid some common mistakes in order to achieve full performance. DC752A is the evaluation board for the LTC2704. It is designed to meet all data sheet specifications, and to allow the LTC2704 to be integrated into other prototype circuitry. All force/sense lines are available to allow the addition of current booster stages or other output circuits.

The DC752A design is presented as a tutorial on properly applying the LTC2704. This board shows how to properly return digital and analog ground currents, and how to compensate for small differences in ground potential between the two banks of two DACs. There are other ways to ground the LTC2704, but the one requirement is that analog and digital grounds be connected at the LTC2704 by a very low impedance path. It is NOT advisable to split the ground planes and connect them with a jumper or inductor. When in doubt, use a single solid ground plane rather than separate planes.