## Intel<sup>®</sup> Stratix<sup>®</sup> 10 TX Transceiver Signal Integrity Development Kit User Guide

ID: 683591 Version: 2019.09.27

UG-20150

## Contents

| 1. Overview                                                            | 4    |

|------------------------------------------------------------------------|------|

| 1.1. General Development Kit Description                               | 4    |

| 1.2. Recommended Operating Conditions                                  |      |

| 1.3. Handling the Kit.                                                 |      |

| 2. Getting Started                                                     | 7    |

| -                                                                      |      |

| 2.1. About the Intel Quartus <sup>®</sup> Prime Software               |      |

| 2.2. Development Kit Package                                           |      |

| 2.3. Installing the Intel FPGA Download Cable II Driver                |      |

| 3. Development Kit Setup                                               |      |

| 3.1. Setting up the Development Kit                                    | 9    |

| 3.2. Factory Default Switch and Jumper Settings                        | . 10 |

| 4. Development Kit Components                                          | . 12 |

| 4.1. Development Kit Overview                                          |      |

| 4.2. Intel Stratix 10 TX FPGA                                          |      |

| 4.3. MAX V CPLD                                                        |      |

| 4.4. FPGA Configuration                                                |      |

| 4.4.1. Configuring the FPGA over Embedded Intel FPGA Download Cable II |      |

| 4.4.2. Configuring the FPGA through Flash Memory                       |      |

| 4.4.3. Configuring the FPGA over External Intel FPGA Download Cable    |      |

| 4.5. Status and Setup Elements                                         |      |

| 4.6. User Input-Output Components                                      | . 27 |

| 4.7. Clocks                                                            | . 28 |

| 4.7.1. Transceiver Dedicated Clocks                                    | 28   |

| 4.7.2. General-Purpose Clocks                                          | . 29 |

| 4.7.3. Embedded Intel FPGA Download Cable II Clock                     |      |

| 4.8. Transceiver Channels                                              |      |

| 4.9. Communication Ports                                               |      |

| 4.10. Flash Memory                                                     |      |

| 4.10.1. Parallel NOR Flash Memory                                      |      |

| 4.10.2. EPCQL Flash Memory                                             |      |

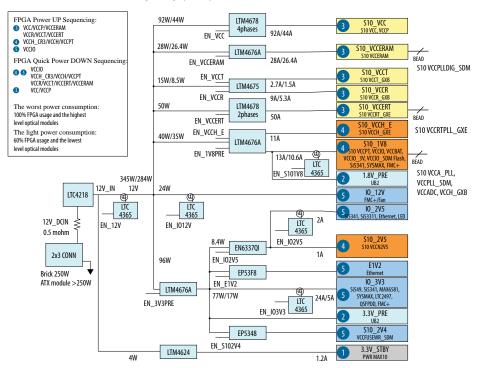

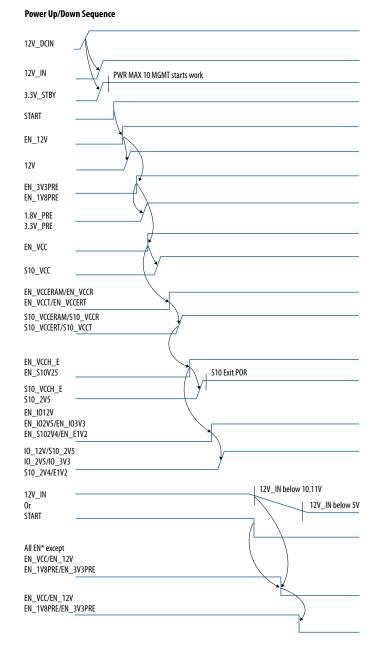

| 4.11. System Power                                                     |      |

| 4.11.1. Power Guidelines                                               |      |

| 4.11.2. Power Supply                                                   |      |

| 4.11.3. Power Management                                               |      |

| 4.11.4. Power Distribution System                                      |      |

| 4.11.5. Thermal Limitations and Protection Guidelines                  | 38   |

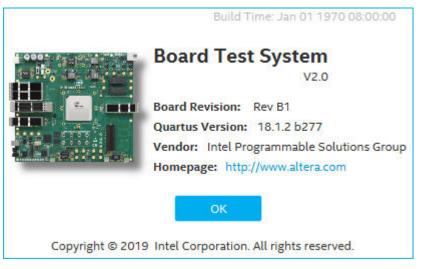

| 5. Board Test System                                                   | . 40 |

| 5.1. Preparing the Development Kit                                     | . 41 |

| 5.2. Running the Board Test System                                     | . 41 |

| 5.3. Using the Board Test System                                       | .42  |

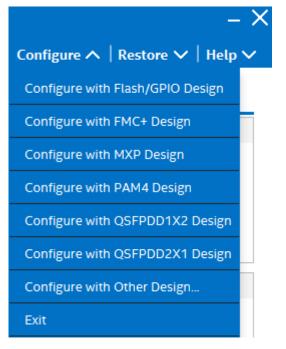

| 5.3.1. The Configure Menu                                              |      |

| 5.3.2. The System Info Tab                                             |      |

| 5.3.3. The GPIO Tab                                                    |      |

| 5.3.4. The EPCQ Tab                                                    | 45   |

| A.2.2. Safety Cautions<br>A.3. Compliance and Conformity Information |    |

|----------------------------------------------------------------------|----|

| A.2.2. Safety Cautions                                               |    |

| ······································                               |    |

| A.2.1. Safety Warnings                                               |    |

| A.2. Safety and Regulatory Information                               |    |

| A.1. Add SmartVID settings in QSF file                               |    |

| A. Additional Information                                            |    |

| 5.4. Simple Socket Server                                            |    |

| 5.3.11. Clock Controller                                             |    |

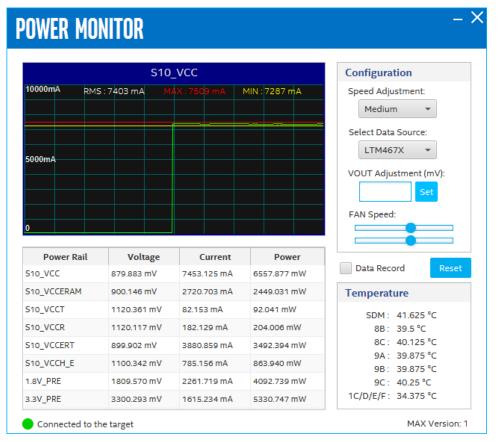

| 5.3.10. Power Monitor                                                | 67 |

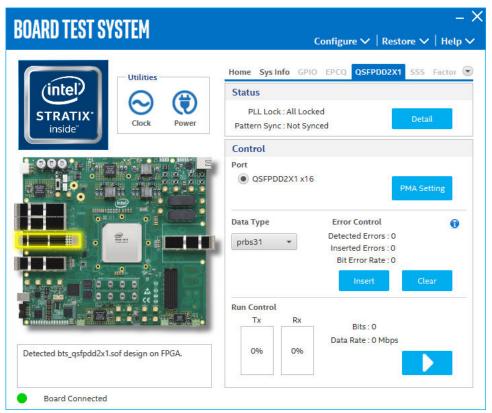

| 5.3.9. The QSFPDD2x1 Tab                                             | 63 |

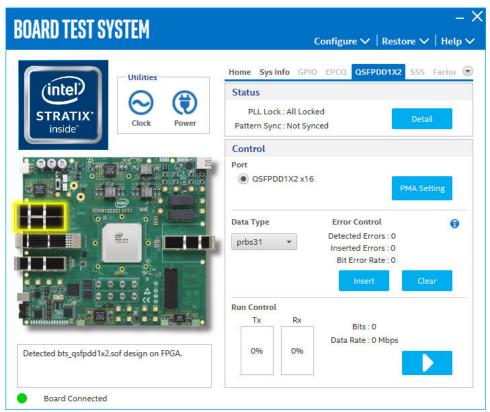

| 5.3.8. The QSFPDD1x2 Tab                                             | 59 |

| 5.3.7. The MXP Tab                                                   |    |

|                                                                      |    |

| 5.3.6. The PAM4 Tab                                                  |    |

## **1. Overview**

## **1.1. General Development Kit Description**

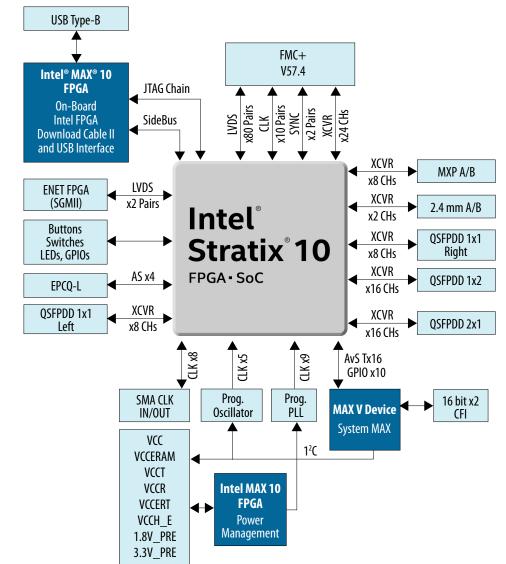

The Intel<sup>®</sup> Stratix<sup>®</sup> 10 TX Transceiver Signal Integrity Development Kit is a complete design environment that includes both hardware and software you need to develop Intel Stratix 10 TX FPGA designs.

The following list describes what you can accomplish with this kit:

- Evaluate transceiver performance up to 58 Gbps for E- Tile.

- Generate and check pseudo-random binary sequence (PRBS) patterns

- Dynamically change differential output voltage (VOD) pre-emphasis and equalization settings to optimize transceiver performance for your channel

- Perform jitter analysis

- Verify physical medium attachment (PMA) compliance to PCI Express\* (PCIe\*), 10G/25G/50G/100G/200G/400G Ethernet and other major standards.

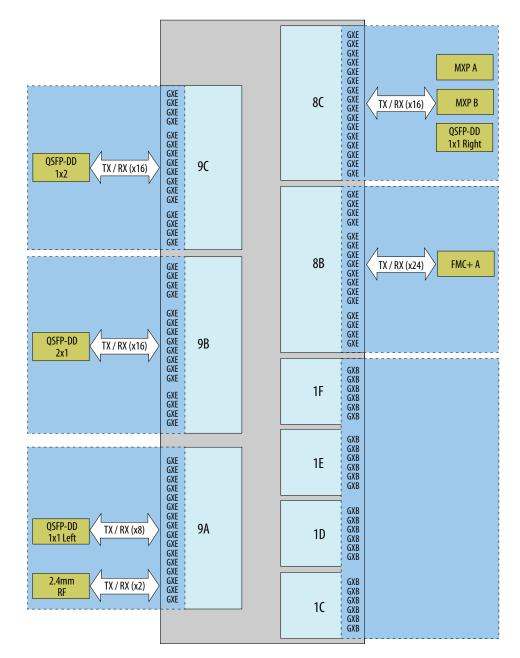

### Figure 1. Intel Stratix 10 TX Development Kit Block Diagram

### **1.2. Recommended Operating Conditions**

The recommended operating conditions for this development kit are:

- Recommended ambient operating temperature range: 0 °C to 45 °C

- Maximum I-VCCERT load current: 50 A

- Maximum ICC load transient percentage: 30 %

- FPGA maximum power supported by the supplied heatsink/fan: 200 W

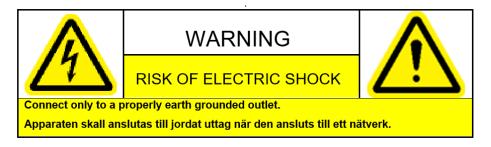

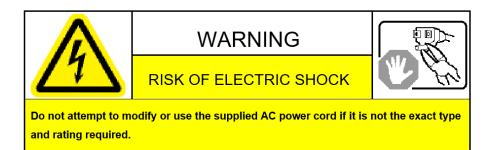

## 1.3. Handling the Kit

When handling the board, it is important to observe static discharge precautions.

- Note: Without proper anti-static handling, the board can be damaged. Therefore, use antistatic handling precautions when touching the board.

- Note: You must not operate this kit in a Vibration environment.

## **2. Getting Started**

## 2.1. About the Intel Quartus<sup>®</sup> Prime Software

The Intel Quartus<sup>®</sup> Prime design software is a multiplatform design environment that easily adapts to your specific needs in all phases of FPGA, CPLD, and SoC designs. The Intel Quartus Prime software delivers the highest performance and productivity for Intel FPGAs, CPLDs, and SoCs.

The new Intel Quartus Prime design software includes everything needed to design for Intel FPGAs, SoCs and CPLDs from design entry and synthesis to optimization, verification and simulation.

The Intel Quartus Prime Design Suite software is available in three editions based on specific design requirements: Pro, Standard, and Lite Edition.

The Intel Quartus Prime Pro Edition is optimized to support the advanced features in Intel's next generation FPGAs and SoCs.

The Intel Stratix 10 TX FPGA is only supported on Intel Quartus Prime Pro Edition. There is no paid license fee required for Intel Stratix 10 support in Intel Quartus Prime Pro Edition.

Included in the Intel Quartus Prime Pro Edition are the Intel Quartus Prime software,  $Nios^{(R)}$  II EDS and the MegaCore IP Library.

To install Intel's development tools, download the Intel Quartus Prime Pro Edition software from the Intel Quartus Prime Pro Edition page from Intel's website.

### 2.2. Development Kit Package

Unzip the initial package which includes board design files, Documents and Factory Recovery files directories. The table below lists the file directory names and a description of their contents.

### Table 1. Installed Development Kit Directory Structure

| Directory Name     | Description of Directory Contents                                                                                                                         |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| board_design_files | Contains schematics, layout, assembly and bill of material<br>board design files. Use these files as a starting point for a<br>new prototype board design |

| documents          | Contains the development kit documentation                                                                                                                |

| factory_recovery   | Contains the original data programmed onto the board<br>before shipment. Use this data to restore the board with its<br>original factory contents         |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

Note: To view the the layout \*.brd files in the board package, you can download the Cadence<sup>®</sup> Allegro<sup>®</sup>/OrCAD<sup>®</sup> Free Viewer from Cadence's website.

### **Related Information**

Cadence Allegro Downloads

### 2.3. Installing the Intel FPGA Download Cable II Driver

The Intel Stratix 10 TX Transceiver Signal Integrity Development Kit includes embedded Intel FPGA Download Cable II circuits for FPGA and MAX® V programming. However, for the host computer and board to communicate, you must install the Intel FPGA Download Cable II driver on the host computer.

Installation instructions for the Intel FPGA Download Cable II driver for your operating system are available on the Intel website.

On the Intel website, navigate to the Cable and Adapter Drivers Information link to locate the table entry for your configuration and click the link to access the instructions.

### **Related Information**

Cable and Adapter Drivers Information

## **3. Development Kit Setup**

The instructions in this chapter explain how to setup the Intel Stratix 10 TX Transceiver Signal Integrity Development Kit.

### 3.1. Setting up the Development Kit

To prepare and apply power to the board, perform the following steps:

- 1. The Intel Stratix 10 TX transceiver signal integrity development kit ships with its board switches preconfigured to support the design examples in the kit. If you suspect your board might not be correctly configured with the default settings, follow the instructions in the Factory Default Switch and Jumper Settings on page 10 to return the board to its factory settings before proceeding forward.

- 2. The development kit ships with design examples stored in the flash device. The **POWER-ON** slide switch (**SW10**) is provided to turn the board **ON** or **OFF**.

- *Note:* When the power cord is plugged into connector **J46** of the Intel Stratix 10 transceiver signal integrity development kit, 12V\_IN and 3.3V\_STBY are present on to the board with switch **SW10** in the **OFF** position. These voltages are restricted to a small area of the board. When switch **SW10** is placed to **ON** position, all voltages planes have power at this point.

- Set the **POWER-ON** switch **SW10** to the **ON** position. When power is supplied to the board, three green LEDs (**D23**, **D24** and **D25**) illuminate and an amber LED (**D5**) extinguishes indicating that the board has power. If the amber LED (**D5**) illuminates, it indicates that one or more power supply is incorrect.

- 4. RESET button (S7) is connected to the MAX V CPLD (MAX\_RESETn pin) that is used for AvST configuration. When this button is pressed, the MAX V CPLD initiates a reloading of the stored image from the flash memory using AvST configuration mode. The image loaded right after power cycle or MAX V reset depends on FACTORY\_LOAD SW5.1 settings.

- OFF(1) factory load

- ON (0) user defined load #1

Page selection can be changed by the PGMSEL button (**S5**) when the board is powered on, and PGM\_CONFIG (**S6**) is used to reconfigure FPGA with corresponding page which is indicated by PGM\_LED0, PGM\_LED1 or PGM\_LED2.

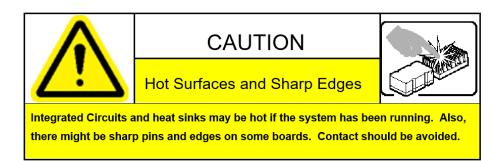

**Caution:** Use only the supplied power supply. Power regulation circuits on the board can get damaged by power supplies with greater voltage.

The MAX V CPLD device on the board contains a parallel flash loader II (PFL II) megafunction. If AvST configuration mode is selected, after a **POWER-ON** or **RESET** (reconfiguration) event, the MAX V CPLD configures the Intel Stratix 10 FPGA in AvST mode with either factory design or user design depending on the setting of FACTORY\_LOAD.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

This development kit includes a MAX V CPLD design which contains the PFL II megafunction. The design resides in the chage dir>\examples\max5 directory. When configuration is complete, LED **D21** (CONF\_DONE) illumintes signaling that the Intel Stratix 10 TX FPGA device is configured successfully. If the configuration fails, the LED **D19** (ERROR) illuminates.

## **3.2. Factory Default Switch and Jumper Settings**

This section shows the factory default switch and jumper settings for the Intel Stratix 10 TX transceiver signal integrity development kit.

| Switch    | Board Label           | Default Position | Function                                      |

|-----------|-----------------------|------------------|-----------------------------------------------|

| CIMO      | MSEL1                 | MSEL1=0          | MSEL Setting = 0                              |

| SW8       | MSEL2                 | MSEL2=0          | MSEL Setting = 0                              |

| SW1-1     | Stratix 10            | OPEN/OFF         | Enable Intel Stratix 10 in<br>JTAG Chain      |

| SW1-2     | MAX V                 | OPEN/OFF         | Enable MAX V in JTAG chain                    |

| SW1-3     | FMC A                 | CLOSE/ON         | Bypass FMC from JTAG chair                    |

| SW1-4     | UBMAX_DIP             | OPEN/OFF         | UB MAX V User Dipswitch                       |

| SW6-1     | OFF = OSC<br>ON = SMA | OPEN/OFF         | Select Si549 clock source fo<br>U1            |

| SW6-2/3/4 | PWRMAX_DIP            | OPEN/OFF         | Power MAX V User Dipswitch                    |

| SW7-1     | OFF=VCC ISOLATE       | CLOSE/ON         | U47/U48 (LTM4680) are enabled in I2C topology |

| SW7-2     | ON=FULL CHAIN         | CLOSE/ON         | U47/U48 (LTM4680) are enabled in I2C topology |

| SW3-1     | EN_VCCH_E             | OPEN/OFF         | Enable on-board VCCH_E<br>regulator           |

| SW3-2     | EN_VCCERT             | OPEN/OFF         | Enable on-board VCCERT regulator              |

| SW2-1     | VCCR                  | OPEN/OFF         | Enable on-board VCCR<br>regulator             |

| SW2-2     | VCCT                  | OPEN/OFF         | Enable on-board VCCT<br>regulator             |

| SW2-3     | VCCERAM               | OPEN/OFF         | Enable on-board VCCERAM regulator             |

| SW2-4     | VCC                   | OPEN/OFF         | Enable on-board VCC<br>regulator              |

| SW5-1     | FACTORY_LOAD          | OPEN/OFF         | Factory Load Control                          |

| SW5-2     | MAX5_SWITCH2          | OPEN/OFF         | MAX V user DIPSwitch                          |

| SW5-3     | MAX5_SWITCH0          | OPEN/OFF         | MAX V user DIPSwitch                          |

| SW5-4     | MAX5_SWITCH1          | OPEN/OFF         | MAX V user DIPSwitch                          |

#### Table 2. **Factory Default Switch Settings**

### 3. Development Kit Setup 683591 | 2019.09.27

## intel

| Switch | Board Label | Default Position | Function                           |

|--------|-------------|------------------|------------------------------------|

| SW4-1  | S10_UNLOCK  | OPEN/OFF         | Intel Stratix 10 User<br>DIPSwitch |

| SW4-2  | USER_DIP2   | OPEN/OFF         | Intel Stratix 10 User<br>DIPSwitch |

| SW4-3  | USER_DIP1   | OPEN/OFF         | Intel Stratix 10 User<br>DIPSwitch |

| SW4-4  | USER_DIP0   | OPEN/OFF         | Intel Stratix 10 User<br>DIPSwitch |

| SW10   | SW10        | OFF              | On-board power switch              |

## **4. Development Kit Components**

### 4.1. Development Kit Overview

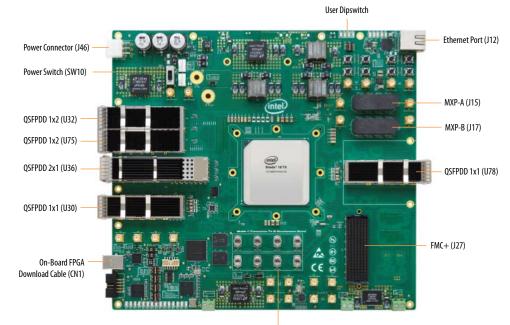

### Figure 2. Intel Stratix 10 TX Transceiver Signal Integrity Development Kit Picture

2.4mm SMA

### Table 3. Development Kit Components

| Board Reference               | Туре               | Description                                              |  |  |

|-------------------------------|--------------------|----------------------------------------------------------|--|--|

|                               | Featured Devices   |                                                          |  |  |

| U39                           | FPGA               | Intel Stratix 10 TX 280 F2912 FPGA<br>(1ST280EY2F55E1VG) |  |  |

| U13                           | CPLD               | System MAX V CPLD (5M2210ZF256)                          |  |  |

| U4                            | FPGA               | USB Intel MAX 10 FPGA<br>(10M04SCU169)                   |  |  |

| U8                            | FPGA               | PWR Intel MAX 10 FPGA<br>(10M16SAU169)                   |  |  |

| General User Input and Output |                    |                                                          |  |  |

| D12-D15                       | User LEDs (Green)  | User LEDs (Green)                                        |  |  |

| D16-D21                       | MAX V LEDs (Green) | MAX V LEDs (Green)                                       |  |  |

|                               | 1                  | continued                                                |  |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

### 4. Development Kit Components 683591 | 2019.09.27

# intel.

| Board Reference | Туре                                                                                 | Description                                                                                                                                                                                                        |

|-----------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S1-S4           | User Push Buttons                                                                    | User Push Buttons                                                                                                                                                                                                  |

| SW4             | User DIP Switches                                                                    | User DIP                                                                                                                                                                                                           |

| SW5             | MAX V DIP Switch                                                                     | MAX V DIP Switch                                                                                                                                                                                                   |

| S5-S8           | MAX V Push Buttons                                                                   | MAX V Push Buttons                                                                                                                                                                                                 |

|                 | Configuration, Status and Setup Element                                              | nts                                                                                                                                                                                                                |

| 38              | Embedded Intel FPGA Download Cable<br>II Programming Header (uses JTAG<br>mode only) | Header to interface external Intel FPGA<br>Download Cable direct to FPGA<br>(through USB Intel MAX 10)                                                                                                             |

| D1-D2           | Green LEDs                                                                           | JTAG transmit-Receive Activity                                                                                                                                                                                     |

| D3-D4           | Green LEDs                                                                           | System Console transmit-Receive<br>Activity                                                                                                                                                                        |

| D5              | Amber LEDs                                                                           | System Power error indicator                                                                                                                                                                                       |

| D6              | Amber LEDs                                                                           | Temperature alert indicator                                                                                                                                                                                        |

| D7-D11          | Ethernet LEDs                                                                        | Ethernet LEDs (TX/RX/LINK)                                                                                                                                                                                         |

|                 | Clock Circuits                                                                       |                                                                                                                                                                                                                    |

| X2              | 50-MHz Oscillator                                                                    | This 50-MHz oscillator is the clock<br>source to clock buffer SL18860DC that<br>provides three 50 MHz outputs to the<br>FPGA, MAX V and UB2 Intel MAX 10                                                           |

| X1              | 50-MHz Oscillator                                                                    | This 50-MHz oscillator provides clock to the PWR Intel MAX 10 FPGA                                                                                                                                                 |

| Y1              | Transceiver Dedicated Reference Clock/<br>Programmable Oscillator                    | Feed clock for Intel Stratix 10 TX<br>device and an LVDS trigger output at<br>board reference J3/J4. The external<br>input is available at board reference J1<br>and J2. The default frequency is<br>156.25 MHz.   |

| U1              | High-speed clock buffer                                                              | Fan-out REFCLKs for Intel Stratix 10 TX transceiver banks                                                                                                                                                          |

| U3              | Transceiver Dedicated Reference Clock/<br>Programmable PLL                           | Feeds clocks for Intel Stratix 10 TX<br>device and an LVDS trigger output at<br>board reference J5/J6. The default<br>frequencies are 156.25 MHz, 125 MHz,<br>100 MHz, 322.265625 MHz, 176.5625<br>MHz, 307.2 MHz. |

| J30,J32         | External core clock input                                                            | SMA external input at CLKIN_2L                                                                                                                                                                                     |

| J31,J33         | External core clock output                                                           | SMA external output at<br>PLL_2L_CLKOUT0                                                                                                                                                                           |

| J34-J35         | External transceiver clock input                                                     | SMA external input at H-tile 1D bank                                                                                                                                                                               |

| J36-J37         | External transceiver clock input                                                     | SMA external input at E-tile 8B bank                                                                                                                                                                               |

| J38-J39         | External transceiver clock input                                                     | SMA external input at E-tile 8C bank                                                                                                                                                                               |

| J40-J41         | External transceiver clock input                                                     | SMA external input at E-tile 9A bank                                                                                                                                                                               |

| J42-J43         | External transceiver clock input                                                     | SMA external input at E-tile 9B bank                                                                                                                                                                               |

| ]44-]45         | External transceiver clock input                                                     | SMA external input at E-tile 9C bank                                                                                                                                                                               |

|                 | Transceiver Interfaces                                                               |                                                                                                                                                                                                                    |

|                 |                                                                                      | continued                                                                                                                                                                                                          |

| Board Reference | Туре                                     | Description                                                                                    |

|-----------------|------------------------------------------|------------------------------------------------------------------------------------------------|

| J15/J17         | MXP connector                            | NRZ 28.9 Gbps or PAM4 58 Gbps, 4 channels connected to each MXP connector                      |

| J19-J26         | 2.4 mm RF connector                      | NRZ 28.9 Gbps or PAM4 58 Gbps, 2<br>channels connected to 2.4 mm RF<br>connector               |

| U30/U78         | QSFPDD 1x1 optical transceiver interface | PAM4 58 Gbps, 8 channels connected to 400 Gbps module                                          |

| U32/U75         | QSFPDD 1x2 optical transceiver interface | NRZ 28.9 Gbps, 8 channels per port connected 200 Gbps module                                   |

| U36             | QSFPDD 2x1 optical transceiver interface | NRZ 28.9 Gbps, 8 channels per port connected to both top and bottom 200 Gbps module            |

| J27             | FMC+ connector                           | NRZ 28 Gbps, 24 channels connected to FMC+ connector                                           |

|                 | Memory Devices                           |                                                                                                |

| U14-U15         | Flash Memory                             | Two 1-Gbit Micron<br>MT28EW01GABA1HPC CFI Flash device                                         |

|                 | Communication Ports                      |                                                                                                |

| J12             | Gigabit Ethernet Port                    | RJ-45 connector which provides a 10/100/1000 Ethernet connection through a Marvell 88E1111 PHY |

| CN1             | USB Type-B connector                     | Connects a type-B USB cable                                                                    |

|                 | Power Supply                             |                                                                                                |

| U47-U48         | Two LTM4678s                             | Power regulators for VCC rail                                                                  |

| U49             | LTM4676A                                 | Power regulator for VCCERAM rail                                                               |

| U51             | LTM4678                                  | Power regulator for VCCERT rail                                                                |

| U50             | LTM4675                                  | Power regulator for VCCR/VCCT rail                                                             |

| U52             | LTM4676A                                 | Power regulator for 1.8V/VCCH_E rail                                                           |

| U58             | EP5348UI                                 | Power regulator for 2.4V rail                                                                  |

| U60             | EN5339                                   | Power regulator for 2.5V rail                                                                  |

| U53             | LTM4676A                                 | Power regulator for 3.3V rail                                                                  |

### 4.2. Intel Stratix 10 TX FPGA

The development board features the Intel Stratix 10 TX FPGA (1ST280EY2F55E1VG).

### Table 4.Intel Stratix 10 TX FPGA I/O Summary

| I/O Count     | Description                                          |  |

|---------------|------------------------------------------------------|--|

| Configuration |                                                      |  |

| 4             | JTAG pins                                            |  |

| 3             | Configuration input pins to set configuration scheme |  |

|               | Configuration 4                                      |  |

### 4. Development Kit Components 683591 | 2019.09.27

# intel

| Signal Name         | I/O Count    | Description                                              |

|---------------------|--------------|----------------------------------------------------------|

| FPGA_CONF_DONE      | 1            | Configuration done pin                                   |

| FPGA_nSTATUS        | 1            | Configuration status pin                                 |

| FPGA_INIT_DONE      | 1            | Configuration pin to signify user mode                   |

| FPGA_nCONFIG        | 1            | Configuration input pin to reset FPGA                    |

| FPGA_OSC_CLK_1      | 1            | 125 MHz Clock                                            |

| FPGA_AS_CLK         | 1            | Configuration Clock for AS configuration schemes         |

| CPU_RESETn          | 1            | Configuration input pin that clears all device registers |

| FPGA_CONFIG_D[15:0] | 32           | Configuration input pin that enables all I/Os            |

| FPGA_AS_DATA[3:0]   | 4            | EPCQL data bus                                           |

| FPGA_AVST_READY     | 1            | SDM ready for AvST configuration scheme                  |

| FPGA_AVST_VALID     | 1            | Data valid for AvST configuration scheme                 |

| FPGA_AVST_CLK       | 1            | Configuration Clock for AvST configuration scheme        |

| FPGA_PR_DONE        | 1            | Partial reconfiguration done pin                         |

| FPGA_PR_REQUEST     | 1            | Partial reconfiguration request pin                      |

| FPGA_PR_ERROR       | 1            | Partial reconfiguration error pin                        |

| NPERSTL0            | 1            | Reset pin for left bottom PCIe HIP                       |

| FPGA_CvP_DONE       | 1            | CvP configuration done pin                               |

| FPGA_SEU_ERR        | 1            | SEU error indicate pin                                   |

| VCC_SDA/SCL         | 2            | SmartVID I <sup>2</sup> C bus                            |

| VCC_ALERTn          | 1            | SmartVID I <sup>2</sup> C bus                            |

|                     | Transceivers |                                                          |

| OIF_SCL[1:0]        | 2            | Optical Management Data Clock 0                          |

| OIF_SDA[1:0]        | 2            | Optical Management Data I/O Bi-<br>Directional Data 0    |

| DDQ1x1_modselL      | 1            | DDQ1x1 module select control pin                         |

| DDQ1x1_resetL       | 1            | DDQ1x1 module reset control pin                          |

| DDQ1x1_Initmode     | 1            | DDQ1x1 initiate mode control pin                         |

| DDQ1x1_modprsL      | 1            | DDQ1x1 module present indicator pin                      |

| DDQ1x1_int1[1:0]    | 2            | DDQ2x1 module interrupt pin                              |

| DDQ1x1_1_modselL    | 1            | DDQ1x1 module select control pin                         |

| DDQ1x1_1_resetL     | 1            | DDQ1x1 module reset control pin                          |

| DDQ1x1_1_Initmode   | 1            | DDQ1x1 initiate mode control pin                         |

|                     | 1            | continued                                                |

### 4. Development Kit Components 683591 | 2019.09.27

| Signal Name              | I/O Count | Description                                           |

|--------------------------|-----------|-------------------------------------------------------|

| DDQ1x1_1_modprsL         | 1         | DDQ1x1 module present indicator pin                   |

| DDQ1x1_1_int1[1:0]       | 2         | DDQ2x1 module interrupt pin                           |

| DDQ2x1_modselL[1:0]      | 2         | DDQ2x1 module select control pin                      |

| DDQ2x1_resetL[1:0]       | 2         | DDQ2x1 module reset control pin                       |

| DDQ2x1_Initmode[1:0]     | 2         | DDQ2x1 initiate mode control pin                      |

| DDQ2x1_modprsL[1:0]      | 2         | DDQ2x1 module present indicator pin                   |

| DDQ2x1_intl[1:0]         | 2         | DDQ2x1 module interrupt pin                           |

| DDQ1x2_modselL[1:0]      | 2         | DDQ1x2 module select control pin                      |

| DDQ1x2_resetL[1:0]       | 2         | DDQ1x2 module reset control pin                       |

| DDQ1x2_Initmode[1:0]     | 2         | DDQ1x2 initiate mode control pin                      |

| DDQ1x2_modprsL[1:0]      | 2         | DDQ1x2 module present indicator pin                   |

| DDQ1x2_int1[1:0]         | 2         | DDQ1x2 module interrupt pin                           |

| FALAp/n[31:0]            | 64        | FMC+ A LA bank GPIOs                                  |

| FALAp/n[33:32]_CON       | 4         | FMC+ A LA bank GPIOs                                  |

| FAHAp/n[23:0]            | 48        | FMC+ A HA bank GPIOs                                  |

| FAHBp/n[21:0]            | 44        | FMC+ A HB bank GPIOs                                  |

| FACLKM2CP/N[1:0]         | 4         | FMC+ A general clocks                                 |

| FACLKBIDIRP/N[3:2]       | 4         | FMC+ A general clocks                                 |

| FAREFCLKC2MP/N           | 2         | FMC+ A general clocks                                 |

| FAREFCLKM2CP/N           | 2         | FMC+ A general clocks                                 |

| FASYNCC2MP/N             | 2         | FMC+ A general clocks                                 |

| FASYNCM2CP/N             | 2         | FMC+ A general clocks                                 |

| RZQ_2N                   | 1         | RZQ pin for bank 2N                                   |

|                          | Other Bus |                                                       |

| USER_DIP[2:0]/S10_Unlock | 4         | User Dipswitch bits                                   |

| USER_LED[3:0]            | 4         | User LED bits                                         |

| USER_IO[9:0]             | 10        | User IO bits                                          |

| USER_PB[3:0]             | 4         | User Push Button bits                                 |

| USB_DATA[7:0]            | 8         | Side bus between Intel Stratix 10 and UB2Intel MAX 10 |

| USB_ADDR[1:0]            | 2         | Side bus between Intel Stratix 10 and UB2Intel MAX 10 |

| USB_FULL/EMPTY/RESETn    | 3         | Side bus between Intel Stratix 10 and UB2Intel MAX 10 |

| USB_OEn/RDn/WRn          | 3         | Side bus between Intel Stratix 10 and UB2Intel MAX 10 |

|                          |           | continued                                             |

### 4. Development Kit Components 683591 | 2019.09.27

# intel

| Signal Name             | I/O Count          | Description                                           |

|-------------------------|--------------------|-------------------------------------------------------|

| USB_SCL/SDA             | 2                  | Side bus between Intel Stratix 10 and UB2Intel MAX 10 |

| ENET_MDIO/MDC/RSTn/INTn | 4                  | 10/100/1000M Ethernet port                            |

| ENET_SGMII_TX_P/N       | 2                  | 10/100/1000M Ethernet port                            |

| ENET_SGMII_RX_P/N       | 2                  | 10/100/1000M Ethernet port                            |

| I2C_1V8_SCL             | 1                  | Intel Stratix 10 I <sup>2</sup> C bus                 |

| I2C_1V8_SDA             | 1                  | Intel Stratix 10 I <sup>2</sup> C bus                 |

|                         | Temperature        |                                                       |

| OVERTEMPn_1V8           | 1                  | Intel Stratix 10 over temperature indicator           |

| TEMP_ALERTn_1V8         | 1                  | Intel Stratix 10 temperature alert indicator          |

|                         | Global Clocks      |                                                       |

| CLK_50M_S10             | 1                  | 50 MHz Global clock input                             |

| CLK_TOP_PLL_125M_p/n    | 2                  | 125 MHz differential core clock for top               |

| CLKIN_SMA_2L_p/n        | 2                  | Global Clock input from SMA                           |

| CLKOUT_SMA_2L_p/n       | 2                  | Dedicated Clock output to SMA                         |

| USB_FPGA_CLK            | 1                  | USB FPGA Clock                                        |

| CLK_BOT_PLL_100M_p/n    | 2                  | 100 MHz differential core clock for bottom            |

|                         | Transceiver Clocks | · ·                                                   |

| CLK_9C_OSC_156M_p/n     | 2                  | Differential REFCLK to xcvr bank 9C                   |

| CLK_9B_OSC_156M_p/n     | 2                  | Differential REFCLK to xcvr bank 9B                   |

| CLK_9A_OSC_156M_p/n     | 2                  | Differential REFCLK to xcvr bank 9A                   |

| CLK_8C_OSC_156M_p/n     | 2                  | Differential REFCLK to xcvr bank 8C                   |

| CLK_8B_OSC_156M_p/n     | 2                  | Differential REFCLK to xcvr bank 8B                   |

| CLK_9C_PLL_322M_p/n     | 2                  | Differential REFCLK to xcvr bank 9C                   |

| CLK_9B_PLL_322M_p/n     | 2                  | Differential REFCLK to xcvr bank 9B                   |

| CLK_9A_PLL_176M_p/n     | 2                  | Differential REFCLK to xcvr bank 9A                   |

| CLK_8C_PLL _176M_p/n    | 2                  | Differential REFCLK to xcvr bank 8C                   |

| CLK_8B_PLL _307M_p/n    | 2                  | Differential REFCLK to xcvr bank 8B                   |

| CLK_1E_PLL_307M_p/n     | 2                  | Differential REFCLK to xcvr bank 1E                   |

| CLKIN_SMA_1D_p/n        | 2                  | Differential REFCLK to xcvr bank 1D                   |

| CLKIN_SMA_8B_p/n        | 2                  | Differential REFCLK to xcvr bank 8B                   |

| CLKIN_SMA_8C_p/n        | 2                  | Differential REFCLK to xcvr bank 8C                   |

| CLKIN_SMA_9A_p/n        | 2                  | Differential REFCLK to xcvr bank 9A                   |

|                         | 1                  | continued                                             |

| Signal Name         | I/O Count | Description                         |

|---------------------|-----------|-------------------------------------|

| CLKIN_SMA_9B_p/n    | 2         | Differential REFCLK to xcvr bank 9B |

| CLKIN_SMA_9C_p/n    | 2         | Differential REFCLK to xcvr bank 9C |

| FAGBTCLKM2CP/N[5:0] | 12        | Differential REFCLK to xcvr bank 8B |

Note:

SmartVID graded devices require the use of a configurable voltage regulator or system controller to receive the device's settings through the Power Management Bus (PMBus<sup>™</sup>) or Pulse-Width Modulation (PWM) interface for proper performance.

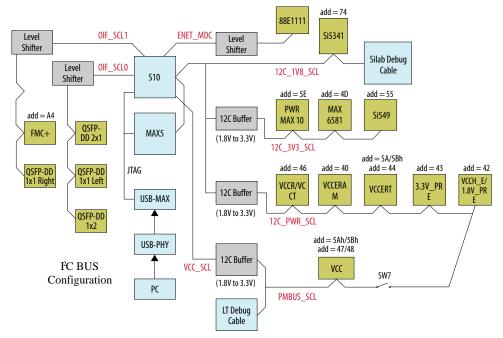

## 4.3. MAX V CPLD

The Intel Stratix 10 TX transceiver signal integrity development kit consists of a MAX V CPLD (5M2210Z-F256), 256-pin FineLine BGA package. MAX V CPLD devices provide programmable solutions for applications such as FPGA reconfiguration from flash memory, I2C chain to manage power consumption, core temperature, fan speed, clock frequency. MAX V devices feature on-chip flash storage, internal oscillator and memory functionality. With up to 50% lower total power versus other CPLDs and requiring as few as one power supply, MAX V CPLDs can help you meet your low power design requirements.

The following list summarizes the features of MAX V CPLD devices:

- 2210 Logic Elements (LEs)

- 8192 bits of User Flash Memory

- 4 global clocks

- 1 internal oscillator

- 271 maximum user I/O pins

- Low-cost, low power and non-volatile CPLD architecture

- Fast propagation delays and clock-to-output times

- Single 1.8V external supply for device core

- Bus-friendly architecture including programmable slew rate, drive strength, bushold and programmable pull-up resistors

### Table 5. MAX V I/O Summary

| Signal Name    | Description            |

|----------------|------------------------|

| FA_A[27:1]     | Flash Address Bus      |

| FM_D[15:0]     | Flash Data Bus         |

| FLASH_RESETN   | Flash reset            |

| FLASH_CEn[1:0] | Flash chip enable      |

| FLASH_OEn      | Flash output enable    |

| FLASH_WEn      | Flash write enable     |

| FLASH_WPn      | Flash write protection |

| FLASH_RDYBSYn  | Flash chip ready/busy  |

|                | continued              |

| Signal Name         | Description                                                      |

|---------------------|------------------------------------------------------------------|

| FLASH_BYTEn         | Flash byte enable                                                |

| FPGA_CONFIG_D[15:0] | FPGA AvST Configuration Data Bus                                 |

| FPGA_INIT_DONE      | FPGA initialization complete                                     |

| FPGA_nSTATUS        | FPGA status                                                      |

| FPGA_CONF_DONE      | FPGA configuration complete                                      |

| FPGA_nCONFIG        | FPGA configuration control pin to reset FPGA                     |

| FPGA_SEU_ERR        | FPGA configuration SEU error                                     |

| FPGA_CvP_DONE       | FPGA CvP configuration done                                      |

| FPGA_PR_REQUEST     | FPGA partial reconfiguration request                             |

| FPGA_PR_DONE        | FPGA partial reconfiguration done                                |

| FPGA_PR_ERROR       | FPGA partial reconfiguration error                               |

| FPGA_MSEL[2:0]      | FPGA configuration mode setting bits                             |

| FPGA_AVST_CLK       | FPGA AvST Configuration clock                                    |

| FPGA_AVST_VALID     | FPGA AvST Configuration data valid                               |

| FPGA_AVST_READY     | FPGA AvST Ready to receive data                                  |

| 12C_1V8_SCL         | MAX V I2C bus                                                    |

| I2C_1V8_SDA         | MAX V I2C bus                                                    |

| SI5341_ENn          | SI5341 1 enable                                                  |

| SI5341_INTn         | SI5341 1 interrupt indicators                                    |

| SI5341_RSTn         | SI5341 1 reset                                                   |

| SI5341_LOLn         | SI5341 1 loss of lock indicators                                 |

| SI547_FS[1:0]       | SI547 frequency selection bits when Si549 is replaced with Si547 |

| PCIe_PERSTn_1V8     | 1.8V PCIe reset signal                                           |

| PCIe_PERSTn_3V3     | 3.3V PCIe reset signal                                           |

| PCIe_WAKEn_3V3      | 3.3V PCIe wake signal                                            |

| FACLKDIR            | FMC+ bi-directional clock direction selection bit                |

| PMBUS_ALERTn        | VCC regulator alert                                              |

| I2C_PWR_ALERTn      | Other regulators alert                                           |

| VCC_ALERTn          | 1.8V VCC regulator alert                                         |

| EN_MASTER[2:0]      | Enable specific I <sup>2</sup> C buffer                          |

| OVERTEMPn_1V8       | FPGA over temperature input 1.8V                                 |

| TEMP_ALERTn         | FPGA temperature alert output                                    |

| OVERTEMPn           | FPGA over temperature output                                     |

|                     |                                                                  |

### 4. Development Kit Components 683591 | 2019.09.27

| Signal Name      | Description                                         |

|------------------|-----------------------------------------------------|

| USB_CFG[14:0]    | Bus between USB MAX 10 and MAX V                    |

| USB_SYSMAX_CLK   | Clock from USB PHY chip                             |

| MAX_OSC_CLK_1    | 25M/100M/125MHz clock input                         |

| SYSMAX_JTAG_TCK  | MAX V TCK                                           |

| SYSMAX_JTAG_TMS  | MAX V TMS                                           |

| SYSMAX_JTAG_TDI  | MAX V TDI                                           |

| SYSMAX_JTAG_TDO  | MAX V TDO                                           |

| FACTORY_LOAD     | Factory image for configuration                     |

| MAX5_SWITCH[2:0] | System MAX V user dipswitch                         |

| PGM_SEL          | Flash memory PGM select pushbutton                  |

| PGM_CONFIG       | Flash memory PGM configuration pushbutton           |

| MAX_RESETn       | System MAX V reset pushbutton                       |

| CPU_RESETn       | CPU reset pushbutton                                |

| PGM_LED[2:0]     | Flash image PGM select indicators                   |

| MAXV_ERROR       | Intel Stratix 10 configuration error indicator LED  |

| MAXV_LOAD        | Intel Stratix 10 configuration active indicator LED |

| MAXV_CONF_DONE   | Intel Stratix 10 configuration done indicator LED   |

| USER_IO[9:0]     | User general I/Os                                   |

| CLK_50M_SYSMAX   | 50 MHz Clock input                                  |

| OPT_FAN_RPM      | Optical interface fan speed control                 |

| FAN_RPM          | FPGA fan speed control                              |

#### I<sup>2</sup>C Diagram Figure 3.

### 4.4. FPGA Configuration

This section describes the FPGA, flash memory and MAX V CPLD System Controller device programming methods supported by the Intel Stratix 10 TX tranceiver signal integrity development kit.

Three configuration methods are mostly used on the Intel Stratix 10 TX transceiver signal integrity development kit.

Embedded Intel FPGA Download Cable II is the default method for configuring the FPGA at any time using the Intel Quartus Prime Programmer in JTAG mode with the supplied USB cable.

MAX V configures the FPGA device via AvST mode using stored images from CFI flash devices either at power-up or pressing the MAX RESETn/PGM CONFIG push button.

JTAG external header for debugging. Intel recommends that you use lower JTAG clock frequency value such as 16 MHz.

### 4.4.1. Configuring the FPGA over Embedded Intel FPGA Download Cable II

Embedded Intel FPGA Download Cable II is the default method for configuring the Intel Stratix 10 TX FPGA using the Intel Quartus Prime Programmer in the JTAG mode with the supplied USB cable.

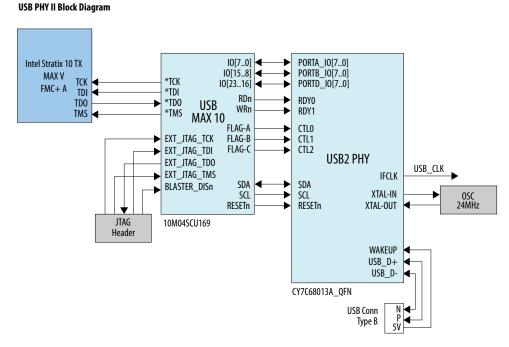

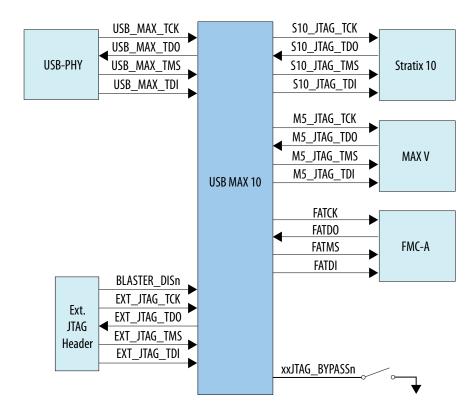

#### Figure 4. Embedded Intel FPGA Download Cable II

The embedded Intel FPGA Download Cable II for USB-based configuration of the Intel Stratix 10 TX FPGA device is implemented using a Type-B USB connector, a CY7C68013A USB2 PHY device, and an Intel MAX 10 10M04SCU169 FPGA. This will allow configuration of the Intel Stratix 10 TX FPGA device using a USB cable directly connected to a computer running Intel Quartus Prime software without requiring the external Intel FPGA Download Cable dongle.

This design will convert USB data to interface with the Intel Stratix 10 TX FPGA's dedicated JTAG port. Four LEDs are provided to indicate embedded Intel FPGA Download Cable II activity. The embedded Intel FPGA Download Cable II is automatically disabled when an external Intel FPGA Download Cable dongle is connected to the JTAG header.

### 4.4.2. Configuring the FPGA through Flash Memory

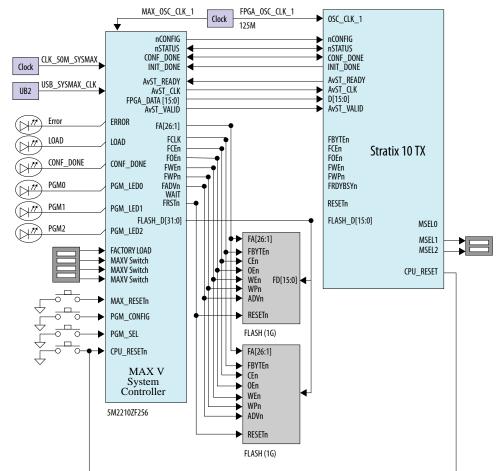

The figure below shows a detailed schematic block diagram for the MAX V + Flash AvSTx16 mode configuration implementation.

Typical JTAG clock frequency for CFI Flash programming via PFL II core is 16 MHz. You Note: may try it with a lower frequency such as 6 MHz if it fails with 16 MHz.

### Figure 5. MAX V Configuration Block Diagram

The PGMSEL dipswitch (S5) is provided to select between POF files (FACTORY and USER) stored on the Flash.

The Parallel Flash Loader II (PFL II) Megafunction is used to implement the AvSTx16 configuration in the MAX V CPLD. The PFL II Megafunction reads data from the flash and converts it to AvST format. This data is written into the Intel Stratix 10 TX FPGA device through dedicated AvST CLK and FPGA Config Data [15:0] pins at corresponding clock rate, such as 25 MHz, 50 MHz and 100 MHz.

Implementation will be done using an MAX V 5M2210ZF256FBGA CPLD acting as the AvST download controller and two 1G Flash devices.

If AvST configuration mode is selected, after a POWER-ON or RESET (reconfiguration) event, the MAX V device shall configure the Intel Stratix 10 TX FPGA in the AvST x16 mode with either the FACTORY POF or an USER DEFINED POF depnding on the FACTORY\_LOAD setting.

The MSEL[2:0] pins indicate which configuration scheme is chosen. The manufacturing default condition is [001] for Fast AS x4 scheme.

For different configuration modes, MSEL [2:0] signals must be set acccording to the table below:

#### Table 6. Support Configuration Modes for Stratix 10 TX Transceiver Signal Integrity

| Configuration Scheme | MSEL [2:0]     |

|----------------------|----------------|

| Avalon-ST (x16)      | 101            |

| AS (Normal mode)     | 011            |

| AS (Fast)            | 001            |

| JTAG only            | 111            |

| Not supported        | Other Settings |

### 4.4.3. Configuring the FPGA over External Intel FPGA Download Cable

The JTAG chain allows programming of both the Intel Stratix 10 TX FPGA and MAX V CPLD devices using an external Intel FPGA Download Cable dongle or the on-board Intel FPGA Download Cable II via the USB Interface Connector. During board bring-up, and as a back-up in case the on-board Intel FPGA Download Cable II has a problem, the external Intel FPGA Download Cable can be used to program both the Intel Stratix 10 and MAX V CPLD via the Intel FPGA Download Cable 2x5 pin 0.1" programming header (J8)

Another 2x5 pin 0.1" vertical non-shrouded header (J9) is provided on the board for programming the Intel MAX 10 FPGA for configuring the on-board Intel FPGA Download Cable II circuitry. Once the on-board Intel FPGA Download Cable II is configured and operational, the on-board Intel FPGA Download Cable II can be used for subsequent programming of the Intel Stratix 10 TX FPGA and MAX V CPLD.

The on-board Intel FPGA Download Cable II JTAG chain connects the downstream JTAG nodes in the following order, with the option to bypass the Intel Stratix 10, MAX V, FMC by a dip switch SW1 setting as follows:

- Switch closed/ON: Corresponding JTAG node is bypassed.

- Switch open/OFF: Corresponding JTAG node is enabled in the JTAG chain.

Pin 2 of the J8 Header is used to disable the embedded Intel FPGA Download Cable II by connecting it to the embedded Intel FPGA Download Cable II's low active disable pin with a pull-up resistor. Since Pin 2 from the mating Intel FPGA Download Cable dongle is GND, when the dongle is connected into the JTAG header, the embedded Intel FPGA Download Cable II is disabled to avoid contention with the external Intel FPGA Download Cable dongle.

#### Figure 6. **JTAG**

## 4.5. Status and Setup Elements

The development board includes board-specific status LEDs and switches for enabling and configuring various features on the board. This section describes these status elements.

### Table 7. Board Specific LEDs

| Board Reference | Signal Name | Description                                                     |

|-----------------|-------------|-----------------------------------------------------------------|

| D23             |             | Green LED. Power 3.3 V present                                  |

| D24             |             | Green LED. Power 3.3 V PRE present                              |

| D25             |             | Green LED. Power 12 V present                                   |

| D5              | PWR_ERR_LED | Amber LED. System Power error indicator                         |

| D1              | JTAG_RX     | Green LED. JTAG receiver activity indicator                     |

| D2              | JTAG_TX     | Green LED. JTAG transmitter activity indicator                  |

| D3              | SC_RX       | Green LED. System console receiver activity indicator           |

| D4              | SC_TX       | Green LED. System console transmitter activity indicator        |

| D7              | ENET_LED_TX | Green LED. Blinks to indicate Ethernet<br>PHY transmit activity |

| continued       |             |                                                                 |

| Board Reference | Signal Name       | Description                                                                            |

|-----------------|-------------------|----------------------------------------------------------------------------------------|

| D8              | ENET_LED_RX       | Green LED. Blinks to indicate Ethernet PHY receive activity.                           |

| D9              | ENET_LED_LINK1000 | Green LED. Illuminates to indicate<br>Ethernet linked at 1000 Mbps<br>connection speed |

| D10             | ENET_LED_LINK100  | Green LED. Illuminates to indicate<br>Ethernet linked at 100 Mbps connection<br>speed  |

| D11             | ENET_LED_LINK10   | Green LED. Illuminates to indicate<br>Ethernet linked at 10 Mbps connection<br>speed   |

| D6              | OVERTEMP          | Amber LED. Intel Stratix 10 FPGA over temperature indicator                            |

This development board includes several different kinds of setup elements. This section describes the following setup elements:

- JTAG Chain Device Removal Switch •

- Program Select Pushbutton

- MAX V Reset Pushbutton

- **CPU Reset Pushbutton**

### **JTAG Chain Device Removal Switch**

The JTAG chain connects the Intel Stratix 10 TX FPGA, the MAX V CPLD, FMC in a chain, with the option to selectively bypass each JTAG node by four dip switch setting.

### **Program Select Pushbutton**

If AvST configuration mode is selected, after a POWER-ON or RESET (reconfiguration) event, the MAX V configures the Intel Stratix 10 TX FPGA if configuration mode is AvST mode with either the FACTORY POF or a USERDEFINED POF depending on FACTORY\_LOAD setting. The setting of the PGMSEL bit is selected by the PGMSEL pushbutton. Pressing this pushbutton and observing the program LEDs (FACTORY or USER) dictates the program selection. Then, the PGM CONFIG pushbutton must be pressed to load the program.

### **MAX V Reset Pushbutton**

This pushbutton is the development board's Master Reset. This pushbuttton is connected to the MAX V CPLD (MAX\_RESETn pin) that is used for AvST configuration. When this button is pressed, the MAX V CPLD initiates a reloading of the stored image from flash memory using AvST configuration mode. The image that is reloaded depends on the PGMSEL setting.

### **CPU Reset Pushbutton**

This pushbutton is the Nios II CPU Reset. This button is connected to a Intel Stratix 10 TX FPGA global signal input pin and can be used by Nios II implementations as a dedicated CPU Reset button. This button is also connected to the MAX V CPLD so that the FPGA device can be reset right after its configuration with AvST mode.

### 4.6. User Input-Output Components

This section describes the user I/O interface to the FPGA. The following I/O elements are described:

- User-defined Pushbuttons

- User-defined DIP Switches

- User-defined LEDs

### **User-Defined Pushbuttons**

This development kit includes 4 user-defined pushbuttons and 4 system pushbuttons that allow you to interact with the Intel Stratix 10 TX FPGA. When you press and hold down the pushbutton, the device pin is set to logic 0; when you release the pushbutton, the device pin is set to logic 1. There is no board-specific function for these general user pushbuttons.

The table below lists the pushbuttons, schematic signal names and their corresponding Intel Stratix 10 TX FPGA device pin numbers.

| Board Reference | Schematic Signal Name | Description       | Intel Stratix 10 TX Pin<br>Number |

|-----------------|-----------------------|-------------------|-----------------------------------|

| S1              | USER_PB0              | User Pushbutton   | N19                               |

| S2              | USER_PB1              | User Pushbutton   | P19                               |

| S3              | USER_PB2              | User Pushbutton   | L23                               |

| S4              | USER_PB3              | User Pushbutton   | M23                               |

| S5              | PGM_SEL               | System Pushbutton | N/A                               |

| S6              | PGM_CONFIG            | System Pushbutton | N/A                               |

| S7              | MAX_RESETn            | System Pushbutton | N/A                               |

| S8              | CPU_RESETn            | System Pushbutton | R35                               |

### Table 8. User-Defined Pushbuttons

### **User-Defined DIP Switch**

Board reference **SW4** and **SW5** are two 4-pin DIP switches. The switches are userdefined and provides additional FPGA input control. When the switch is in the OPEN or OFF position, a logic **1** is selected. When the switch is in the CLOSED or ON position, a logic **0** is selected. There is no board-specific function for these switches.

The table below lists the schematic signal names of each DIP switch and their corresponding Intel Stratix 10 TX FPGA pin numbers.

### Table 9. User-Defined DIP Switch

| Board Reference | Schematic Signal Name | Intel Stratix 10 TX Pin Number |

|-----------------|-----------------------|--------------------------------|

| SW4.4           | USER_DIP0             | G23                            |

| SW4.3           | USER_DIP1             | G24                            |

| SW4.2           | USER_DIP2             | К23                            |

| SW4.1           | S10_UNLOCK            | К22                            |

### **User-Defined LEDs**

The development board includes 8 user-defined LEDs. Board references **D12** through **D19** are user LEDs that allow status and debugging signals to be driven to the LEDs from the designs loaded into the Intel Stratix 10 TX FPGA device. The LEDs illuminate when a logic **0** is driven and turns off when a logic **1** is driven. There is no boardspecific function for these LEDs.

The table below lists the user-defined schematic signal names and their corresponding Intel Stratix 10 TX FPGA device pin numbers.

#### Table 10. **User-Defined LEDs**

| Board Reference | Schematic Signal Name | Intel Stratix 10 TX Pin Number |

|-----------------|-----------------------|--------------------------------|

| D12             | USER_LED0             | G31                            |

| D13             | USER_LED1             | H31                            |

| D14             | USER_LED2             | G32                            |

| D15             | USER_LED3             | G33                            |

## 4.7. Clocks

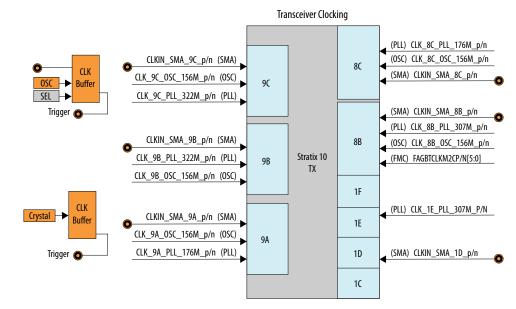

### 4.7.1. Transceiver Dedicated Clocks

Dedicated clocking scheme that is implemented on the Intel Stratix 10 TX transceiver signal integrity development board allows different protocols to run simultaneously by the Intel Stratix 10 TX FPGA.

Differential clock sources are provided from an  $I^2C$  programmable oscillator or PLL to the dedicated REFCLK input pins of transceiver blocks on both sides of the FPGA. The default frequencies for the oscillator and PLL at startup are:

- 156.25 MHz (Y1 and U3)

- 322.265625 MHz (U3) •

- 176.5625 MHz (U3) ٠

- 307.2 MHz (U3)

The default frequencies can be overridden and a different frequency can be programmed into the oscillators and PLLs for support of other protocols.

Note: Programmed frequencies are lost upon a board power down. Oscillator and PLL frequencies return to their default frequency upon power up.

> The oscillator or PLL provides a differential LVDS trigger output to SMA connectors for scope or other laboratory equipment triggering purposes.

In addition to the two oscillators and PLLs, each transceiver tile have dedicated differential REFCLK input from a pair of SMA connectors to allow use of laboratory equipment clock generators as the transceiver clock source.

The six inputs below connect directly to the transceiver clock inputs:

- J34/J35 SMA connector direct connection to H-tile block

- J36/J37 SMA connector direct connection to E-tile 8B block

- J38/J39 SMA connector direct connection to E-tile 8C block

- J40/J41 SMA connector direct connection to E-tile 9A block

- J42/J43 SMA connector direct connection to E-tile 9B block

- J44/J45 SMA connector direct connection to E-tile 9C block

The figure below shows the dedicated transceiver clocks that are implemented on the Intel Stratix 10 TX FPGA development kit.

### Figure 7. Transceiver Clocks

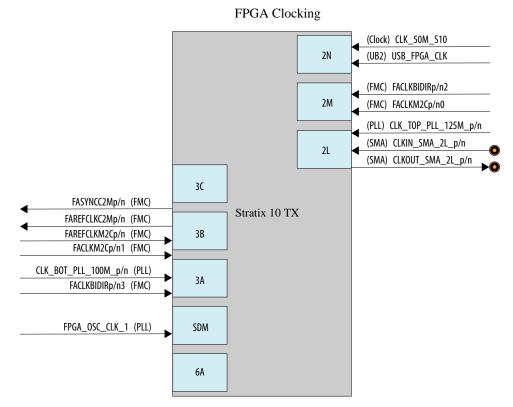

### 4.7.2. General-Purpose Clocks

In addition to transceiver dedicated clocks, five other clock sources are provided to the FPGA Global CLK inputs for general FPGA design as shown in the figure below.

The usage of these clocks is as follows:

- 50 MHz oscillator through an SL18860 buffer for Nios II applications.

USB\_FPGA\_CLK drives from on-board Intel FPGA Download Cable II circuit.

- External differential clock source from SMA connectors. Dedicated differential output clock to SMA connectors.

- Three clock outputs are provided from two Si5341 PLLs:

- CLK\_BOT\_PLL\_100M\_P/N: 100 MHz LVDS Standard

- CLK\_TOP\_PLL\_125M\_P/N: 125 MHz LVDS Standard

- FPGA\_OSC\_CLK\_1: 125 MHz 1.8V CMOS Standard

- Clocks from FMC+ daughter card

#### Figure 8. **FPGA Clocks**

### 4.7.3. Embedded Intel FPGA Download Cable II Clock

A 24 MHz crystal is dedicated for the embedded Intel FPGA Download Cable II circuit. The crystal is used to clock the Cypress CY7C68013A USB2 PHY device.

### 4.8. Transceiver Channels

The Intel Stratix 10 TX transceiver signal integrity development kit dedicates 90 channels from both the left and right sides of the device. Transceiver channels are allocated as shown in the table below.

Figure 9. **Transceiver Channels Block Diagram**

4. Development Kit Components 683591 | 2019.09.27

# intel

### Table 11. Transceiver Channels

| Transceiver Channel                           | Data Rate                     | Number of Channels |

|-----------------------------------------------|-------------------------------|--------------------|

| 2.4mm RF channel                              | NRZ 28.9 Gbps or PAM4 58 Gbps | 2                  |

| MXP connector A                               | NRZ 28.9 Gbps or PAM4 58 Gbps | 4                  |

| MXP connector B                               | NRZ 28.9 Gbps or PAM4 58 Gbps | 4                  |

| QSFPDD 1x1 Optical Interface (Left and Right) | NRZ 28.9 Gbps or PAM4 58 Gbps | 16                 |

|                                               |                               | continued          |

| Transceiver Channel          | Data Rate                     | Number of Channels |

|------------------------------|-------------------------------|--------------------|

| QSFPDD 1x2 Optical Interface | NRZ 28.9 Gbps or PAM4 58 Gbps | 16                 |

| QSFPDD 2x1 Optical Interface | NRZ 28.9 Gbps or PAM4 58 Gbps | 16                 |

| FMC+ A Interface             | 17.4 Gbps or 28.3 Gbps        | 24                 |

### Table 12.2.4 mm RF Interface

| Signal Net Name        | Description          |

|------------------------|----------------------|

| SMAA_TXp/n, SMAB_TXp/n | 2.4mm RF Transmitter |

| SMAA_RXp/n, SMAB_RXp/n | 2.4mm RF Receiver    |

### Table 13. MXP Interface

| Signal Net Name | Description       |

|-----------------|-------------------|

| MXPA_TXp/n[3:0] | MXP A Transmitter |

| MXPA_RXp/n[3:0] | MXP A Receiver    |

| MXPB_TXp/n[3:0] | MXP B Transmitter |

| MXPB_RXp/n[3:0] | MXP B Receiver    |

### Table 14. Optical Modules Interface

| Signal Net Name         | Description           |

|-------------------------|-----------------------|

| QSFPDD2x1_TXp/n[15:0]   | QSFPDD2x1 Transmitter |

| QSFPDD2x1_RXp/n[15:0]   | QSFPDD2x1 Receiver    |

| QSFPDD1x2_TXp/n[15:0]   | QSFPDD1x2 Transmitter |

| QSFPDD1x2_RXp/n[15:0]   | QSFPDD1x2 Receiver    |

| QSFPDD1x1_TXp/n[7:0]    | QSFPDD1x1 Transmitter |

| QSFPDD1x1_RXp/n[7:0]    | QSFPDD1x1 Receiver    |

| QSFPDD1x1_1_TXp/n [7:0] | QSFPDD1x1 Transmitter |

| QSFPDD1x1_1_RXp/n [7:0] | QSFPDD1x1 Receiver    |

### Table 15. FMC+ Interface

| Signal Net Name | Description            |  |

|-----------------|------------------------|--|

| FAC2Mp/n[23:0]  | FMC+ A GXB Transmitter |  |

| FAM2Cp/n[23:0]  | FMC+ A GXB Receiver    |  |

### **4.9. Communication Ports**

The Intel Stratix 10 TX transceiver signal integrity development kit supports a 10/100/1000 BASE-T Ethernet connection using a Marvell 88E1111 PHY device and the Intel Triple-Speed Ethernet Megacore MAC function. The device is an auto-negotiating Ethernet PHY with an SGMII interface to the FPGA.

The Intel Stratix 10 GX FPGA device can communicate with the LVDS interfaces at up to 1.25 Gbps. The MAC function is provided in the FPGA for typical networking applications. The Marvell 88E1111 PHY uses 2.5 V and 1.2 V power rails and requires a 25-MHz reference clock driven from a dedicated oscillator. It interfaces to an RJ-45 connector with internal magnetics that are used for driving copper lines with Ethernet traffic.

### Table 16. Ethernet PHY Pin Assignments

| Schematic Signal Name | Marvell 88E1111 (U23) PHY Pin<br>Number | Description                      |

|-----------------------|-----------------------------------------|----------------------------------|

| ENET_LED_LINK1000     | 60/73                                   | 1000 Mb link LED                 |

| ENET_LED_LINK100      | 74                                      | 100 Mb link LED                  |

| ENET_LED_LINK10       | 59/76                                   | 10 Mb link LED                   |

| ENET_LED_TX           | 68                                      | TX data active LED               |

| ENET_LED_RX           | 69                                      | RX data active LED               |

| ENET_SGMII_TX_P       | 82                                      | SGMII transmit                   |

| ENET_SGMII_TX_N       | 81                                      | SGMII transmit                   |

| ENET_SGMII_RX_P       | 77                                      | SGMII receive                    |

| ENET_SGMII_RX_N       | 75                                      | SGMII receive                    |

| ENET_XTAL_25MHZ       | 55                                      | 25 MHz clock                     |

| ENET_T_INTn           | 23                                      | Management bus interrrupt        |

| ENET_RSET             | 30                                      | Device reset                     |

| MDIO_T                | 24                                      | Management bus data input/output |

| MDC_T                 | 25                                      | Management bus data clock        |

| MDI_P0                | 29                                      | Management bus data              |

| MDI_N0                | 31                                      | Management bus data              |

| MDI_P1                | 33                                      | Management bus data              |

| MDI_N1                | 34                                      | Management bus data              |

| MDI_P2                | 39                                      | Management bus data              |

| MDI_N2                | 41                                      | Management bus data              |

| MDI_P3                | 42                                      | Management bus data              |

| MDI_N3                | 43                                      | Management bus data              |

### 4.10. Flash Memory

### 4.10.1. Parallel NOR Flash Memory

The Intel Stratix 10 TX Transceiver Signal Integrity Development Kit has two 1-Gbit CFI compatible asynchronous flash device for non-volatile storage of the FPGA configuration data, board information, test application data and user code space.

Two flash devices are implemented to achieve a 16-bit wide data bus at 16 bits each per device. Both MAX V CPLD and Intel Stratix 10 TX FPGA can access this flash device.

MAX V CPLD accesses are for AvST configuration of the FPGA at power-on and board reset events. It uses the PFL Megafunction.

#### Table 17. Memory Map of the first 1G NOR Flash Memory (x16)

| Block Description | Size (KB) | Address Range             |

|-------------------|-----------|---------------------------|

| Reserved          | 512       | 0x0750.0000 - 0x0757.FFFF |

| Reserved          | 14336     | 0x0670.0000 - 0x074F.FFFF |

| Reserved          | 8192      | 0x05F0.0000 - 0x06FF.FFFF |

| Reserved          | 8192      | 0x0570.0000 - 0x05EF.FFFF |

| User hardware1    | 44032     | 0x02C0.0000 - 0x056F.FFFF |

| User hardware0    | 44032     | 0x0010.0000 - 0x02BF.FFFF |

| PFL option bits   | 256       | 0x000C.0000 - 0x000F.FFFF |

| Reserved          | 256       | 0x0008.0000 - 0x000B.FFFF |

| Reserved          | 256       | 0x0004.0000 - 0x0007.FFFF |

| Reserved          | 256       | 0x0000.0000 - 0x0003.FFFF |

#### Table 18. Memory Map of the second 1G NOR Flash Memory (x16)

| Block Description | Size (KB) | Address Range             |

|-------------------|-----------|---------------------------|

| User hardware2    | 44032     | 0x0010.0000 - 0x02BF.FFFF |

| PFL option bits   | 256       | 0x000C.0000 - 0x000F.FFFF |

| Reserved          | 256       | 0x0008.0000 - 0x000B.FFFF |

| Reserved          | 256       | 0x0004.0000 - 0x0007.FFFF |

| Reserved          | 256       | 0x0000.0000 - 0x0003.FFFF |