## **General Description**

The DS1858 dual temperature-controlled nonvolatile (NV) variable resistors with three monitors consists of two  $50k\Omega$  256-position linear variable resistors, three analog monitor inputs (MON1, MON2, MON3), and a direct-to-digital temperature sensor. The device provides an ideal method for setting and temperature-compensating bias voltages and currents in control applications using minimal circuitry. The variable resistor settings are stored in EEPROM memory and can be accessed over the 2-wire serial bus.

### **Applications**

**Optical Transceivers Optical Transponders** Instrumentation and Industrial Controls **RF Power Amps** Diagnostic Monitoring

#### **Features**

- **♦** Five Total Monitored Channels (Temperature, V<sub>CC</sub>, MON1, MON2, MON3)

- ♦ Three External Analog Inputs (MON1, MON2, MON3)

- ♦ Internal Direct-to-Digital Temperature Sensor

- ♦ Two 50kΩ, Linear, 256-Position, Nonvolatile **Temperature-Controlled Variable Resistors**

- ♦ Resistor Settings Changeable Every 2°C

- **♦** Access to Monitoring and ID Information **Configurable with Separate Device Addresses**

- ♦ 2-Wire Serial Interface

- **♦ Two Buffers with TTL/CMOS-Compatible Inputs** and Open-Drain Outputs

- ♦ Operates from a 3.3V or 5V Supply

- ♦ SFF-8472 Compatible

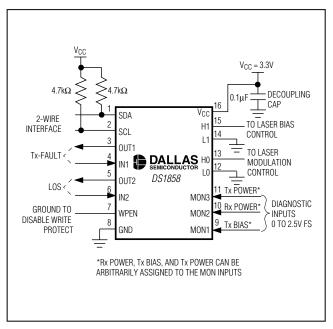

## **Typical Operating Circuit**

## **Ordering Information**

| PART            | TEMP RANGE     | PIN-PACKAGE                 |

|-----------------|----------------|-----------------------------|

| DS1858E-050     | -40°C to +95°C | 16 TSSOP                    |

| DS1858E-050+    | -40°C to +95°C | 16 TSSOP                    |

| DS1858E-050/T&R | -40°C to +95°C | 16 TSSOP<br>(Tape-and-Reel) |

| DS1858B-050     | -40°C to +95°C | 16-Ball CSBGA               |

<sup>+</sup>Denotes lead-free package.

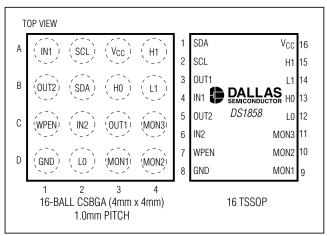

## **Pin Configurations**

#### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on VCC Relative to Ground   | 0.5V to +6.0V                  |

|-------------------------------------|--------------------------------|

| Voltage on Inputs Relative          |                                |

| to Ground*                          | 0.5V to V <sub>CC</sub> + 0.5V |

| Voltage on Resistor Inputs Relative |                                |

| to Ground*                          | 0.5V to V <sub>CC</sub> + 0.5V |

| Current into Resistors        | 5mA            |

|-------------------------------|----------------|

| Operating Temperature Range   | 40°C to +95°C  |

| Programming Temperature Range |                |

| Storage Temperature Range     | 55°C to +125°C |

| Soldering Temperature         |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +95^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                        | SYMBOL           | CONDITIONS    | MIN       | TYP MAX               | UNITS |

|----------------------------------|------------------|---------------|-----------|-----------------------|-------|

| Supply Voltage                   | Vcc              | (Note 1)      | 3.0       | 5.5                   | V     |

| Input Logic 1 (SDA, SCL, WPEN)   | VIH              | (Note 2)      | 0.7 x Vcc | V <sub>CC</sub> + 0.3 | V     |

| Input Logic 0 (SDA, SCL, WPEN)   | VIL              | (Note 2)      | -0.3      | 0.3 x V <sub>CC</sub> | V     |

| Resistor Inputs (L0, L1, H0, H1) |                  |               | -0.3      | V <sub>CC</sub> + 0.3 | V     |

| Resistor Current                 | I <sub>RES</sub> |               | -3        | +3                    | mA    |

| Lineart Legis Levels (INIA INIO) | VIH              | Input logic 1 | 1.5       |                       | V     |

| Input Logic Levels (IN1, IN2)    | VIL              | Input logic 0 |           | 0.9                   | V     |

#### DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = 3.0V to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted.)

| PARAMETER                                 | SYMBOL           | CONDITIONS                                                       | MIN    | TYP    | MAX    | UNITS |

|-------------------------------------------|------------------|------------------------------------------------------------------|--------|--------|--------|-------|

| Supply Current                            | Icc              | (Note 3)                                                         |        | 1      | 2      | mA    |

| Input Leakage                             | Ι <sub>Ι</sub> L |                                                                  | -1     |        | +1     | μΑ    |

| Input Current each I/O Pin                |                  | 0.4 x V <sub>CC</sub> < V <sub>I/O</sub> < 0.9 x V <sub>CC</sub> | -10    |        | +10    | μΑ    |

| O. d. | V <sub>OL1</sub> | 3mA sink current                                                 | 0      |        | 0.4    | \ /   |

| Low-Level Output Voltage (SDA)            | V <sub>OL2</sub> | 6mA sink current                                                 | 0      |        | 0.6    | V     |

| Full-Scale Input (MON1, MON2, MON3)       |                  | (Note 4)                                                         | 2.4875 | 2.5    | 2.5125 | V     |

| Full-Scale V <sub>CC</sub> Monitor        |                  | (Note 5)                                                         | 6.5208 | 6.5536 | 6.5864 | V     |

| I/O Capacitance                           | C <sub>I/O</sub> |                                                                  |        |        | 10     | рF    |

| WPEN Pullup                               | RWPEN            |                                                                  | 40     | 65     | 100    | kΩ    |

| OLITA OLITO Valtaria                      | V <sub>OL1</sub> | 3mA sink current                                                 | 0      |        | 0.4    | V     |

| OUT1, OUT2 Voltage                        | V <sub>OL2</sub> | 6mA sink current                                                 | 0      |        | 0.6    | V     |

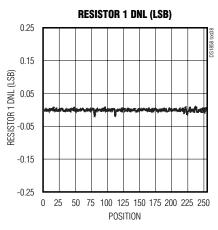

| Digital Power-On Reset                    | POD              |                                                                  | 1.0    |        | 2.2    | V     |

| Analog Power-On Reset                     | POA              |                                                                  | 2.0    |        | 2.6    | V     |

<sup>\*</sup>Not to exceed 6.0V.

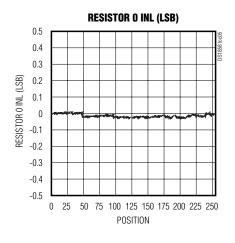

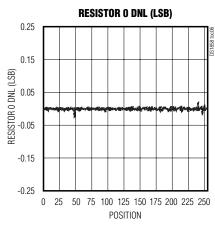

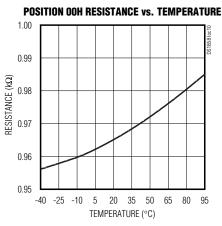

#### **ANALOG RESISTOR CHARACTERISTICS**

(V<sub>CC</sub> = 3.0V to 5.5V, T<sub>A</sub> =  $-40^{\circ}$ C to  $+95^{\circ}$ C, unless otherwise noted.)

| PARAMETER               | SYMBOL | CONDITIONS             | MIN | TYP | MAX  | UNITS  |

|-------------------------|--------|------------------------|-----|-----|------|--------|

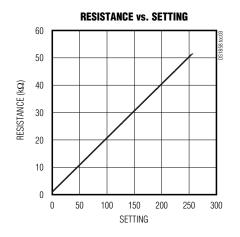

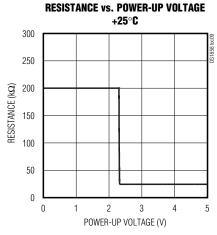

| Position 00h Resistance |        | T <sub>A</sub> = +25°C | 0.7 | 1.0 | 1.25 | kΩ     |

| Position FFh Resistance |        | T <sub>A</sub> = +25°C | 40  | 50  | 60   | kΩ     |

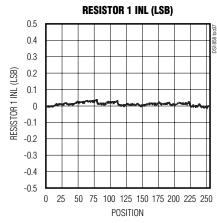

| Absolute Linearity      |        | (Note 6)               | -2  |     | +2   | LSB    |

| Relative Linearity      |        | (Note 7)               | -1  |     | +1   | LSB    |

| Temperature Coefficient |        | (Note 8)               |     | 50  |      | ppm/°C |

#### **ANALOG VOLTAGE MONITORING**

(V<sub>CC</sub> = 3.0V to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted.)

| PARAMETER                                      | SYMBOL | CONDITIONS | MIN | TYP  | MAX | UNITS                |

|------------------------------------------------|--------|------------|-----|------|-----|----------------------|

| Input Resolution                               | ΔVMON  |            |     | 610  |     | μV                   |

| Supply Resolution                              | ΔVcc   |            |     | 1.6  |     | mV                   |

| Input/Supply Accuracy                          | Acc    |            |     | 0.25 | 0.5 | % FS<br>(full scale) |

| Update Rate for MON1, MON2, MON3, Temp, or VCC | tframe |            |     | 25   | 36  | ms                   |

#### **DIGITAL THERMOMETER**

( $V_{CC} = 3.0V$  to 5.5V,  $T_A = -40$ °C to +95°C, unless otherwise noted.)

| PARAMETER         | SYMBOL           | CONDITIONS     | TYP | MAX  | UNITS |

|-------------------|------------------|----------------|-----|------|-------|

| Thermometer Error | T <sub>ERR</sub> | -40°C to +95°C |     | ±3.0 | °C    |

#### AC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = 3.0V to 5.5V,  $T_A$  = -40°C to +95°C, unless otherwise noted.)

| PARAMETER                         | SYMBOL           | CONDITIONS                      | MIN TYP                | MAX     | UNITS |  |

|-----------------------------------|------------------|---------------------------------|------------------------|---------|-------|--|

| COL Clask Francisco               | 6                | Fast mode (Note 9)              | 0                      | 400     | Id I= |  |

| SCL Clock Frequency               | fscl             | Standard mode (Note 9)          | 0                      | 100     | kHz   |  |

| Bus Free Time Between STOP and    | +                | Fast mode (Note 9)              | 1.3                    |         |       |  |

| START Condition                   | t <sub>BUF</sub> | Standard mode (Note 9)          | 4.7                    |         | μs    |  |

| Hold Time (Repeated)              | tup 074          | Fast mode (Notes 9, 10)         | 0.6                    |         |       |  |

| START Condition                   | thd:Sta          | Standard mode (Notes 9, 10)     | 4.0                    |         | μs    |  |

| Low Period of SCL Clock           | t. 0.11          | Fast mode (Note 9)              | 1.3                    |         |       |  |

| Low Period of SCL Clock           | tLOW             | Standard mode (Note 9)          | 4.7                    |         | μs    |  |

| Lligh David of COL Clask          |                  | Fast mode (Note 9)              | 0.6                    |         | μs    |  |

| High Period of SCL Clock          | tHIGH            | Standard mode (Note 9)          | 4.0                    |         |       |  |

| Data Hold Time                    | tup p.e.         | Fast mode (Notes 9, 11, 12)     | 0                      | 0.9     |       |  |

| Data Hold Time                    | thd:dat          | Standard mode (Notes 9, 11, 12) | 0                      |         | μs    |  |

| Data Catura Tima                  |                  | Fast mode (Note 9)              | 100                    |         |       |  |

| Data Setup Time                   | tsu:dat          | Standard mode (Note 9)          | 250                    |         | ns    |  |

| Start Satura Tima                 | to o             | Fast mode (Note 9)              | 0.6                    |         |       |  |

| Start Setup Time                  | tsu:sta          | Standard mode (Note 9)          | 4.7                    |         | μs    |  |

| Rise Time of Both SDA and SCL     | to               | Fast mode (Note 13)             | 20 + 0.1C <sub>B</sub> | 300     | 200   |  |

| Signals                           | t <sub>R</sub>   | Standard mode (Note 13)         | 20 + 0.1C <sub>B</sub> | 1000    | ns    |  |

| Fall Time of Both SDA and SCL     | +                | Fast mode (Note 13)             | 20 + 0.1C <sub>B</sub> | 300     | 20    |  |

| Signals                           | tF               | Standard mode (Note 13)         | 20 + 0.1C <sub>B</sub> | 300     | ns    |  |

| Cotup Time for STOD Condition     | to 070           | Fast mode                       | 0.6                    |         |       |  |

| Setup Time for STOP Condition     | tsu:sto          | Standard mode                   | 4.0                    |         | μs    |  |

| Capacitive Load for Each Bus Line | СВ               | B (Note 13) 400                 |                        | 400     | рF    |  |

| EEPROM Write Time                 | tw               | (Note 14)                       | 10                     | <u></u> | ms    |  |

- **Note 1:** All voltages are referenced to ground.

- Note 2: I/O pins of fast-mode devices must not obstruct the SDA and SCL lines if V<sub>CC</sub> is switched off.

- Note 3: SDA and SCL are connected to V<sub>CC</sub> and all other input signals are connected to well-defined logic levels.

- Note 4: The maximum voltage the MON inputs will read is approximately 2.5V, even if the voltage on the inputs is greater than 2.5V.

- Note 5: This voltage is defining the maximum range of the analog-to-digital converter voltage and not the maximum V<sub>CC</sub> voltage.

- **Note 6:** Absolute linearity is the difference of measured value from expected value at DAC position. The expected value is a straight line from measured minimum position to measured maximum position.

- **Note 7:** Relative linearity is the deviation of an LSB DAC setting change vs. the expected LSB change. The expected LSB change is the slope of the straight line from measured minimum position to measured maximum position.

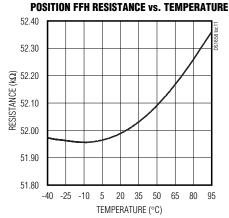

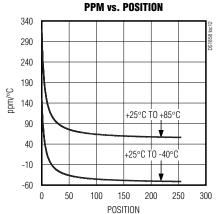

- Note 8: See the Typical Operating Characteristics.

- Note 9: A fast-mode device can be used in a standard-mode system, but the requirement t<sub>SU:DAT</sub> > 250ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>RMAX</sub> + t<sub>SU:DAT</sub> = 1000ns + 250ns = 1250ns before the SCL line is released.

## AC ELECTRICAL CHARACTERISTICS (continued)

( $V_{CC} = 3.0V$  to 5.5V,  $T_A = -40$ °C to +95°C, unless otherwise noted.)

- **Note 10:** After this period, the first clock pulse is generated.

- Note 11: The maximum t<sub>HD:DAT</sub> only has to be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

- Note 12: A device must internally provide a hold time of at least 300ns for the SDA signal (see the V<sub>IH MIN</sub> of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- Note 13: C<sub>B</sub>—total capacitance of one bus line, timing referenced to 0.9 x V<sub>CC</sub> and 0.1 x V<sub>CC</sub>.

- Note 14: EEPROM write begins after a STOP condition occurs.

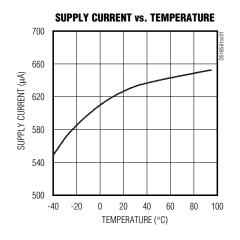

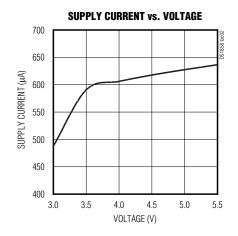

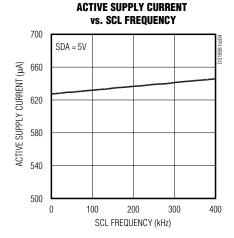

### **Typical Operating Characteristics**

$(V_{CC} = 5.0V, T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V_{CC} = 5.0V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Descriptions**

| PIN | BALL | NAME | FUNCTION                                                                                                                                                                                                                                                                                                  |

|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | B2   | SDA  | 2-Wire Serial Data I/O Pin. This pin is for serial data transfer to and from the device.                                                                                                                                                                                                                  |

| 2   | A2   | SCL  | 2-Wire Serial Clock Input. The serial clock input is used to clock data into and out of the device.                                                                                                                                                                                                       |

| 3   | СЗ   | OUT1 | Open-Drain Buffer Output                                                                                                                                                                                                                                                                                  |

| 4   | A1   | IN1  | TTL/CMOS-Compatible Input to Buffer                                                                                                                                                                                                                                                                       |

| 5   | B1   | OUT2 | Open-Drain Buffer Output                                                                                                                                                                                                                                                                                  |

| 6   | C2   | IN2  | TTL/CMOS-Compatible Input to Buffer                                                                                                                                                                                                                                                                       |

| 7   | C1   | WPEN | Write Protect Enable. The device is not write protected if WPEN is connected to ground. This pin has an internal pullup (RwPEN). See Table 6.                                                                                                                                                             |

| 8   | D1   | GND  | Ground                                                                                                                                                                                                                                                                                                    |

| 9   | D3   | MON1 | External Analog Input                                                                                                                                                                                                                                                                                     |

| 10  | D4   | MON2 | External Analog Input                                                                                                                                                                                                                                                                                     |

| 11  | C4   | MON3 | External Analog Input                                                                                                                                                                                                                                                                                     |

| 12  | D2   | LO   | Low-End Resistor 0 Terminal. It is not required that the low-end terminals be connected to a potential less than the high-end terminals of the corresponding resistor. Voltage applied to any of the resistor terminals cannot exceed the power-supply voltage, V <sub>CC</sub> , or go below ground.     |

| 13  | В3   | HO   | High-End Resistor 0 Terminal. It is not required that the high-end terminals be connected to a potential greater than the low-end terminals of the corresponding resistor. Voltage applied to any of the resistor terminals cannot exceed the power-supply voltage, V <sub>CC</sub> , or go below ground. |

| 14  | B4   | L1   | Low-End Resistor 1 Terminal                                                                                                                                                                                                                                                                               |

| 15  | A4   | H1   | High-End Resistor 1 Terminal                                                                                                                                                                                                                                                                              |

| 16  | A3   | Vcc  | Supply Voltage                                                                                                                                                                                                                                                                                            |

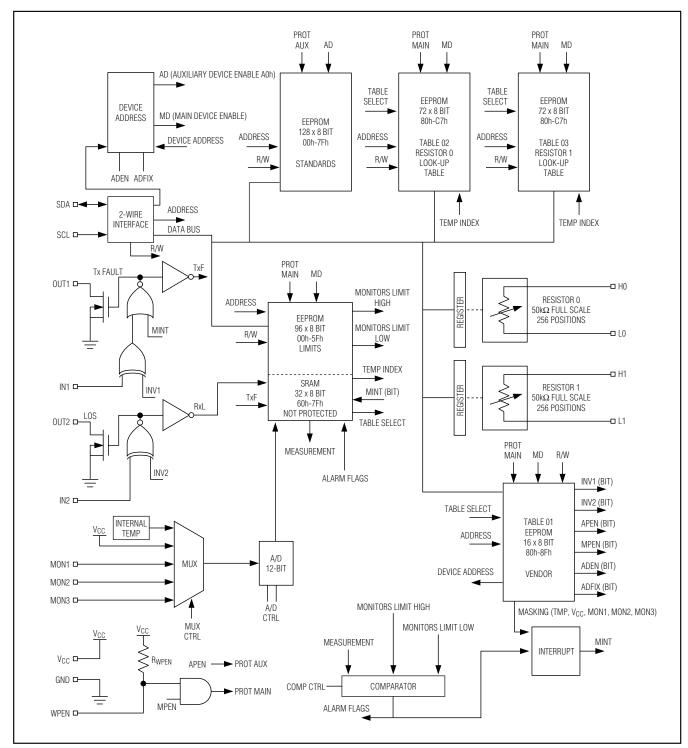

### **Detailed Description**

The user can read the registers that monitor the V<sub>CC</sub>, MON1, MON2, MON3, and temperature analog signals. After each signal conversion, a corresponding bit is set that can be monitored to verify that a conversion has occurred. The signals also have alarm flags that notify the user when the signals go above or below the user-defined value. Interrupts can also be set for each signal.

The position values of each resistor can be independently programmed. The user can assign a unique value to each resistor for every  $2^{\circ}$ C increment over the  $-40^{\circ}$ C to  $+102^{\circ}$ C range.

Two buffers are provided to convert logic-level inputs into open-drain outputs. Typically these buffers are used to implement transmit (Tx) fault and loss-of-signal (LOS) functionality. Additionally, OUT1 can be asserted in the event that one or more of the monitored values go beyond user-defined limits.

Figure 1. DS1858 Block Diagram

**Table 1. Scales for Monitor Channels**

| SIGNAL      | +FS<br>SIGNAL | +FS<br>(hex) | -FS<br>SIGNAL | -FS<br>(hex) |

|-------------|---------------|--------------|---------------|--------------|

| Temperature | 127.996°C     | 7FFF         | -128°C        | 8000         |

| Vcc         | 6.55V         | FFFF         | OV            | 0000         |

| MON1        | 2.5V          | FFFF         | OV            | 0000         |

| MON2        | 2.5V          | FFFF         | OV            | 0000         |

| MON3        | 2.5V          | FFFF         | OV            | 0000         |

### **Table 2. Signal Comparison**

| SIGNAL      | FORMAT           |

|-------------|------------------|

| Vcc         | Unsigned         |

| MON1        | Unsigned         |

| MON2        | Unsigned         |

| MON3        | Unsigned         |

| Temperature | Two's complement |

#### **Monitored Signals**

Each signal (V<sub>CC</sub>, MON1, MON2, MON3, and temperature) is available as a 16-bit value with 12-bit accuracy (left-justified) over the serial bus. See Table 1 for signal scales and Table 2 for signal format. The four LSBs should be masked when calculating the value.

The signals are updated every frame rate (tframe) in a round-robin fashion.

The comparison of all five signals with the high and low user-defined values are done automatically. The corresponding flags are set to 1 within a specified time of the occurrence of an out-of-limit condition.

### Calculating Signal Values

The LSB =  $100\mu V$  for  $V_{CC}$ , and the LSB =  $38.147\mu V$  for the MON signals.

## Monitor/Vcc Bit Weights

| MSB | 2 <sup>15</sup> | 214            | 213 | 212 | 211 | 210 | 2 <sup>9</sup> | 28 |

|-----|-----------------|----------------|-----|-----|-----|-----|----------------|----|

| LSB | 27              | 2 <sup>6</sup> | 25  | 24  | 23  | 22  | 21             | 20 |

To calculate the value of  $V_{CC}$ , convert the unsigned 16-bit value to decimal and multiply by  $100\mu V$ .

## **VCC Conversion Examples**

| MSB (BIN) | LSB (BIN) | VOLTAGE (V) |

|-----------|-----------|-------------|

| 10000000  | 10000000  | 3.29        |

| 11000000  | 11111000  | 4.94        |

## Table 3. Look-up Table Address for Corresponding Temperature Values

| TEMPERATURE | CORRESPONDING LOOK-UP TABLE ADDRESS |

|-------------|-------------------------------------|

| <-40°C      | 80h                                 |

| -40°C       | 80h                                 |

| -38°C       | 81h                                 |

| -36°C       | 82h                                 |

| -34°C       | 83h                                 |

| _           | _                                   |

| +98°C       | C5h                                 |

| +100°C      | C6h                                 |

| +102°C      | C7h                                 |

| >+102°C     | C7h                                 |

## **Monitor Conversion Example**

| MSB (BIN) | LSB (BIN) | VOLTAGE (V) |

|-----------|-----------|-------------|

| 11000000  | 00000000  | 1.875       |

| 10000000  | 10000000  | 1.255       |

To calculate the value of MON1, MON2, or MON3 convert the unsigned 16-bit value to decimal and multiply by 38.147µV.

To calculate the value of the temperature, treat the two's complement value binary number as an unsigned binary number, then convert to decimal and divide by 256. If the result is greater than or equal to 128, then subtract 256 from the result.

Temperature: high byte: -128°C to +127°C signed; low byte: 1/256°C.

### **Temperature Bit Weights**

| S   | 2 <sup>6</sup> | 25  | 24  | 23  | 22  | 21  | 20  |

|-----|----------------|-----|-----|-----|-----|-----|-----|

| 2-1 | 2-2            | 2-3 | 2-4 | 2-5 | 2-6 | 2-7 | 2-8 |

## **Temperature Conversion Examples**

| MSB (BIN) | LSB (BIN) | TEMPERATURE (°C) |

|-----------|-----------|------------------|

| 01000000  | 00000000  | 64               |

| 01000000  | 00001111  | 64.059           |

| 01011111  | 00000000  | 95               |

| 11110110  | 00000000  | -10              |

| 11011000  | 00000000  | -40              |

## **Table 4. ADEN Address Configuration**

| ADEN<br>(ADDRESS<br>ENABLE) | NO. OF SEPARATE<br>DEVICE<br>ADDRESSES | ADDITIONAL<br>INFORMATION |

|-----------------------------|----------------------------------------|---------------------------|

| 0                           | 2                                      | See Figure 2              |

| 1                           | 1 (Main Device only)                   | See Figure 3              |

**Table 5. ADEN and ADFIX Bits**

| ADEN | ADFIX | AUXILIARY<br>ADDRESS | MAIN ADDRESS              |

|------|-------|----------------------|---------------------------|

| 0    | 0     | A0h                  | A2h                       |

| 0    | 1     | A0h                  | EEPROM<br>(Table 01, 8Ch) |

| 1    | 0     | N/A                  | A2h                       |

| 1    | 1     | N/A                  | EEPROM<br>(Table 01, 8Ch) |

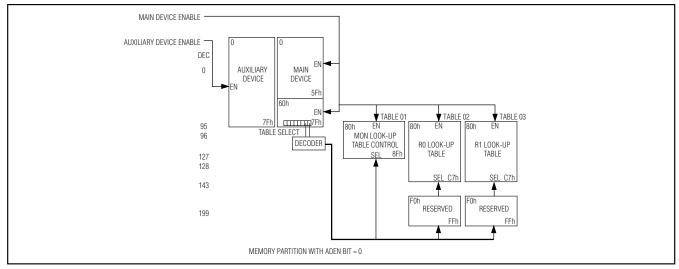

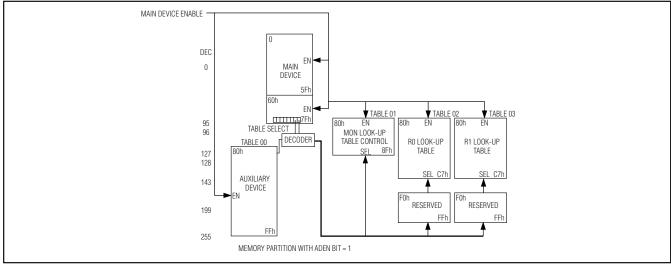

Figure 2. Memory Organization, ADEN = 0

Figure 3. Memory Organization, ADEN = 1

#### Variable Resistors

The value of each variable resistor is determined by a temperature-addressed look-up table, which can assign a unique value (00h to FFh) to each resistor for every 2°C increment over the -40°C to +102°C range (see Table 3). See the *Temperature Conversion* section for more information.

The variable resistors can also be used in manual mode. If the TEN bit equals 0, then the resistors are in manual mode and the temperature indexing is disabled. The user sets the resistors in manual mode by writing to addresses 82h and 83h in Table 01 to control resistors 0 and 1, respectively.

#### **Memory Description**

Main and auxiliary memories can be accessed by two separate device addresses. The Main Device address is A2h (or value in Table 01 byte 8Ch, when ADFIX = 1) and the Auxiliary Device address is A0h. A user option is provided to respond to one or two device addresses. This feature can be used to save component count in SFF applications (Main Device address can be used) or other applications where both GBIC (Auxiliary Device address can be used) and monitoring functions are implemented and two device addresses are needed. The memory blocks are enabled with the corresponding device address. Memory space from 80h and up is accessible only through the Main Device address. This memory is organized as three tables; the desired table can be selected by the contents of memory location 7Fh, Main Device. The Auxiliary Device address has no access to the tables, but the Auxiliary Device address can be mapped into the Main Device's memory space as a fourth table. Device addresses are programmable with two control bits in EEPROM.

ADEN configures memory access to respond to different device addresses (see Tables 4 and 5).

The default device address for EEPROM-generated addresses is A2h.

If the ADEN bit is 1, additional 128 bytes of EEPROM are accessible through the Main Device, selected as Table 00 (see Figure 3). In this configuration, the Auxiliary Device is not accessible. APEN controls the protection of Table 00 regardless of the setting of ADEN.

ADFIX (address fixed) determines whether the Main Device address is determined by an EEPROM byte (Table 01, byte 8Ch, when ADFIX =1). There can be up to 128 devices sharing a common 2-wire bus, with each device having its own unique device address.

#### **Memory Protection**

Memory access from either device address can be either read/write or read only. Write protection is accomplished by a combination of control bits in EEPROM (APEN and MPEN in configuration register 89h) and a write-protect enable (WPEN) pin. Since the WPEN pin is often not accessible from outside the module, this scheme effectively allows the module to be locked by the manufacturer to prevent accidental writes by the end user.

Separate write protection is provided for the Auxiliary and Main Device address through distinct bits APEN and MPEN. APEN and MPEN are bits from configuration register 89h, Table 01. Due to the location, the APEN and MPEN bits can only be written through the Main Device address. The control of write privileges through the Auxiliary Device address is dependent on the value of APEN. Care should be taken with the setting of MPEN, once set to a 1, assuming WPEN is high, access through the Main Device is thereafter denied unless WPEN is taken to a low level. By this means inadvertent end-user write access can be denied.

Main Device address space 60h to 7Fh is SRAM and is not write protected by APEN, MPEN, or WPEN. For example, the user may reset flags set by the device. Bytes designated as "Reserved" may be used as scratchpad, but they will not be stored in a power cycle because of their volatility. These bytes are reserved for added functionality in future versions of this device. Note that in single device mode (ADEN bit = 1), APEN determines the protection level of Table 00, independent of WPEN.

The write-protect operation, for both Main and Auxiliary Devices, is summarized in Tables 6 and 7.

**Table 6. Main Device**

| WPEN | MPEN | PROTECT MAIN |

|------|------|--------------|

| 0    | Χ    | No           |

| Х    | 0    | No           |

| 1    | 1    | Yes          |

Table 7. Auxiliary Device

| APEN | WPEN | PROTECT AUXILIARY |

|------|------|-------------------|

| 0    | Χ    | No                |

| 1    | Х    | Yes               |

## **Register Map**

A description of the registers is below. The registers are read only (R) or read/write (R/W). The R/W registers are writable only if write protect has not been asserted (see the *Memory Description* section).

## **Auxiliary Device**

| MEMORY LOCATION (hex) | EEPROM/SRAM | R/W | DEFAULT SETTING (hex) | NAME OF LOCATION | FUNCTION |

|-----------------------|-------------|-----|-----------------------|------------------|----------|

| 00 to 7F              | EEPROM      | R/W | 00                    | Standards Data   |          |

## **Main Device**

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF LOCATION                   | FUNCTION                                                                                                             |

|-----------------------------|-----------------|-----|-----------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 00 to 01                    | EEPROM          | R/W | 00                          | TMPlimhi (MSB to LSB)              | Contains upper limit settings for temperature. If the limit is violated, a flag in Main Device byte 70h is set.      |

| 02 to 03                    | EEPROM          | R/W | 00                          | TMPlimlo (MSB to LSB)              | Contains lower limit settings for temperature. If the limit is violated, a flag in Main Device byte 70h is set.      |

| 04 to 07                    | EEPROM          | R   | 00                          | Reserved                           | _                                                                                                                    |

| 08 to 09                    | EEPROM          | R/W | 00                          | V <sub>CC</sub> limhi (MSB to LSB) | Contains upper limit settings for V <sub>CC</sub> . If the limit is violated, a flag in Main Device byte 70h is set. |

| 0A to 0B                    | EEPROM          | R/W | 00                          | V <sub>CC</sub> limlo (MSB to LSB) | Contains lower limit settings for V <sub>CC</sub> . If the limit is violated, a flag in Main Device byte 70h is set. |

| 0C to 0F                    | EEPROM          | _   | 00                          | Reserved                           | _                                                                                                                    |

| 10 to 11                    | EEPROM          | R/W | 00                          | MON1limhi (MSB to LSB)             | Contains upper limit settings for MON1. If the limit is violated, a flag in Main Device byte 70h is set.             |

| 12 to 13                    | EEPROM          | R/W | 00                          | MON1limlo (MSB to LSB)             | Contains lower limit settings for MON1. If the limit is violated, a flag in Main Device byte 70h is set.             |

| 14 to 17                    | EEPROM          | _   | 00                          | Reserved                           | _                                                                                                                    |

| 18 to 19                    | EEPROM          | R/W | 00                          | MON2limhi (MSB to LSB)             | Contains upper limit settings for MON2. If the limit is violated, a flag in Main Device byte 70h is set.             |

| 1A to 1B                    | EEPROM          | R/W | 00                          | MON2limlo (MSB to LSB)             | Contains lower limit settings for MON2. If the limit is violated, a flag in Main Device byte 70h is set.             |

| 1C to 1F                    | EEPROM          | _   | 00                          | Reserved                           | _                                                                                                                    |

**Note:** SRAM defaults are power-on defaults. EEPROM defaults are factory defaults.

## **Main Device (continued)**

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF LOCATION                         | FUNCTION                                                                                                                                          |

|-----------------------------|-----------------|-----|-----------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 20 to 21                    | EEPROM          | R/W | 00                          | MON3limhi (MSB to LSB)                   | Contains upper limit settings for MON3. If the limit is violated, a flag in Main Device byte 71h is set.                                          |

| 22 to 23                    | EEPROM          | R/W | 00                          | MON3limhi (MSB to LSB)                   | Contains lower limit settings for MON3. If the limit is violated, a flag in Main Device byte 71h is set.                                          |

| 24 to 5F                    | EEPROM          | _   | 00                          | Reserved                                 | _                                                                                                                                                 |

| 60 to 61                    | SRAM            | R   | _                           | Measured TMP<br>(MSB to LSB)             | Digitized measured value for temperature.<br>See Table 1.                                                                                         |

| 62 to 63                    | SRAM            | R   | _                           | Measured V <sub>CC</sub><br>(MSB to LSB) | Digitized measured value for V <sub>CC</sub> . See Table 1.                                                                                       |

| 64 to 65                    | SRAM            | R   | _                           | Measured MON1<br>(MSB to LSB)            | Digitized measured value for MON1.<br>See Table 1.                                                                                                |

| 66 to 67                    | SRAM            | R   | _                           | Measured MON2<br>(MSB to LSB)            | Digitized measured value for MON2.<br>See Table 1.                                                                                                |

| 68 to 69                    | SRAM            | R   | _                           | Measured MON3<br>(MSB to LSB)            | Digitized measured value for MON3.<br>See Table 1.                                                                                                |

| 6A to 6D                    | SRAM            | R   | _                           | Reserved                                 | _                                                                                                                                                 |

| 6E                          | SRAM            | _   | _                           | Logic states                             | _                                                                                                                                                 |

| Bit 7                       | _               | R   | X                           | HIZSTA                                   | Resistor status bit. A high indicates that both resistors are in high-impedance mode. A low indicates that both resistors are operating normally. |

| 6                           | _               | R/W | 0                           | HIZCO                                    | Resistor control bit. Setting this bit high causes both resistors to go into a high-impedance state.                                              |

| 5                           | _               |     | X                           | X                                        | _                                                                                                                                                 |

| 4                           |                 |     | Х                           | X                                        |                                                                                                                                                   |

| 2                           |                 | R   | Х                           | TXF                                      | This status bit is high when OUT1 is high assuming there is an external pullup resistor on OUT1.                                                  |

| 3                           |                 | _   | Х                           | X                                        |                                                                                                                                                   |

| 1                           | _               | R   | X                           | RXL                                      | This status bit is high when OUT2 is high assuming there is an external pullup resistor on OUT2.                                                  |

| 0                           | <u> </u>        | R   | Х                           | RDYB                                     | This status bit goes high when V <sub>CC</sub> has fallen below the POA level.                                                                    |

## **Main Device (continued)**

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W      | DEFAULT<br>SETTING<br>(hex) | NAME OF LOCATION   | FUNCTION                                                                                                                                                                                                                         |

|-----------------------------|-----------------|----------|-----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6F                          | SRAM            | _        | _                           | Conversion updates | _                                                                                                                                                                                                                                |

| Bit 7                       | _               | R/W      | 0                           | TAU                | This bit goes high after a temperature and address update has occurred for the corresponding measurement in bytes 60h to 61h. This bit can be written to a 0 by the user and monitored to verify that a conversion has occurred. |

| 6                           | _               | R/W      | 0                           | VccU               | This bit goes high after a V <sub>CC</sub> update has occurred for the corresponding measurement in bytes 62h to 63h. This bit can be written to a 0 by the user and monitored to verify that a conversion has occurred.         |

| 5                           | _               | R/W      | 0                           | MON1U              | This bit goes high after a MON1 update has occurred for the corresponding measurement in bytes 64h to 65h. This bit can be written to a 0 by the user and monitored to verify that a conversion has occurred.                    |

| 4                           | _               | R/W      | 0                           | MON2U              | This bit goes high after a MON2 update has occurred for the corresponding measurement in bytes 66h to 67h. This bit can be written to a 0 by the user and monitored to verify that a conversion has occurred.                    |

| 3                           | _               | _        | 0                           | MON3U              | This bit goes high after a MON3 update has occurred for the corresponding measurement in bytes 68h to 69h. This bit can be written to a 0 by the user and monitored to verify that a conversion has occurred.                    |

| 2                           |                 |          | 0                           | 0                  |                                                                                                                                                                                                                                  |

| 11                          |                 | <u> </u> | 0                           | X                  | <u> </u>                                                                                                                                                                                                                         |

| 0                           | _               | _        | 0                           | X                  | _                                                                                                                                                                                                                                |

| 70                          | SRAM            | R        |                             | Alarm flags        | _                                                                                                                                                                                                                                |

| Bit 7                       | <u> </u>        |          | _                           | TMPhi              | This alarm flag goes high when the upper limit of the temperature setting is violated.                                                                                                                                           |

| 6                           | <u> </u>        |          |                             | TMPlo              | This alarm flag goes high when the lower limit of the temperature setting is violated.                                                                                                                                           |

| 5                           | _               |          | _                           | V <sub>CC</sub> hi | This alarm flag goes high when the upper limit of the V <sub>CC</sub> setting is violated.                                                                                                                                       |

## **Main Device (continued)**

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF LOCATION   | FUNCTION                                                                                                                                                           |

|-----------------------------|-----------------|-----|-----------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4                           | _               |     | _                           | V <sub>CC</sub> lo | This alarm flag goes high when the lower limit of the $V_{CC}$ setting is violated.                                                                                |

| 3                           | _               |     | _                           | MON1hi             | This alarm flag goes high when the upper limit of the MON1 setting is violated.                                                                                    |

| 2                           | _               |     | _                           | MON1lo             | This alarm flag goes high when the lower limit of the MON1 setting is violated.                                                                                    |

| 1                           | _               |     | _                           | MON2hi             | This alarm flag goes high when the upper limit of the MON2 setting is violated.                                                                                    |

| 0                           | _               | _   |                             | MON2lo             | This alarm flag goes high when the lower limit of the MON2 setting is violated.                                                                                    |

| 71                          | SRAM            | R   | _                           | Alarm flags        | _                                                                                                                                                                  |

| Bit 7                       | _               | _   | _                           | MON3hi             | This alarm flag goes high when the upper limit of the MON3 setting is violated.                                                                                    |

| 6                           | _               |     | _                           | MON3lo             | This alarm flag goes high when the lower limit of the MON3 setting is violated.                                                                                    |

| 5                           |                 |     |                             | X                  | _                                                                                                                                                                  |

| 4                           | _               |     | _                           | X                  | _                                                                                                                                                                  |

| 3                           | _               |     | _                           | X                  | _                                                                                                                                                                  |

| 2                           |                 | _   | _                           | X                  |                                                                                                                                                                    |

| 1                           |                 |     |                             | X                  |                                                                                                                                                                    |

| 0                           | _               | _   |                             | MINT               | A mask of all flags located in Table 01 byte 88h determines the value of MINT. MINT is maskable to 0 if no interrupt is desired by setting Table 01 byte 88h to 0. |

| 72 to 7E                    | SRAM            | R   | 00                          | Reserved           | _                                                                                                                                                                  |

| 7F                          | SRAM            | R/W | _                           | Table select       | _                                                                                                                                                                  |

| Bit 7                       |                 | _   | 0                           | X                  |                                                                                                                                                                    |

| 6                           |                 |     | 0                           | X                  |                                                                                                                                                                    |

| 5                           |                 |     | 0                           | X                  |                                                                                                                                                                    |

| 4                           |                 |     | 0                           | X                  |                                                                                                                                                                    |

| 3                           |                 |     | 0                           | X                  | _                                                                                                                                                                  |

| 2                           |                 |     | 0                           | X                  |                                                                                                                                                                    |

| 1                           |                 |     | 0                           | Table select bits  | Set bits = 00 to select Table 00, set bits = 01 to select Table 01, set bits = 10 to select                                                                        |

| 0                           | _               |     | 0                           |                    | Table 02, set bits = 11 to select Table 03.                                                                                                                        |

## Table 01h

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF<br>LOCATION | FUNCTION                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------|-----------------|-----|-----------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80                          | SRAM            | R/W |                             | Mode                | _                                                                                                                                                                                                                                                                                                                                            |

| Bit 7                       | _               | _   | 0                           | Х                   | _                                                                                                                                                                                                                                                                                                                                            |

| 6                           | _               | _   | 0                           | Х                   | _                                                                                                                                                                                                                                                                                                                                            |

| 5                           | _               |     | 0                           | Х                   | _                                                                                                                                                                                                                                                                                                                                            |

| 4                           | _               |     | 0                           | Х                   | _                                                                                                                                                                                                                                                                                                                                            |

| 3                           |                 |     | 0                           | Х                   | _                                                                                                                                                                                                                                                                                                                                            |

| 2                           |                 |     | 0                           | Х                   | _                                                                                                                                                                                                                                                                                                                                            |

| 1                           | _               | _   | 1                           | TEN                 | If TEN = 0, the temperature conversions update and the resistors can be controlled manually. The user sets the resistor in manual mode by writing to addresses 82h and 83h in Table 01 to control resistors 0 and 1, respectively.                                                                                                           |

| 0                           | _               | _   | 1                           | AEN                 | AEN = 0 provides manual control of the temperature index.                                                                                                                                                                                                                                                                                    |

| 81                          | SRAM            | R   | _                           | Temp index          | This byte is the temperature-calculated index used to select the address of resistor settings in the look-up tables.                                                                                                                                                                                                                         |

| 82                          | SRAM            | R/W | 00                          | Resistor 0          | Resistor 0 position values from 00h to FFh.                                                                                                                                                                                                                                                                                                  |

| 83                          | SRAM            | R/W | 00                          | Resistor 1          | Resistor 1 position values from 00h to FFh.                                                                                                                                                                                                                                                                                                  |

| 84 to 87                    | SRAM            | _   | 00                          | Reserved            | _                                                                                                                                                                                                                                                                                                                                            |

| 88                          | EEPROM          | R/W |                             | Interrupt enable    | This byte configures a maskable interrupt, determining which event asserts a buffer 1 output (MINT set to 1, see register 89h in Table 01). If any combination of temperature, VCC, MON1, MON2, or MON3 is desired to generate an interrupt, the corresponding bits are set to 1. If interrupt generation is not desired, set all bits to 0. |

| Bit 7                       | _               | _   | 1                           | TMP                 | _                                                                                                                                                                                                                                                                                                                                            |

| 6                           |                 |     | 1                           | V <sub>CC</sub>     |                                                                                                                                                                                                                                                                                                                                              |

| 5                           |                 |     | 1                           | MON1                |                                                                                                                                                                                                                                                                                                                                              |

| 4                           |                 |     | 1                           | MON2                | <u> </u>                                                                                                                                                                                                                                                                                                                                     |

| 3                           | _               |     | 1                           | MON3                |                                                                                                                                                                                                                                                                                                                                              |

| 2                           |                 |     | 0                           | X                   | _                                                                                                                                                                                                                                                                                                                                            |

| 1                           |                 |     | 0                           | X                   |                                                                                                                                                                                                                                                                                                                                              |

| 0                           | _               |     | 0                           | X                   | _                                                                                                                                                                                                                                                                                                                                            |

| 89                          | EEPROM          | R/W |                             | Configuration       | _                                                                                                                                                                                                                                                                                                                                            |

| Bit 7                       | _               | _   | 0                           | X                   | _                                                                                                                                                                                                                                                                                                                                            |

| 6                           | _               |     | 0                           | X                   |                                                                                                                                                                                                                                                                                                                                              |

## Table 01h (continued)

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF<br>LOCATION | FUNCTION                                                                                                                         |

|-----------------------------|-----------------|-----|-----------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

| 5                           |                 | _   | 0                           | ADEN                | Controls if the device responds to one or two device addresses (see the <i>Memory Description</i> section and Table 5).          |

| 4                           |                 | _   | 0                           | ADFIX               | Controls the means by which Main and Auxiliary Device addresses are set (see the <i>Memory Description</i> section and Table 5). |

| 3                           | _               | _   | 0                           | APEN                | Controls auxiliary write protect. See the <i>Memory Description</i> section.                                                     |

| 2                           |                 | _   | 0                           | MPEN                | Controls main write protect. See the <i>Memory Description</i> section.                                                          |

| 1                           |                 | _   | 0                           | INV1                | Configures buffer 1 with OUT1 = MINT + (INV1 [XOR] IN1).                                                                         |

| 0                           | _               | _   | 0                           | INV2                | Configures buffer 2 with OUT2 = INV2 [XOR] IN2.                                                                                  |

| 8A to 8B                    | EEPROM          | _   | 00                          | Reserved            |                                                                                                                                  |

| 8C                          | EEPROM          | R/W | A2                          | Device address      | Contains Main Device address if the bit ADFIX = 1. If ADFIX = 0, then address A2h is used.                                       |

| 8D to 8F                    | EEPROM          | _   | _                           | Reserved            | _                                                                                                                                |

#### Table 02h

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF LOCATION    | FUNCTION                      |

|-----------------------------|-----------------|-----|-----------------------------|---------------------|-------------------------------|

| 80 to C7                    | EEPROM          | R/W | FF                          | Resistor 0 Temp LUT | Look-up table for Resistor 0. |

| F0 to FF                    | EEPROM          | R   | FF                          | Reserved            | _                             |

### Table 03h

| MEMORY<br>LOCATION<br>(hex) | EEPROM/<br>SRAM | R/W | DEFAULT<br>SETTING<br>(hex) | NAME OF LOCATION    | FUNCTION                      |

|-----------------------------|-----------------|-----|-----------------------------|---------------------|-------------------------------|

| 80 to C7                    | EEPROM          | R/W | FF                          | Resistor 1 Temp LUT | Look-up table for Resistor 1. |

| F0 to FF                    | EEPROM          | R   | FF                          | Reserved            |                               |

#### Temperature Conversion

The direct-to-digital temperature sensor measures temperature through the use of an on-chip temperature measurement technique with an operating range from -40°C to +102°C. Temperature conversions are initiated upon power-up, and the most recent conversion is stored in memory locations 60h and 61h of the Main Device, which are updated every tframe. Temperature conversions do not occur during an active read or write to memory.

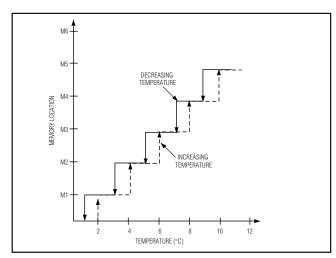

The value of each resistor is determined by the temperature-addressed look-up table. The look-up table assigns a unique value to each resistor for every 2°C increment with a 1°C hysteresis at a temperature transition over the operating temperature range (see Figure 4).

#### Power-Up and Low-Voltage Operation

During power-up, the device is inactive until V<sub>CC</sub> exceeds the digital power-on-reset voltage (POD). At this voltage, the digital circuitry, which includes the 2-wire interface, becomes functional. However, EEPROM backed registers/settings cannot be internally read (recalled into shadow SRAM) until V<sub>CC</sub> exceeds the analog power-on-reset voltage (POA) at which time the remainder of the device becomes fully functional. Once V<sub>CC</sub> exceeds POA, the RDYB bit in byte 6Eh of the Main Device memory is timed to go from a 1 to a 0 and indicates when analog to digital conversions begin. If V<sub>CC</sub> ever dips below POA, the RDYB bit will read as a 1 again. Once a device exceeds POA and the EEPROM is recalled, the values remain active (recalled) until V<sub>CC</sub> falls below POD.

For 2-wire device addresses sourced from EEPROM (ADFIX = 1), the device address defaults to A2h until VCC exceeds POA and the EEPROM values are recalled. The Auxiliary Device (A0h) is always available within this voltage window (between POD and the EEPROM recall) regardless of the programmed state of ADEN.

Furthermore, as the device powers-up, the  $V_{CC}$ lo alarm flag (bit 4 of 70h in Main Device) will default to a 1 until the first  $V_{CC}$  analog-to-digital conversion occurs and sets or clears the flag accordingly.

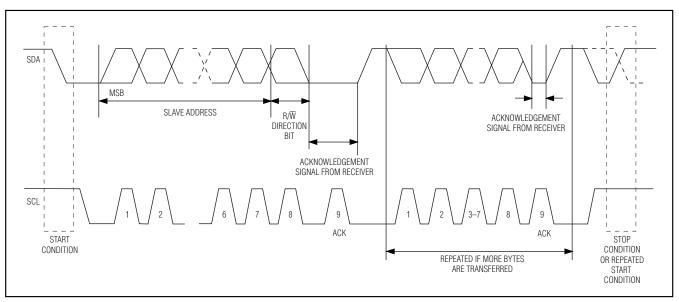

## 2-Wire Operation

Clock and Data Transitions: The SDA pin is normally pulled high with an external resistor or device. Data on the SDA pin may only change during SCL-low time periods. Data changes during SCL-high periods will indicate a start or stop condition depending on the conditions discussed below. See the timing diagrams in Figures 5 and 6 for further details.

Figure 4. Look-Up Table Hysteresis

**Start Condition:** A high-to-low transition of SDA with SCL high is a start condition, which must precede any other command. See the timing diagrams in Figures 5 and 6 for further details.

**Stop Condition:** A low-to-high transition of SDA with SCL high is a stop condition. After a read or write sequence, the stop command places the DS1858 into a low-power mode. See the timing diagrams in Figures 5 and 6 for further details.

**Acknowledge:** All address and data bytes are transmitted through a serial protocol. The DS1858 pulls the SDA line low during the ninth clock pulse to acknowledge that it has received each word.

**Standby Mode:** The DS1858 features a low-power mode that is automatically enabled after power-on, after a stop command, and after the completion of all internal operations.

**Device Addressing:** The DS1858 must receive an 8-bit device address word following a start condition to enable a specific device for a read or write operation. The address word is clocked into this part's MSB to LSB. The address byte consists of Ah (1010) followed by either A2h or the value in Table 01 8Ch for the Main Device or A0h for the Auxiliary Device then the R/W bit. This byte must match the address programmed into Table 01 8Ch or A0h (for the Auxiliary Device). If a device address match occurs, this part will output a zero for one clock cycle as an acknowledge and the corresponding block of memory is enabled (see the *Memory Organization* section). If the R/W bit is high, a read operation is initiated. If the R/W is low, a write operation is initiated (see the *Memory Organization*

section). If the address does not match, this part returns to a low-power mode.

#### Write Operations

After receiving a matching address byte with the R/W bit set low, provided there is no write protect, the device goes into the write mode of operation (see the Memory Organization section). The master must transmit an 8-bit EEPROM memory address to the device to define the address where the data is to be written. After the byte has been received, the DS1858 transmits a zero for one clock cycle to acknowledge the address has been received. The master must then transmit an 8-bit data word to be written into this address. The DS1858 again transmits a zero for one clock cycle to acknowledge the receipt of the data. At this point, the master must terminate the write operation with a stop condition. The DS1858 then enters an internally timed write process tw to the EEPROM memory. All inputs are disabled during this byte write cycle.

#### Page Write

The DS1858 is capable of an 8-byte page write. A page is any 8-byte block of memory starting with an address evenly divisible by eight and ending with the starting address plus seven. For example, addresses 00h through 07h constitute one page. Other pages would be addresses 08h through 0Fh, 10h through 17h, 18h through 1Fh, etc.

A page write is initiated the same way as a byte write, but the master does not send a STOP condition after the first byte. Instead, after the slave acknowledges the data byte has been received, the master can send up to seven more bytes using the same nine-clock sequence. The master must terminate the write cycle with a STOP condition or the data clocked into the DS1858 will not be latched into permanent memory.

The address counter rolls on a page during a write. The counter does not count through the entire address space as during a read. For example, if the starting address is 06h and 4 bytes are written, the first byte goes into address 06h. The second goes into address 07h. The third goes into address 00h (not 08h). The fourth goes into address 01h. If more than 9 bytes or more are written before a STOP condition is sent, the first bytes sent are overwritten. Only the last 8 bytes of data are written to the page.

**Acknowledge Polling:** Once the internally timed write has started and the DS1858 inputs are disabled, acknowledge polling can be initiated. The process involves transmitting a start condition followed by the device address. The R/W bit signifies the type of operation that is desired. The read or write sequence will only

be allowed to proceed if the internal write cycle has completed and the DS1858 responds with a zero.

#### **Read Operations**

After receiving a matching address byte with the R/W bit set high, the device goes into the read mode of operation. There are three read operations: current address read, random read, and sequential address read.

#### **Current Address Read**

The DS1858 has an internal address register that maintains the address used during the last read or write operation, incremented by one. This data is maintained as long as V<sub>CC</sub> is valid. If the most recent address was the last byte in memory, then the register resets to the first address.

Once the device address is clocked in and acknowledged by the DS1858 with the R/W bit set to high, the current address data word is clocked out. The master does not respond with a zero, but does generate a stop condition afterwards.

#### Single Read

A random read requires a dummy byte write sequence to load in the data byte address. Once the device and data address bytes are clocked in by the master, and acknowledged by the DS1858, the master must generate another start condition. The master now initiates a current address read by sending the device address with the R/W bit set high. The DS1858 acknowledges the device address and serially clocks out the data byte.

#### Sequential Address Read

Sequential reads are initiated by either a current address read or a random address read. After the master receives the first data byte, the master responds with an acknowledge. As long as the DS1858 receives this acknowledge after a byte is read, the master can clock out additional data words from the DS1858. After reaching address FFh, it resets to address 00h.

The sequential read operation is terminated when the master initiates a stop condition. The master does not respond with a zero.

For a more detailed description of 2-wire theory of operation, see the following section.

### \_2-Wire Serial Port Operation