#### **DS28E18**

# 1-Wire<sup>®</sup> to I<sup>2</sup>C/SPI Bridge with Command Sequencer

## **General Description**

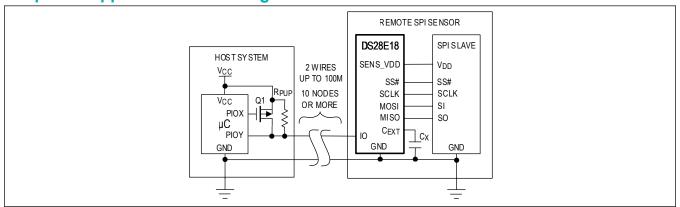

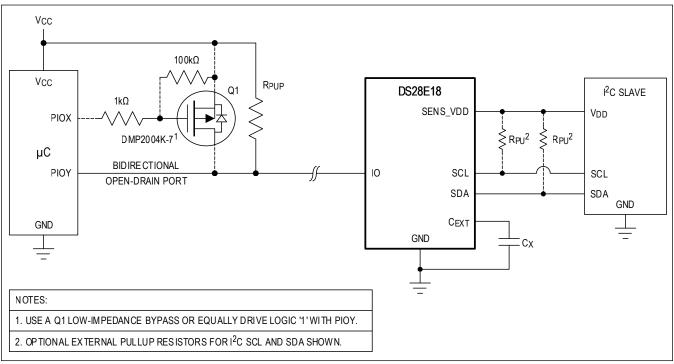

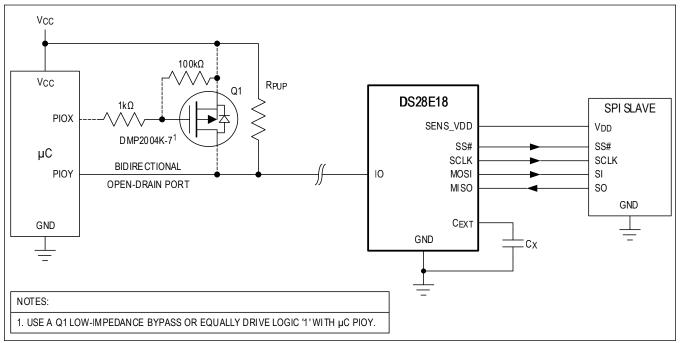

The DS28E18 is a simple communications bridge that resides at a remote SPI or I<sup>2</sup>C sensor and allows the sensor to be controlled by just two wires coming from the host system. It reduces the wire count from six (for SPI) or four (for I<sup>2</sup>C). These two wires use Maxim's 1-Wire protocol that combines power and signal on a single wire, and which is driven by the programmable I/O pins on the host's microcontroller. The 1-Wire network supports connection lengths up to 100m and 10 sensor nodes or more.

The IC provides a 512-byte command sequencer in SRAM that can be loaded with multiple I<sup>2</sup>C or SPI commands. Once loaded, the host controller sends a command to execute the sequence, power, and collect data from attached I<sup>2</sup>C or SPI peripherals. A subsequent 1-Wire command reads collected data. Power for attached sensors or peripherals is sourced from the 1-Wire line making the DS28E18 a very efficient solution to remotely power and control complex I<sup>2</sup>C or SPI devices such as sensors, ADCs, DACs, and display controllers.

When used as a bridge for I<sup>2</sup>C slave devices, the DS28E18 communicates at standard mode (100kHz), fast mode (400kHz) or fast-mode plus (Fm+, 1MHz). In SPI mode, multiple clock rates are supported up to 2.3MHz. Configuring for I<sup>2</sup>C or SPI operation is performed with a 1-Wire command; I<sup>2</sup>C is the power-on default. When operating in I<sup>2</sup>C mode, two programmable GPIO pins are available for additional peripheral control.

Each DS28E18 provides a unique and secure 64-bit ROM identification number (ROM ID) that serves as the device's address on the 1-Wire bus. Multiple DS28E18 devices can coexist with other devices in a 1-Wire network and be accessed individually without affecting other devices.

## **Applications**

- Examining Environmental Conditions

- Accessory Identification and Control

- Equipment Configuration and Monitoring

- Grain Elevator Monitoring

#### **Benefits and Features**

- Operate Remote I<sup>2</sup>C or SPI Devices Using Single-Contact 1-Wire Interface

- Extending I<sup>2</sup>C/SPI Communication Distance

- Reduce Six Wires (for SPI) or Four Wires (for I<sup>2</sup>C) to Two Wires

- 512-Byte Sequencer for Autonomous Operation of Attached Devices

- Two Configurable GPIO Pins for Additional Peripheral Control

- No External Power Required

- DS28E18 Parasitically Powered from 1-Wire

- I<sup>2</sup>C/SPI Peripheral Power Derived from the 1-Wire Line

- Flexible 1-Wire and I<sup>2</sup>C/SPI Master Operational Modes

- Supports Standard (11kbps) and Overdrive (90kbps) 1-Wire Communication

- 100kHz, 400kHz, and 1MHz for I<sup>2</sup>C Slaves

- · Up to 2.3MHz for SPI Slaves

- Easy to Integrate

- Small, 2mm x 3mm x 0.75mm, 8-Pin TDFN Package

- -40°C to +85°C Operation

- 2.97V to 3.63V Operating Voltage Range

Ordering Information appears at end of data sheet.

## **Simplified Application Block Diagram**

## **Absolute Maximum Ratings**

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Junction Temperature              | +125°C         |

| Storage Temperature Range         | 40°C to +125°C |

| Soldering Temperature (reflow)    | +260°C         |

| Lead Temperature (soldering, 10s) | +260°C         |

|                                   |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 8 TDFN-EP

| Package Code                              | T823+3C        |  |  |

|-------------------------------------------|----------------|--|--|

| Outline Number                            | <u>21-0174</u> |  |  |

| Land Pattern Number 90-0091               |                |  |  |

| Thermal Resistance, Single-Layer Board:   |                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )    | 60°C/W         |  |  |

| Junction-to-Case ( $\theta_{JC}$ ) 11°C/W |                |  |  |

| Thermal Resistance, Four-Layer Board:     |                |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )    | 60°C/W         |  |  |

| Junction-to-Case $(\theta_{JC})$          | 11°C/W         |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                         | SYMBOL            | CONDITIONS                        | MIN   | TYP                       | MAX  | UNITS |

|-----------------------------------|-------------------|-----------------------------------|-------|---------------------------|------|-------|

| IO PIN: GENERAL DATA              |                   |                                   |       |                           |      |       |

| 1-Wire Pullup Voltage             | V <sub>PUP</sub>  | ( <u>Note 1</u> )                 | 2.97  |                           | 3.63 | V     |

| 1-Wire Pullup<br>Resistance       | R <sub>PUP</sub>  | ( <u>Note 1</u> , <u>Note 2</u> ) | 300   |                           | 1000 | Ω     |

| Input Capacitance                 | C <sub>IO</sub>   | ( <u>Note 4</u> )                 |       | 0.1 +<br>C <sub>EXT</sub> |      | nF    |

| Capacitor External                | C <sub>EXT</sub>  | ( <u>Note 1</u> )                 | 399.5 | 470                       |      | nF    |

| Voltage Capacitor<br>External Min | V <sub>CEXT</sub> | t <sub>RSTL</sub> = 640µs         |       | 1.5                       |      | V     |

| Input Load Current                | ΙL                | IO pin at V <sub>PUP</sub>        |       | 8.5                       | 300  | μA    |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                       | SYMBOL                                                              | CONE                                                   | ITIONS                                              | MIN                                                  | TYP                        | MAX                       | UNITS |  |

|---------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|----------------------------|---------------------------|-------|--|

| High-to-Low Switching Threshold | V <sub>TL</sub>                                                     | (Note 3, Note 5, Note                                  | <u>fe 6</u> )                                       |                                                      | 0.65 x<br>V <sub>PUP</sub> |                           | V     |  |

| Input Low Voltage               | V <sub>IL</sub>                                                     | ( <u>Note 7</u> )                                      |                                                     |                                                      |                            | 0.1 x<br>V <sub>PUP</sub> | mV    |  |

| Low-to-High Switching Threshold | V <sub>TH</sub>                                                     | ( <u>Note 3</u> , <u>Note 5</u> , <u>Note 5</u>        | <u>'e 8</u> )                                       |                                                      | 0.75 x<br>V <sub>PUP</sub> |                           | V     |  |

| Switching Hysteresis            | V <sub>HY</sub>                                                     | (Note 3, Note 5, Note                                  | <u>9</u> )                                          |                                                      | 0.3                        |                           | V     |  |

| Output Low Voltage              | V <sub>OL</sub>                                                     | I <sub>OL</sub> = 4mA ( <u>Note 10</u>                 | )                                                   |                                                      |                            | 0.4                       | V     |  |

|                                 |                                                                     |                                                        | Standard speed                                      | 25                                                   |                            |                           |       |  |

| Recovery Time                   | t <sub>REC</sub>                                                    | R <sub>PUP</sub> = 1000Ω,<br>( <u>Note 1, Note 11,</u> | Standard speed,<br>directly prior to<br>reset pulse | 100                                                  |                            |                           | μs    |  |

|                                 |                                                                     | <u>Note 12</u> )                                       | Overdrive speed                                     | 5                                                    |                            |                           |       |  |

|                                 |                                                                     |                                                        |                                                     | Overdrive speed,<br>directly prior to<br>reset pulse | 10                         |                           |       |  |

| Rising-Edge Hold-off<br>Time    | t <sub>REH</sub>                                                    | Applies to standard speed only (Note 3, Note 13)       |                                                     |                                                      | 1                          |                           | μs    |  |

| Time Cleb Danielian             |                                                                     | Standard speed (No                                     | te 3, <u>Note 14</u> )                              | 85                                                   |                            | - µs                      |       |  |

| Time Slot Duration              | tslot                                                               | Overdrive speed ( <u>Note 3, Note 14</u> )             |                                                     | 11                                                   |                            |                           |       |  |

| IO PIN: 1-Wire RESET, P         | RESENCE-DET                                                         | ECT CYCLE                                              |                                                     |                                                      |                            |                           |       |  |

| Reset Low Time                  |                                                                     | Standard speed (No                                     | <u>te 1</u> )                                       | 480                                                  |                            | 640                       |       |  |

| Reset Low Time                  | t <sub>RSTL</sub>                                                   | Overdrive speed (N                                     | ote 1)                                              | 48                                                   |                            | 80                        | μs    |  |

| Reset High Time                 | t··                                                                 | Standard speed (No                                     | <u>ite 1, Note 15</u> )                             | 480                                                  |                            |                           |       |  |

| Reset High Time                 | <sup>t</sup> RSTH                                                   | Overdrive speed (Note 1, Note 15)                      |                                                     | 48                                                   |                            |                           | μs    |  |

| Presence-Detect Fall            | tenn                                                                | Standard speed (No                                     | te 3, <u>Note 16</u> )                              |                                                      | 1.25                       |                           | μs    |  |

| Time                            | t <sub>FPD</sub> Overdrive speed ( <u>Note 3</u> , <u>Note 16</u> ) |                                                        | ote 3, <u>Note 16</u> )                             |                                                      | 0.15                       |                           | μδ    |  |

| Presence-Detect                 | Detect Standard speed                                               | Standard speed (No                                     | te 1, Note 17)                                      | 65                                                   |                            | 75                        |       |  |

| Sample Time                     | t <sub>MSP</sub>                                                    | Overdrive speed (Note 1, Note 17)                      |                                                     | 7                                                    |                            | 10                        | μs    |  |

| IO PIN: 1-Wire WRITE            |                                                                     |                                                        |                                                     |                                                      |                            |                           |       |  |

| Write-Zero Low Time             | t                                                                   | Standard speed (No                                     | te 1, Note 18)                                      | 60                                                   | 60 120                     |                           | 116   |  |

| WING ZEIO LOW TIME              | t <sub>WOL</sub>                                                    | Overdrive speed (No                                    | ote 1, Note 18)                                     | 6                                                    |                            | 16                        | μs    |  |

| Write-One Low Time              | thanks                                                              | Standard speed (No                                     | te 1, Note 18)                                      | 0.25                                                 |                            | 15                        |       |  |

| Write-One Low Time              | t <sub>W1L</sub>                                                    | Overdrive speed ( <u>Note 1</u> , <u>Note 18</u> )     | 0.25                                                |                                                      | 2                          | μs                        |       |  |

(Limits are 100% tested at  $T_A = +25^{\circ}C$  and  $T_A = +85^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                        | SYMBOL                 | CONDITIONS                                                                                                              | MIN                        | TYP                        | MAX                        | UNITS |

|----------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| IO PIN: 1-Wire READ              | 1                      |                                                                                                                         | I                          |                            |                            |       |

| Deadless The                     |                        | Standard speed ( <i>Note 1</i> , <i>Note 19</i> )                                                                       | 0.25                       |                            | 15 - δ                     |       |

| Read Low Time                    | t <sub>RL</sub>        | Overdrive speed (Note 1, Note 19)                                                                                       | 0.25                       |                            | 2 - δ                      | μs    |

| Dead Consider Time               |                        | Standard speed (Note 1, Note 19)                                                                                        | t <sub>RL</sub> + δ        |                            | 15                         |       |

| Read Sample Time                 | tmsr                   | Overdrive speed (Note 1, Note 19)                                                                                       | t <sub>RL</sub> + δ        |                            | 2                          | μs    |

| STRONG PULLUP OPE                | RATION                 |                                                                                                                         |                            |                            |                            |       |

| Otaca a Dullius Come at          |                        | SENS_VDD Off                                                                                                            |                            |                            | 4                          | А     |

| Strong Pullup Current            | I <sub>SPU</sub>       | I <sub>SENS_VDD</sub> = 10mA ( <i>Note 20</i> )                                                                         |                            |                            | 14                         | mA    |

| Strong Pullup Voltage            | V <sub>SPU</sub>       | ( <u>Note 20</u> )                                                                                                      | 2.0                        |                            |                            | V     |

| SENSOR V <sub>DD</sub> OUTPUT    | SUPPLY PIN             |                                                                                                                         |                            |                            |                            |       |

| SENS_VDD Output<br>Voltage       | V <sub>SENS_VDD</sub>  | Sequencer active, IO = 3.3V, $I_{SENS\_VDD}$<br>= 1mA, $R_{LOAD}$ = 3.3k $\Omega$ , SENS_VD $\overline{D}$ on (Note 20) |                            | 3.28                       |                            | V     |

| SENS_VDD Current                 | I <sub>SENS_VDD</sub>  | Sequencer active, IO = 3.3V, SENS_VDD on ( <i>Note 20</i> )                                                             |                            |                            | 10                         | mA    |

| SENS_VDD High-Z                  |                        | Strong pullup not active or SENS_VDD off                                                                                |                            | 10                         |                            | МΩ    |

| I2C, SPI, AND GPIO PIN           | IS                     |                                                                                                                         |                            |                            |                            |       |

| Output Low                       | PIO_V <sub>OL</sub>    | I <sub>OL</sub> = 4mA ( <u>Note 10</u> )                                                                                |                            |                            | 0.4                        | V     |

| Output High                      | PIO_V <sub>OH</sub>    | I <sub>OH</sub> = -2mA                                                                                                  | V <sub>SPU</sub> - 0.4     |                            |                            | ٧     |

| Input Low                        | PIO_V <sub>IL</sub>    |                                                                                                                         | -0.3                       |                            | 0.18 x<br>V <sub>SPU</sub> | V     |

| Input High                       | PIO_V <sub>IH</sub>    |                                                                                                                         | 0.70 x<br>V <sub>SPU</sub> |                            | V <sub>SPU</sub> + 0.3     | V     |

| Switching Hysteresis             | PIO_V <sub>HY</sub>    |                                                                                                                         |                            | 0.05 x<br>V <sub>SPU</sub> |                            | ٧     |

| Leakage Current                  | PIO_I <sub>L</sub>     | Not including any pullup/pulldown current.                                                                              | -1                         |                            | +1                         | μΑ    |

| Input Capacitance                | PIO_C <sub>I</sub>     | ( <u>Note 3</u> )                                                                                                       |                            | 10                         |                            | pF    |

| <b>Command Timing</b>            |                        |                                                                                                                         |                            |                            |                            |       |

| Operation Time                   | t <sub>OP</sub>        | Note 3                                                                                                                  |                            |                            | 1                          | ms    |

| I <sup>2</sup> C MASTER (STANDAR | RD MODE) ( <u>Note</u> | <u>22</u> )                                                                                                             |                            |                            |                            |       |

| SCL Clock Frequency              | f <sub>SCL</sub>       |                                                                                                                         |                            |                            | 100                        | kHz   |

| SCK High Time                    | tHIGH                  |                                                                                                                         | 4.0                        |                            |                            | μs    |

| SCK Low Time                     | t <sub>LOW</sub>       |                                                                                                                         | 4.7                        |                            |                            | μs    |

| Start Setup Time                 | t <sub>SU:STA</sub>    |                                                                                                                         | 4.7                        |                            |                            | μs    |

| Stop Setup Time                  | tsu:sto                |                                                                                                                         | 4.0                        |                            |                            | μs    |

| Data Setup Time                  | t <sub>SU:DAT</sub>    |                                                                                                                         | 250                        |                            |                            | ns    |

| Data Hold Time                   | t <sub>HD:DAT</sub>    | ( <u>Note 23</u> )                                                                                                      | 0                          |                            |                            | μs    |

(Limits are 100% tested at  $T_A$  = +25°C and  $T_A$  = +85°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                            | SYMBOL                 | CONDITIONS                                               | MIN  | TYP | MAX | UNITS |

|--------------------------------------|------------------------|----------------------------------------------------------|------|-----|-----|-------|

| Start Hold Time                      | t <sub>HD:STA</sub>    |                                                          | 4    |     |     |       |

| Bus Free Time Between STOP and START | t <sub>BUF</sub>       |                                                          | 4.7  |     |     | μs    |

| Fall Time                            | t <sub>F</sub>         |                                                          |      | 30  |     | ns    |

| Capacitive Load for Each Bus Line    | C <sub>B</sub>         | I <sup>2</sup> C mode ( <i>Note 1</i> , <i>Note 24</i> ) |      |     | 400 | pF    |

| I <sup>2</sup> C MASTER (FAST MOD    | DE) ( <u>Note 22</u> ) |                                                          |      |     |     |       |

| SCL Clock Frequency                  | f <sub>SCL</sub>       |                                                          |      |     | 400 | kHz   |

| SCK High Time                        | <sup>t</sup> HIGH      |                                                          | 0.6  |     |     | μs    |

| SCK Low Time                         | $t_{LOW}$              |                                                          | 1.3  |     |     | μs    |

| Start Setup Time                     | tsu:sta                |                                                          | 0.6  |     |     | μs    |

| Stop Setup Time                      | tsu:sto                |                                                          | 0.6  |     |     | μs    |

| Data Setup Time                      | t <sub>SU:DAT</sub>    |                                                          | 100  |     |     | ns    |

| Data Hold Time                       | thd:dat                | ( <u>Note 23</u> )                                       | 0    |     |     | μs    |

| Start Hold Time                      | thd:sta                |                                                          | 0.6  |     |     | μs    |

| Bus Free Time Between STOP and START | t <sub>BUF</sub>       |                                                          | 1.3  |     |     | μs    |

| Fall Time                            | t <sub>F</sub>         |                                                          |      | 30  |     | ns    |

| Capacitive Load for Each Bus Line    | C <sub>B</sub>         | I <sup>2</sup> C mode ( <i>Note 1</i> , <i>Note 24</i> ) |      |     | 400 | pF    |

| I <sup>2</sup> C MASTER (FAST-MOD    | DE PLUS) ( <u>Note</u> | <u>22</u> )                                              | •    |     |     |       |

| SCL Clock Frequency                  | f <sub>SCL</sub>       |                                                          |      |     | 1   | MHz   |

| SCK High Time                        | <sup>t</sup> HIGH      |                                                          | 0.26 |     |     | μs    |

| SCK Low Time                         | $t_{LOW}$              |                                                          | 0.5  |     |     | μs    |

| Start Setup Time                     | tsu:sta                |                                                          | 0.26 |     |     | μs    |

| Stop Setup Time                      | tsu:sto                |                                                          | 0.26 |     |     | μs    |

| Data Setup Time                      | tsu:dat                |                                                          | 50   |     |     | ns    |

| Data Hold Time                       | thd:dat                | ( <u>Note 23</u> )                                       | 0    |     |     | μs    |

| Start Hold Time                      | t <sub>HD:STA</sub>    |                                                          | 0.26 |     |     | μs    |

| Bus Free Time Between STOP and START | t <sub>BUF</sub>       |                                                          | 0.5  |     |     | μs    |

| Fall Time                            | t <sub>F</sub>         |                                                          |      | 30  |     | ns    |

| Capacitive Load for Each Bus Line    | C <sub>B</sub>         | (Note 1, Note 24)                                        |      |     | 550 | pF    |

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

| PARAMETER                                       | SYMBOL                              | CONDITIONS | MIN | TYP                          | MAX | UNITS  |  |  |

|-------------------------------------------------|-------------------------------------|------------|-----|------------------------------|-----|--------|--|--|

| SPI MASTER ( <u>Note 25</u> )                   | SPI MASTER (Note 25)                |            |     |                              |     |        |  |  |

|                                                 |                                     | SPD = 0b00 |     | 88.9                         | 100 | - kHz  |  |  |

| SPI Master Operating                            | f                                   | SPD = 0b01 |     | 333.3                        | 400 | KIIZ   |  |  |

| Frequency                                       | fMCK                                | SPD = 0b10 |     | 0.8                          | 1   | MHz    |  |  |

|                                                 |                                     | SPD = 0b11 |     | 2.0                          | 2.3 | IVITIZ |  |  |

| SPI Master SCK Period                           | tMCK                                |            |     | $\frac{1}{f_{MCK}}$          |     | μs     |  |  |

| SCK Output Pulse-<br>Width High/Low             | t <sub>MCH</sub> , t <sub>MCL</sub> |            |     | t <sub>MCK</sub>             |     | μs     |  |  |

| MOSI Output Hold Time<br>After SCK Sample Edge  | tмон                                |            |     | $\frac{3}{4} \times t_{MCK}$ |     | μs     |  |  |

| MOSI Output Valid to<br>Sample Edge             | t <sub>MOV</sub>                    |            |     | $\frac{t_{MCK}}{4}$          |     | μs     |  |  |

| MISO Input Valid to<br>SCK Sample Edge<br>Setup | t <sub>MIS</sub>                    |            |     | 50                           |     | ns     |  |  |

| MISO Input to SCK<br>Sample Edge Hold           | t <sub>MIH</sub>                    |            |     | 50                           |     | ns     |  |  |

| MOSI Transition to SS<br>Transition             | t <sub>SS:SU</sub>                  |            |     | t <sub>MCK</sub>             |     | μs     |  |  |

| SS Active to First SCK<br>Edge                  | tss:clk                             | SPI mode 3 |     | $\frac{3}{4} \times t_{MCK}$ |     | μs     |  |  |

- Note 1: System requirement.

- Note 2: System requirement. Maximum allowable pullup resistance is a function of the number of 1-Wire devices in the system and 1-Wire recovery times. The specified value here applies to systems with only one device and with the minimum 1-Wire recovery times.

- Note 3: Guaranteed by design and/or characterization only. Not production tested.

- Note 4: Value represents the internal parasite capacitance when V<sub>PUP</sub> is first applied. Once the parasite capacitance is charged, it does not affect normal communication. Typically, during normal communication, the internal parasite capacitance is effectively ~100pF.

- Note 5: V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub> are a function of the internal supply voltage, which is a function of V<sub>PUP</sub>, R<sub>PUP</sub>, 1-Wire timing, and capacitive loading on IO. Lower V<sub>PUP</sub>, higher R<sub>PUP</sub>, shorter t<sub>REC</sub>, and heavier capacitive loading all lead to lower values of V<sub>TL</sub>, V<sub>TH</sub>, and V<sub>HY</sub>.

- Note 6: Voltage below which, during a falling edge on IO, a logic-zero is detected.

- Note 7: The voltage on IO must be less than or equal to V<sub>ILMAX</sub> at all times the master is driving IO to a logic-zero level.

- Note 8: Voltage above which, during a rising edge on IO, a logic-one is detected.

- Note 9: After  $V_{TH}$  is crossed during a rising edge on IO, the voltage on IO must drop by at least  $V_{HY}$  to be detected as logic-zero.

- Note 10: The current-voltage (I-V) characteristic is linear for voltages less than 1V.

- Note 11: Applies to a single device attached to a 1-Wire line.

- Note 12:  $t_{REC}$  (min) covers operation at worst-case temperature.  $V_{PUP}$ ,  $R_{PUP}$ ,  $C_{IO}$ ,  $t_{RSTL}$ ,  $t_{WOL}$ ,  $t_{RL}$ , and  $t_{RECMIN}$  can be significantly reduced under less extreme conditions. Contact the factory for more information.

- Note 13: The earliest recognition of a negative edge is possible at t<sub>REH</sub> after V<sub>TH</sub> has been previously reached.

- Note 14: Defines the maximum possible bit rate. Equal to 1/(t<sub>W0LMIN</sub> + t<sub>RECMIN</sub>).

- Note 15: An additional reset or communication sequence cannot begin until the reset high time has expired.

### DS28E18

## 1-Wire® to I<sup>2</sup>C/SPI Bridge with Command Sequencer

- Note 16: Time from  $V_{IO}$  = 80% of  $V_{PUP}$  and  $V_{IO}$  = 20% of  $V_{PUP}$  at the negative edge on IO at the beginning of the presence detect pulse.

- Note 17: Interval after t<sub>RSTL</sub> during which a bus master can read a logic 0 on IO if there is a device present. The power-up presence detect pulse could be outside this interval, but will be complete within 2ms after power-up.

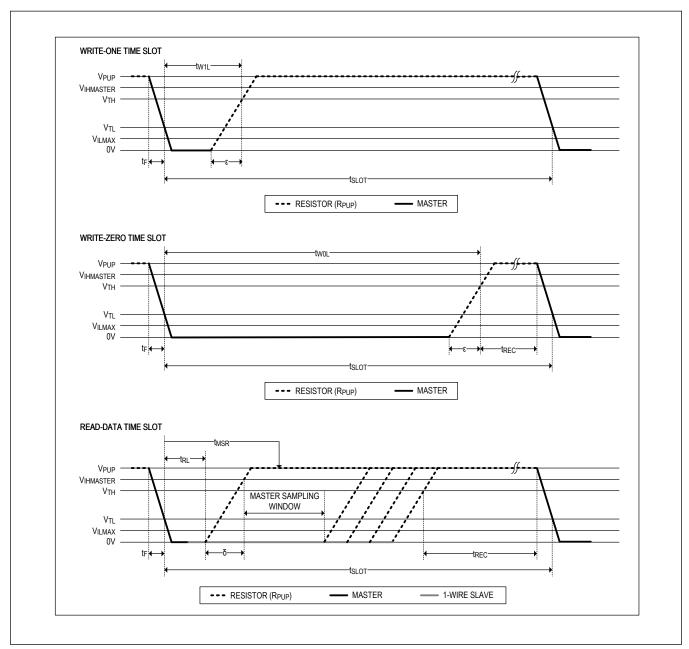

- Note 18:  $\epsilon$  in Figure 6 represents the time required for the pullup circuitry to pull the voltage on IO up from  $V_{IL}$  to  $V_{TH}$ . The actual maximum duration for the master to pull the line low is  $t_{W1LMAX} + t_F \epsilon$  and  $t_{W0LMAX} + t_F \epsilon$ , respectively.

- Note 19:  $\delta$  in Figure 6 represents the time required for the pullup circuitry to pull the voltage on IO up from  $V_{IL}$  to the input-high threshold of the bus master. The actual maximum duration for the master to pull the line low is  $t_{RLMAX} + t_{F}$ .

- Note 20: I<sub>SPU</sub> is the current drawn from IO during a strong pullup (SPU) operation. The pullup circuit on IO during the SPU operation should be such that the voltage at IO is greater than or equal to V<sub>SPUMIN</sub>. A low-impedance bypass of R<sub>PUP</sub> activated during the SPU operation is the recommended method to meet this requirement. See the <u>Typical Application Circuits</u> for details.

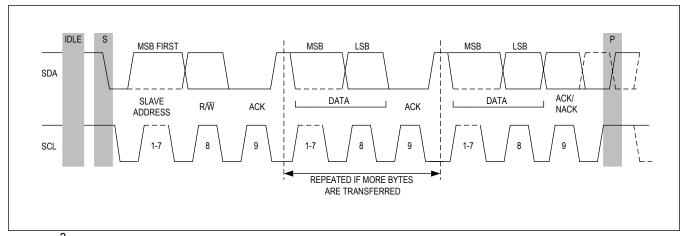

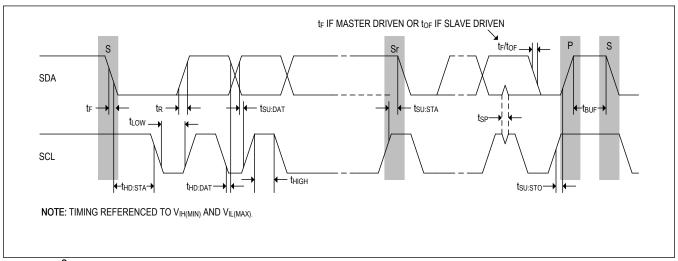

- **Note 21:** All I<sup>2</sup>C timing values are referred to V<sub>IH(MIN)</sub> and V<sub>IL(MAX)</sub> levels.

- Note 22: See Figure 10 for I<sup>2</sup>C timing symbol details. Rise and fall times are system dependent and not included.

- Note 23: The DS28E18 provides 2.5µs (standard mode), 675ns (fast mode), or 280ns (Fm+) minimum hold time, not including rise/fall time, for the SDA signal.

- Note 24:  $C_B$  = Total capacitance of one bus line in pF. The maximum bus capacitance allowable may vary from this value depending on the actual operating voltage and frequency of the application (I<sup>2</sup>C bus specification Rev. 03, 19 June 2007).

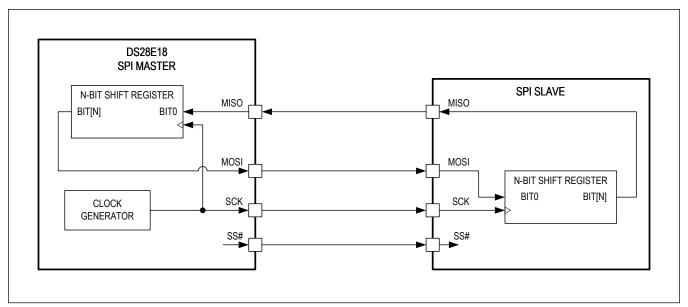

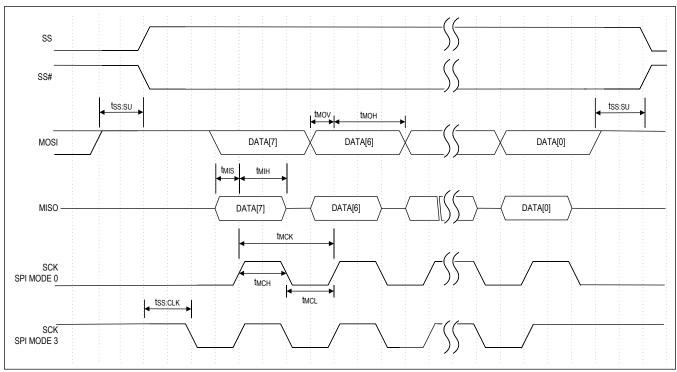

- Note 25: See Figure 12 for SPI timing symbol details. The f<sub>MCK</sub> options listed only effect speed for the SPI WRITE/READ BYTE command. The f<sub>MCK</sub> for the SPI WRITE/READ BIT command is variable up to a maximum of 134kHz. Rise and fall times are system dependent and not included.

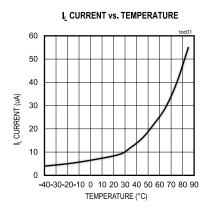

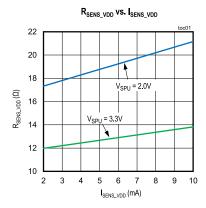

## **Typical Operating Characteristics**

( $V_{PUP}$  = +3.3V;  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$  unless otherwise noted.)

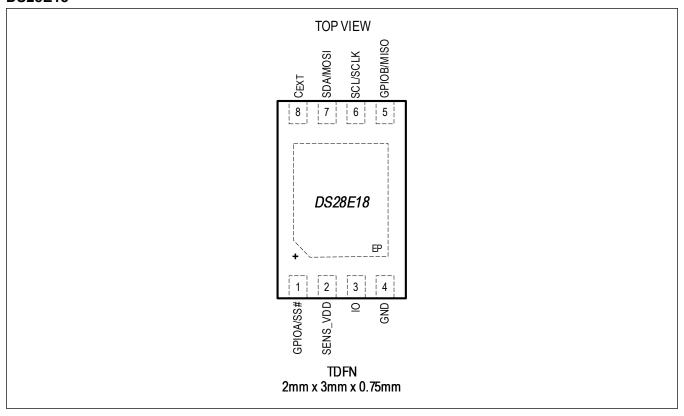

## **Pin Configuration**

## **DS28E18**

## **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GPIOA/SS#        | General-Purpose I/O (Default). If the DS28E18 is configured for SPI master operation, this pins is used as an active-low slave select (SS#) . In SPI master mode, this pin is output only.                                                                                                                                                                                                                                                  |

| 2   | SENS_VDD         | Output Supply for Powering External I <sup>2</sup> C/SPI Sensors/Devices. Connect this output supply pin to the external I <sup>2</sup> C/SPI devices power supply pin. This pin is only an output during strong pullup operation. When not in strong pullup operation, this pin is set to a high-impedance state.  Note: See the <i>Electrical Characteristics</i> table for detailed information on the maximum supply current supported. |

| 3   | Ю                | 1-Wire Bus Interface. This is an open-drain pin that requires an external pullup resistance (R <sub>PUP</sub> ).                                                                                                                                                                                                                                                                                                                            |

| 4   | GND              | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5   | GPIOB/MISO       | General Purpose I/O (Default). If the DS28E18 is configured for SPI Master mode, this pin is used as master input slave output (MISO) and operates as an input-only I/O.                                                                                                                                                                                                                                                                    |

| 6   | SCL/SCLK         | I <sup>2</sup> C Serial Clock (SCL) (Default). If the DS28E18 is configured for SPI Master mode, this pin is used as the SPI clock (SCLK).                                                                                                                                                                                                                                                                                                  |

| 7   | SDA/MOSI         | I <sup>2</sup> C Serial-Data Input/Output (Default). If the DS28E18 is configured for SPI Master mode, this pin is used as the master output slave input (MOSI). When configured as MOSI, this pin is an output only.                                                                                                                                                                                                                       |

| 8   | C <sub>EXT</sub> | Input for External Capacitor. Nominally a 470nF capacitor is to be connected from this pin to ground. This pin acts as the parasite power (i.e., derives power from the 1-Wire bus) during 1-Wire operation. Alternately, this pin may also be directly connected to a power supply in the voltage range of VPUP.                                                                                                                           |

| _   | EP               | Exposed Pad. Solder evenly to the board's ground plane for proper operation. Refer to <u>Application Note 3273: Exposed Pads: A Brief Introduction</u> for additional information.                                                                                                                                                                                                                                                          |

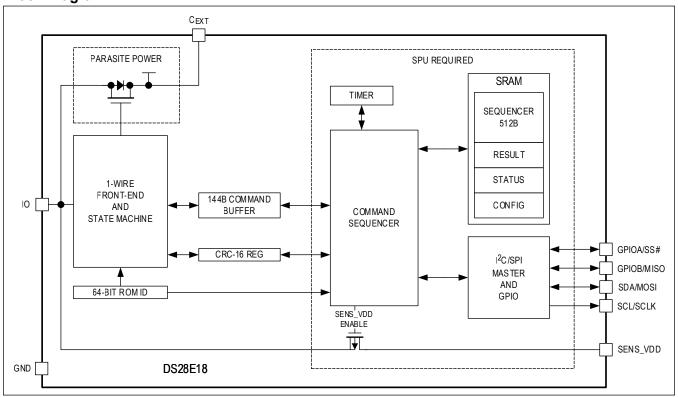

## **Functional Diagram**

## **Block Diagram**

## **Detailed Description**

The DS28E18 integrates a 1-Wire slave front-end, an I<sup>2</sup>C/SPI bus master peripheral, GPIO, power control, and functionality to bridge these circuit elements for data communication and power delivery to attached I<sup>2</sup>C/SPI slaves. The IC has a 144-byte command buffer that utilizes 16-bytes for device function command operations and 128-bytes to transfer formed packets with sequential commands into a 512-byte SRAM sequencer. The formed packets installed in the SRAM sequencer can be called to write and/or read I<sup>2</sup>C/SPI data to attached slaves. The maximum length of a sequence is 512 bytes. Upon completion of a sequence, the I<sup>2</sup>C/SPI slave response is recovered using a Read sequencer command. From a host controller, DS28E18 communication is performed serially using the 1-Wire protocol, which requires only a single data connection and a ground return for signaling. The DS28E18 includes a 64-bit unique ROM ID, which guarantees unique and secure identification and also serves as the address of the device in a multidrop 1-Wire network environment where multiple devices reside on a common 1-Wire bus and operate independently of each other.

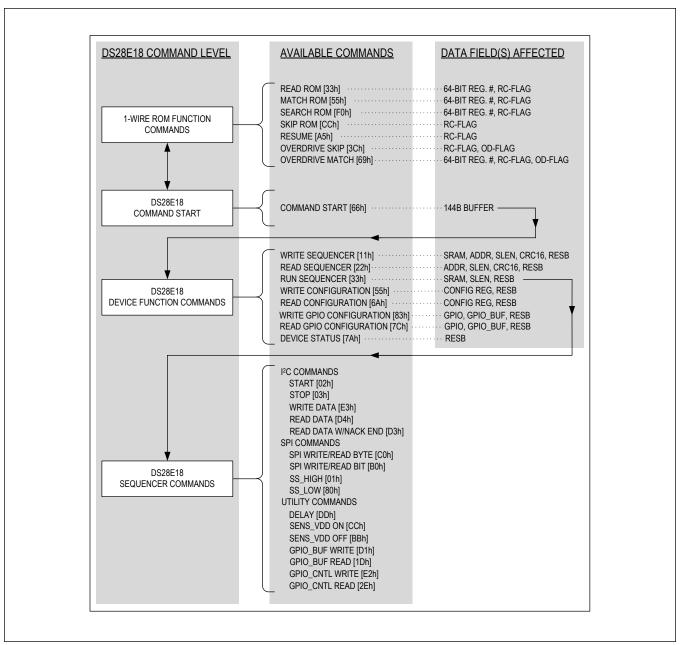

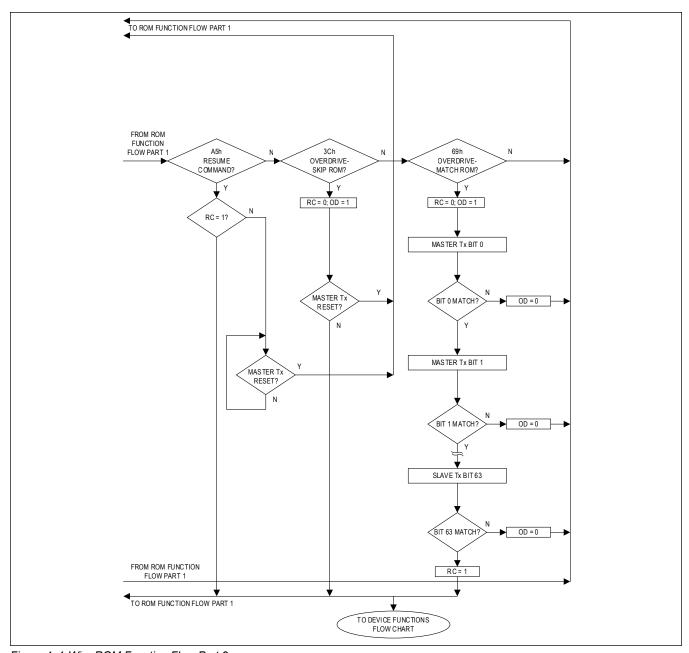

<u>Figure 1</u> shows the hierarchical structure of the 1-Wire ROM function, device function, and sequencer commands. The bus master must first provide one of the seven ROM function commands: Read ROM, Match ROM, Search ROM, Skip ROM, Resume, Overdrive-Skip ROM, or Overdrive-Match ROM. Upon completion of an Overdrive-Skip ROM or Overdrive-Match ROM command byte executed at standard speed, the device enters overdrive mode where all subsequent communication occurs at a higher speed. **All 1-Wire data communication is performed least significant bit first.**

Figure 1. DS28E18 1-Wire Commands Hierarchical Structure

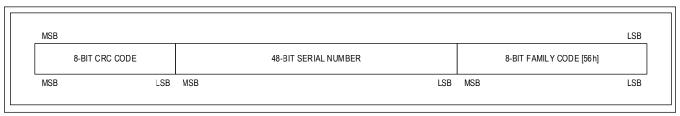

#### 64-Bit ROM ID

Each DS28E18 contains a unique ROM ID that is 64 bits long. The first 8 bits are a 1-Wire family code. The next 48 bits are a unique serial number. The last 8 bits are a cyclic redundancy check (CRC) of the first 56 bits. See <u>Figure 2</u> for details. The 1-Wire CRC is generated using a polynomial generator consisting of a shift register and XOR gates. The polynomial is  $X^8 + X^5 + X^4 + 1$ . Additional information about the 1-Wire CRC is available in <u>Application Note 27: Understanding and Using Cyclic Redundancy Checks with Maxim iButton® Products</u>.

Figure 2. 64-Bit ROM ID

### Power-Up ROM ID Serialization

On power-up, the ROM ID value is 5600000000000000000. The uniquely programmed factory value for each DS28E18 needs to be loaded from memory. After power-up, issue a Skip ROM command followed by a Write GPIO Configuration command. This initial command populates the unique device ROM ID, including family code, serialization, and CRC-16. Ignore the command CRC-16 result and the Result byte, as both might be invalid. Next issue a successful Write GPIO Configuration command to configure the GPIO pullup/down states so that the voltage on the GPIO ports is known. See the <a href="Power-Up of GPIO/I<sup>2</sup>C Pins">Power-Up of GPIO/I<sup>2</sup>C Pins</a> section. However, this will not clear the POR status bit. Another successful Device Status command should be issued to receive valid status information and clear the POR status bit.

#### 1-Wire Bus System

The 1-Wire bus is a system that has a single bus master and one or more slaves. In all instances, the DS28E18 is a slave device. The bus master is typically a microcontroller. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Wire signaling (signal types and timing). The 1-Wire protocol defines bus transactions in terms of the bus state during specific time slots, which are initiated on the falling edge of sync pulses from the bus master.

#### **Hardware Configuration**

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open-drain or three-state outputs. The 1-Wire port (i.e., IO pin) of the DS28E18 is open drain with an internal circuit equivalent.

A multidrop bus consists of a 1-Wire bus with multiple slaves attached. The DS28E18 supports both a standard and overdrive communication speed of 11kbps (max) and 90kbps (max), respectively. The value of the pullup resistor primarily depends on the network size and load conditions. The DS28E18 requires a pullup resistor of  $1k\Omega$  (max) at any speed. Some 1-Wire masters have the pullup resistance ( $R_{PUP}$ ) built in and others require the addition of  $R_{PUP}$  as an external resistor.

The idle state for the 1-Wire bus is high. If for any reason a transaction needs to be suspended, the bus must be left in the idle state if the transaction is to resume. If this does not occur and the bus is left low for more than 16µs in overdrive operation, one or more devices on the bus could be reset.

#### **Transaction Sequence**

The protocol for accessing the DS28E18 through the 1-Wire port is as follows:

- Initialization

- ROM function command

- Device function command

- Transaction/data

#### Initialization

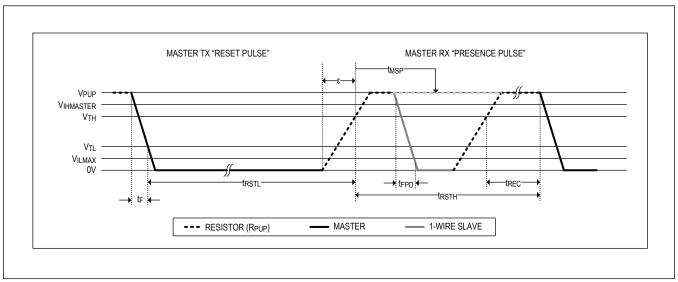

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that the DS28E18 is on the bus and is ready to operate.

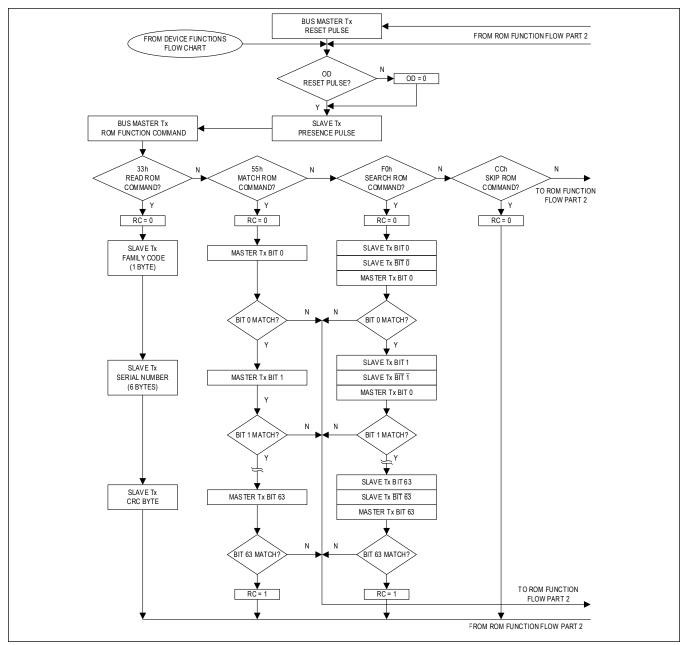

#### 1-Wire ROM Function Commands

Once the bus master has detected a presence, it can issue one of the seven ROM function commands that the DS28E18 supports. All ROM function commands are 8 bits long. A list of these commands follows. See the flowcharts in <u>Figure 3</u> and Figure 4.

Figure 3. 1-Wire ROM Function Flow Part 1

Figure 4. 1-Wire ROM Function Flow Part 2

### Search ROM [F0h]

When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their ROM ID numbers. By taking advantage of the wired-AND property of the bus, the master can use a process of elimination to identify the ID of all slave devices. For each bit in the ID number, starting with the least significant bit, the bus master issues a triplet of time slots. On the first slot, each slave device participating in the search outputs the true value of its ID number bit. On the second slot, each slave device participating in the search outputs the complemented value of its ID number bit. On the third slot, the master writes the true value of the bit to be selected. All slave devices that do not match the bit written by the master stop participating in the search. If both of the read bits are zero, the master knows that slave

devices exist with both states of the bit. By choosing which state to write, the bus master branches in the search tree. After one complete pass, the bus master knows the ROM ID number of a single device. Additional passes identify the ID numbers of the remaining devices. Refer to <u>Application Note 187: 1-Wire Search Algorithm</u> for a detailed discussion, including an example.

#### Read ROM [33h]

The Read ROM command allows the bus master to read the DS28E18 8-bit family code, unique 48-bit serial number, and 8-bit CRC. This command can only be used if there is a single slave on the bus. If more than one slave is present on the bus, a data collision occurs when all slaves try to transmit at the same time (open drain produces a wired-AND result). The resultant family code and 48-bit serial number result in a mismatch of the CRC.

#### Match ROM [55h]

The Match ROM command, followed by a 64-bit ROM sequence, allows the bus master to address a specific DS28E18 on a multidrop bus. Only the DS28E18 that exactly matches the 64-bit ROM sequence responds to the subsequent Device command. All other slaves wait for a reset pulse. This command can be used with a single device or multiple devices on the bus.

#### Skip ROM [CCh]

This command can save time in a single-drop bus system by allowing the bus master to access the Device commands without providing the 64-bit ROM ID. If more than one slave is present on the bus and, for example, a read command is issued following the Skip ROM command, data collision occurs on the bus as multiple slaves transmit simultaneously (open-drain pulldowns produce a wired-AND result).

#### Resume [A5h]

To maximize the data throughput in a multidrop environment, the Resume command is available. This command checks the status of the RC bit and, if it is set, directly transfers control to the Device commands, similar to a Skip ROM command. The only way to set the RC bit is through successfully executing the Match ROM, Search ROM, or Overdrive-Match ROM command. Once the RC bit is set, the device can repeatedly be accessed through the Resume command. Accessing another device on the bus clears the RC bit, preventing two or more devices from simultaneously responding to the Resume command.

#### Overdrive-Skip ROM [3Ch]

On a single-drop bus, this command can save time by allowing the bus master to access the device commands without providing the 64-bit ROM ID. Unlike the normal Skip ROM command, the Overdrive-Skip ROM command sets the DS28E18 into the overdrive mode (OD = 1). All communication following this command must occur at overdrive speed until a reset pulse of minimum  $480\mu s$  duration resets all devices on the bus to standard speed (OD = 0).

When issued on a multidrop bus, this command sets all overdrive-supporting devices into overdrive mode. To subsequently address a specific overdrive-supporting device, a reset pulse at overdrive speed must be issued followed by a Match ROM or Search ROM command sequence. This speeds up the time for the search process. If more than one slave supporting overdrive is present on the bus and the Overdrive-Skip ROM command is followed by a read command, data collision occurs on the bus as multiple slaves transmit simultaneously (open-drain pulldowns produce a wired-AND result).

#### Overdrive-Match ROM [69h]

The Overdrive-Match ROM command, followed by a 64-bit ROM sequence transmitted at overdrive speed, allows the bus master to address a specific DS28E18 on a multidrop bus and to simultaneously set it in Overdrive mode. Only the DS28E18 that exactly matches the 64-bit ROM sequence responds to the subsequent device command. Slaves already in Overdrive mode from a previous Overdrive-Skip ROM or successful Overdrive-Match ROM command remain in Overdrive mode. All overdrive-capable slaves return to standard speed at the next reset pulse having a minimum duration of 480µs. The Overdrive-Match ROM command can be used with a single device or multiple devices on the bus.

#### 1-Wire Signaling and Timing

The 1-Wire protocol consists of four types of signaling on one line: reset cycle with reset pulse and presence pulse, write-zero, write-one, and read-data. Except for the presence pulse, the 1-Wire master initiates all falling edges. The 1-Wire master can communicate at two speeds: standard and overdrive. While in overdrive mode, the fast timing applies to all wave forms.

<u>Figure 5</u> shows the initialization sequence required to begin any communication. A reset pulse followed by a presence pulse indicates that a slave is ready to receive data, given the correct ROM and device function command.

Figure 5. 1-Wire Reset/Presence-Detect Cycle

#### **Read/Write Time Slots**

Data communication on the 1-Wire bus takes place in time slots that carry a single bit each. Write time slots transport data from 1-Wire master to a connected slave. Read time slots transfer data from slave to the 1-Wire master. <u>Figure 6</u> illustrates the definitions of the write and read time slots.

All communication begins with the master pulling the data line low. As the voltage on the 1-Wire line falls below the threshold  $V_{TL}$ , the slave starts its internal timing generator that determines when the data line is sampled during a write time slot and how long data is valid during a read time slot.

#### Master-to-Slave

For a write-one time slot, the voltage on the data line must have crossed the  $V_{TH}$  threshold before the write-one low time  $t_{W1LMAX}$  is expired. For a write-zero time slot, the voltage on the data line must stay below the  $V_{TH}$  threshold until the write-zero low time  $t_{W0LMIN}$  is expired. For the most reliable communication, the voltage on the data line should not exceed  $V_{ILMAX}$  during the entire  $t_{W0L}$  or  $t_{W1L}$  window required by the slave. After the  $V_{TH}$  threshold has been crossed, the DS28E18 needs a recovery time  $t_{REC}$  before it is ready for the next time slot.

#### Slave-to-Master

A read-data time slot begins like a write-one time slot. The voltage on the data line must remain below  $V_{TL}$  until the read low time  $t_{RL}$  (read low time) is expired. During the  $t_{RL}$  window, when responding with a 0, the slave starts pulling the data line low; its internal timing generator determines when this pulldown ends and the voltage starts rising again. When responding with a 1, the slave does not hold the data line low at all, and the voltage starts rising as soon as  $t_{RL}$  is over. Note that the slave  $t_{RL}$  during a logic 1 is adequately an approximation of the 1-Wire master  $t_{W1L}$  setting.

The slave t<sub>RL</sub> plus the bus rise time on the near end and the internal timing generator of the slave on the far end define the 1-Wire master sampling window, in which the 1-Wire master performs a read from the data line. After reading from

the data line, the 1-Wire master waits until  $t_{SLOT}$  is expired. This guarantees sufficient recovery time  $t_{REC}$  for the slave to get ready for the next time slot. Note that  $t_{REC}$  specified herein applies only to a single slave attached to a 1-Wire line. For multidevice configurations,  $t_{REC}$  must be extended to accommodate the additional 1-Wire device input capacitance.

Figure 6. 1-Wire Read/Write Timing Diagrams

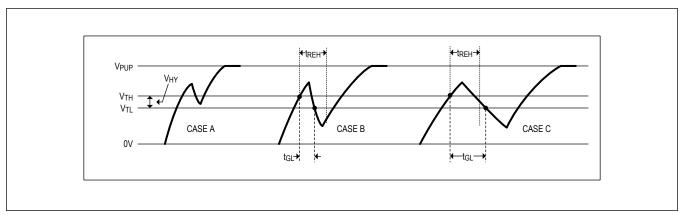

#### **Improved Network Behavior**

In a 1-Wire environment, line termination is possible only during transients controlled by the bus master (1-Wire driver). 1-Wire networks, therefore, are susceptible to noise of various origins. Depending on the physical size and topology of the network, reflections from end points and branch points can add up or cancel each other to some extent. Such

reflections are visible as glitches or ringing on the 1-Wire communication line. Noise coupled onto the 1-Wire line from external sources can also result in signal glitching. A glitch during the rising edge of a time slot can cause a slave device to lose synchronization with the master and, consequently, result in a Search ROM command coming to a dead end or cause a device-specific function command to abort. For better performance in network applications, the DS28E18 uses a 1-Wire front-end that is less sensitive to noise. The IO 1-Wire front-end has hysteresis, and a rising edge hold off delay.

- On the low-to-high transition, if the line rises above V<sub>TH</sub> but does not go below V<sub>TL</sub>, the glitch is filtered (<u>Figure 7</u>, case A.)

- The rising edge hold-off delay (nominally 100ns), t<sub>REH</sub>, filters glitches that go below V<sub>TL</sub> before t<sub>REH</sub> has expired (<u>Figure 7</u>, case B.) Effectively the device does not see the initial rise, and the t<sub>REH</sub> delay resets when the line goes below V<sub>TL</sub>.

- If the line goes below V<sub>TL</sub> after t<sub>REH</sub> has expired the glitch is not filtered and is taken as the beginning of a new time slot (<u>Figure 7</u>, case C.)

Independent of the time slot, the falling edge of the presence pulse has a controlled slew rate to reduce ringing. The falling delay is specified by  $t_{\text{FPD}}$ .

Figure 7. Noise Suppression Scheme

#### **Device Function Commands**

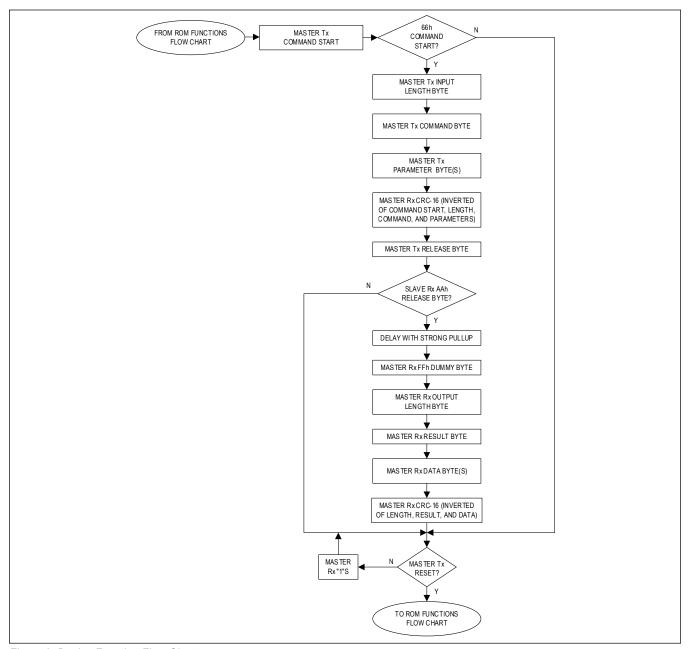

After a 1-Wire reset/presence cycle and ROM function command sequence (Figure 3 or Figure 4) is successful, a command start can be accepted and then followed by a device function command. In general, these commands follow the state flow diagram (Figure 8). Within this diagram, the data transfer is verified when writing and reading by a CRC of 16-bit type (CRC-16). The CRC-16 is computed as described in Application Note 27: Understanding and Using Cyclic Redundancy Checks with Maxim 1-Wire and iButton Products.

Figure 8. Device Function Flow Chart

Additionally, the subsequent sections will describe each device function command in detail. The device function commands are each 8-bit values and are shown in Table 1.

**Table 1. Device Function Commands**

| DEVICE COMMAND           | COMMAND CODE |

|--------------------------|--------------|

| Write Sequencer          | 11h          |

| Read Sequencer           | 22h          |

| Run Sequencer            | 33h          |

| Write Configuration      | 55h          |

| Read Configuration       | 6Ah          |

| Write GPIO Configuration | 83h          |

| Read GPIO Configuration  | 7Ch          |

| Device Status            | 7Ah          |

#### **Command Start (66h)**

Command Start is used for device function commands. After the command start byte, the next byte transmitted is the length byte. This indicates the length of both the command (i.e., device function command) and parameters. The result of the command is provide in similar format. The command start structure does not require a strong pullup (SPU) until after the release byte. After the release byte, the command is started and a command dependent delay is put into effect with the SPU power being delivered to the 1-Wire bus. The command dependent delay and SPU power is needed to execute device function commands and sequencer commands when applicable.

**Table 2. Command Start Description**

| COMMAND START        |                                                                                                                                                                                                                                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code         | 66h                                                                                                                                                                                                                                                                                                                                |

| Parameter Byte(s)    | Length byte followed by command and parameters. The first byte after the length byte is the device function command.                                                                                                                                                                                                               |

|                      | Process the command and parameters sequence. The command code is followed by a length byte followed by the device function command and parameters.                                                                                                                                                                                 |

|                      | Next, the master receives a two-byte inverted CRC-16 of the command start byte + length byte + command + parameters is sent. If the CRC-16 is correct, the master then sends the release byte (AAh).                                                                                                                               |

| Usage                | Once the release byte is received, the command is started. At that time the master must provide strong pullup on the 1-Wire to power the device. The required delay is command dependent with a minimum delay of $t_{\rm OP}$ .                                                                                                    |

|                      | After the delay, the master reads a dummy byte for clocking purposes. After the dummy byte, the command result is read, length byte first, followed by a result byte, optional result data, and an inverted CRC-16. If the command is not supported, the response will have a length of 00h followed by the CRC-16 value of FFFFh. |

| Command Restrictions | None                                                                                                                                                                                                                                                                                                                               |

| Device Operation     | Verify Release byte is AAh.<br>Start command.                                                                                                                                                                                                                                                                                      |

| Command Duration     | See t <sub>OP</sub> (command dependent).                                                                                                                                                                                                                                                                                           |

| Result               | Command dependent followed by inverted CRC-16.                                                                                                                                                                                                                                                                                     |

## **Table 3. Generic Command Start Sequence**

| Reset                                                                   |

|-------------------------------------------------------------------------|

| Presence Pulse                                                          |

| <rom select=""></rom>                                                   |

| Tx: Command Start (66h)                                                 |

| Tx: Length Byte (varies with command)                                   |

| Tx: Command                                                             |

| Tx: Parameters (varies with command)                                    |

| Rx: CRC-16 (inverted of command start, length, command, and parameters) |

| Tx: Release Byte (AAh)                                                  |

| <spu command="" delay,="" dependent=""></spu>                           |

| Rx: Dummy Byte (not used in CRC calculation)                            |

| Rx: Length Byte (varies with command)                                   |

| Rx: Result Byte (varies with command)                                   |

| Rx: Result Bata (varies with command)                                   |

| Rx: CRC-16 (inverted of length byte, result byte, and result data)      |

| Reset                                                                   |

### Write Sequencer Command (11h)

### **Table 4. Write Sequencer Description**

| WRITE SEQUENCER      |                                                                                                                                                                                                                   |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command Code         | 11h                                                                                                                                                                                                               |

| Parameter Byte(s)    | ADDR_LO, ADDR_HI, data array to write                                                                                                                                                                             |

| Usage                | This command writes up to 128-bytes to the 512-byte command sequencer SRAM starting at the specified address.                                                                                                     |

| Command Restrictions | The sum of the specified address and length must be within the command sequencer valid address range, that is to not exceed 512 bytes in the sequencer memory. If 512 bytes is exceeded, nothing will be written. |

| Device Operation     | Write up to the maximum buffer length of 128 bytes of data to the command sequencer SRAM. The command processor sets the result byte after verifying the parameters and writing the data.                         |

| Command Duration     | top                                                                                                                                                                                                               |

| Result Byte          | 77h: Invalid input or parameter AAh: Success                                                                                                                                                                      |

## Table 5. Write Sequencer Parameter: ADDR\_LO

| BIT 7   | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

|---------|-------|-------|-------|-------|-------|-------|-------|--|

| ADDR_LO |       |       |       |       |       |       |       |  |

#### ADDR\_LO: (Bits 7:0)

00h-FFh: The lower 8 bits of the target write address in the command sequencer SRAM.

## Table 6. Write Sequencer Parameter ADDR HI

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       | RFU   |       |       |       |       |       |       |

#### RFU (Bits 7:1): RFU

0000000b-1111111b: Reserved for future use.

#### ADDR\_HI: (Bit 0): Sequencer Address High Bit

0b-1b: The most significant bit of the target write address in the command sequencer SRAM.

## **Table 7. Write Sequencer Parameter: Data Array**

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

|       | DATA  |       |       |       |       |       |       |  |  |

#### **DATA: (Bits 7:0)**

00h-FFh: Byte to write to the command sequencer SRAM starting at the target write address (ADDR\_HI:ADDR\_LO).

DATA is a variable length array of bytes, *DATA[n]*, that is written to the command sequencer SRAM. The length of the array, *n*, is determined from the length parameter as part of the 1-Wire Start command. A minimum of one byte of data is required for the Write Sequencer command. The array, *DATA[n]*, is written to the command sequencer SRAM in the same order it is transmitted.

**Note:** The 1-Wire protocol transmits the data least significant bit to most significant bit. The DS28E18 1-Wire slave interface receives the 1-Wire data and writes it in little endian form to the internal command buffer first and then transfers data during the command duration to the command sequencer SRAM.

## **Table 8. Write Sequencer Command Transfer**

| Reset                                                                           |

|---------------------------------------------------------------------------------|

| Presence Pulse                                                                  |

| <rom select=""></rom>                                                           |

| Tx: Command Start (66h)                                                         |

| Tx: Length Byte (4 to 131) Command + ADDR_LO + ADDR_HI + DATA[n]                |

| Tx: Command 11h (Write Sequencer                                                |

| Tx: Parameter (ADDR_LO)                                                         |

| Tx: Parameter (ADDR_HI)                                                         |

| Tx: Data (n = 1 to 128 bytes)                                                   |

| Rx: CRC-16 (inverted of command start, length, command, parameters, data array) |

| Tx: Release Byte (AAh)                                                          |

| <delay t<sub="">OP&gt;</delay>                                                  |

| Rx: Dummy Byte (not used in CRC calculation)                                    |

| Rx: Length Byte (1)                                                             |

| Rx: Result Byte                                                                 |

| Rx: CRC-16 (inverted of length and result byte)                                 |

| Reset                                                                           |

### Read Sequencer Command (22h)

## **Table 9. Read Sequencer Description**

| READ SEQUENCER       |                                                                                                                             |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Command Code         | 22h                                                                                                                         |

| Parameter Byte(s)    | See below                                                                                                                   |

| Usage                | Read up to 128 bytes from the 512-byte command sequencer SRAM with the Read Sequencer command.                              |

| Command Restrictions | SLEN + ADDR must be less than or equal to 512. 0 ≤ SLEN ≤ 127  Note: If SLEN equals 0, the length of the read is 128 bytes. |

| Device Operation     | Validates parameters. Reads data from the command sequencer SRAM. Sets the Result byte. Returns data read.                  |

| Command Duration     | top                                                                                                                         |

| Result Byte          | 77h: Invalid input or parameter<br>AAh: Success                                                                             |

## Table 10. Read Sequencer Parameter ADDR\_LO

| BIT 7 | BIT 6   | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |  |

|-------|---------|-------|-------|-------|-------|-------|-------|--|--|

|       | ADDR_LO |       |       |       |       |       |       |  |  |

#### ADDR\_LO: (Bits 7:0)

00h-FFh: The lower 8 bits of the target read address in the command sequencer SRAM.

## Table 11. Read Sequencer Parameter Byte 2: SLEN:ADDR\_HI

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |  |

|-------|-------|-------|-------|-------|-------|-------|-------|--|

|       | SLEN  |       |       |       |       |       |       |  |

#### **SLEN: (Bits 7:1)**

00h-7Fh: The number of bytes to read from the command sequencer SRAM.

Note: Setting the SLEN field to 0 reads 128 bytes, the maximum number.

#### ADDR\_HI: (Bit 0)

0b-1b: The most significant bit of the target read address in the command sequencer SRAM. Combine the ADDR\_HI bit with the ADDR\_LO field to set the starting read address for the Read Sequencer command.

## **Table 12. Read Sequencer Command Transfer**

| Reset                                                                   |

|-------------------------------------------------------------------------|

| Presence Pulse                                                          |

| <rom select=""></rom>                                                   |

| Tx: Command Start (66h)                                                 |

| Tx: Length Byte (3)                                                     |

| Tx: Command 22h (Read Sequencer)                                        |

| Tx: Parameter (ADDR_LO)                                                 |

| Tx: Parameter (SLEN:ADDR_HI)                                            |

| Rx: CRC-16 (inverted of command start, length, command, and parameters) |

## **Table 12. Read Sequencer Command Transfer (continued)**

| Tx: Release Byte (AAh)                                             |  |  |  |  |  |  |

|--------------------------------------------------------------------|--|--|--|--|--|--|

| <delay t<sub="">OP&gt;</delay>                                     |  |  |  |  |  |  |

| Rx: Dummy Byte (not used in CRC calculation)                       |  |  |  |  |  |  |

| Rx: Length Byte $(1 \le m \le 129 \text{ max})$                    |  |  |  |  |  |  |

| Rx: Result Byte                                                    |  |  |  |  |  |  |

| Rx: Data Array up to 128 bytes (if m is > 1, receive (m-1) bytes)  |  |  |  |  |  |  |

| Rx: CRC-16 (inverted of length, result byte, and data array bytes) |  |  |  |  |  |  |