## **Product Overview**

The DW3000 IC family is a fully integrated single chip Ultra Wideband (UWB) low-power low-cost transceiver IC compliant to IEEE802.15.4-2015 and IEEE802.15.4z (BPRF mode). It can be used in 2-way ranging, TDoA and PDoA systems to locate assets to an accuracy of 10 cm.

# **Key Features**

- IEEE802.15.4-2015 UWB IEEE802.15.4z (BPRF mode)

- Supports channels 5 & 9 (6489.6 MHz & 7987.2 MHz)

- Supports 2-way ranging, TDoA and PDoA location schemes

- Low external component count

- Supports enhanced Time-of-Flight security modes

- Integrated HW AES 256

- Worldwide UWB Radio Regulatory compliance

- Low power consumption

- Data rates of 850 kbps and 6.8 Mbps

- Packet length up to 1023 bytes

- Integrated MAC support features

- Up to 38 MHz SPI interface

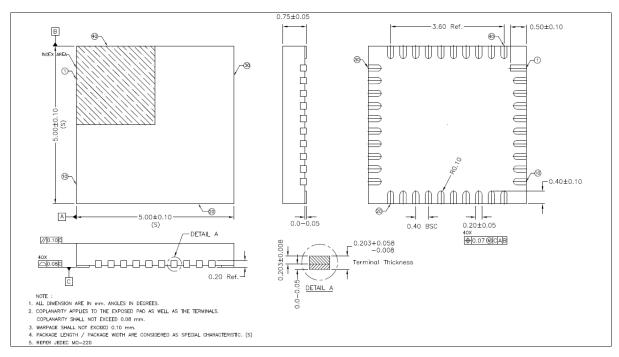

- QFN40 (5mm x 5 mm) and WLCSP52 (3.1mm x 3.5mm) package options

## **Key Benefits**

- Provides precision location and data transfer simultaneously

- Asset location to an accuracy of 10 cm

- High multipath fading immunity

- Secure ranging/distance measurement

- Supports high tag densities in RTLS

- Low cost precision location

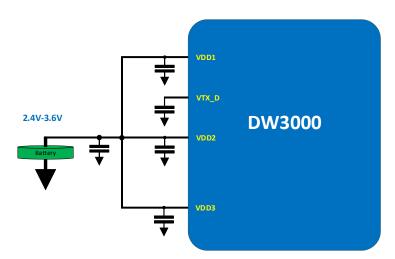

- Suitable for coin cell applications

## **Applications**

- Precision real time location systems (RTLS) using two-way ranging, TDoA or PDoA schemes in a variety of markets:

- o Healthcare

- Consumer

- Industrial

- Automotive

- Presence detection for secure entry and secure payment

- Location aware wireless sensor networks

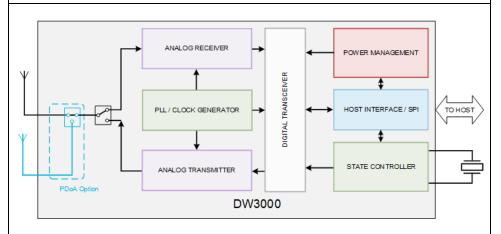

High Level Functional Diagram

# DW3000 UWB Transceiver

# **Table of Contents**

| 1 IC DESCRIPTION                        | 5           | 6 POWERING DW300033                                  |

|-----------------------------------------|-------------|------------------------------------------------------|

| 1.1 DW3000 VARIANTS                     |             | 6.1 LOWEST BILL OF MATERIALS (BOM) POWERING SCHEME35 |

| DW1000                                  | 6           | 6.2 HIGHEST EFFICIENCY POWERING SCHEME35             |

| 2 PIN CONFIGURATIONS AND FUNCTI         | ON          | 6.3 MOBILE POWERING SCHEME                           |

| DESCRIPTIONS                            |             | 6.4 Typical power profiles                           |

|                                         |             | 6.4.1 TX current profile for the minimal             |

| 3 ELECTRICAL SPECIFICATIONS             | 11          | BOM 37                                               |

| 3.1 Nominal Operating Conditions        | 11          | 6.4.2 TX current profile for high efficiency         |

| 3.2 DC CHARACTERISTICS                  |             | modes 38                                             |

| 3.3 RECEIVER AC CHARACTERISTICS         |             | 6.4.3 RX current profile39                           |

| 3.4 RECEIVER SENSITIVITY CHARACTERISTIC | cs 13       | 6.4.4 RX current profile for high efficiency         |

| REFERENCE CLOCK AC CHARACTERISTICS      |             | BOMs 39                                              |

| 3.5 TRANSMITTER AC CHARACTERISTICS      | 15          | 6.4.5 Typical TWR current profile41                  |

| 3.6 LINK BUDGET                         | 15          | 6.5 Internal Power supply distribution 42            |

| 3.7 TEMPERATURE AND VOLTAGE MONITO      | OR          | 7 APPLICATION INFORMATION43                          |

| CHARACTERISTICS                         | 16          | 7 APPLICATION INFORMATION43                          |

| 3.8 LOCATION FUNCTIONALITY CHARACTER    | RISTICS 16  | 7.1 APPLICATION CIRCUIT DIAGRAM (LOWEST BOM          |

| 3.9 ABSOLUTE MAXIMUM RATINGS            | 17          | POWERING SCHEME)43                                   |

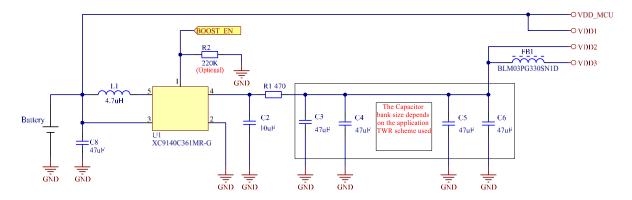

| 3.10 TYPICAL PERFORMANCE                | 17          | 7.2 BOOST CIRCUIT DIAGRAM43                          |

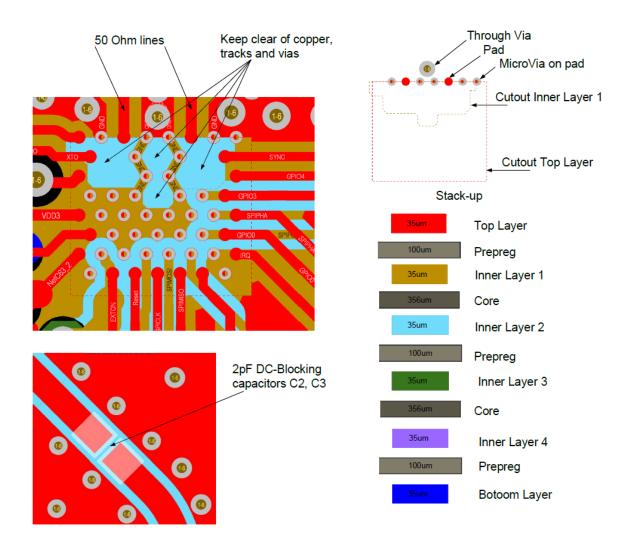

| 3.10.1 Transmit Spectrum                |             | 7.3 RECOMMENDED CHIP LAYOUT AND STACK-UP 44          |

| 3.10.2 Transmit Power Adjustme          |             | 7.3.1 WLCSP variant Stack-up44                       |

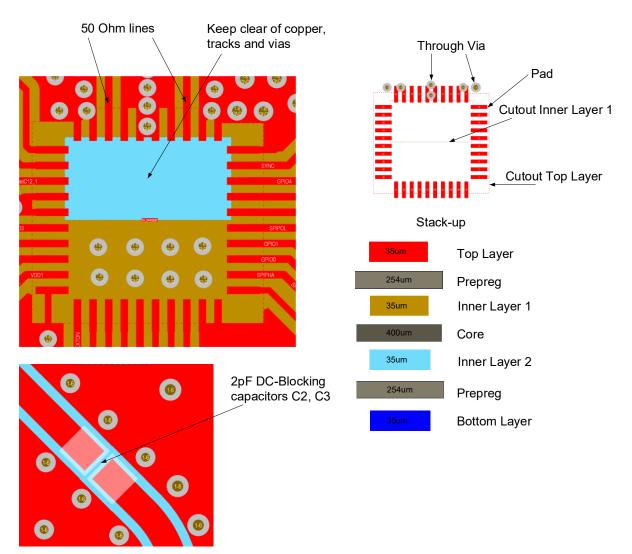

| 3.10.3 Receiver Blocking                |             | 7.3.2 QFN variant Stack-up45                         |

| 3.10.4 Ranging                          | 21          | 7.4 RECOMMENDED COMPONENTS                           |

| 4 FUNCTIONAL DESCRIPTION                | 22          | 8 REFLOW PROFILES47                                  |

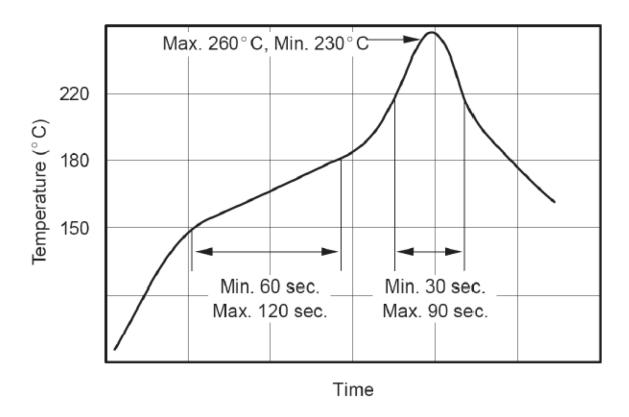

| 4.1 PHYSICAL LAYER MODES                | 22          | 8.1 REFLOW PROFILE OF THE WLCSP PACKAGE 47           |

| 4.2 SUPPORTED CHANNELS AND BANDWIE      |             | 8.2 REFLOW PROFILE OF THE QFN PACKAGE 47             |

| 4.3 SUPPORTED BIT RATES AND PULSE RE    |             | ·                                                    |

| FREQUENCIES (PRF)                       |             | 9 PACKAGING & ORDERING INFORMATION48                 |

| 4.4 SYMBOL TIMINGS                      |             | 9.1 PACKAGE DIMENSIONS WLCSP48                       |

| 4.5 FRAME FORMAT IEEE802.15.4-201       | 1,          | 9.2 QFN CHIP VARIANT49                               |

| IEEE802.15.4-2015                       |             | 9.2.1 Package Dimensions QFN49                       |

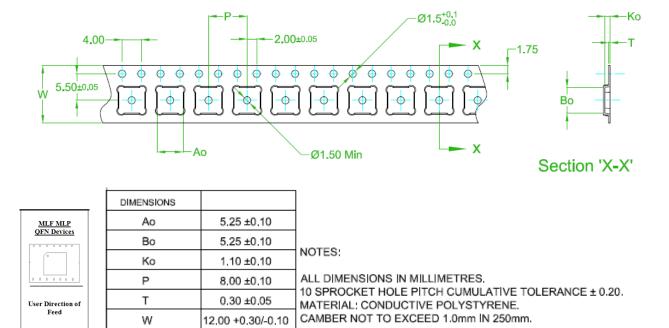

| 4.6 PACKET FORMATS OF IEEE STD 802.1    | .5.4z™ . 23 | 9.2.2 Tape and Reel packaging                        |

| 4.7 PROPRIETARY LONG FRAMES             | 23          | information: QFN chip variant49                      |

| 4.8 NO DATA FRAMES                      | 23          | 9.2.3 Tape and Reel packaging                        |

| 4.9 HOST CONTROLLER INTERFACE           | 24          | information: WLCSP chip variant51                    |

| 4.9.1 SPI Functional Description        | 24          | 9.2.4 WLCSP, QFN Device Package Marking              |

| 4.9.2 SPI Timing Parameters             | 24          | 53                                                   |

| 4.9.3 SPI Operating Modes               | 25          | 10 GLOSSARY54                                        |

| 4.9.4 SPI Transaction Formatting        |             | 10 GEOSSANT                                          |

| 4.9.5 GPIO and SPI I/O internal po      | ull         | 11 REFERENCES55                                      |

| up/down                                 |             | 12 DOCUMENT HISTORY55                                |

| 4.10 REFERENCE CRYSTAL OSCILLATOR       |             |                                                      |

| 4.10.1 Calculation of external ca       | •           | 13 FURTHER INFORMATION56                             |

| values for frequency trim               | 29          |                                                      |

| 5 OPERATIONAL STATES                    | 31          |                                                      |

| 5.1 OVERVIEW                            | 31          |                                                      |

| 5.2 OPERATING STATE TRANSITIONS         | 32          |                                                      |

# **List of Figures**

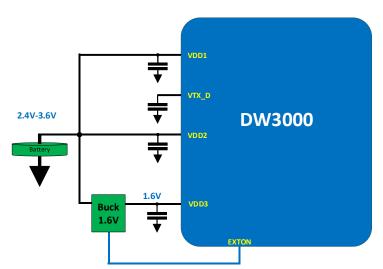

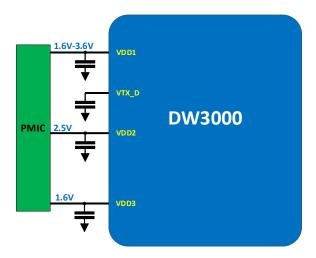

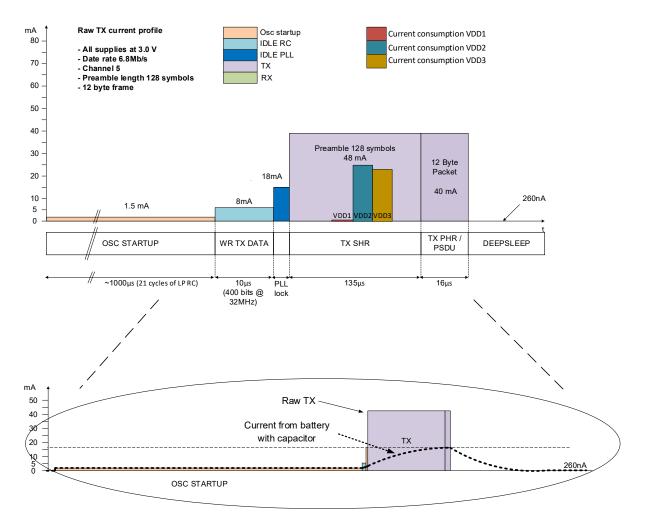

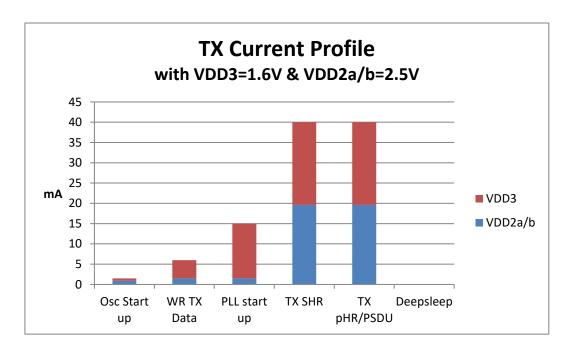

| IGURE 1: IC BLOCK DIAGRAM5                      | FIGURE 24: SINGLE O/P BUCK SMPS OPTION35            |

|-------------------------------------------------|-----------------------------------------------------|

| IGURE 2: THE QFN TOP VIEW PIN ASSIGNMENTS       | FIGURE 25: MOBILE OPTION36                          |

| IGURE 3: THE WLCSP PIN ASSIGNMENTS              | FIGURE 26: CURRENT PROFILE WHEN TRANSMITTING A      |

| IGURE 4: TYPICAL TRANSMIT SPECTRUM CHANNEL 5 17 | FRAME (6.8MBPS) IN LOWEST BOM USE CASE 37           |

| IGURE 5: TYPICAL TRANSMIT SPECTRUM CHANNEL 9 18 | FIGURE 27: CURRENT CONSUMPTION DURING TX FOR HIGH   |

| IGURE 6 TX POWER COARSE AND FINE GAIN SETTINGS  | EFFICIENCY POWERING MODES38                         |

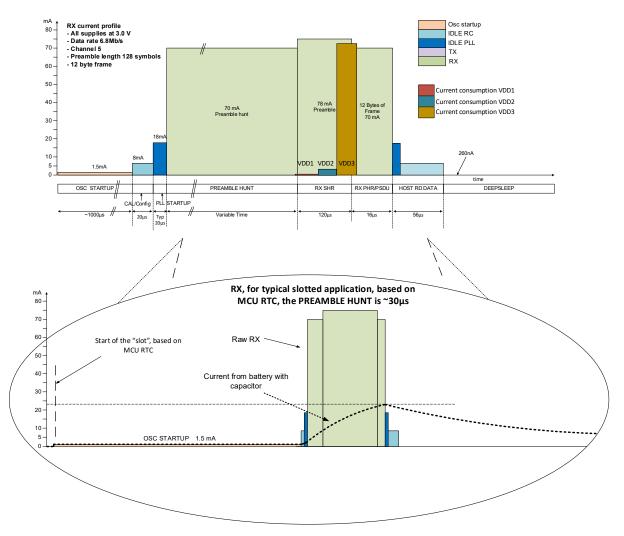

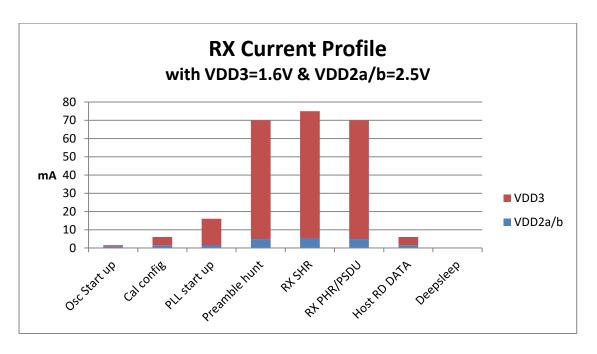

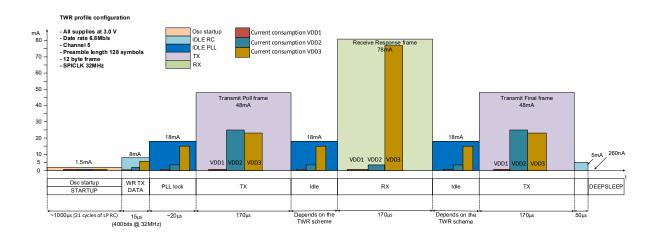

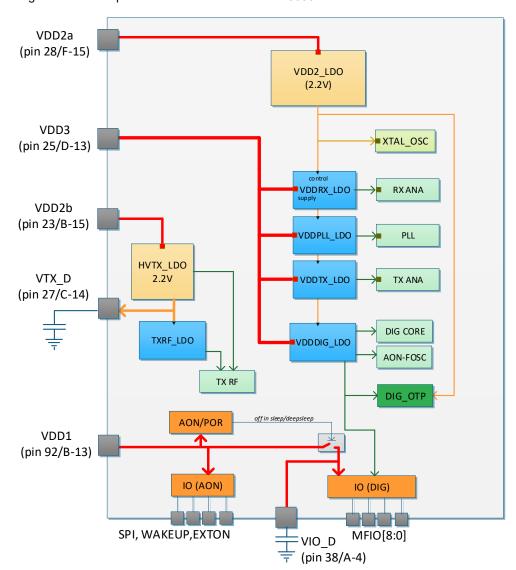

| CHANNEL 5 19                                    | FIGURE 28: CURRENT PROFILE FOR RECEIVING A FRAME 39 |

| IGURE 7 TX POWER COARSE AND FINE GAIN SETTINGS  | FIGURE 29: CURRENT CONSUMPTION DURING RX FOR HIGH   |

| CHANNEL 9 19                                    | EFFICIENCY POWERING MODES40                         |

| IGURE 8 BLOCKING PERFORMANCE CHANNEL 5          | FIGURE 30 CURRENT PROFILE OF INITATOR IN THE DS-TWR |

| IGURE 9 BLOCKING PERFORMANCE CHANNEL 9          | WITH EMBEDDED DATA TO FRAMES41                      |

| IGURE 10 RANGING PERFORMANCE CHANNEL 5 21       | FIGURE 31: INTERNAL POWER DISTRIBUTION42            |

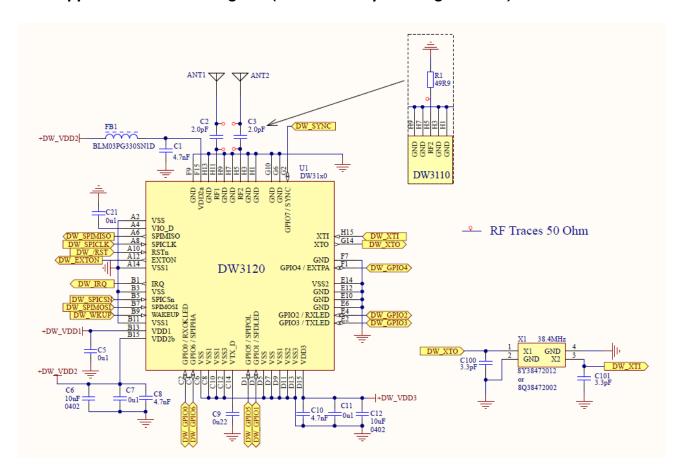

| IGURE 11 RANGING PERFORMANCE CHANNEL 9 21       | FIGURE 32: DW3000 WLCSP APPLICATION CIRCUIT 43      |

| IGURE 12: IEEE802.15.4-2011 PPDU STRUCTURE 23   | FIGURE 33 BOOST CIRCUIT43                           |

| IGURE 13: SPI TIMING DIAGRAM24                  | FIGURE 34 RECOMMENDED WLCSP STACK-UP44              |

| IGURE 14: DW3000 SPIPHA=0 TRANSFER PROTOCOL 25  | FIGURE 35 RECOMMENDED QFN STACK-UP45                |

| IGURE 15: DW3000 SPIPHA=1 TRANSFER PROTOCOL 26  | FIGURE 36 REFLOW PROFILE OF THE WLCSP PACKAGE 47    |

| IGURE 16: SPI COMMAND FORMATTING                | FIGURE 37: PACKAGE DIMENSIONS WLCSP48               |

| IGURE 17: SPI AND GPIO PULL UP/DOWN             | FIGURE 38: PACKAGE DIMENSIONS QFN49                 |

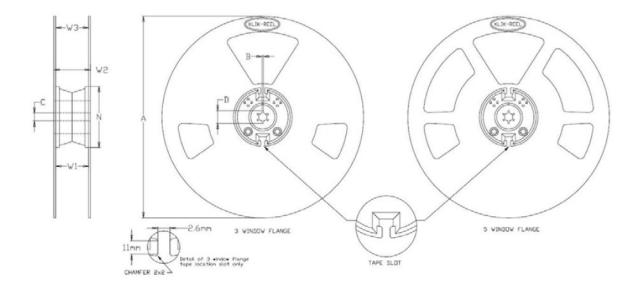

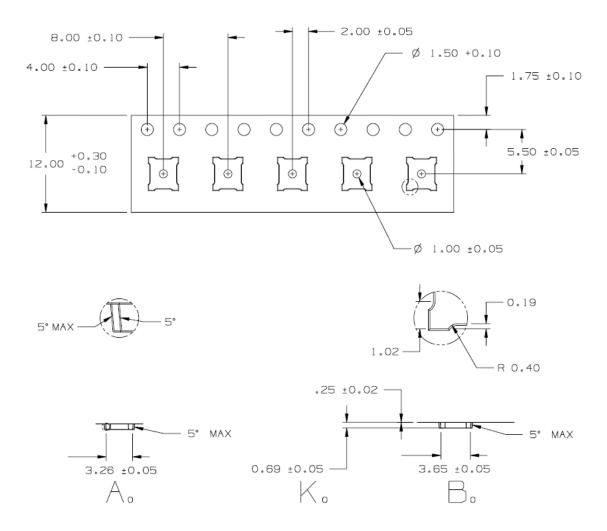

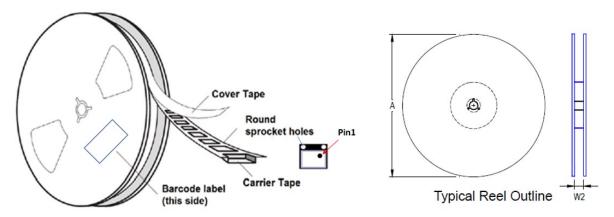

| IGURE 18 CRYSTAL MODEL                          | FIGURE 39 QFN TAPE ORIENTATION AND DIMENSIONS 49    |

| IGURE 19 CRYSTAL TRIM PLOT30                    | FIGURE 40 QFN REEL INFORMATION50                    |

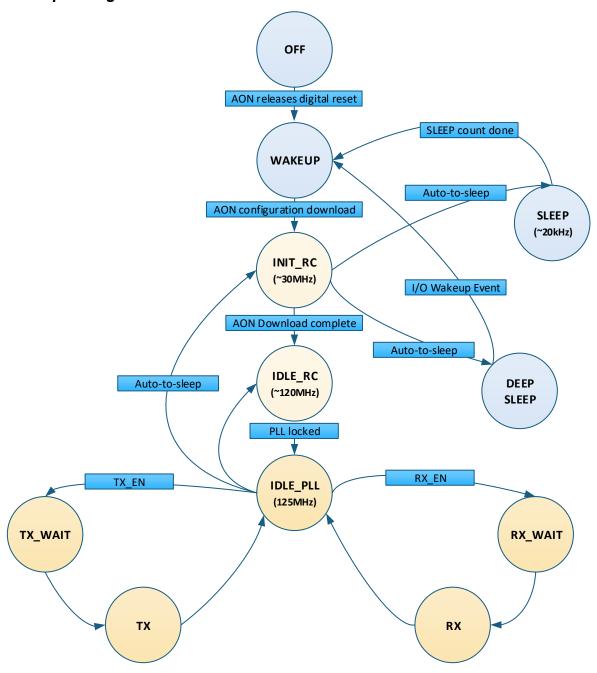

| IGURE 20: OPERATING STATE TRANSITIONS           | FIGURE 41 WLCSP TAPE ORIENTATION AND DIMENSIONS51   |

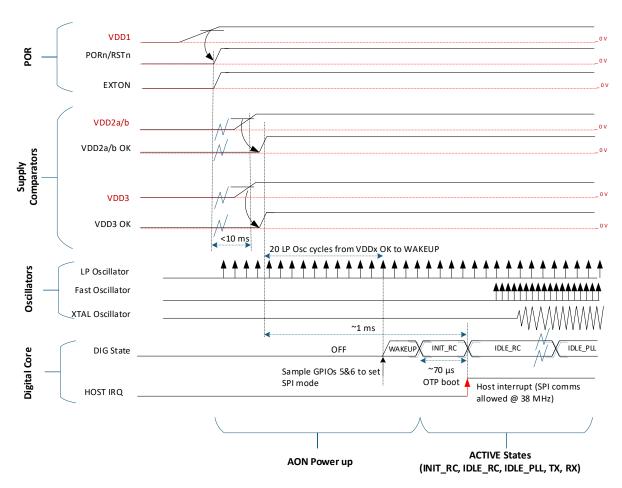

| IGURE 21: TIMING DIAGRAM FOR COLD START POR 33  | FIGURE 42 WLCSP REEL INFORMATION                    |

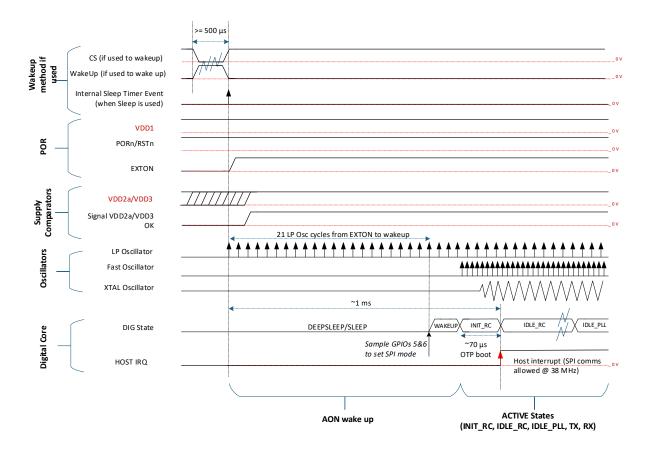

| IGURE 22 TIMING DIAGRAM FOR WARM START 34       | FIGURE 43: DEVICE PACKAGE MARKINGS53                |

| IGURE 23: LOWEST BOM POWERING OPTION            |                                                     |

## **List of Tables**

| TABLE 1: DW3000 VARIANTS                             | 6  |

|------------------------------------------------------|----|

| TABLE 2: DW3000 QFN & WLCSP PIN FUNCTIONS            | 8  |

| TABLE 3: ABBREVIATIONS                               | 10 |

| TABLE 4: NOMINAL OPERATING CONDITIONS                |    |

| TABLE 5: DC CHARACTERISTICS                          | 11 |

| TABLE 6: RECEIVER AC CHARACTERISTICS                 | 12 |

| TABLE 7 TEST CONDITIONS OF THE RX SENSITIVITY        |    |

| MEASUREMENTS                                         | 13 |

| TABLE 8: RX SENSITIVITY CHARACTERISTICS (CHANNEL 5). | 13 |

| TABLE 9: RX SENSITIVITY CHARACTERISTICS (CHANNEL 9). | 13 |

| TABLE 10: REFERENCE CLOCK AC CHARACTERISTICS         | 14 |

| TABLE 11: TRANSMITTER AC CHARACTERISTICS             | 15 |

| TABLE 12: TYPICAL LINK BUDGET FOR DW3110             | 15 |

| TABLE 13: TEMPERATURE AND VOLTAGE MONITOR            |    |

| CHARACTERISTICS                                      | 16 |

| TABLE 14: LOCATION ACCURACY CHARACTERISTICS          | 16 |

| TABLE 15: ABSOLUTE MAXIMUM RATINGS                   | 17 |

| TABLE 16 UWB CHANNELS SUPPORTED                      | 22 |

| TABLE 17 PRF AND DATA RATES SUPPORTED                | 22 |

| TABLE 18 DW3000 SYMBOL TIMINGS DURATION              | 22 |

| TABLE 19 SPI TIMING PARAMETERS                       | 25 |

| TABLE 21 SPI MODE CONFIGURATION                      | 25 |

| TABLE 22: OPERATING STATES                           | 31 |

| TABLE 23 RECOMMENDED COMPONENTS                      | 46 |

| TABLE 24 CRITICAL PARAMETERS FOR LEAD FREE SOLDER    | OF |

| THE WLSCP PACKAGE                                    | 47 |

| TABLE 25: GLOSSARY OF TERMS                          | 54 |

| TABLE 26: DOCUMENT HISTORY                           | 55 |

#### **DOCUMENT INFORMATION**

#### Disclaimer

Decawave reserves the right to change product specifications without notice. As far as possible changes to functionality and specifications will be issued in product specific errata sheets or in new versions of this document. Customers are advised to check with Decawave for the most recent updates on this product.

Copyright © 2020 Decawave Ltd

#### LIFE SUPPORT POLICY

Decawave products are not authorized for use in safety-critical applications (such as life support) where a failure of the Decawave product would reasonably be expected to cause severe personal injury or death. Decawave customers using or selling Decawave products in such a manner do so entirely at their own risk and agree to fully indemnify Decawave and its representatives against any damages arising out of the use of Decawave products in such safety-critical applications.

**Caution!** ESD sensitive device. Precaution should be used when handling the device in order to prevent permanent damage.

#### **REGULATORY APPROVALS**

The DW3000, as supplied from Decawave, has not been certified for use in any particular geographic region by the appropriate regulatory body governing radio emissions in that region although it is capable of such certification depending on the region and the manner in which it is used.

All products developed by the user incorporating the DW3000 must be approved by the relevant authority governing radio emissions in any given jurisdiction prior to the marketing or sale of such products in that jurisdiction and user bears all responsibility for obtaining such approval as needed from the appropriate authorities.

#### **TRADEMARKS**

FiRa, FiRa Consortium, the FiRa logo, the FiRa Certified logo, and FiRa tagline are trademarks or registered trademarks of FiRa Consortium or its licensor(s)/ supplier(s) in the US and other countries and may not be used without permission. All other trademarks, service marks, and product or service names are trademarks or registered trademarks of their respective owners.

# 1 IC DESCRIPTION

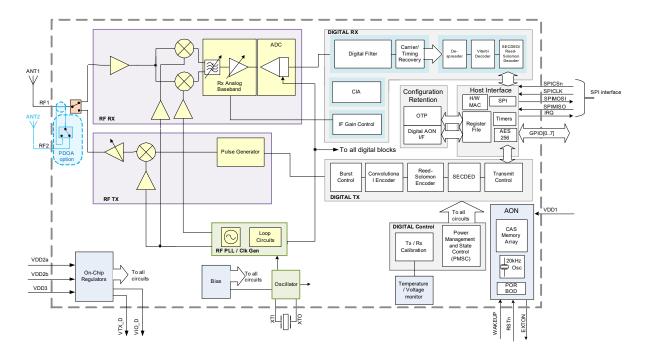

DW3000 is a fully integrated low-power, single chip CMOS RF 6.5GHz-8GHz IR-UWB transceiver IC compliant with the IEEE 802.15.4-2015 (HRP UWB PHY), IEEE 802.15.4z and IEEE 802.15.8 standards.

DW3000 consists of an analog front end containing a receiver and a transmitter and a digital back end that interfaces to an off-chip host processor. A TX/RX switch is used to connect the receiver or transmitter to the antenna port. Temperature and voltage monitors are provided on-chip.

The receiver consists of an RF front end which amplifies the received signal in a low-noise amplifier before down-converting it directly to baseband. The receiver is optimized for wide bandwidth, high linearity and low noise figure. This allows each of the supported IEEE802.15.4-2015 UWB channels to be down converted with minimum additional noise and distortion. The baseband signal is demodulated and the resulting received data is made available to the host controller via SPI.

The transmit pulse train is generated by applying digitally encoded transmit data to the analog pulse generator. The pulse train is up-converted to a carrier generated by the synthesizer and centred on one of the permitted IEEE802.15.4-2015 UWB channels. The modulated RF waveform is amplified before transmission from the external antenna.

A variant of the IC is available which has two RF antenna ports and is used for Phase Difference of Arrival (PDoA) applications. In this variant the receiver switches between antenna ports to enable a PDoA measurement.

The IC has an on-chip One-Time Programmable (OTP) memory. This memory can be used to store calibration data such as TX power level and crystal initial frequency error adjustment.

Figure 1: IC Block Diagram

The Always-On (AON) memory is 256 bytes and can be used to retain DW3000 configuration data during the lowest power operational states. The AON can operate directly from battery. This data is downloaded during crystal start up automatically.

DW3000 contains a phase-locked-loop (PLL) with integrated loop filters. This PLL provides the RF local oscillator signals for the Rx Mixer and the Tx RF frequency carrier to the Tx mixer. The channel information signal defines the output channel frequency as follows; channel 5 = 6489.6 MHz, channel 9 = 7987.2 MHz

The DW3000 has various debug and test options (RF loopback, event counters. test modes and more) and gives access to internal signals for on-the-bench debugging and to simplify production test.

The DW3000 incorporates Time Stamp system security features to prevent all known hacking type attacks such as 'imposter', 'cicada', 'parasite' 'record & replay' attacks etc.

The host interface includes a peripheral-only SPI for device communications and configuration. Several MAC features are implemented including CRC generation, CRC checking and receive frame filtering.

#### 1.1 DW3000 Variants

The following DW3000 variants exists:

Table 1: DW3000 variants

| IC Variant | Type of package | Number of<br>balls/pads PDoA support |     | Operating<br>Temperature |

|------------|-----------------|--------------------------------------|-----|--------------------------|

| DW3110     | WLCSP           | 52                                   | No  |                          |

| DW3120     | WLCSP           | 52                                   | Yes |                          |

| DW3210     | QFN             | 40                                   | No  | -40°C to +85°C           |

| DW3220     | QFN             | 40                                   | Yes |                          |

# 1.2 DW3000 Backwards compatibility with DW1000

DW3000 is backward compatible with DW1000 on channel 5 and for data rates of 6.8 Mb/s and 850 kb/s.

# 2 PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

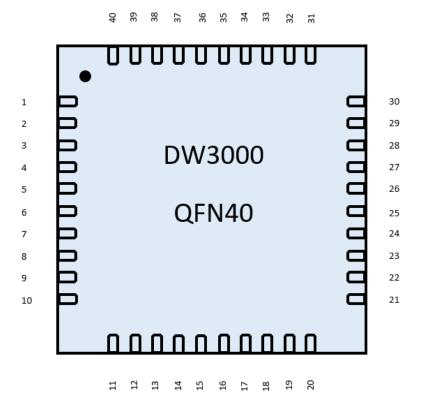

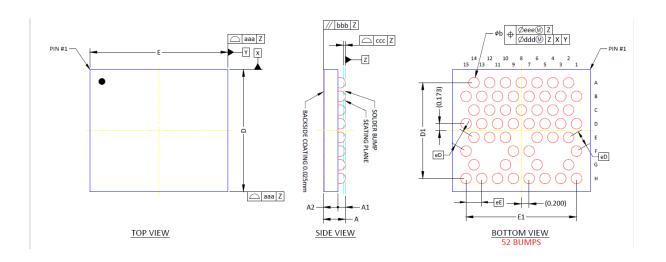

The DW3000 chip can be supplied in two packages, QFN (40 pads) or WLSCP (52 balls). The pin assignments for packages is illustrated on Figure 2 and Figure 3 and the description is given in the Table 2 below.

Figure 2: The QFN Top view pin assignments

#### DEADBUG (BUMP UP/BOTTOM) VIEW A14 A2 A10 A6 B15 C12 C10 C8 C2 D13 D11 D9 D7 D5 D3 D1 E2 E14 E12 E10 E6 E4 F7 F15 F9 G14 G10 G6 G2 H15 НЗ Н1 H11

Figure 3: The WLCSP pin assignments

#### Table 2: DW3000 QFN & WLCSP Pin functions

| Signal<br>Name                | QFN<br>Pin<br>#      | WLCSP<br>Ball<br>#               | I/O Type<br>(default) | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------|----------------------|----------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRQ                           | 1                    | B-1                              | DIO (O-L)             | Interrupt request output from the DW3000 to the host processor. By default IRQ is an active-high output but may be configured to be active low if required. For correct operation in SLEEP and DEEPSLEEP modes it should be configured for active high operation. This pin will float in SLEEP and DEEPSLEEP states and may cause spurious interrupts on the host unless pulled low externally (100k $\Omega$ recommended). When the IRQ functionality is not being used the pin may be reconfigured as a general purpose I/O line², GPIO8. |

| GPIO6 /<br>EXTRXE /<br>SPIPHA | 2                    | C-4                              | DIO (I)               | General purpose I/O pin². On power-up it acts as the SPIPHA (SPI phase selection) pin for configuring the SPI mode of operation. It may be configured for use as EXTRXE (External Receiver Enable). This pin goes high when the DW3000 is in receive mode. After power-up, the pin will default to a General Purpose I/O pin.                                                                                                                                                                                                               |

| GPIO0/<br>RXOKLED             | 3                    | C-2                              | DIO (I)               | General purpose I/O pin². It may be configured for use as a RXOKLED driving pin that can be used to light a LED on reception of a good frame.                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO1/<br>SFDLED              | 4                    | D-3                              | DIO (I)               | General purpose I/O pin². It may be configured for use as a SFDLED driving pin that can be used to light a LED when SFD (Start Frame Delimiter) is found by the receiver.                                                                                                                                                                                                                                                                                                                                                                   |

| GPIO5 /<br>EXTTXE /<br>SPIPOL | 5                    | D-1                              | DIO (I)               | General purpose I/O pin². On power-up it acts as the SPIPOL (SPI polarity selection) pin for configuring the SPI operation mode. After power-up, the pin will default to a General Purpose I/O pin. It may be configured for use as EXTTXE (External Transmit Enable). This pin goes high when the DW3000 is in transmit mode.                                                                                                                                                                                                              |

| GPIO2 /<br>RXLED              | 6                    | E-4                              | DIO (I)               | General purpose I/O pin². It may be configured for use as a RXLED driving pin that can be used to light a LED during receive mode.                                                                                                                                                                                                                                                                                                                                                                                                          |

| GPIO3 /<br>TXLED              | 7                    | E-2                              | DIO (I)               | General purpose I/O pin². It may be configured for use as a TXLED driving pin that can be used to light a LED following a transmission.                                                                                                                                                                                                                                                                                                                                                                                                     |

| GPIO4/<br>EXTPA               | 8                    | F-1                              | DIO (I)               | General purpose I/O pin².<br>It may be configured for use as EXTPA (External Power Amplifier). This pin can enable an external Power Amplifier.                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO7/<br>SYNC                | 9                    | G-2                              | DIO (I)               | The SYNC input pin is used for external synchronisation. When the SYNC input functionality is not being used this pin may be reconfigured as a general purpose I/O pin², GPIO7. This pin is internally pulled down.                                                                                                                                                                                                                                                                                                                         |

| GND                           | 10<br>11<br>12       | E-6<br>E-10<br>E-12<br>F7        | G                     | RF ground pin <sup>1</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RF2                           | 13                   | H-5                              | AIO                   | RF port for antenna 2 (50 $\Omega$ single ended RF connection). When in use for PDoA, a series 2pF is required on the pin. In non PDoA chip variants, a 2pF is <b>not</b> required, but it should be grounded with 50 $\Omega$ . A 50 $\Omega$ PCB trace from the RF2 port to the termination resistor is also required in this case.                                                                                                                                                                                                       |

| GND                           | 14<br>15<br>16<br>17 | F-9<br>G-6<br>G-10<br>H-1<br>H-3 | G                     | RF ground pin <sup>1</sup> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RF1                           | 18                   | H-11                             | AIO                   | RF port for antenna 1 (50 $\Omega$ single ended connection). A 2pF is required on the pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Signal<br>Name      | QFN<br>Pin<br># | WLCSP<br>Ball<br>#                 | I/O Type<br>(default) | DESCRIPTION                                                                                                                                                                                                                                                            |  |

|---------------------|-----------------|------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| GND                 | 19<br>20        | H-7<br>H-9<br>H-13                 | G                     | RF ground pin <sup>1</sup> .                                                                                                                                                                                                                                           |  |

| XTI                 | 21              | H-15                               | Al                    | Reference crystal input or external reference overdrive pin.                                                                                                                                                                                                           |  |

| XTO                 | 22              | G-14                               | Al                    | Reference crystal output.                                                                                                                                                                                                                                              |  |

| VDD2a               | 28              | F-15                               | Р                     | Voltage Supply (2.4V to 3.6V) <sup>1</sup> . F-15 requires isolation with a ferrite from B-15.                                                                                                                                                                         |  |

| VDD2b               | 23              | B-15                               | Р                     | Voltage Supply (2.4V to 3.6V) 1.                                                                                                                                                                                                                                       |  |

| VSS2                | 24              | D-11<br>E-14                       | G                     | Ground return for VDD2.                                                                                                                                                                                                                                                |  |

| VSS3                | 25              | C-12<br>D-13                       | G                     | Ground return for VDD3.                                                                                                                                                                                                                                                |  |

| VDD3                | 26              | D-15                               | Р                     | Voltage Supply (1.5V to 3.6V) <sup>1</sup> .                                                                                                                                                                                                                           |  |

| VTX_D               | 27              | C-14                               | PD                    | TX supply decoupling. Requires external capacitor to ground¹.                                                                                                                                                                                                          |  |

| VDD1                | 29              | B-13                               | Р                     | Main power supply (1.62V – 3.6V). This pin also supplies the device I/O's and Always-On domain¹. The following I/Os are supplied by this pin: WAKEUP, EXTON, RSTn, SPICLK, SPICSn, SPICDI and SPICDO.                                                                  |  |

| VSS1                | 30              | A-14<br>B-11<br>C-8<br>C-10<br>D-9 | G                     | Ground return for VDD1.                                                                                                                                                                                                                                                |  |

| EXTON               | 31              | A-12                               | DO (O-L)              | External device enable. Asserted during wake up process and held active until device enters sleep mode. Can be used to control external DC-DC converters or other circuits that are not required when the device is in sleep mode so as to minimise power consumption. |  |

| WAKEUP              | 32              | B-9                                | DI                    | When asserted into its active high state, the WAKEUP pin brings the DW3000 out of SLEEP or DEEPSLEEP states into operational mode. This should be connected to ground if not used.                                                                                     |  |

| RSTn                | 33              | A-10                               | DIO (O-H)             | Reset pin. Active Low Output. May be pulled low by external open drain driver to reset the DW3000. Must not be pulled high by external source.                                                                                                                         |  |

| SPICLK              | 34              | A-8                                | DI                    | SPI peripheral clock input.                                                                                                                                                                                                                                            |  |

| SPICDI<br>(SPIMOSI) | 35              | B-7                                | DI                    | SPI peripheral data input.                                                                                                                                                                                                                                             |  |

| SPICDO<br>(SPIMISO) | 36              | A-6                                | D0 (O-L)              | SPI peripheral data output.                                                                                                                                                                                                                                            |  |

| SPICSn              | 37              | B-5                                | DI                    | SPI chip select. This is an active low enable input. The high-to-low transition on SPICSn signals the start of a new SPI transaction. SPICSn can also act as a wake-up signal to bring DW3000 out of either SLEEP or DEEPSLEEP states.                                 |  |

| VIO_D               | 38              | A-4                                | PD                    | IO supply decoupling. Internally connected to the VDD1 with switch to allow disconnect from VDD1 for ultra-low power consumption mode.                                                                                                                                 |  |

| VSS                 | 39<br>40        | A-2<br>B-3<br>C-6<br>D-5<br>D-7    | G                     | Ground return for internal digital supply <sup>1</sup> .                                                                                                                                                                                                               |  |

© Decawave 2020 DW3000 Datasheet Page 9 Version 1.1

<sup>&</sup>lt;sup>1</sup>Reference to the schematics and the layout <sup>2</sup>GPIO pins are not suitable to drive LEDs directly. See Table 5 for details of the maximum current limit.

Table 3: Abbreviations

| ABBREVIATION                                                         | EXPLANATION                                 |  |  |  |

|----------------------------------------------------------------------|---------------------------------------------|--|--|--|

| Al                                                                   | Analog Input.                               |  |  |  |

| AIO                                                                  | Analog Input / Output.                      |  |  |  |

| AO                                                                   | Analog Output.                              |  |  |  |

| DI                                                                   | Digital Input.                              |  |  |  |

| DIO                                                                  | Digital Input / Output.                     |  |  |  |

| DO                                                                   | Digital Output.                             |  |  |  |

| G                                                                    | Ground.                                     |  |  |  |

| Р                                                                    | Power Supply.                               |  |  |  |

| PD                                                                   | Power Decoupling.                           |  |  |  |

| NC                                                                   | No Connect.                                 |  |  |  |

| O-L                                                                  | Defaults to output, low level after reset.  |  |  |  |

| O-H                                                                  | Defaults to output, high level after reset. |  |  |  |

| I                                                                    | Defaults to input.                          |  |  |  |

| Note: Any signal with the suffix 'n' indicates an active low signal. |                                             |  |  |  |

# 3 ELECTRICAL SPECIFICATIONS

## 3.1 Nominal Operating Conditions

**Table 4: Nominal Operating Conditions**

| Parameter                                                    | Min  | Тур. | Max | Units    | Condition/Note                                                           |

|--------------------------------------------------------------|------|------|-----|----------|--------------------------------------------------------------------------|

| Operating temperature                                        | -40  |      | 85  | Ç        |                                                                          |

| Storage temperature                                          | -65  |      | 150 | ů        |                                                                          |

| Supply voltage VDD1                                          | 1.62 | 3.0  | 3.6 | V        |                                                                          |

| Supply voltage VDD2a and VDD2b                               | 2.4  | 3.0  | 3.6 | V        |                                                                          |

| Supply voltage VDD3                                          | 1.5  | 3.0  | 3.6 | <b>V</b> |                                                                          |

| Voltage on GPIO0-5, WAKEUP,<br>RSTn, SPICSn, SPIMOSI, SPICLK |      |      | 3.6 | ٧        | Note that 3.6 V is the max voltage that should be applied to these pins. |

Note: Unit operation is guaranteed by design when operating within these ranges. Sufficient headroom for any power supply voltage ripple should be considered in system designs.

#### 3.2 DC Characteristics

T<sub>amb</sub> = 25 °C, all supplies at 3.0V

**Table 5: DC Characteristics**

| Parameter                                     | Min.          | Tyn  | Max. | Units                   | Condition/Note                                                                                |

|-----------------------------------------------|---------------|------|------|-------------------------|-----------------------------------------------------------------------------------------------|

|                                               | win.          | Тур. | wax. | Units                   | Condition/Note                                                                                |

| Supply current DEEP SLEEP mode                |               | 260  |      | nA                      |                                                                                               |

| Supply current SLEEP mode                     |               | 850  |      |                         | -                                                                                             |

| Supply current IDLE mode channel 5            |               | 18   |      | -                       |                                                                                               |

| Supply current IDLE mode channel 9            |               | 32   |      | mA                      |                                                                                               |

| Supply current IDLE-RC mode                   |               | 8    |      | -                       |                                                                                               |

| Supply current OSC start-up                   |               | 1.5  |      |                         |                                                                                               |

| Current single frame Tx/Rx with 47u           | F capacit     | or   |      |                         |                                                                                               |

| TX CH5                                        |               | 14   |      |                         | Refer to section 6.4.1 for details                                                            |

| TX CH9                                        |               | 17   |      |                         | of single TX frame configuration.                                                             |

| RX CH5                                        |               | 16   |      | - mA                    | Refer to section 6.4.3 for details                                                            |

| RX CH9                                        |               | 19   |      |                         | of single RX frame configuration.                                                             |

| Peak current continuous Tx/Rx                 | I.            | 1    |      | 1                       |                                                                                               |

| TX CH5 (nominal power<br>@ -41.3dBm/MHz) VDD2 |               | 23   |      |                         |                                                                                               |

| TX CH5 (nominal power<br>@ -41.3dBm/MHz) VDD3 |               | 25   |      |                         |                                                                                               |

| TX CH5 (maximum power @ -32dBm/MHz). VDD2     |               | 29   |      |                         |                                                                                               |

| TX CH5 (maximum power @ -32dBm/MHz). VDD3     |               | 25   |      | as test mode. In normal | Continuous TX mode is only used as test mode. In normal device operation the TX is powered up |

| TX CH9 (nominal power @ -41.3dBm/MHz). VDD2   |               | 24   |      | mA                      | for a frame transmission and then powered down.                                               |

| TX CH9 (nominal power @ -41.3dBm/MHz). VDD3   |               | 35   |      |                         |                                                                                               |

| TX CH9 (maximum power @ -32dBm/MHz). VDD2     |               | 29   |      |                         |                                                                                               |

| TX CH9 (maximum power @ -32dBm/MHz). VDD3     |               | 35   |      |                         |                                                                                               |

| RX CH5                                        |               | 72   |      |                         |                                                                                               |

| RX CH9                                        |               | 88   |      |                         |                                                                                               |

| Digital input voltage high                    | 0.7 *<br>VDD1 |      |      | V                       |                                                                                               |

| Parameter                    | Min.          | Тур. | Max.          | Units | Condition/Note                                                                                                                        |

|------------------------------|---------------|------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| Digital input voltage low    |               |      | 0.3 *<br>VDD1 |       |                                                                                                                                       |

| Digital output voltage high  | 0.7 *<br>VDD1 |      |               |       | Assumes 500 Ω load.                                                                                                                   |

| Digital output voltage low   |               |      | 0.3*<br>VDD1  |       |                                                                                                                                       |

| Digital output drive current |               |      |               |       |                                                                                                                                       |

| GPIOx, IRQ                   |               |      | 0.8           | mA    | While these IO can drive higher currents than specified, this value should be considered a maximum for continuously loaded operation. |

| SPICDO                       | 8             | 10   |               |       |                                                                                                                                       |

| EXTON                        | 3             | 4    |               |       |                                                                                                                                       |

Note: Peak supply currents quoted can be significantly reduced if VDD3 is supplied from a high efficiency SMPS at 1.6V for example.

## 3.3 Receiver AC Characteristics

**Table 6: Receiver AC Characteristics**

| Parameter                                        | Min. | Тур.   | Max. | Units | Condition/Note                                                                         |

|--------------------------------------------------|------|--------|------|-------|----------------------------------------------------------------------------------------|

| Centre Frequency Channel 5                       |      | 6489.6 |      | MHz   |                                                                                        |

| Centre Frequency Channel 9                       |      | 7987.2 |      | MHz   |                                                                                        |

| Channel bandwidths                               |      | 499.2  |      | MHz   | Programmable.                                                                          |

| Input P1dB compression point. Channel 5          |      | -25    |      | dBm   | Measured at IC input.                                                                  |

| Input P1dB compression point. Channel 9          |      | -32    |      | dBm   | Measured at IC input.                                                                  |

| In-band blocking level                           |      | -80    |      | dBm   | Chip referred (power at the pin) to give 1% PER with 3dB desense.                      |

| Out-of-band blocking level                       |      | -17    |      | dBm   | Chip referred (power at the pin) to give 1% PER with 3dB desense (see figure 8 and 9). |

| Relative velocity between Receiver & Transmitter | 0    |        | 500  | m/s   | 64 preamble 6.8 Mbps, 12 bytes.                                                        |

## 3.4 Receiver Sensitivity Characteristics

The receiver sensitivity measured at the 1% Packet Error Rate (PER).

Table 7 Test conditions of the Rx sensitivity measurements

| Parameter                                    | Value                               |

|----------------------------------------------|-------------------------------------|

| Ambient Temperature                          | 25 °C                               |

| Supply voltage                               | 3.0V                                |

| PHR rate (of data packets)                   | 850Kbps                             |

| Payload length (of data packets)             | 20 bytes                            |

| Preamble Code                                | 9                                   |

| SFD Type for Preamble for frames length 1024 | Decawave-defined 16-symbol SFD      |

| SFD Type for Preamble for frames length 64   | IEEE 802.15.4z defined 8-symbol SFD |

| Carrier frequency offset                     | ±10 ppm                             |

Table 8: Rx Sensitivity Characteristics (Channel 5)

| Typical<br>Receiver<br>Sensitivity<br>(dBm/500MHz) | Data Rate | Preamble<br>length<br>(symbols) | STS<br>length<br>(symbols) | Conditions            |

|----------------------------------------------------|-----------|---------------------------------|----------------------------|-----------------------|

| -100                                               | 850 Kbps  | 1024                            | n/a                        | See Table 7           |

| -94.3                                              | 6.8 Mbps  | 64                              | 64                         | See Table 7           |

| -98.6                                              | 6.8 Mbps  | 64                              | 64                         | No data packets mode. |

|                                                    |           |                                 |                            | See Table 7           |

Table 9: Rx Sensitivity Characteristics (Channel 9)

| Typical<br>Receiver<br>Sensitivity<br>(dBm/500MHz) | Data Rate | Preamble<br>length<br>(symbols) | STS<br>length<br>(symbols) | Conditions                           |

|----------------------------------------------------|-----------|---------------------------------|----------------------------|--------------------------------------|

| -99.3                                              | 850 Kbps  | 1024                            | n/a                        | See Table 7                          |

| -93.2                                              | 6.8 Mbps  | 64                              | 64                         | See Table 7                          |

| -98.0                                              | 6.8 Mbps  | 64                              | 64                         | No data packets mode.<br>See Table 7 |

Note: The above typical receiver sensitivities are for DW3110 and DW3210 variants. For PDoA variants (DW3120, DW3220) the RX sensitivity level is approximately 1.4 dB lower (i.e. less sensitive) due to the additional internal PDoA switch.

#### Reference Clock AC Characteristics

T<sub>amb</sub> = 25 °C, all supplies at 3.0V

**Table 10: Reference Clock AC Characteristics**

| Parameter                                | Min.                               | Тур.      | Max. | Units  | Condition/Note                                                                                   |  |

|------------------------------------------|------------------------------------|-----------|------|--------|--------------------------------------------------------------------------------------------------|--|

| Crystal oscillator reference frequency   |                                    | 38.4      |      | MHz    | A 38.4 MHz signal can be provided from an external reference in place of a crystal if desired.   |  |

| External Crystal Specific                | ations                             |           |      |        |                                                                                                  |  |

| Load<br>capacitance                      | 0                                  |           | 35   | pF     | Depends on crystal used and PCB parasitics.                                                      |  |

| Shunt<br>capacitance                     | 0                                  |           | 4    | pF     |                                                                                                  |  |

| Drive level                              |                                    |           | 200  | μW     | Depends on crystal & load capacitance used.                                                      |  |

| Equivalent<br>Series Resistance<br>(ESR) |                                    |           | 60   | Ω      |                                                                                                  |  |

| Frequency<br>tolerance                   |                                    |           | ±20  | ppm    | DW3000 includes circuitry to trim the crystal oscillator to reduce the initial frequency offset. |  |

| Crystal trimming range                   | -20                                |           | +20  | ppm    | Trimming range provided by on-chip circuitry. Depends on the crystal used and PCB design.        |  |

| External Reference (Fo                   | or example                         | e a TCXO) |      |        |                                                                                                  |  |

| Amplitude                                | 0.8                                |           | VDD2 | Vpp    | Must be AC coupled. A coupling capacitor value of 2200 pF is recommended.                        |  |

| SSB phase noise power density            |                                    |           | -132 | dBc/Hz | @1 kHz offset.                                                                                   |  |

| SSB phase noise power density            |                                    |           | -145 | dBc/Hz | @10 kHz offset.                                                                                  |  |

| Duty Cycle                               | 40                                 |           | 60   | %      |                                                                                                  |  |

| Internal Fast and Slow                   | Internal Fast and Slow Oscillators |           |      |        |                                                                                                  |  |

| Slow RC Oscillator                       |                                    | 23        |      | kHz    | User programmable <sup>1</sup>                                                                   |  |

| Fast RC Oscillator                       |                                    | 125       |      | MHz    | Internally calibrated.                                                                           |  |

¹Note: Chip start-up time depends on this clock. The typical frequency of Slow LP OCS reflected the chip start-up time of 913us. With the time, required to download the AON after wake-up, the overall start-up time is ∼1000us. It is possible to trim the LP OSC to the higher frequency in software, which would decrease the start-up time to ∼770us.

#### 3.5 Transmitter AC Characteristics

Tamb = 25 °C, all supplies at 3.0V

**Table 11: Transmitter AC Characteristics**

| Parameter                                     | Min. | Тур.   | Max. | Units   | Condition/Note                     |

|-----------------------------------------------|------|--------|------|---------|------------------------------------|

| Centre Frequency Channel 5                    |      | 6489.6 |      |         |                                    |

| Centre Frequency Channel 9                    |      | 7987.2 |      | MHz     |                                    |

| Channel Bandwidths                            |      | 499.2  |      |         | Programmable.                      |

| Output power spectral density (programmable)  |      |        | -31  | dBm/MHz | Using DW3110 <sup>1</sup>          |

| Load impedance                                |      | 50     |      | Ω       | Single ended.                      |

| Power level range                             |      | 30     |      | dB      |                                    |

| Power level step                              |      | 0.5    |      | uБ      | See figure 6 and figure 7.         |

| Output power variation with                   |      | 0.02   |      | dB/°C   | Channel 5.                         |

| temperature                                   |      | 0.01   |      | UB/°C   | Channel 9.                         |

| Output power variation with voltage           |      | 0      |      | dB/V    | Internally regulated.              |

| Transmit bandwidth variation with temperature |      | 0.06   |      | MHz/°C  | With internal calibration enabled. |

¹The TX power quoted is for the DW3110 (CSP) variant, measured as a mean power in a 1MHz bandwidth. Typically the QFN package variants (DW3210, DW3220) output 2 dB less maximum TX power. For the PDoA variants (DW3120, DW3220) the TX power is reduced by an additional ∼1 dB due to insertion loss associated with the internal PDoA switch.

## 3.6 Link Budget

Using the receiver sensitivity above, expected transmission link budgets can be estimated with the following assumptions:

- 1. Receiver sensitivities as per Table 11 below.

- 2. Transmitter and receiver antennas have 0 dBi gain.

- 3. No losses between the antenna and DW3000 RF pins.

- 4. The transmitter is operating at an EIRP of -41.3 dBm/MHz (widely used regulatory limit).

Table 12: Typical Link Budget for DW3110

| Typical Link | Budget (dB) |           | Preamble            | STS                 |                                        |

|--------------|-------------|-----------|---------------------|---------------------|----------------------------------------|

| CH5          | СН9         | Data Rate | length<br>(symbols) | length<br>(symbols) | Condition/Note                         |

| 86           | 85          |           | 1024                | n/a                 |                                        |

| 91           | 90          | 850 Kbps  | 128                 | n/a                 | With 12 bytes data → 5 dB gating gain. |

| 89           | 88          | 6.8 Mbps  | 64                  | 64                  | With 12 bytes data → 9 dB gating gain. |

| 98           | 97          |           | 64                  | 64                  | No data mode  → 9 dB gating gain.      |

## Temperature and Voltage Monitor Characteristics

**Table 13: Temperature and Voltage Monitor Characteristics**

| Parameter                    | Min. | Тур. | Max. | Units |

|------------------------------|------|------|------|-------|

| Voltage Monitor Range        | 1.62 |      | 3.8  | V     |

| Voltage Monitor Accuracy     |      | 5    |      | %     |

| Temperature Monitor Range    | -40  |      | 105  | °C    |

| Temperature Monitor Accuracy | -3   |      | 3    | %     |

# 3.8 Location functionality Characteristics

**Table 14: Location Accuracy Characteristics**

| Parameter                               | Тур.   | Units | Condition/Note               |

|-----------------------------------------|--------|-------|------------------------------|

| Ranging accuracy <sup>1</sup>           | +/- 6  | cm    |                              |

| Ranging standard deviation <sup>2</sup> | 1.5    | cm    | In line of eight conditions  |

| PDoA accuracy <sup>34</sup>             | +/- 10 | deg   | In line of sight conditions. |

| PDoA standard deviation                 | 5      | deg   |                              |

<sup>&</sup>lt;sup>1</sup> After calibration is applied. Approximately +/-15cm without calibration. <sup>2</sup> Ranging standard deviation is measured at -85 dBm power level.

<sup>&</sup>lt;sup>3</sup> Note: in a typical PDoA based system the computed angle of arrival (AoA) accuracy is better than the PDoA accuracy by a factor of approximately two i.e. if PDoA accuracy is ±10° then AoA accuracy is ±5°.

<sup>4</sup> For optimal PDoA performance a crystal offset of greater than |5| ppm is required between devices.

## 3.9 Absolute Maximum Ratings

**Table 15: Absolute Maximum Ratings**

| Parameter                                                       | Min. | Max. | Units |

|-----------------------------------------------------------------|------|------|-------|

| Supply voltage                                                  | -0.3 | 4.0  | V     |

| Receiver power                                                  |      | 14   | dBm   |

| Storage temperature                                             | -65  | +150 | °C    |

| Operating temperature (Industrial)                              | -40  | +85  | °C    |

| MSL (Moisture sensitivity level) for WLCSP package <sup>1</sup> | 1    | 1    | Level |

| MSL (Moisture sensitivity level) for QFN packages <sup>1</sup>  | 3    | 3    | Level |

| ESD (Human Body Model)                                          |      | 2000 | V     |

<sup>&</sup>lt;sup>1</sup>Note: Tested according JEDEC-JSTD-020 spec.

# 3.10 Typical performance

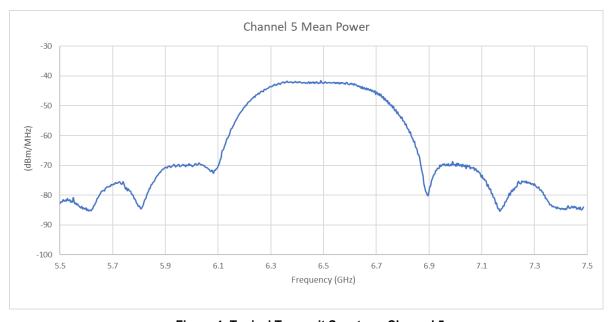

#### 3.10.1 Transmit Spectrum

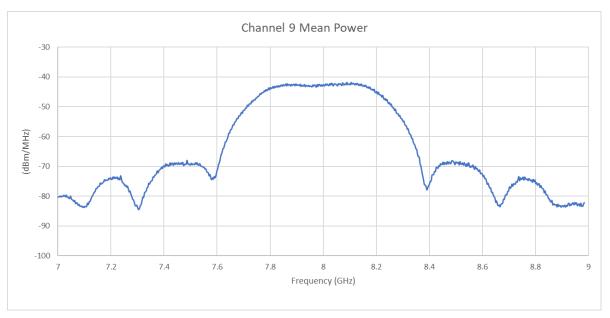

The typical transmit spectrums for channel 5 and channel 9 are on the pictures below.

The UWB configuration is:

- PRF = 64 MHz

- Preamble length = 64 symbols

- STS length = 64 symbols

- Data length = 20 bytes

Figure 4: Typical Transmit Spectrum Channel 5

Figure 5: Typical Transmit Spectrum Channel 9

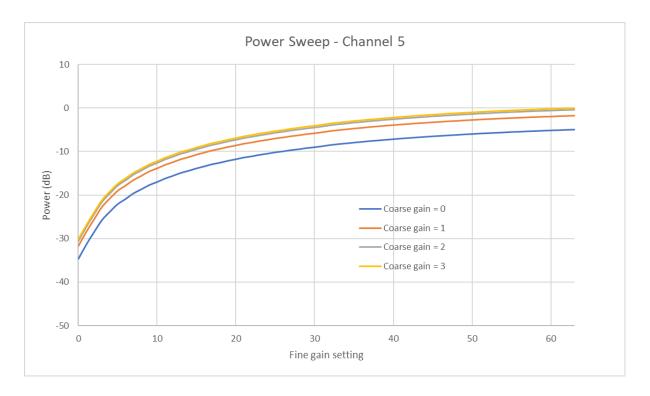

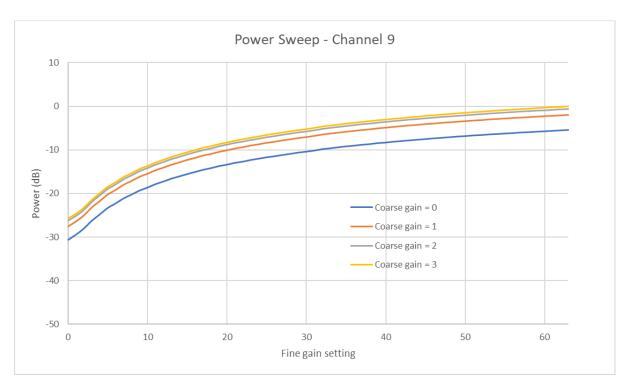

## 3.10.2 Transmit Power Adjustment

DW3000 has a coarse TX power adjustment and a fine TX power adjustment. The plots below show the relationship between these adjustments for each channel. The y-axis, Power(dB), is the output power in dB below the maximum.

Figure 6 Tx power coarse and fine gain settings Channel 5

Figure 7 Tx power coarse and fine gain settings Channel 9

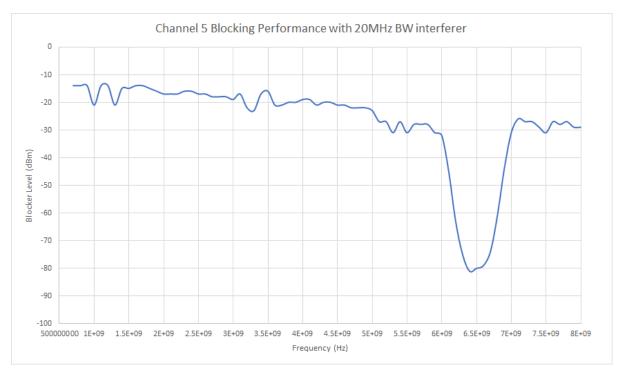

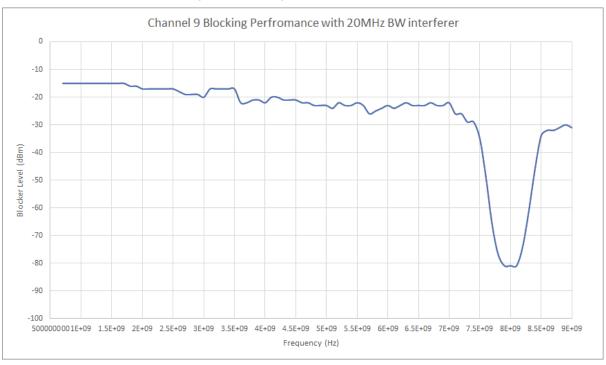

#### 3.10.3 Receiver Blocking

The following plots show typical blocking levels to give 1% UWB PER at 3 dB back off from the sensitivity point. The UWB configuration is:

- PRF = 64 MHz

- Preamble length = 64 symbols

- STS length = 64 symbols

Figure 8 Blocking performance channel 5

Figure 9 Blocking performance channel 9

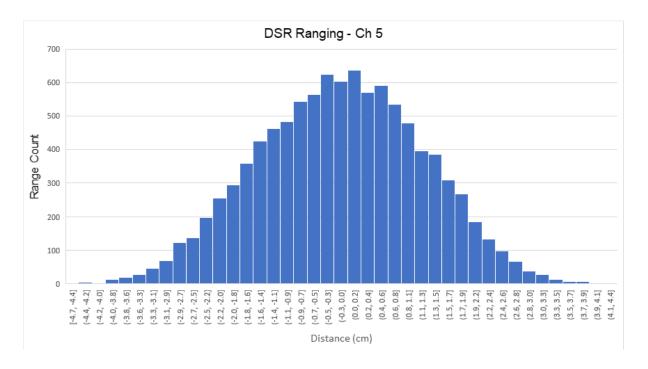

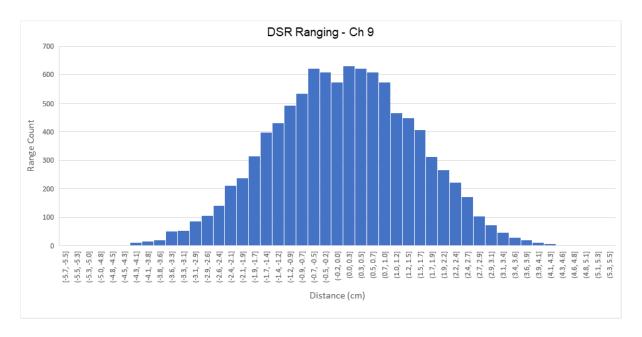

#### 3.10.4 Ranging

Typical measured distribution of double sided two-way ranging (DSR) performance.

Figure 10 Ranging performance channel 5

Figure 11 Ranging performance channel 9

# 4 FUNCTIONAL DESCRIPTION

#### 4.1 Physical Layer Modes

Please refer to IEEE802.15.4-2015 and IEEE802.15.4z for the PHY specification.

#### 4.2 Supported Channels and Bandwidths

The DW3000 supports the following IEEE802.15.4-2015 and IEEE802.15.4z UWB channels:

Table 16 UWB Channels supported

| UWB Channel Number | Centre Frequency (MHz) | Bandwidth (MHz) |

|--------------------|------------------------|-----------------|

| 5                  | 6489.6                 | 499.2           |

| 9                  | 7987.2                 | 499.2           |

#### 4.3 Supported Bit Rates and Pulse Repetition Frequencies (PRF)

The DW3000 supports IEEE802.15.4-2011, IEEE802.15.4-2015 UWB standard bit rates 850 kbps and 6.81 Mbps and nominal PRF values of 16 MHz and 64 MHz. The Base PRF (BPRF) mode of a newly defined draft standard IEEE802.15.4z is also supported.

Table 17 PRF and data rates supported

| PRF (MHz)       | Data Rate (Mbps) |

|-----------------|------------------|

| 16 <sup>1</sup> | 0,85             |

| 16 <sup>1</sup> | 6.81             |

| 64 <sup>2</sup> | 0.85             |

| 64 <sup>2</sup> | 6.81             |

Actual PRF mean values are slightly higher for SHR as opposed to the other portions of a frame. Mean PRF values are 16.1/15.6 MHz and 62.89/62.4 MHz, nominally referred to as 16 MHz and 64 MHz in this document. Refer to [1], [2] (UWB PHY rate-dependent and timing-related parameters) for full details of peak and mean PRFs.

In general, lower data rates give increased receiver sensitivity, increased link margin and longer range but due to longer frame lengths for a given number of data bytes they result in increased air occupancy per frame and a reduction in the number of individual transmissions that can take place per unit time.

16MHz PRF gives a marginal reduction in transmitter power consumption over 64 MHz PRF (BPRF).

#### 4.4 Symbol timings

Timing durations in IEEE802.15.4 are expressed in an integer number of symbols. This convention is adopted in DW3000 documentation. Symbol times vary depending on the data rate and PRF configuration of the device and the part of the frame. DW3000 can transmit PHR on the 0.85 and 6.81 Mbps data rates. See the table below for symbol timings supported by DW3000.

Table 18 DW3000 Symbol Timings Duration

| PRF<br>(MHz) | Data Rate<br>(Mbps) | SHR<br>(ns) | PHR 0.85 Mbps<br>(ns) | PHR 6.81 Mbps<br>(ns) | Data<br>(ns) |

|--------------|---------------------|-------------|-----------------------|-----------------------|--------------|

| 16           | 0.85                | 993.59      | 1025.64               | -                     | 1025.64      |

| 16           | 6.81                | 993.59      | 1025.64               | 128.21                | 128.21       |

| 64           | 0.85                | 1017.63     | 1025.64               | -                     | 1025.64      |

| 64           | 6.81                | 1017.63     | 1025.64               | 128.21                | 128.21       |

<sup>&</sup>lt;sup>1</sup> Backward-compatible for 802.15.4-2011 UWB devices

<sup>&</sup>lt;sup>2</sup> Base PRF (BPRF) mode of 802.15.4z(draft) and 802.15.4-2011

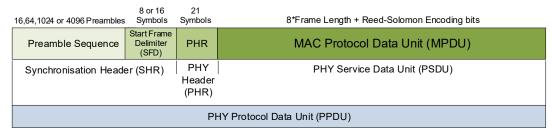

#### 4.5 Frame Format IEEE802.15.4-2011, IEEE802.15.4-2015

IEEE802.15.4-2011, IEEE802.15.4-2015 frames are structured as shown in Figure 12. Detailed descriptions of the frame format are given in the standard. The frame consists of a synchronisation header (SHR) which includes the preamble symbols and start frame delimiter (SFD), followed by the PHY header (PHR) and data. The data frame is usually specified in number of bytes and the frame format will include 48 Reed-Solomon parity bits following each block of 330 data bits (or less).

While zero length payloads and zero length PHR is supported the maximum frame length is 1023 bytes, including the 2-byte FCS.

Figure 12: IEEE802.15.4-2011 PPDU Structure

#### 4.6 Packet Formats of IEEE Std 802.15.4z™

The 4z amendment added new packet formats to HRP UWB PHY incorporating a Scrambled Timestamp Sequence (STS) into the packet structure, defining four STS Packet Configurations as shown in Figure 7 below.

The STS is a random sequence of positive and negative pulses generated using an AES-128 based deterministic random bit generator (DRBG). Only valid transmitters and receivers have the correct seed (i.e., the key and IV) to generate the sequence for transmission and to validly cross correlate in the receiver to determine the receive timestamp. The STS provides for secure receive timestamping and secure ranging.

#### STS packet configuration 0 (SP0) SYNC SFD PHR PHY Payload STS packet configuration 1 (SP1) SYNC SFD STS PHR PHY Payload STS packet configuration 2 (SP2) SYNC **SFD** PHR PHY Payload STS STS packet configuration 3 (SP3) SYNC STS SFD

Figure 7: IEEE 802.15.4z HRP UWB PHY PPDU formats

#### 4.7 Proprietary long frames

The DW3000 offers a proprietary long frame mode where frames of up to 1023 bytes may be transferred. Refer to the DW3000 user manual for full details.

#### 4.8 No Data frames

The DW3000 offers zero length payloads and zero length PHR (SP3). This is for use cases where an alternative method of data communications is available.

#### 4.9 Host Controller Interface

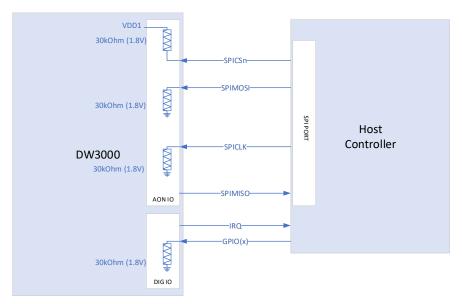

The primary interface DW3000 is via a 4 wire SPI interface. DW3000 will act a SPI peripheral device, in non-daisy-chain mode and operate at SPI clock frequencies up to 36MHz.

#### 4.9.1 SPI Functional Description

The host interface to DW3000 is a 4-wire SPI-compatible peripheral. The assertion of SPICSn low by the SPI controller (host) indicates the beginning of a transaction.

The SPI interface is used to read and write registers in the DW3000 device. All data and address transfer on the SPI is most significant bit first. All address bytes are transmitted with MSB first, and all data is transmitted commencing with lowest addressed byte.

- Assertion low of SPICSn initialises transaction.

- De-assertion high of SPICSn ends the SPI transaction.

- The device supports direct and per-byte sub-addressing access to the full register space.

- Efficient block data reading/writing is allowed. Continuous, long transactions can be carried out while the addressed location is auto-incremented on the DW3000 side.

The SPICDO (ex. SPIMISO) I/O of DW3000 is going open-drain when SPICSn is de-asserted, to allow interoperation with other peripherals on the SPI bus.

SPI daisy chaining is not supported. This is the mode where the CDO (ex. SPIMISO), CDI (ex. SPIMOSI) lines are passed through a device when it is not chip selected.

#### 4.9.2 SPI Timing Parameters

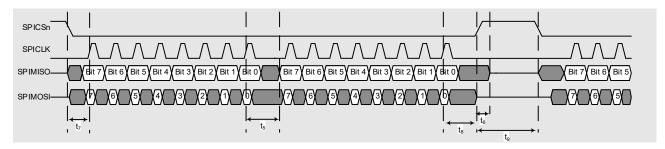

The SPI peripheral complies with the Motorola SPI protocol within the constraints of the timing parameters listed in Table 19 and illustrated in Figure 13 and Figure 14.

Figure 13: SPI Timing Diagram

**Table 19 SPI Timing Parameters**

| Parameter       | Min | Max | Unit | Description                                                  |

|-----------------|-----|-----|------|--------------------------------------------------------------|

| t <sub>1</sub>  |     | 3   | ns   | SPICSn asserted low to valid peripheral (DW3000) output data |

| t <sub>2</sub>  |     | 8.5 | ns   | SPICLK low to valid peripheral (DW3000) output data.         |

| t <sub>3</sub>  | 14  |     | ns   | Controller data setup time.                                  |

| t <sub>4</sub>  | 2   |     | ns   | Controller data hold time.                                   |

| t <sub>5</sub>  | 27  |     | ns   | LSB last byte to MSB next byte.                              |

| t <sub>6</sub>  |     | 45  | ns   | SPICSn deasserted high to CDO tristate.                      |

| t <sub>7</sub>  | 23  |     | ns   | Start time; time from select asserted to first SPICLK.       |

| t <sub>8</sub>  | 24  |     | ns   | Last SPICLK to SPICSn deasserted.                            |

| t <sub>9</sub>  | 40  |     | ns   | Idle time between consecutive accesses.                      |

| t <sub>10</sub> |     | 36¹ | MHz  | SPICLK SPI mode 0                                            |

<sup>1</sup>Note: SPICLK frequency in CRC mode is 20MHz.

#### 4.9.3 SPI Operating Modes

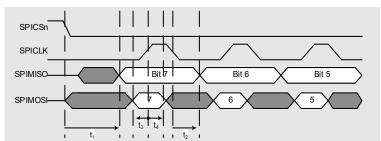

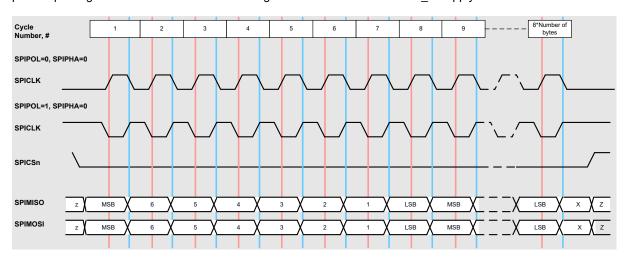

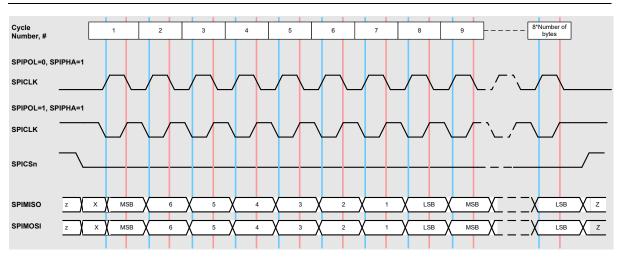

The SPI interface supports both clock polarities (SPIPOL=0/1) and phases (SPIPHA=0/1), as defined in the Motorola SPI protocol. The DW3000 transfer protocols for each SPIPOL and SPIPHA setting are given in Figure 14 and Figure 15. These modes are selected using GPIO 5 & 6 as follows:

**Table 20 SPI Mode Configuration**

| GPIO 5<br>(SPIPOL) | GPIO 6<br>(SPIPHA) | SPI<br>Mode |

|--------------------|--------------------|-------------|

| 0                  | 0                  | 0           |

| 0                  | 1                  | 1           |

| 1                  | 0                  | 2           |

| 1                  | 1                  | 3           |

GPIO 5 and 6 pins are sampled as shown on the Figure 21 and Figure 22 to determine the SPI mode. They are internally pulled low to configure a default SPI mode 0. If mode other than 0 is required, then they should be pulled up using an external resistor of value no greater than 10 k $\Omega$  to the VIO D supply.

Figure 14: DW3000 SPIPHA=0 Transfer Protocol

Figure 15: DW3000 SPIPHA=1 Transfer Protocol

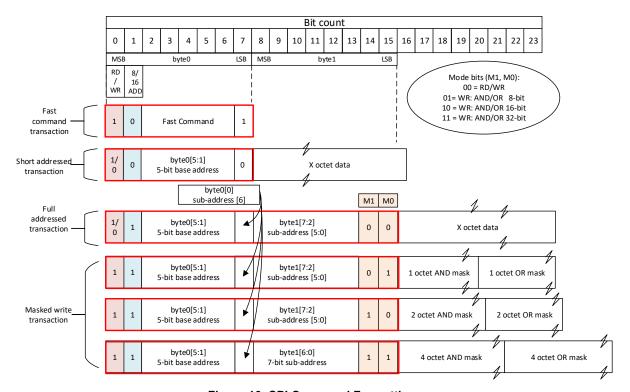

#### 4.9.4 SPI Transaction Formatting

The SPI command structure allows for 4 different types of SPI command:

- 1. Fast, single byte commands. Up to 32 unique commands such as "TX now", "TX/RX Off".

- 2. Fast addressed mode. Allowing for read and write addressing to 32 addresses. This command structure is padded by a trailing bit to allow the SPI address decoder time to fetch any read data. The length of the read is determined by the length of the SPI transaction.

- 3. Full addressed mode. Allowing for read and write addressing to 32 addresses and up to 128 byte offset addressing. This command structure is padded by a trailing bit to allow the SPI address decoder time to fetch any read data. The length of the read or write is determined by the length of the SPI transaction.

- 4. Masked write transaction. These are intended to simplify read-modify-write operations by allowing the host to write to an address and apply a set, clear or toggle mask to 1, 2, or 4 bytes. The SPI command decoder then carries out the required read-modify-write instructions internally.

Figure 16: SPI Command Formatting

## 4.9.5 GPIO and SPI I/O internal pull up/down

All of the GPIO pins have a software controllable internal pull down resistor except for SPICSn, which has a pull up, to ensure safe operation when input pins are not driven. The value of the internal resistors can vary with the VDD1 supply voltage over a range from 10 k $\Omega$  (VDD1 is 1.8V) to 30 k $\Omega$  (VDD1 is 3.6V).

Figure 17: SPI and GPIO pull up/down

#### 4.10 Reference Crystal Oscillator

With the addition of an external 38.4 MHz crystal and appropriate loading capacitors, the on-chip crystal oscillator generates the reference frequency for the integrated frequency synthesizer's RFPLL.

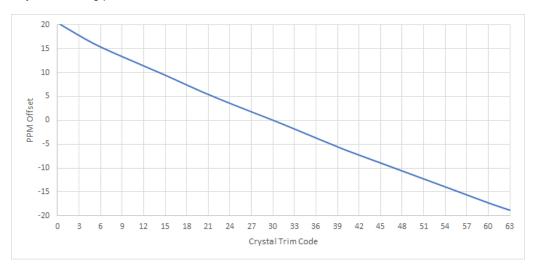

The DW3000 crystal oscillator is used to provide the reference clock to the internal PLL and provides a direct clock source to the digital core when operating in the lower power INIT\_RC mode. The oscillator operates at a frequency of 38.4 MHz. A trim facility is provided which can be used to trim out crystal initial frequency error. Typically, a trimming range of ± 20 ppm is possible using a 6-bit trim range. This trimming in 0.125pF steps provides for up to 8 pF additional capacitance on the XTI and XTO crystal connections.

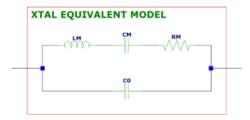

#### 4.10.1 Calculation of external capacitor values for frequency trim

Ideally the value of external loading capacitors (Cext) should be calculated to give an equal trim range about the center trim value. To do this, one needs to estimate the parasitic capacitance (Cpar) between the crystal pads XTI/XTO and the crystal pads. A good starting estimate is usually about 5 pF however some trial and error maybe required initially. The values of Cm, Lm, Rm and Co obtained from the crystal manufacturer are also required.

Figure 18 Crystal Model

Using the following formulae, the required Cext and trim range can be estimated where:

$$f_{S} = \frac{1}{2\pi\sqrt{C_{M}L_{M}}}$$

$$f_{P} = f_{S}\left(\sqrt{1 + \frac{C_{M}}{C_{0}}}\right)$$

$$f_{L} = f_{S}\left(\sqrt{1 + \frac{C_{M}}{C_{L}}}\right)$$

$$C_{L} = C_{0} + \frac{1}{2}\left(C_{TRIM} + C_{PAR} + C_{EXT}\right)$$

$$\Delta f_{ppm} = 10^{6} \times \frac{f_{L} - f_{L_{NOM}}}{f_{L_{NOM}}}$$

A typical crystal trimming plot is shown below:

Figure 19 Crystal Trim plot

# **5 OPERATIONAL STATES**

## 5.1 Overview

DW3000 has a number of basic operations states as described in Table 21.

**Table 21: Operating States**

| State     | Description                                                                                                                    |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|--|

| OFF       | Digital core is powered off, digital LDO is disabled. Reset is held low.                                                       |  |

| INIT_RC   | System is clocked from 30MHz RC Osc, SPI comms @ 7MHz. AON download is performed. Automatically goes to IDLE_RC on completion. |  |