# **ESD Protection Diode**

# Low Capacitance Array for High Speed Data Lines

The ESD8104 is designed to protect high speed data lines from ESD. Ultra-low capacitance and low ESD clamping voltage make this device an ideal solution for protecting voltage sensitive high speed data lines. The flow-through style package allows for easy PCB layout and matched trace lengths necessary to maintain consistent impedance between high speed differential lines such as USB 3.0/3.1 and HDMI 2.0.

### **Features**

- Low Capacitance (0.37 pF Max, I/O to GND)

- Protection for the Following IEC Standards: IEC 61000-4-2 (Level 4)

- Low ESD Clamping Voltage

- SZ Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

# **Typical Applications**

- USB 3.0/3.1

- eSATA

- HDMI 1.3/1.4/2.0

- DisplayPort

### **MAXIMUM RATINGS** (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                                 | Symbol           | Value       | Unit     |

|--------------------------------------------------------|------------------|-------------|----------|

| Operating Junction Temperature Range                   | TJ               | -55 to +125 | °C       |

| Storage Temperature Range                              | T <sub>stg</sub> | -55 to +150 | °C       |

| Lead Solder Temperature –<br>Maximum (10 Seconds)      | TL               | 260         | °C       |

| IEC 61000-4-2 Contact (ESD)<br>IEC 61000-4-2 Air (ESD) | ESD<br>ESD       | ±15<br>±15  | kV<br>kV |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

See Application Note AND8308/D for further description of survivability specs.

1

# ON Semiconductor®

www.onsemi.com

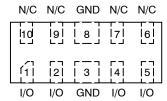

### MARKING DIAGRAM

### UDFN10 CASE 517BB

4C = Specific Device Code (tbd)

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

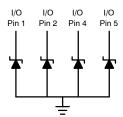

# PIN CONFIGURATION AND SCHEMATIC

Pins 3, 8

Note: Common GND - Only Minimum of 1 GND connection required

### **ORDERING INFORMATION**

| Device         | Package             | Shipping              |

|----------------|---------------------|-----------------------|

| ESD8104MUTAG   | UDFN10<br>(Pb-Free) | 3000 /<br>Tape & Reel |

| SZESD8104MUTAG | UDFN10<br>(Pb-Free) | 3000 /<br>Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

### **ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = 25°C unless otherwise noted)

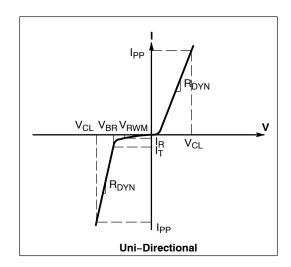

| Symbol           | Parameter                                          |  |  |

|------------------|----------------------------------------------------|--|--|

| I <sub>PP</sub>  | Maximum Peak Pulse Current                         |  |  |

| V <sub>C</sub>   | Clamping Voltage @ I <sub>PP</sub>                 |  |  |

| V <sub>RWM</sub> | Working Peak Reverse Voltage                       |  |  |

| I <sub>R</sub>   | Maximum Reverse Leakage Current @ V <sub>RWM</sub> |  |  |

| $V_{BR}$         | Breakdown Voltage @ I <sub>T</sub>                 |  |  |

| I <sub>T</sub>   | Test Current                                       |  |  |

| R <sub>DYN</sub> | Dynamic Resistance                                 |  |  |

<sup>\*</sup>See Application Note AND8308/D for detailed explanations of datasheet parameters.

# **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ unless otherwise specified)

| Parameter                                                   | Symbol           | Conditions                                                                                                                                            |  | Тур                         | Max                  | Unit |

|-------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------------------------|----------------------|------|

| Reverse Working Voltage                                     | $V_{RWM}$        | I/O Pin to GND                                                                                                                                        |  |                             | 3.3                  | V    |

| Breakdown Voltage                                           | $V_{BR}$         | I <sub>T</sub> = 1 mA, I/O Pin to GND                                                                                                                 |  | 5.0                         |                      | V    |

| Reverse Leakage Current                                     | I <sub>R</sub>   | V <sub>RWM</sub> = 3.3 V, I/O Pin to GND                                                                                                              |  |                             | 1.0                  | μΑ   |

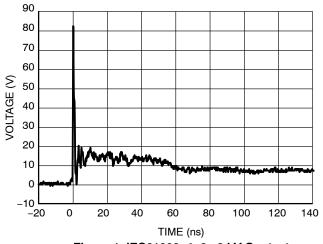

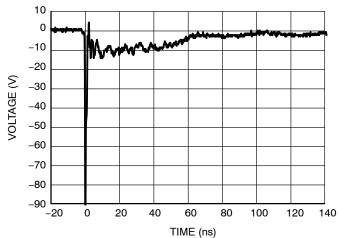

| Clamping Voltage<br>(Note 1)                                | V <sub>C</sub>   | IEC61000-4-2, ±8 kV Contact                                                                                                                           |  | See Figures 1 and 2         |                      | V    |

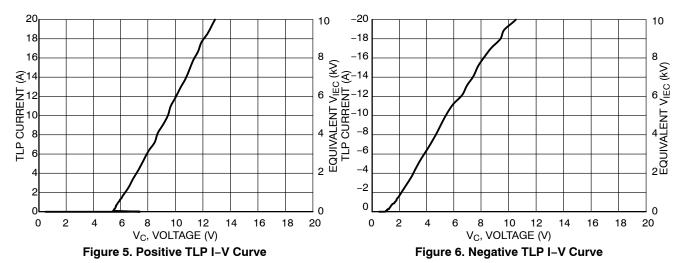

| Clamping Voltage<br>TLP (Note 2)<br>See Figures 5 through 8 | V <sub>C</sub>   |                                                                                                                                                       |  | 8.5<br>-4.5<br>11.4<br>-8.0 |                      | V    |

| Dynamic Resistance                                          | R <sub>DYN</sub> | I/O Pin to GND<br>GND to I/O Pin                                                                                                                      |  | 0.36<br>0.44                |                      | Ω    |

| Junction Capacitance                                        | СЈ               | $V_R$ = 0 V, f = 1 MHz between I/O Pins and GND $V_R$ = 0 V, f = 1 MHz between I/O Pins $V_R$ = 0 V, f = 1 MHz, $T_A$ = 65°C between I/O Pins and GND |  | 0.30<br>0.15<br>0.37        | 0.37<br>0.20<br>0.47 | pF   |

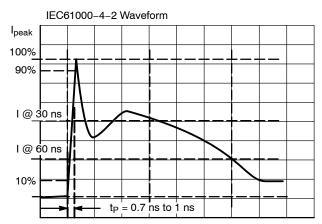

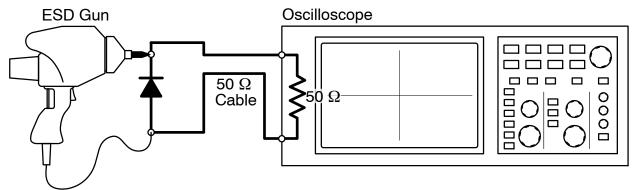

- 1. For test procedure see Figures 3 and 4 and application note AND8307/D.

- 2. ANSI/ESD STM5.5.1 Electrostatic Discharge Sensitivity Testing using Transmission Line Pulse (TLP) Model. TLP conditions:  $Z_0 = 50 \Omega$ ,  $t_p = 100 \text{ ns}$ ,  $t_r = 4 \text{ ns}$ , averaging window;  $t_1 = 30 \text{ ns}$  to  $t_2 = 60 \text{ ns}$ .

Figure 1. IEC61000-4-2 +8 kV Contact Clamping Voltage

Figure 2. IEC61000-4-2 -8 kV Contact Clamping Voltage

# IEC 61000-4-2 Spec.

|       | -                      |                              |                         |                         |

|-------|------------------------|------------------------------|-------------------------|-------------------------|

| Level | Test Volt-<br>age (kV) | First Peak<br>Current<br>(A) | Current at<br>30 ns (A) | Current at<br>60 ns (A) |

| 1     | 2                      | 7.5                          | 4                       | 2                       |

| 2     | 4                      | 15                           | 8                       | 4                       |

| 3     | 6                      | 22.5                         | 12                      | 6                       |

| 4     | 8                      | 30                           | 16                      | 8                       |

Figure 3. IEC61000-4-2 Spec

Figure 4. Diagram of ESD Clamping Voltage Test Setup

The following is taken from Application Note AND8307/D – Characterization of ESD Clamping Performance.

# **ESD Voltage Clamping**

For sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000-4-2 waveform. Since the IEC61000-4-2 was written as a pass/fail spec for larger

systems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes. For more information on how ON Semiconductor creates these screenshots and how to interpret them please refer to AND8307/D.

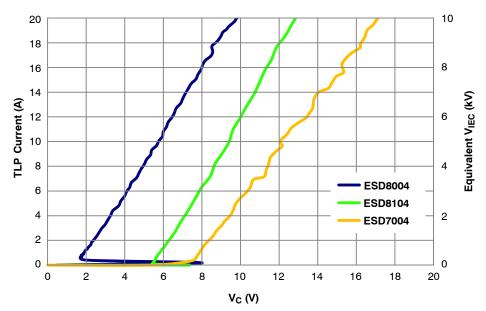

NOTE: TLP parameter:  $Z_0 = 50 \ \Omega$ ,  $t_p = 100 \ ns$ ,  $t_r = 300 \ ps$ , averaging window:  $t_1 = 30 \ ns$  to  $t_2 = 60 \ ns$ .  $V_{IEC}$  is the equivalent voltage stress level calculated at the secondary peak of the IEC 61000–4–2 waveform at  $t = 30 \ ns$  with 2 A/kV. See TLP description below for more information.

### Transmission Line Pulse (TLP) Measurement

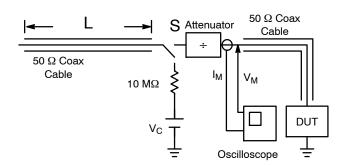

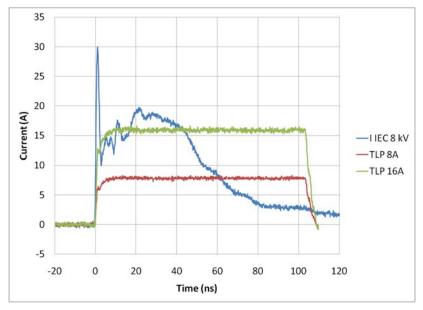

Transmission Line Pulse (TLP) provides current versus voltage (I–V) curves in which each data point is obtained from a 100 ns long rectangular pulse from a charged transmission line. A simplified schematic of a typical TLP system is shown in Figure 7. TLP I–V curves of ESD protection devices accurately demonstrate the product's ESD capability because the 10s of amps current levels and under 100 ns time scale match those of an ESD event. This is illustrated in Figure 8 where an 8 kV IEC 61000–4–2 current waveform is compared with TLP current pulses at 8 A and 16 A. A TLP I–V curve shows the voltage at which the device turns on as well as how well the device clamps voltage over a range of current levels. For more information on TLP measurements and how to interpret them please refer to AND9007/D.

Figure 7. Simplified Schematic of a Typical TLP System

Figure 8. Comparison Between 8 kV IEC 61000-4-2 and 8 A and 16 A TLP Waveforms

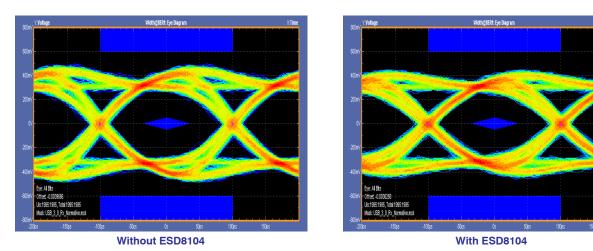

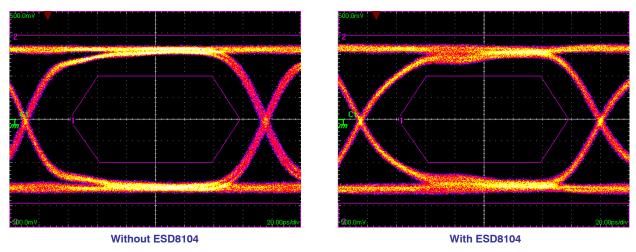

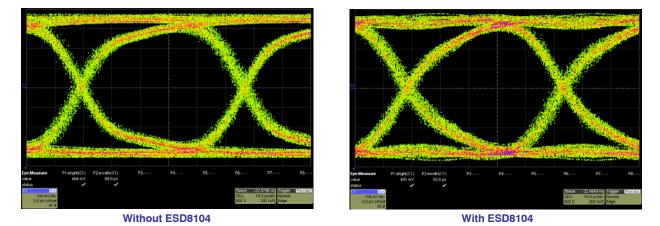

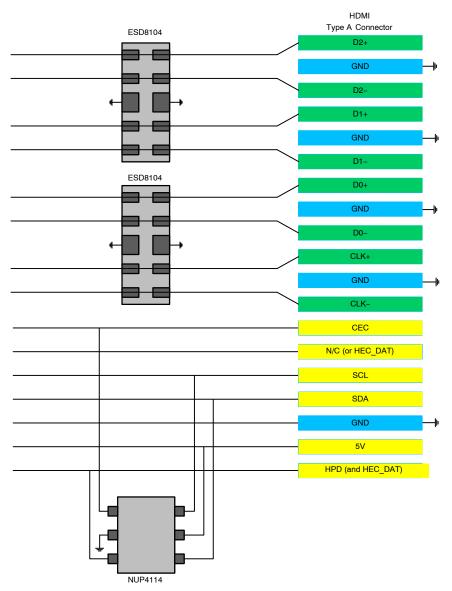

Figure 9. USB 3.0 Eye Diagram with and without ESD8104. 5 Gb/s

Figure 10. HDMI 2.0 Eye Diagram with and without ESD8104. 6 Gb/s

Figure 11. USB 3.1 Eye Diagram with and without ESD8104. 10 Gb/s

See application note AND9075/D for further description of eye diagram testing methodology.

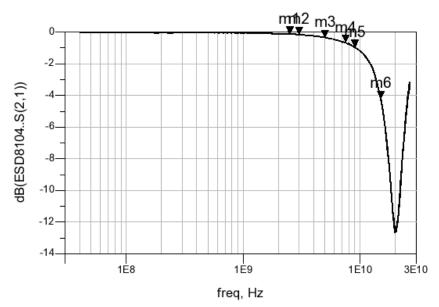

Figure 12. RF Insertion Loss

TABLE 1. RF Insertion Loss: Application Description

| Interface | Data Rate<br>(Gb/s) | Fundamental Frequency<br>(GHz) | 3 <sup>rd</sup> Harmonic Frequency<br>(GHz) | ESD8104 Insertion Loss<br>(dB) |

|-----------|---------------------|--------------------------------|---------------------------------------------|--------------------------------|

| USB 3.0   | 5.0                 | 2.5 (m1)                       | 7.5 (m4)                                    | m1 = 0.128<br>m2 = 0.155       |

| HDMI 2.0  | 6.0                 | 3.0 (m2)                       | 9.0 (m5)                                    | m3 = 0.352<br>m4 = 0.659       |

| USB 3.1   | 10                  | 5.0 (m3)                       | 15 (m6)                                     | m5 = 0.958<br>m6 = 4.194       |

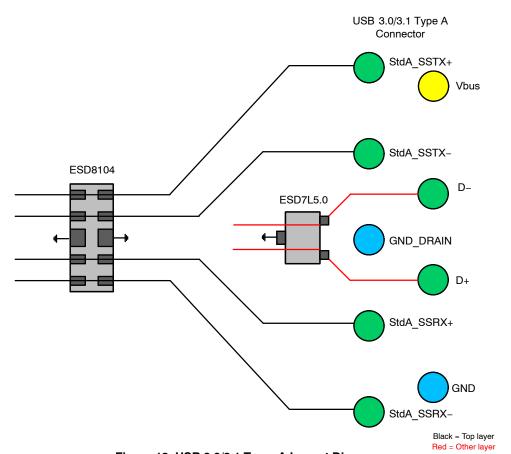

Figure 13. USB 3.0/3.1 Type-A Layout Diagram

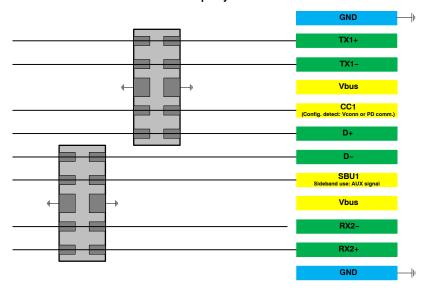

Type-C Hybrid Top Mount Connector Top Layer

Type-C Hybrid Top Mount Connector Bottom Layer

Figure 14. USB 3.1 Type-C Layout Diagram

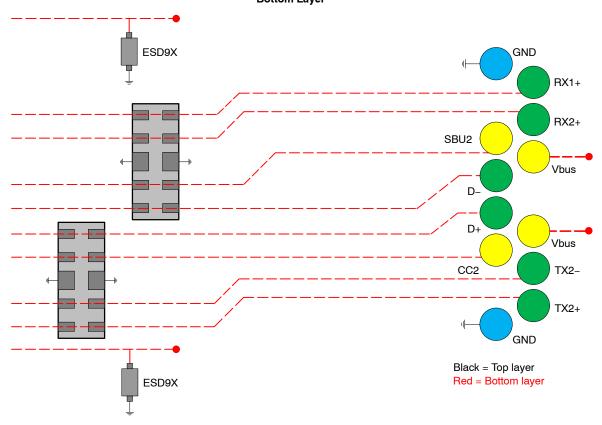

Figure 15. HDMI Layout Diagram

# **PCB Layout Guidelines**

Steps must be taken for proper placement and signal trace routing of the ESD protection device in order to ensure the maximum ESD survivability and signal integrity for the application. Such steps are listed below.

- Place the ESD protection device as close as possible to the I/O connector to reduce the ESD path to ground and improve the protection performance.

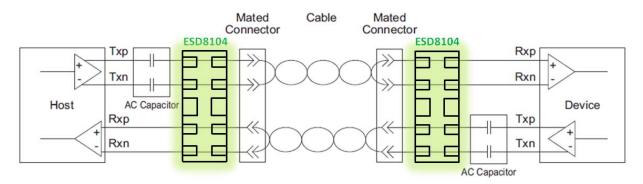

- ◆ In USB 3.0/3.1 applications, the ESD protection device should be placed between the AC coupling capacitors and the I/O connector on the TX differential lanes as shown in Figure 16.

- Make sure to use differential design methodology and impedance matching of all high speed signal traces.

- Use curved traces when possible to avoid unwanted reflections.

- Keep the trace lengths equal between the positive and negative lines of the differential data lanes to avoid common mode noise generation and impedance mismatch.

- Place grounds between high speed pairs and keep as much distance between pairs as possible to reduce crosstalk.

Figure 16. USB 3.0/3.1 Connection Diagram

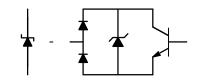

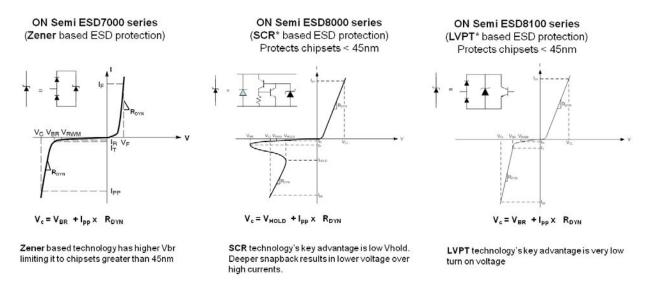

### **ESD Protection Device Technology**

ON Semiconductor's portfolio contains three main technologies for low capacitance ESD protection device which are highlighted below and in Figure 17.

- ESD7000 series: Zener diode based technology. This technology has a higher breakdown voltage (VBR) limiting it to protecting chipsets with larger geometries.

- ESD8000 series: Silicon controlled rectifier (SCR) type technology. The key advatange for this technology is a low holding voltage (VH) which produces a deeper snapback that results in lower voltage over high

- currents as shown in the TLP results in Figure 18. This technology provides optimized protection for chipsets with small geometries against thermal failures resulting in chipset damage (also known as "hard failures").

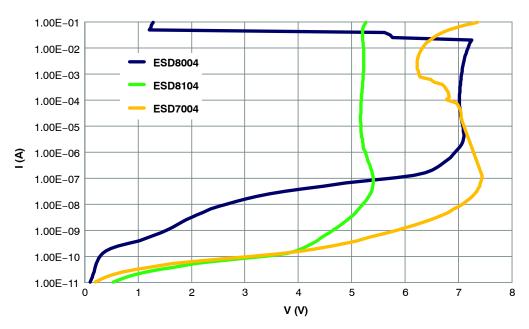

- ESD8100 series: Low voltage punch through (LVPT)

type technology. The key advatange for this technology

is a very low turn-on voltage as shown in Figure 19.

This technology provides optimized protection for

chipsets with small geometries against recoverable

failures due to voltage peaks (also known as "soft

failures").

Figure 17. ON Semiconductor's Low-cap ESD Technology Portfolio

Figure 18. High Current, TLP, IV Characteristic of Each Technology

Figure 19. Low Current, DC, IV Characteristic of Each Technology

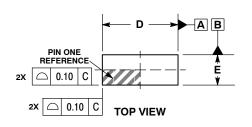

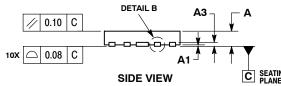

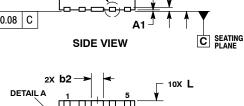

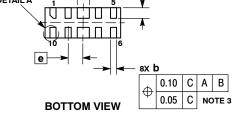

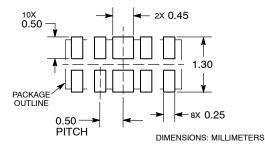

# **MECHANICAL CASE OUTLINE**

PACKAGE DIMENSIONS

### UDFN10 2.5x1, 0.5P CASE 517BB-01 **ISSUE 0**

**DATE 17 NOV 2009**

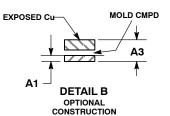

# OPTIONAL CONSTRUCTIONS

### NOTES:

- DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.45        | 0.55 |  |

| A1  | 0.00        | 0.05 |  |

| A3  | 0.13 REF    |      |  |

| b   | 0.15        | 0.25 |  |

| b2  | 0.35        | 0.45 |  |

| D   | 2.50 BSC    |      |  |

| Е   | 1.00 BSC    |      |  |

| е   | 0.50 BSC    |      |  |

| L   | 0.30        | 0.40 |  |

| L1  |             | 0.05 |  |

# **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code

= Date Code M

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

### **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON47059E        | Electronic versions are uncontrolled except when accessed directly from the Document Reposito<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | UDFN10 2.5X1, 0.5P |                                                                                                                                                                                  | PAGE 1 OF 1 |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.