# ESDL2011

## **ESD Protection Diode**

## Micro-Packaged Diodes for ESD Protection

The ESDL2011 is designed to protect voltage sensitive components that require low capacitance from ESD and transient voltage events. Excellent clamping capability, low capacitance, low leakage, and fast response time, make these parts ideal for ESD protection on designs where board space is at a premium. Because of its low capacitance, the part is well suited for use in high speed data line applications.

#### Features

- Low Capacitance 0.17 pF (Typ)

- Low Clamping Voltage

- Small Body Outline Dimensions: 0.60 mm x 0.30 mm

- Low Body Height: 0.2 mm

- Stand-off Voltage: 1.0 V

- IEC61000-4-2 Level 4 ESD Protection

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

#### **Typical Applications**

- USB 3.x

- Thunderbolt 3.0

#### MAXIMUM RATINGS

| Rating                                                                                                             | Symbol                             | Value       | Unit       |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|------------|

| IEC 61000-4-2 (ESD) Contact<br>Air                                                                                 |                                    | ±15<br>±15  | kV         |

| Total Power Dissipation on FR-4 Board<br>(Note 1) @ $T_A = 25^{\circ}C$<br>Thermal Resistance, Junction-to-Ambient | Ρ <sub>D</sub><br>R <sub>θJA</sub> | 313<br>400  | mW<br>°C/W |

| Junction and Storage Temperature Range                                                                             | T <sub>J</sub> , T <sub>stg</sub>  | -55 to +150 | °C         |

| Lead Solder Temperature – Maximum (10 Second Duration)                                                             | ΤL                                 | 260         | °C         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. FR-4 = 28 mm<sup>2</sup> 1 oz. Cu JEDEC JESD51-3 two layer PCB.

See Application Note AND8308/D for further description of survivability specs.

## **ON Semiconductor®**

www.onsemi.com

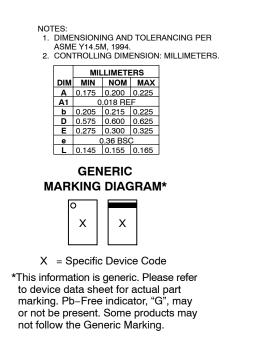

MARKING

A = Specific Device Code

#### **ORDERING INFORMATION**

| Device         | Package           | Shipping <sup>†</sup>  |

|----------------|-------------------|------------------------|

| ESDL2011PFCT5G | DSN2<br>(Pb–Free) | 10000 / Tape &<br>Reel |

+ For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

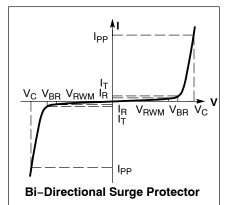

| ( //             | /                                                  |  |  |

|------------------|----------------------------------------------------|--|--|

| Symbol           | Parameter                                          |  |  |

| I <sub>PP</sub>  | Maximum Reverse Peak Pulse Current                 |  |  |

| V <sub>C</sub>   | Clamping Voltage @ I <sub>PP</sub>                 |  |  |

| V <sub>RWM</sub> | Working Peak Reverse Voltage                       |  |  |

| I <sub>R</sub>   | Maximum Reverse Leakage Current @ V <sub>RWM</sub> |  |  |

| V <sub>BR</sub>  | Breakdown Voltage @ I <sub>T</sub>                 |  |  |

| Ι <sub>Τ</sub>   | Test Current                                       |  |  |

\*See Application Note AND8308/D for detailed explanations of datasheet parameters.

#### **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ unless otherwise specified)

| Parameter                                            | Symbol           | Conditions                                                                                                                              | Min             | Тур           | Max          | Unit |

|------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|--------------|------|

| Reverse Working Voltage                              | V <sub>RWM</sub> | I/O Pin to GND                                                                                                                          |                 |               | 1.0          | V    |

| Breakdown Voltage                                    | V <sub>BR</sub>  | I <sub>T</sub> = 1 mA, I/O Pin to GND                                                                                                   | 1.4             | 1.65          | 2.3          | V    |

| Reverse Leakage Current                              | I <sub>R</sub>   | V <sub>RWM</sub> = 1.0 V                                                                                                                |                 | 30            | 500          | nA   |

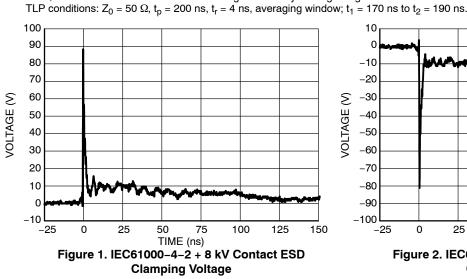

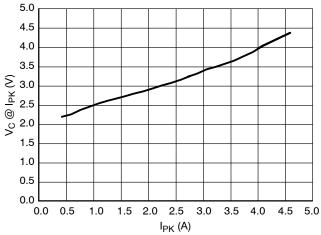

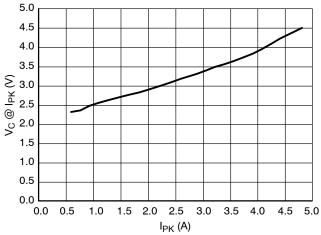

| Clamping Voltage (Note 2)                            | V <sub>C</sub>   | IEC61000-4-2, ±8 kV Contact                                                                                                             | Figures 1 and 2 |               | 2            | V    |

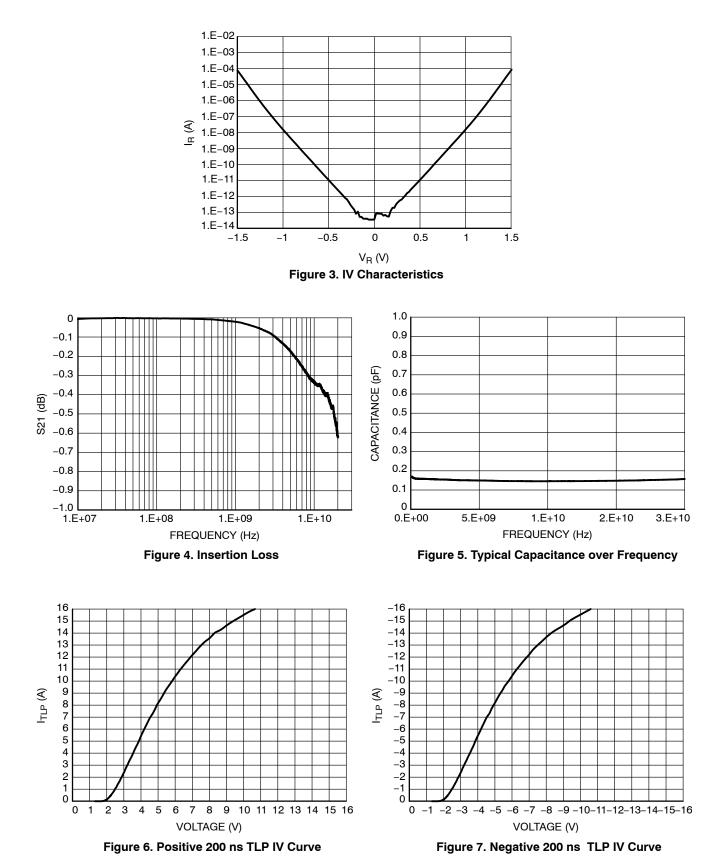

| Clamping Voltage<br>200 ns TLP                       | V <sub>C</sub>   | $I_{PP} = 4 A $ $\begin{cases} IEC61000-4-2 \text{ Level 1 Equivalent} \\ (\pm 2 \text{ kV Contact}, \pm 4 \text{ kV Air}) \end{cases}$ |                 | 3.5           | 4.0          | V    |

|                                                      |                  | IPP = 8 A<br>IEC61000-4-2 Level 2 Equivalent<br>(±4 kV Contact, ±8 kV Air)                                                              |                 | 4.8           | 6.0          |      |

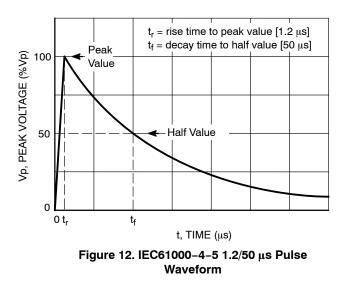

| Reverse Peak Pulse Current<br>per Figure 12          | I <sub>PP</sub>  | per IEC61000–4–5 (1.2/50 $\mu s),R_{eq}$ = 12 $\Omega$                                                                                  | 3.5             | 4.5           |              | A    |

| Clamping Voltage 1.2/50 μs<br>Waveform per Figure 12 | V <sub>C</sub>   | $I_{PP}$ = 2.1 A, IEC61000–4–5 (1.2/50 μs),<br>R <sub>eq</sub> = 12 Ω                                                                   |                 | 2.9           | 3.5          | V    |

| Clamping Voltage 1.2/50 μs<br>Waveform per Figure 12 | V <sub>C</sub>   | $I_{PP}$ = 3.5 A, IEC61000–4–5 (1.2/50 μs),<br>R <sub>eq</sub> = 12 Ω                                                                   |                 | 3.6           | 4.0          | V    |

| Dynamic Resistance (TLP)                             | R <sub>DYN</sub> | I/O Pin to GND (4 A to 8 A, 200 ns TLP)                                                                                                 |                 | 0.34          | 0.5          | Ω    |

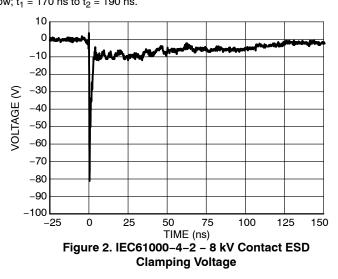

| Junction Capacitance                                 | CJ               | V <sub>R</sub> = 0 V, f = 1 MHz                                                                                                         |                 | 0.17          | 0.20         | pF   |

| Insertion Loss                                       | ۱ <sub>L</sub>   | f = 5 GHz<br>f = 10 GHz                                                                                                                 |                 | 0.165<br>0.34 | 0.20<br>0.40 | dB   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

2. For test procedure see application note AND8307/D.

3. ANSI/ESD STM5.5.1 - Electrostatic Discharge Sensitivity Testing using Transmission Line Pulse (TLP) Model.

## ESDL2011

### **TYPICAL CHARACTERISTICS**

## ESDL2011

### **TYPICAL CHARACTERISTICS**

Figure 8. Positive Clamping Voltage vs. Peak Pulse Current (per IEC61000–4–5 (t\_p = 1.2/50  $\mu s,\,R_{eq}$  = 12  $\Omega))$

Figure 9. Negative Clamping Voltage vs. Peak Pulse Current (per IEC61000–4–5 (t\_p = 1.2/50  $\mu s,\,R_{eq}$  = 12  $\Omega))$

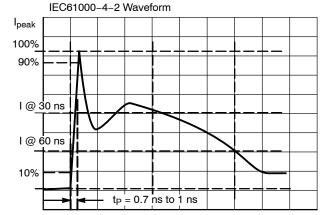

#### IEC 61000-4-2 Spec.

| Level | Test Volt-<br>age (kV) | First Peak<br>Current<br>(A) | Current at<br>30 ns (A) | Current at<br>60 ns (A) |

|-------|------------------------|------------------------------|-------------------------|-------------------------|

| 1     | 2                      | 7.5                          | 4                       | 2                       |

| 2     | 4                      | 15                           | 8                       | 4                       |

| 3     | 6                      | 22.5                         | 12                      | 6                       |

| 4     | 8                      | 30                           | 16                      | 8                       |

Figure 10. IEC61000-4-2 Spec

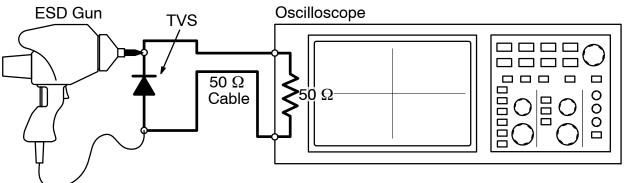

Figure 11. Diagram of ESD Test Setup

#### **ESD Voltage Clamping**

For sensitive circuit elements it is important to limit the voltage that an IC will be exposed to during an ESD event to as low a voltage as possible. The ESD clamping voltage is the voltage drop across the ESD protection diode during an ESD event per the IEC61000–4–2 waveform. Since the IEC61000–4–2 was written as a pass/fail spec for larger systems such as cell phones or laptop computers it is not clearly defined in the spec how to specify a clamping voltage

at the device level. ON Semiconductor has developed a way to examine the entire voltage waveform across the ESD protection diode over the time domain of an ESD pulse in the form of an oscilloscope screenshot, which can be found on the datasheets for all ESD protection diodes. For more information on how ON Semiconductor creates these screenshots and how to interpret them please refer to AND8307/D.

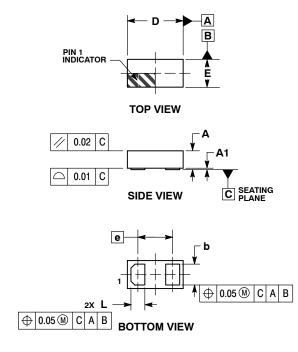

X4DFN2, 0.60x0.30, 0.36P CASE 152AX

ISSUE G

DATE 12 APR 2019

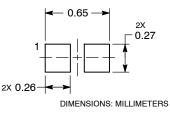

#### RECOMMENDED SOLDER FOOTPRINT\*

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 98AON06808G                           | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION: X4DFN2, 0.60x0.30, 0.36P |                                                                                                                                                                                     | PAGE 1 OF 1 |  |  |

| ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding<br>the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically<br>disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the<br>rights of others. |                                       |                                                                                                                                                                                     |             |  |  |