### ESDR0524P

### **ESD Protection Diode**

## Low Capacitance ESD Protection for High Speed Data

The ESDR0524P surge protection is designed to protect high speed data lines from ESD. Ultra-low capacitance and low ESD clamping voltage make this device an ideal solution for protecting voltage sensitive high speed data lines. The flow-through style package allows for easy PCB layout and matched trace lengths necessary to maintain consistent impedance between high speed differential lines such as HDMI.

#### **Features**

- Low Capacitance (0.3 pF Typical, I/O to I/O)

- ESD Rating of Class 3B (Exceeding 8 kV) per Human Body model and Class C (Exceeding 400 V) per Machine Model

- Protection for the Following IEC Standards: IEC 61000-4-2 (±8 kV Contact)

- UL Flammability Rating of 94 V-0

- This is a Pb-Free Device

#### **Typical Applications**

- HDMI

- DVI

- Display Port

- MDDI

- eSATA

#### **MAXIMUM RATINGS** (T<sub>J</sub> = 25°C unless otherwise noted)

| Rating                                                 | Symbol           | Value       | Unit     |

|--------------------------------------------------------|------------------|-------------|----------|

| Operating Junction Temperature Range                   | $T_{J}$          | -55 to +125 | °C       |

| Storage Temperature Range                              | T <sub>stg</sub> | -55 to +150 | °C       |

| Lead Solder Temperature –<br>Maximum (10 Seconds)      | TL               | 260         | °C       |

| IEC 61000-4-2 Contact (ESD)<br>IEC 61000-4-2 Air (ESD) | ESD<br>ESD       | ±12<br>±15  | kV<br>kV |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

See Application Note AND8308/D for further description of survivability specs.

### ON Semiconductor®

www.onsemi.com

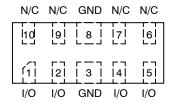

#### MARKING DIAGRAM

#### UDFN10 CASE 517BB

4P = Specific Device Code

M = Date Code\*

= Pb-Free Package

(Note: Microdot may be in either location)

\*Date Code orientation and/or position may vary depending upon manufacturing location.

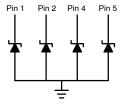

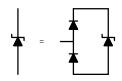

# PIN CONFIGURATION AND SCHEMATIC

Pins 3, 8

#### **ORDERING INFORMATION**

| Device         | Package             | Shipping              |

|----------------|---------------------|-----------------------|

| ESDR0524PMUTAG | UDFN10<br>(Pb-Free) | 3000 /<br>Tape & Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

1

#### ESDR0524P

### **ELECTRICAL CHARACTERISTICS** ( $T_A = 25^{\circ}C$ unless otherwise specified)

| Parameter               | Symbol         | Conditions                                                      | Min | Тур | Max | Unit |

|-------------------------|----------------|-----------------------------------------------------------------|-----|-----|-----|------|

| Reverse Working Voltage | $V_{RWM}$      | I/O Pin to GND (Note 1)                                         |     |     | 5.0 | V    |

| Breakdown Voltage       | $V_{BR}$       | I <sub>T</sub> = 1 mA, I/O Pin to GND                           | 5.5 |     |     | V    |

| Reverse Leakage Current | I <sub>R</sub> | V <sub>RWM</sub> = 5 V, I/O Pin to GND                          |     |     | 1.0 | μΑ   |

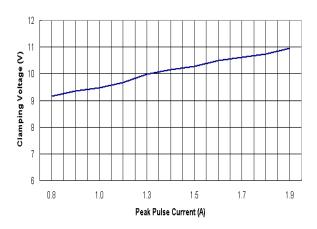

| Clamping Voltage        | V <sub>C</sub> | I <sub>PP</sub> = 1 A, I/O Pin to GND (8 x 20 μs pulse)         |     |     | 15  | V    |

| Junction Capacitance    | CJ             | V <sub>R</sub> = 0 V, f = 1 MHz between I/O Pins                |     | 0.3 | 0.4 | pF   |

| Junction Capacitance    | CJ             | $V_R = 0 \text{ V, f} = 1 \text{ MHz}$ between I/O Pins and GND |     | 0.5 | 0.8 | pF   |

Surge protection devices are normally selected according to the working peak reverse voltage (V<sub>RWM</sub>), which should be equal or greater than the DC or continuous peak operating voltage level.

#### ESDR0524P

#### **TYPICAL CHARACTERISTICS**

Figure 1. Clamping Voltage vs. Peak Pulse Current

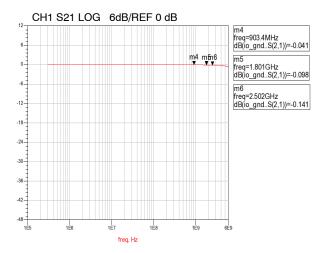

Figure 3. Insertion Loss S21 - I/O to GND

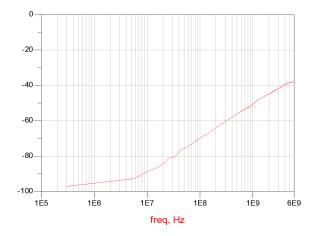

Figure 5. Analog Crosstalk - I/O to I/O

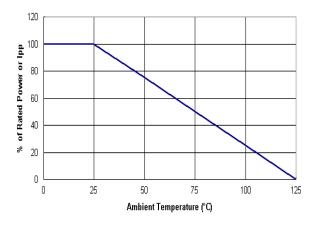

Figure 2. Power Derating Curve

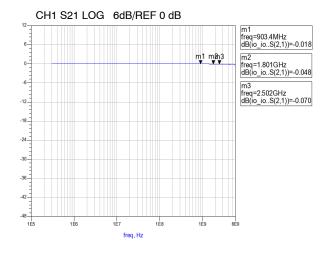

Figure 4. Insertion Loss S21 - I/O to I/O

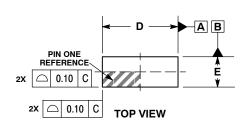

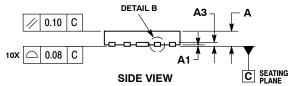

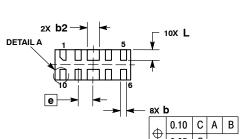

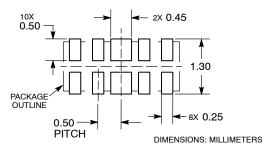

### **MECHANICAL CASE OUTLINE**

#### UDFN10 2.5x1, 0.5P CASE 517BB-01 **ISSUE 0**

**DATE 17 NOV 2009**

С 0.05

NOTE 3

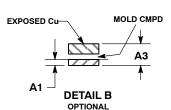

OPTIONAL CONSTRUCTIONS

CONSTRUCTION

#### NOTES:

- DIMENSIONING AND TOLERANCING PER

ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.30mm FROM TERMINAL.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 0.45        | 0.55 |  |

| A1  | 0.00        | 0.05 |  |

| A3  | 0.13 REF    |      |  |

| b   | 0.15        | 0.25 |  |

| b2  | 0.35        | 0.45 |  |

| D   | 2.50 BSC    |      |  |

| Е   | 1.00 BSC    |      |  |

| е   | 0.50 BSC    |      |  |

| L   | 0.30        | 0.40 |  |

| L1  |             | 0.05 |  |

#### **GENERIC MARKING DIAGRAM\***

XXX = Specific Device Code

= Date Code M

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

#### **RECOMMENDED SOLDERING FOOTPRINT\***

**BOTTOM VIEW**

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON47059E        | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | UDFN10 2.5X1, 0.5P |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and unare trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.