# 24-Bit Single-Channel Precision µModule Data Acquisition System

#### **FEATURES**

- ▶ Highly-integrated data acquisition solution

- ▶ Seven programmable-gain options

- ► G = 0.325, 0.65, 1.3, 2.6, 5.2, 10.4, 20.8 V/V

- Maximum input range of ±12.6 V differential

- ▶ Maximum input common-mode range of -12 V to +12 V

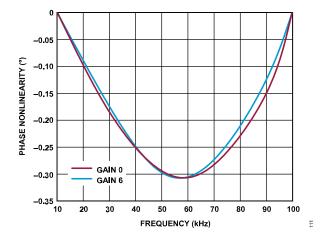

- ▶ Fourth-order AAF with maximum flatness and linear phase

- ► Full aliasing protection with 100 dB typical rejection

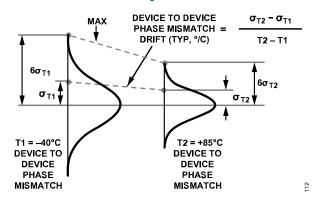

- ▶ Excellent device-to-device phase matching and drift

- Combined precision AC and DC performance:

- ▶ Total system dynamic range up to 130 dB

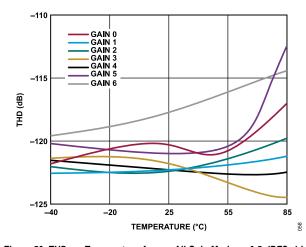

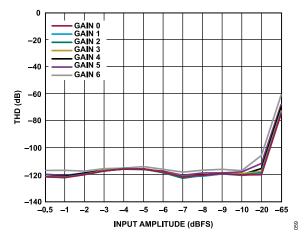

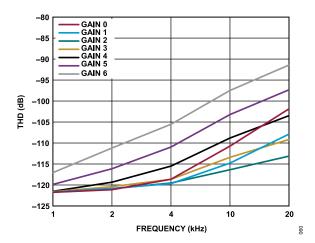

- ▶ -120 dB typical THD at 0.325 V/V gain

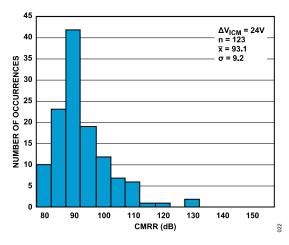

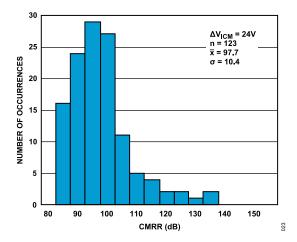

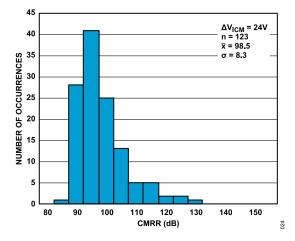

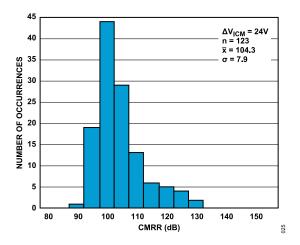

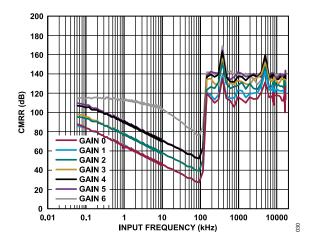

- ▶ 100 dB minimum DC CMRR at 20.8 V/V gain

- 25 pA maximum input bias current at 25°C

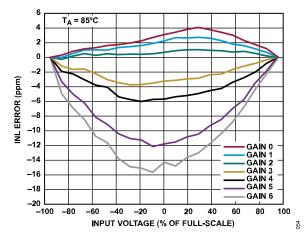

- ▶ ±6 ppm typical INL

- ▶ 5.5 ppm/°C maximum gain error drift

- ▶ ±0.13° maximum device-to-device phase mismatch at 20 kHz

- ▶ Programmable output data rate, filter type, and latency

- ▶ Linear phase digital filter options:

- Wideband low-ripple FIR filter (110 kHz maximum input bandwidth)

- ▶ Sinc5 filter (1.024 MSPS, 198.4 kHz maximum input bandwidth, 4 µs maximum group delay)

- ► Sinc3 filter (50 Hz/60 Hz rejection)

- Integrated LDO

- Built-in supply decoupling capacitors

- ▶ Configuration through pin strapping or SPI

- ▶ Digital interface optimized for isolated applications

- ▶ Suite of diagnostic check mechanisms

- ▶ Operating temperature range: -40°C to +85°C

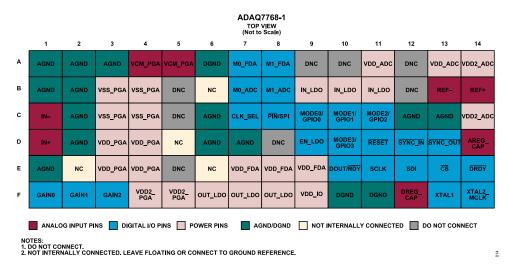

- ► Packaging:12.00 mm × 6.00 mm 84-ball CSP\_BGA with an 0.80 mm ball pitch

- ▶ 10× footprint reduction vs. discrete solution

## **APPLICATIONS**

- Universal input measurement platform

- Electrical test and measurement

- Sound and vibration, acoustic and material science research and development

- Control and hardware in loop verification

- ▶ Condition monitoring for predictive maintenance

- Audio test

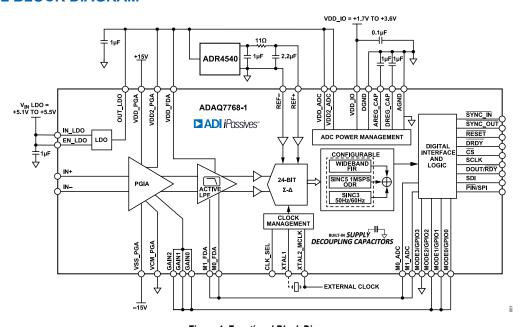

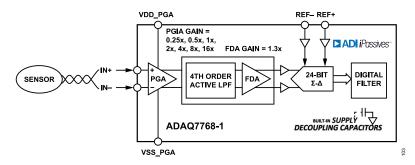

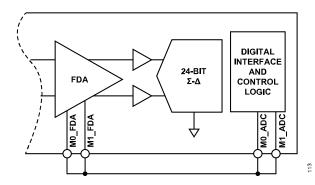

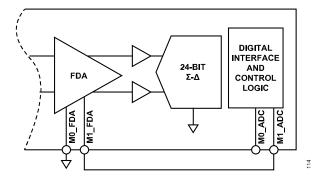

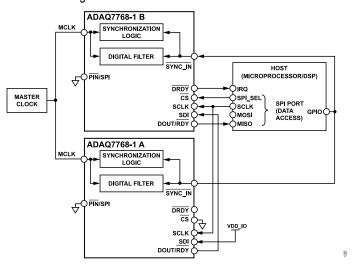

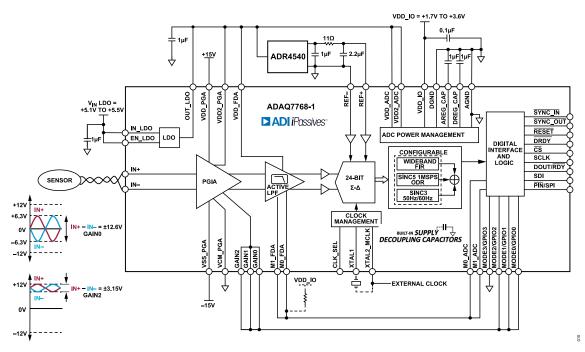

# FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

Protected by U.S. patents 10,680,633 B1 and 10,979,062 B2.

# **TABLE OF CONTENTS**

| Features                                    | 1  | Continuous Conversion Mode                  | 77 |

|---------------------------------------------|----|---------------------------------------------|----|

| Applications                                | 1  | One-Shot Conversion Mode                    | 77 |

| Functional Block Diagram                    | 1  | Synchronization of Multiple ADAQ7768-1      |    |

| General Description                         | 4  | Devices                                     | 79 |

| Specifications                              | 5  | Additional Functionality of the ADAQ7768-1  | 80 |

| Timing Specifications                       | 14 | Reset                                       | 80 |

| 1.8 V Timing Specifications                 |    | Status Header                               | 80 |

| Absolute Maximum Ratings                    |    | Diagnostics                                 | 80 |

| Thermal Resistance                          |    | Applications Information                    | 81 |

| Electrostatic Discharge (ESD) Ratings       | 19 | Quick Start-Up                              |    |

| Pin Configuration and Function Descriptions |    | Sensor Interfacing and Gain Control         |    |

| Typical Performance Characteristics         |    | Isolation and Power Solution                |    |

| Terminology                                 |    | Power Supply Sequencing                     |    |

| Theory of Operation                         |    | Reference, Reference Buffer, and Linearity  |    |

| Analog Input                                |    | Boost Buffer                                | 81 |

| Analog Input Range                          |    | Recommended Interface                       |    |

| Selecting the Input Range                   |    | Programmable Digital Filter                 |    |

| Anti-Aliasing Filter                        |    | Layout Guidelines                           |    |

| FDA Power Modes                             |    | Register Summary                            |    |

| Linearity Boost Buffers                     |    | Register Details                            |    |

| Reference Input and Buffering               |    | Component Type Register                     |    |

| Core Converter                              |    | Unique Product ID Register                  |    |

| Power Supplies                              |    | Device Grade and Revision Register          |    |

| Power Supply Decoupling                     |    | User Scratchpad Register                    |    |

| Power Standby                               |    | Device Vendor ID Register                   |    |

| Clocking and Sampling Tree                  |    | Interface Format Control Register           |    |

| Clocking and Clock Selection                |    | Power and Clock Control Register            |    |

| Digital Filtering                           |    | Analog Buffer Control Register              |    |

| ADC Speed and Performance                   |    | Conversion Source Select and Mode           |    |

| Device Configuration Method                 |    | Control Register                            | 90 |

| Pin Control Mode Overview                   |    | Digital Filter and Decimation Control       | 00 |

| SPI Control Overview                        |    | Register                                    | 91 |

| SPI Control Mode                            |    | SINC3 Decimation Rate (MSB) Register        |    |

| Quick Start-Up Guide                        |    | SINC3 Decimation Rate (LSB) Register        |    |

| Power Supply Connection                     |    | Periodic Conversion Rate Control Register   |    |

| Device Control Mode                         |    | Synchronization Modes and Reset             | 0_ |

| Selecting the Input Range                   |    | Triggering Register                         | 92 |

| Selecting the MCLK Divider and Source       |    | GPIO Port Control Register                  |    |

| Digital Filter Setting                      |    | GPIO Output Control Register                |    |

| ADC Power Mode                              |    | GPIO Input Read Register                    |    |

| Basic Register Setup                        |    | Offset Calibration MSB Register             |    |

| Noise Performance and Resolution            |    | Offset Calibration MID Register             |    |

| Digital Interface                           |    | Offset Calibration LSB Register             |    |

| SPI Reading and Writing                     |    | Gain Calibration MSB Register               |    |

| SPI Control Error Handling                  |    | Gain Calibration MID Register               |    |

| Cyclic Redundancy Check (CRC) on Serial     |    | Gain Calibration LSB Register               |    |

| Interface                                   |    | SPI Diagnostic Control Register             |    |

| Conversion Read Modes                       |    | ADC Diagnostic Feature Control Register     |    |

| Data Conversion Modes                       |    | Digital Diagnostic Feature Control Register |    |

|                                             |    | gg                                          | 55 |

analog.com Rev. 0 | 2 of 98

# **TABLE OF CONTENTS**

| Conversion Result Register          | 95 | Coefficient Control Register | 96 |

|-------------------------------------|----|------------------------------|----|

| Device Error Flags Master Register  | 95 | Coefficient Data Register    | 97 |

| SPI Error Register                  | 96 | Access Key Register          | 97 |

| ADC Diagnostics Output Register     | 96 | Outline Dimensions           | 98 |

| Digital Diagnostics Output Register | 96 | Ordering Guide               | 98 |

| MCLK Diagnostic Output Register     |    | Evaluation Boards            |    |

# **REVISION HISTORY**

3/2023—Revision 0: Initial Version

analog.com Rev. 0 | 3 of 98

### **GENERAL DESCRIPTION**

The ADAQ7768-1 is a 24-bit precision data acquisition (DAQ) µModule® system that encapsulates signal conditioning, conversion, and processing blocks into one system-in-package (SiP) design for the rapid development of highly compact, high-performance precision DAQ systems.

The ADAQ7768-1 consists of:

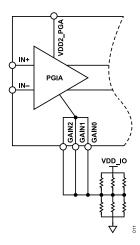

- A low-noise, low-bias current, high-bandwidth programmablegain instrumentation amplifier (PGIA) also capable of signal amplification and signal attenuation while maintaining high input impedance.

- ▶ A fourth-order, low-noise, linear phase anti-aliasing filter.

- A low-noise, low-distortion, high-bandwidth ADC driver plus an optional linearity boost buffer.

- $\blacktriangleright$  A high-performance medium bandwidth 24-bit Σ- $\Delta$  ADC with programmable digital filter.

- ▶ A low-noise, low-dropout linear regulator.

- ▶ Reference buffers.

- ▶ Critical passive components required for the signal chain.

The ADAQ7768-1 supports fully differential input signal with a maximum range of ±12.6 V. It has an input common-mode voltage range of ±12 V with excellent common-mode rejection ratio (CMRR).

The input signal is fully buffered with very low input bias current of 2 pA typical. This allows easy input impedance matching and enables the ADAQ7768-1 to directly interface to sensors with high output impedance.

The seven pin-configurable gain settings offer additional system dynamic range and improved signal chain noise performance with input signals of lower amplitude.

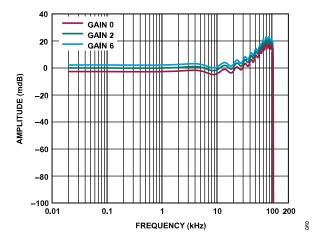

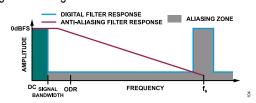

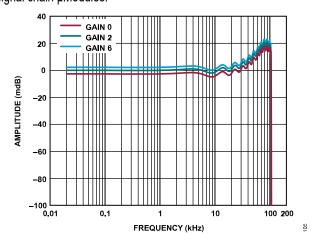

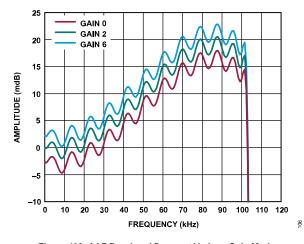

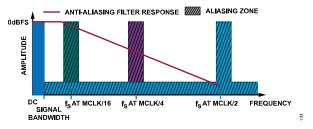

A fourth-order low-pass analog filter combined with the user-programmable digital filter ensures the signal chain is fully protected against the high frequency noise and out-of-band tones presented at the input node from aliasing back into the band of interest. The analog low-pass filter is carefully designed to achieve high phase linearity and maximum in-band magnitude response flatness. Constructed with Analog Devices's iPASSIVES™ technology, the resistor network used within the analog low-pass filter possesses superior resistance matching in both absolute values and overtemperature. As a result, the signal chain performance is maintained with minimum drift overtemperature and the ADAQ7768-1 has a tight phase mismatch across devices.

A high-performance ADC driver amplifier ensures the full settling of the ADC input at the maximum sampling rate. The driver circuit is designed for minimum additive noise, error, and distortion while maintaining stability. The fully differential architecture helps to maximize the signal chain dynamic range.

The analog-to-digital converter (ADC) inside the ADAQ7768-1 is a high-performance, 24-bit precision, single-channel sigma-delta converter with excellent AC performance and DC precision, and the throughput rate of 256 kSPS from a 16.384 MHz MCLK.

An optional linearity boost buffer further improves the signal chain linearity.

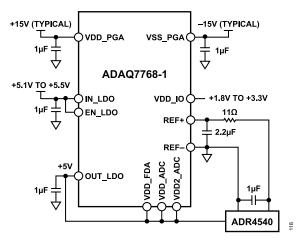

The ADAQ7768-1 is specified with the input reference voltage of 4.096 V, but the device can support reference voltages ranging from VDD ADC down to 1 V.

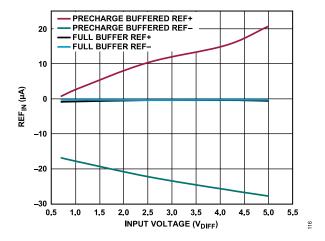

The ADAQ7768-1 has two types of reference buffers: a precharge reference buffer to ease the reference input driving requirement or a full reference buffer to provide high impedance reference input. Both buffers are optional and can be turned off through register configuration.

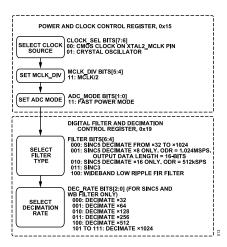

ADAQ7768-1 supports three clock input types: crystal, complementary-metal-oxide-semiconductor (CMOS), or low-voltage differential signaling (LVDS).

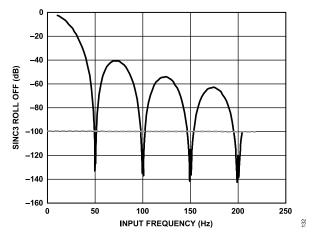

Three types of digital low pass filters are available on the ADAQ7768-1. The wideband filter offers a filter profile similar to an ideal brick wall filter, making it ideal for frequency analysis. The sinc5 filter offers a low latency path with a smooth step response while maintaining a good level of aliasing rejection. It also supports an output data rate up to 1.024 MSPS from a 16.384 MHz MCLK, making the sinc5 filter ideal for low latency data capturing and time domain analysis. The sinc3 filter supports a wide decimation ratio and can produce output data rate down to 50 SPS from a 16.384 MHz MCLK. This, combined with the simultaneous 50Hz/ 60Hz rejection post filter, makes the sinc3 filter especially useful for precision DC measurement. All the three digital filters on the ADAQ7768-1 are FIR filters with linear phase response. The bandwidths of the filters, which directly correspond to the bandwidth of the DAQ signal chain, are fully programmable through register configuration.

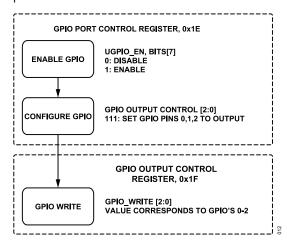

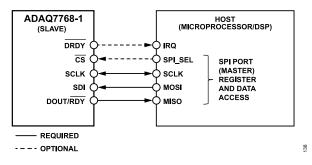

The ADAQ7768-1 also supports two device configuration methods. The user has the option to choose to configure the device through register write through its SPI, or through a simple hardware pin strapping method to configure the device to operate under a number of predefined modes.

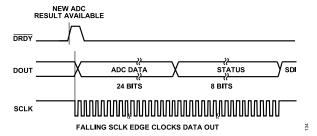

A single SPI supports both the register access and sample data readback functions. The ADAQ7768-1 always acts as a SPI target. Multiple interface modes are supported with a minimum of three IO channels required to communicate with the device.

The ADAQ7768-1 also features a suite of internal diagnostic functions to detect a broad range of errors during operation to improve the system reliability.

The ADAQ7768-1 device has an operating temperature range of -40°C to +85°C and is available in a 12.00 mm × 6.00 mm 84-ball CSP\_BGA package with an 0.80 mm ball pitch, which makes it ideal for multiple channel applications. The ADAQ7768-1 uses only 75 mm<sup>2</sup> of board space, 10 times less than the discrete solution that uses 750 mm<sup>2</sup>.

analog.com Rev. 0 | 4 of 98

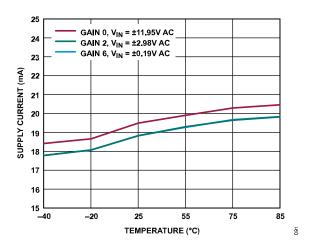

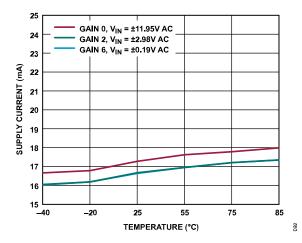

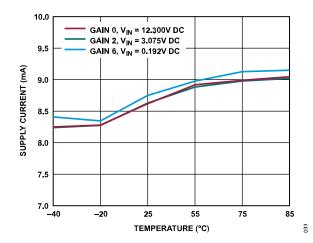

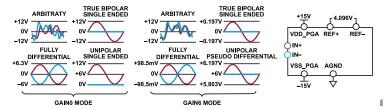

# **SPECIFICATIONS**

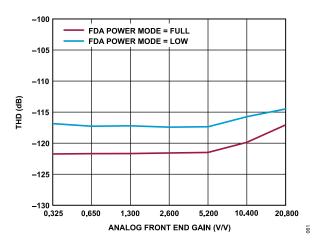

VDD\_PGA = 15 V, VSS\_PGA = -15 V, AGND = DGND = 0 V, input common-mode voltage = 0 V, IN\_LDO = 5.1 V to 5.5 V, OUT\_LDO = VDD2\_PGA = VDD\_ADC, VDD2\_ADC = 2 V to 5.5 V, VDD\_IO = 1.7 V to 3.6 V, REF+ = 4.096 V, REF- = 0 V, MCLK = SCLK = 16.384 MHz 50:50 duty cycle,  $f_{\text{MOD}}$  = MCLK/2, filter = wideband low ripple, decimation = 32, ODR = 256 kSPS, linearity boost buffer on, reference precharge buffers on, FDA = full power mode,  $T_{\text{A}}$  =  $-40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_{\text{A}}$  =  $25^{\circ}\text{C}$ .

Table 1.

| Parameter                            | Test Conditions/Comments                    | Min            | Тур     | Max         | Unit |

|--------------------------------------|---------------------------------------------|----------------|---------|-------------|------|

| ANALOG INPUT CHARACTERISTICS         |                                             |                |         |             |      |

| Input Bias Current                   | T <sub>A</sub> = 25°C                       |                | 2       | 25          | pA   |

| ·                                    | -40°C < T <sub>A</sub> < +85°C              |                |         | 100         | pA   |

| Input Offset Current                 | T <sub>A</sub> = 25°C                       |                | 2       | 25          | pA   |

| ·                                    | -40°C < T <sub>A</sub> < +85°C              |                |         | 60          | pA   |

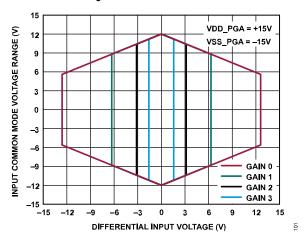

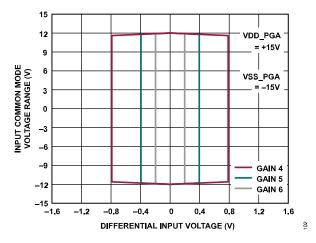

| Input Voltage Range                  | Individual pin, IN+ and IN-                 | VSS_PGA + 3.25 |         | VDD_PGA - 3 | V    |

| Input Common Mode Range <sup>1</sup> |                                             | -12            |         | 12          | V    |

| Analog Front-End Gain (AFE_GAIN)     | Gain 0 mode                                 |                | 0.325   |             | V/V  |

| , - ,                                | Gain 1 mode                                 |                | 0.65    |             | V/V  |

|                                      | Gain 2 mode                                 |                | 1.3     |             | V/V  |

|                                      | Gain 3 mode                                 |                | 2.6     |             | V/V  |

|                                      | Gain 4 mode                                 |                | 5.2     |             | V/V  |

|                                      | Gain 5 mode                                 |                | 10.4    |             | V/V  |

|                                      | Gain 6 mode                                 |                | 20.8    |             | V/V  |

| Full-Scale Input Range (FSR)         | Differential IN+ to IN-                     |                |         |             |      |

| ,                                    | FSR = ±V <sub>REF</sub> /AFE_GAIN           |                |         |             |      |

|                                      | Gain 0 mode                                 |                | ±12.603 |             | V    |

|                                      | Gain 1 mode                                 |                | ±6.302  |             | V    |

|                                      | Gain 2 mode                                 |                | ±3.151  |             | V    |

|                                      | Gain 3 mode                                 |                | ±1.575  |             | V    |

|                                      | Gain 4 mode                                 |                | ±0.788  |             | V    |

|                                      | Gain 5 mode                                 |                | ±0.394  |             | V    |

|                                      | Gain 6 mode                                 |                | ±0.197  |             | V    |

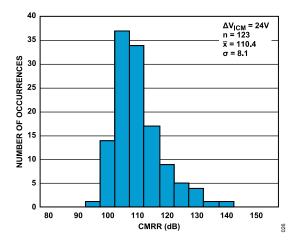

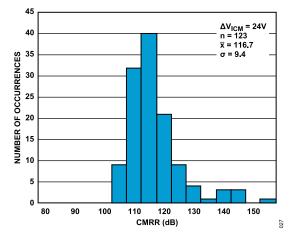

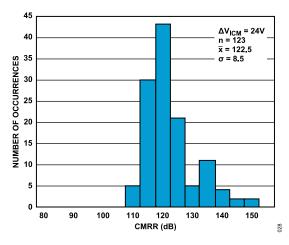

| Common-Mode Rejection DC             | DC to 60 Hz, RTI, V <sub>ICM</sub> = ± 10 V |                |         |             |      |

| Gain 0 Mode                          | T <sub>A</sub> = 25°C                       |                | 92      |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 71             |         |             |      |

| Gain 1 Mode                          | T <sub>A</sub> = 25°C                       |                | 95      |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 75             |         |             |      |

| Gain2 Mode                           | T <sub>A</sub> = 25°C                       |                | 97      |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 78             |         |             |      |

| Gain 3 Mode                          | T <sub>A</sub> = 25°C                       |                | 102     |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 84             |         |             |      |

| Gain 4 Mode                          | T <sub>A</sub> = 25°C                       |                | 108     |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 90             |         |             |      |

| Gain 5 Mode                          | T <sub>A</sub> = 25°C                       |                | 114     |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 95             |         |             |      |

| Gain 6 Mode                          | T <sub>A</sub> = 25°C                       |                | 120     |             | dB   |

|                                      | -40°C < T <sub>A</sub> < +85°C              | 100            |         |             |      |

| Common-Mode Rejection AC             | AC CMRR (f = 1 kHz), RTI                    |                |         |             |      |

| - ·-··                               | Gain 0 mode                                 |                | 63      |             | dB   |

|                                      | Gain 1 mode                                 |                | 65      |             | dB   |

|                                      | Gain 2 mode                                 |                | 78      |             | dB   |

|                                      | Gain 3 mode                                 |                | 78      |             | dB   |

analog.com Rev. 0 | 5 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                   | Test Conditions/Comments                                                              | Min   | Тур                  | Max   | Unit       |

|-----------------------------|---------------------------------------------------------------------------------------|-------|----------------------|-------|------------|

|                             | Gain 4 mode                                                                           |       | 90                   |       | dB         |

|                             | Gain 5 mode                                                                           |       | 90                   |       | dB         |

|                             | Gain 6 mode                                                                           |       | 113                  |       | dB         |

| Input Current Noise         |                                                                                       |       |                      |       |            |

| Spectral Density            | f = 10 kHz                                                                            |       | 1                    |       | fA/√Hz     |

| Peak-to-Peak                | f = 0.1 Hz to 10 Hz                                                                   |       | 100                  |       | fA p-p     |

| Input Resistance            | Common mode and differential                                                          |       | 5 × 10 <sup>12</sup> |       | Ω          |

| Input Capacitance           |                                                                                       |       | 15                   |       | pF         |

| VERALL SYSTEM DC ACCURACY   |                                                                                       |       |                      |       |            |

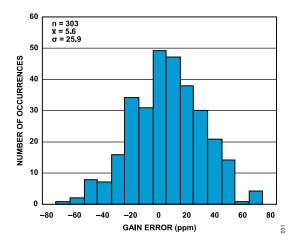

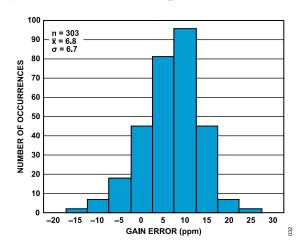

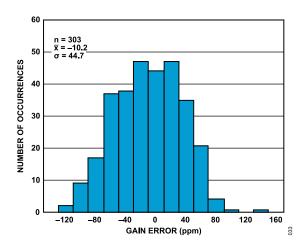

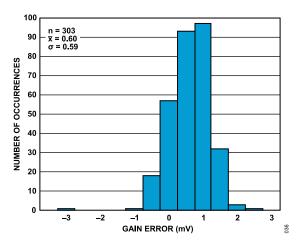

| Gain Error                  | All gain modes, RTI, T <sub>A</sub> = 25°C                                            | -0.05 | ±0.005               | +0.05 | %          |

|                             |                                                                                       | -500  | ±50                  | +500  | ppm        |

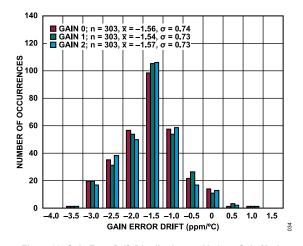

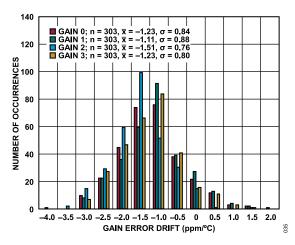

| Gain Error Drift            | All gain modes, RTI, endpoint method                                                  | -5.5  | -1.6                 | +2.5  | ppm/°C     |

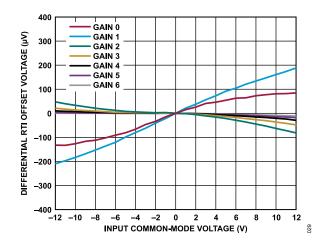

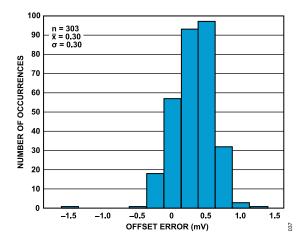

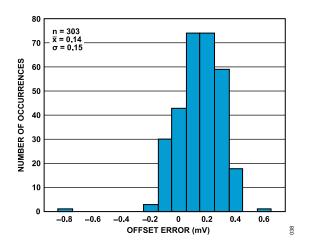

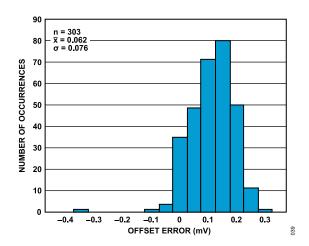

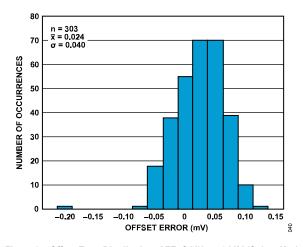

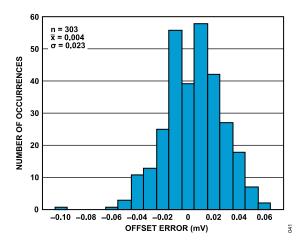

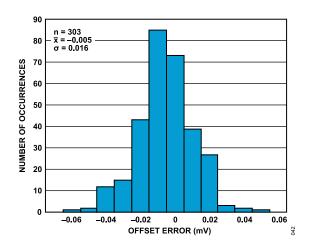

| Offset Error                | RTI, T <sub>A</sub> = 25°C                                                            |       |                      |       |            |

|                             | Gain 0 mode                                                                           |       | ±0.60                | ±5.8  | mV         |

|                             | Gain 1 mode                                                                           |       | ±0.30                | ±2.9  | mV         |

|                             | Gain 2 mode                                                                           |       | ±0.14                | ±2.1  | mV         |

|                             | Gain 3 mode                                                                           |       | ±0.06                | ±1.4  | mV         |

|                             | Gain 4 mode                                                                           |       | ±0.02                | ±1.0  | mV         |

|                             | Gain 5 mode                                                                           |       | ±0.01                | ±0.8  | mV         |

|                             | Gain 6 mode                                                                           |       | ±0.01                | ±0.7  | mV         |

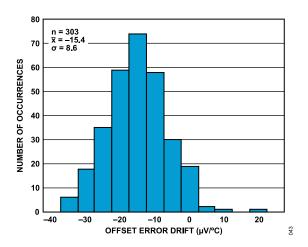

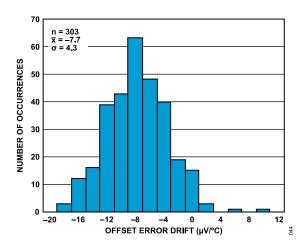

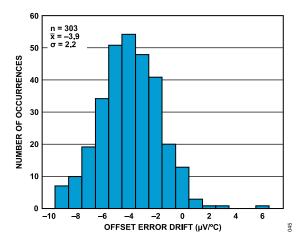

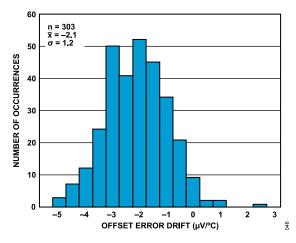

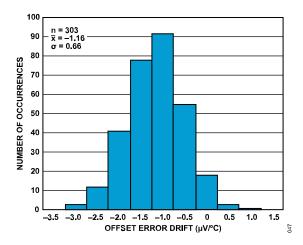

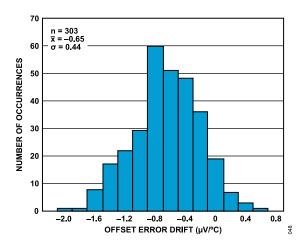

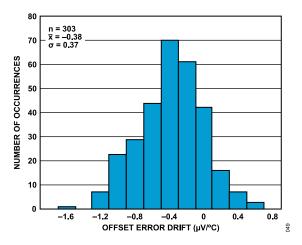

| Offset Error Drift          | RTI, endpoint method                                                                  |       |                      |       |            |

|                             | Gain 0 mode                                                                           | -61.0 | -16.0                | +29.0 | μV/°C      |

|                             | Gain 1 mode                                                                           | -31.0 | -8.0                 | +15.0 | μV/°C      |

|                             | Gain 2 mode                                                                           | -16.0 | -4.0                 | +8.0  | μV/°C      |

|                             | Gain 3 mode                                                                           | -8.5  | -2.2                 | +4.0  | μV/°C      |

|                             | Gain 4 mode                                                                           | -5.0  | -1.2                 | +2.5  | μV/°C      |

|                             | Gain 5 mode                                                                           | -3.0  | -0.7                 | +1.7  | μV/°C      |

|                             | Gain 6 mode                                                                           | -2.2  | -0.5                 | +1.3  | μV/°C      |

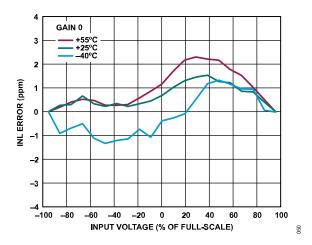

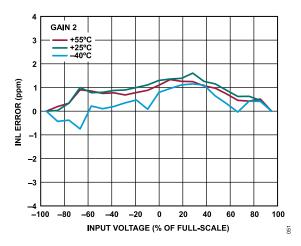

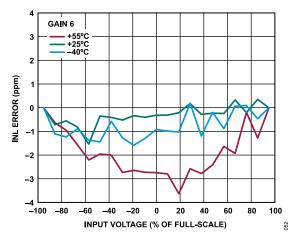

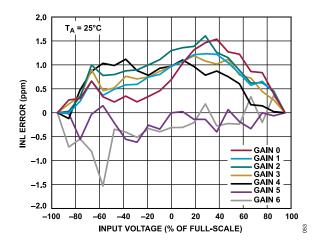

| Integral Nonlinearity (INL) | Endpoint method                                                                       |       | 0.0                  | . 1.0 | μν, σ      |

| Gain 0 Mode                 | T <sub>A</sub> = 25°C                                                                 |       | ±6                   |       | ppm of FSR |

| Can o Modo                  | -40°C < T < +85°C                                                                     |       | 20                   | ±18   | ppm of FSR |

| Gain 1 Mode                 | T <sub>A</sub> = 25°C                                                                 |       | ±6                   | 110   | ppm of FSR |

| Cam i wode                  | -40°C < T <sub>A</sub> < +85°C                                                        |       | 10                   | ±17   | ppm of FSR |

| Gain 2 Mode                 | T <sub>A</sub> = 25°C                                                                 |       | ±6                   | ±17   | ppm of FSR |

| Guill 2 Wode                | -40°C < T <sub>A</sub> < +85°C                                                        |       | 10                   | ±17   | ppm of FSR |

| Gain 3 Mode                 | $T_A = 25^{\circ}C$                                                                   |       | ±6                   | 217   | ppm of FSR |

| Gain o Mode                 | -40°C < T <sub>A</sub> < +85°C                                                        |       | 10                   | ±18   | ppm of FSR |

| Gain 4 Mode                 | T <sub>A</sub> = 25°C                                                                 |       | ±6                   | 110   | ppm of FSR |

| Gain + Mode                 | -40°C < T <sub>A</sub> < +85°C                                                        |       | 10                   | ±19   | ppm of FSR |

| Gain 5 Mode                 | T <sub>A</sub> = 25°C                                                                 |       | ±6                   | 113   | ppm of FSR |

| Gain 5 Mode                 | -40°C < T <sub>A</sub> < +85°C                                                        |       | 10                   | ±22   | ppm of FSR |

| Gain 6 Mode                 | T <sub>A</sub> = 25°C                                                                 |       | ±6.5                 | ±22   | ppm of FSR |

| Call O Mode                 | -40°C < T <sub>A</sub> < +85°C                                                        |       | ±0.0                 | ±30   | ppm of FSR |

| Low Frequency Noise         | Sinc3 filter, ODR = 50 SPS, bandwidth = 15<br>Hz, shorted input, RTI, FDA = low power |       |                      | 100   | рршоггог   |

|                             | mode                                                                                  |       |                      |       |            |

|                             | Gain 0 mode                                                                           |       | 1.55                 |       | μV RMS     |

|                             | Gain 1 mode                                                                           |       | 0.89                 |       | μV RMS     |

|                             | Gain 2 mode                                                                           |       | 0.51                 |       | μV RMS     |

analog.com Rev. 0 | 6 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                            | Test Conditions/Comments                     | Min   | Тур   | Max | Unit   |

|--------------------------------------|----------------------------------------------|-------|-------|-----|--------|

|                                      | Gain 3 mode                                  |       | 0.33  |     | μV RMS |

|                                      | Gain4 mode                                   |       | 0.25  |     | μV RMS |

|                                      | Gain 5 mode                                  |       | 0.22  |     | μV RMS |

|                                      | Gain 6 mode                                  |       | 0.21  |     | μV RMS |

|                                      | Sinc3 filter, ODR = 50 SPS, bandwidth =      |       |       |     |        |

|                                      | 15 Hz, shorted input, RTI, FDA = full power  |       |       |     |        |

|                                      | mode                                         |       |       |     |        |

|                                      | Gain 0 mode                                  |       | 3.02  |     | μV RMS |

|                                      | Gain 1 mode                                  |       | 1.55  |     | μV RMS |

|                                      | Gain 2 mode                                  |       | 0.89  |     | μV RMS |

|                                      | Gain 3 mode                                  |       | 0.48  |     | μV RMS |

|                                      | Gain 4 mode                                  |       | 0.30  |     | μV RMS |

|                                      | Gain 5 mode                                  |       | 0.25  |     | μV RMS |

|                                      | Gain 6 mode                                  |       | 0.22  |     | μV RMS |

| Peak-to-Peak Resolution <sup>2</sup> | Sinc3 filter, ODR = 50 SPS, bandwidth = 15   |       |       |     |        |

|                                      | Hz, shorted input, RTI, FDA = low power mode |       |       |     |        |

|                                      | Gain 0 mode                                  |       | 21.2  |     | Bits   |

|                                      | Gain 1 mode                                  |       | 21.0  |     | Bits   |

|                                      | Gain 2 mode                                  |       | 20.8  |     | Bits   |

|                                      | Gain 3 mode                                  |       | 20.5  |     | Bits   |

|                                      | Gain 4 mode                                  |       | 19.9  |     | Bits   |

|                                      | Gain 5 mode                                  |       | 19.9  |     | Bits   |

|                                      | Gain 6 mode                                  |       | 18.1  |     | Bits   |

|                                      | Sinc3 filter, ODR = 50 SPS, bandwidth =      |       | 10.1  |     | DIIS   |

|                                      | 15 Hz, shorted input, RTI, FDA = full power  |       |       |     |        |

|                                      | mode                                         |       |       |     |        |

|                                      | Gain 0 mode                                  |       | 20.3  |     | Bits   |

|                                      | Gain 1 mode                                  |       | 20.2  |     | Bits   |

|                                      | Gain 2 mode                                  |       | 20.0  |     | Bits   |

|                                      | Gain 3 mode                                  |       | 19.9  |     | Bits   |

|                                      | Gain 4 mode                                  |       | 19.6  |     | Bits   |

|                                      | Gain 5 mode                                  |       | 18.9  |     | Bits   |

|                                      | Gain 6 mode                                  |       | 18.0  |     | Bits   |

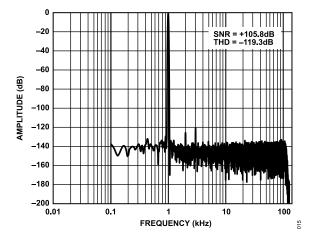

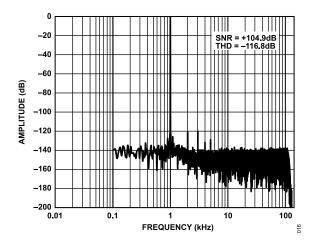

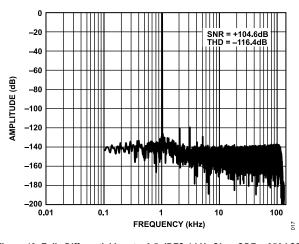

| VERALL SYSTEM AC PERFORMANCE         | Wideband low ripple FIR filter, ODR = 256    |       |       |     |        |

|                                      | kSPS, bandwidth = 110.8 kHz, decimation      |       |       |     |        |

|                                      | by 32                                        |       |       |     |        |

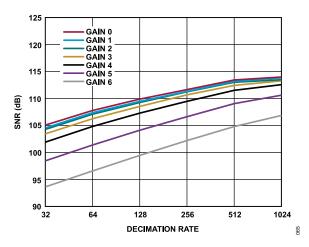

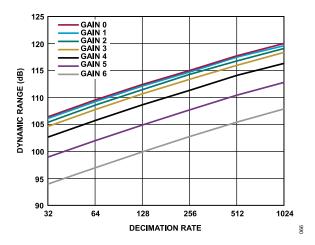

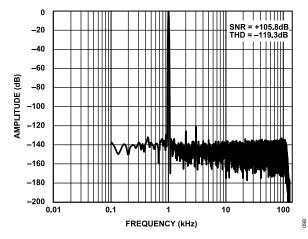

| Dynamic Range <sup>3</sup>           | Shorted input                                |       |       |     |        |

| Gain0 Mode                           |                                              | 105.8 | 106.7 |     | dB     |

|                                      | Bandwidth = 1 Hz                             |       | 157.2 |     | dB     |

| Gain 1 Mode                          |                                              | 105.5 | 106.4 |     | dB     |

|                                      | Bandwidth = 1 Hz                             |       | 156.9 |     | dB     |

| Gain 2 Mode                          |                                              | 104.7 | 105.7 |     | dB     |

|                                      | Bandwidth = 1 Hz                             |       | 156.1 |     | dB     |

| Gain 3 Mode                          |                                              | 103.7 | 104.8 |     | dB     |

|                                      | Bandwidth = 1 Hz                             |       | 155.3 |     | dB     |

| Gain 4 Mode                          |                                              | 101.5 | 102.7 |     | dB     |

|                                      | Bandwidth = 1 Hz                             |       | 153.1 |     | dB     |

| Gain 5 Mode                          |                                              | 97.3  | 98.9  |     | dB     |

|                                      | Bandwidth = 1 Hz                             |       | 149.3 |     | dB     |

analog.com Rev. 0 | 7 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| arameter                                      | Test Conditions/Comments                | Min   | Typ Max | Unit                                  |

|-----------------------------------------------|-----------------------------------------|-------|---------|---------------------------------------|

| Gain6 Mode                                    |                                         | 92.1  | 93.8    | dB                                    |

|                                               | Bandwidth = 1 Hz                        |       | 144.1   | dB                                    |

|                                               | total system                            |       | 130     | dB                                    |

| Noise Spectral Density                        | RTI, shorted input, at 1 kHz            |       |         |                                       |

|                                               | Gain 0 mode                             |       | 122     | nV/√Hz                                |

|                                               | Gain 1 mode                             |       | 63.8    | nV/√Hz                                |

|                                               | Gain 2 mode                             |       | 35      | nV/√Hz                                |

|                                               | Gain 3 mode                             |       | 19      | nV/√Hz                                |

|                                               | Gain 4 mode                             |       | 12.3    | nV/√Hz                                |

|                                               | Gain 5 mode                             |       | 9.5     | nV/√Hz                                |

|                                               | Gain 6 mode                             |       | 8.6     | nV/√Hz                                |

| ntegrated Voltage Noise                       | RTI, shorted input                      |       |         |                                       |

|                                               | Gain 0 mode                             |       | 41.2    | μV RMS                                |

|                                               | Gain 1 mode                             |       | 21.4    | μV RMS                                |

|                                               | Gain 2 mode                             |       | 11.6    | μV RMS                                |

|                                               | Gain 3 mode                             |       | 6.4     | μV RMS                                |

|                                               | Gain 4 mode                             |       | 4.1     | μV RMS                                |

|                                               | Gain 5 mode                             |       | 3.1     | μV RMS                                |

|                                               | Gain 6 mode                             |       | 2.8     | μV RMS                                |

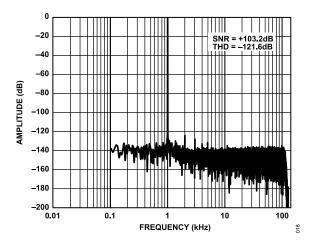

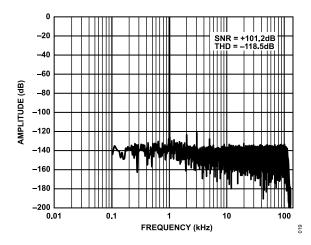

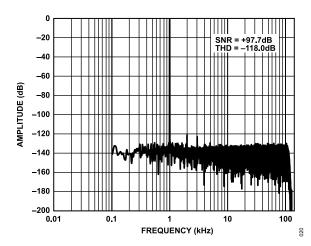

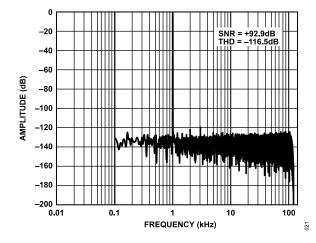

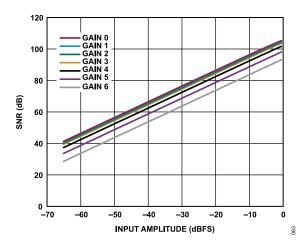

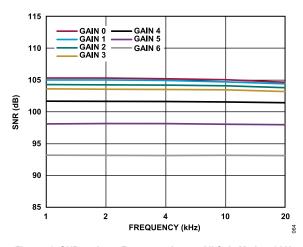

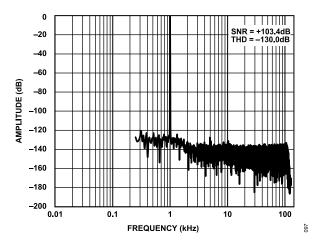

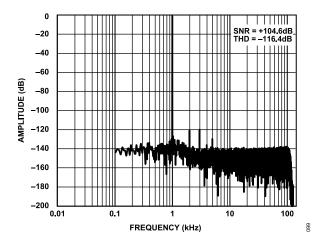

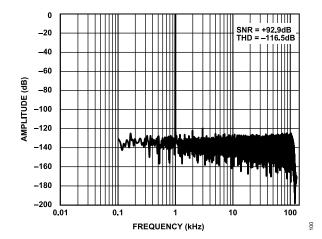

| Signal-to-Noise Ratio (SNR)                   | -0.5 dBFS, sine input, 1 kHz input tone |       |         | F                                     |

|                                               | Gain 0 mode                             | 103.9 | 105.9   | dB                                    |

|                                               | Gain 1 mode                             | 102.2 | 104.9   | dB                                    |

|                                               | Gain 2 mode                             | 101.8 | 104.4   | dB                                    |

|                                               | Gain 3 mode                             | 100.5 | 103.4   | dB                                    |

|                                               | Gain 4 mode                             | 98.5  | 100.8   | dB                                    |

|                                               | Gain 5 mode                             | 96.1  | 98.0    | dB                                    |

|                                               | Gain 6 mode                             | 91.2  | 93.1    | dB                                    |

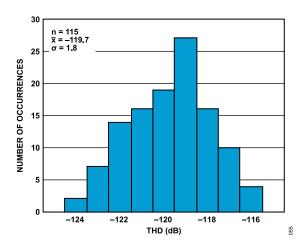

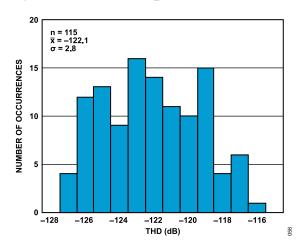

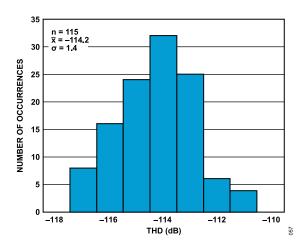

| Total Harmonic Distortion (THD)               | -0.5 dBFS, sine input, 1 kHz input tone | V 12  | 00.1    | 45                                    |

| rotal Flatmonic Biotolium (FIB)               | Gain 0 mode                             |       | -120    | dB                                    |

|                                               | Gain 1 mode                             |       | -120    | dB                                    |

|                                               | Gain 2 mode                             |       | -120    | dB                                    |

|                                               | Gain 3 mode                             |       | -120    | dB                                    |

|                                               | Gain 4 mode                             |       | -120    | dB                                    |

|                                               | Gain 5 mode                             |       | -120    | dB                                    |

|                                               | Gain 6 mode                             |       | -115    | dB                                    |

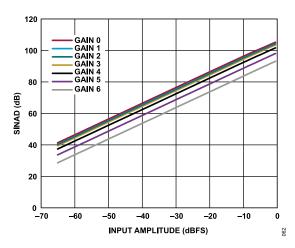

| Signal-to-Noise and Distortion Ratio (SINAD)  | -0.5 dBFS, sine input, 1 kHz input tone |       | 110     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| orginal to 140130 and Distortion (and Conv.D) | Gain 0 mode                             | 103.8 |         | dB                                    |

|                                               | Gain 1 mode                             | 102.1 |         | dB                                    |

|                                               | Gain 2 mode                             | 101.7 |         | dB                                    |

|                                               | Gain 3 mode                             | 100.4 |         | dB                                    |

|                                               | Gain 4 mode                             | 98.4  |         | dB                                    |

|                                               | Gain 5 mode                             | 96.0  |         | dB                                    |

|                                               | Gain 6 mode                             | 91.1  |         | dB                                    |

| Spurious-Free Dynamic Range (SFDR)            | -0.5 dBFS, sine input, 1 kHz input tone | 31.1  |         | ub                                    |

| Opunous-i ree Dynamio Nange (OFDN)            | Gain 0 mode                             |       | 121     | dBc                                   |

|                                               | Gain 1 mode                             |       | 121     | dBc                                   |

|                                               | Gain 2 mode                             |       | 121     | dBc                                   |

|                                               |                                         |       |         |                                       |

|                                               | Gain 3 mode                             |       | 121     | dBc                                   |

|                                               | Gain 4 mode                             | 1     | 121     | dBc                                   |

analog.com Rev. 0 | 8 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                                                    | Test Conditions/Comments                                                                        | Min    | Тур    | Max    | Unit    |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------|--------|--------|---------|

|                                                              | Gain 5 mode                                                                                     |        | 121    |        | dBc     |

|                                                              | Gain 6 mode                                                                                     |        | 116    |        | dBc     |

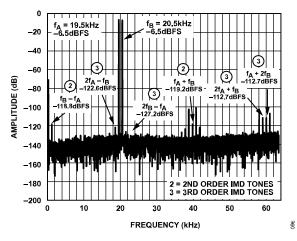

| Intermodulation Distortion (IMD)                             | $f_{IN\_A} = 19.5 \text{ kHz}, f_{IN\_B} = 20.5 \text{ kHz}$                                    |        |        |        |         |

|                                                              | Gain 0 mode second order                                                                        |        | -115   |        | dB      |

|                                                              | Gain 0 mode third order                                                                         |        | -105   |        | dB      |

|                                                              | Gain 2 mode second order                                                                        |        | -115   |        | dB      |

|                                                              | Gain 2 mode third order                                                                         |        | -115   |        | dB      |

|                                                              | Gain 6 mode second order                                                                        |        | -111   |        | dB      |

|                                                              | Gain 6 mode third order                                                                         |        | -95    |        | dB      |

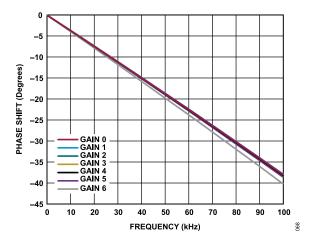

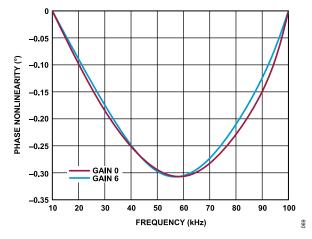

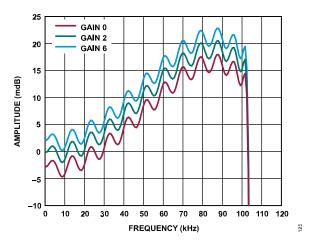

| NALOG FRONT-END MAGNITUDE AND PHASE PERFORMANCE <sup>4</sup> |                                                                                                 |        |        |        |         |

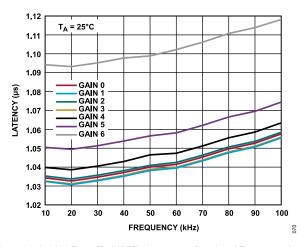

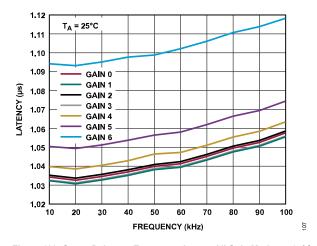

| Analog Group Delay                                           | f <sub>IN</sub> = 20 kHz, Gain0 mode                                                            |        | 1.011  |        | μs      |

|                                                              | f <sub>IN</sub> = 20 kHz, Gain6 mode                                                            |        | 1.070  |        | μs      |

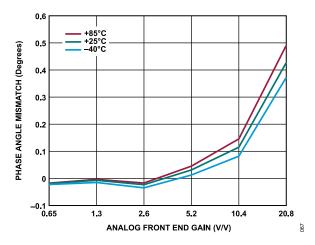

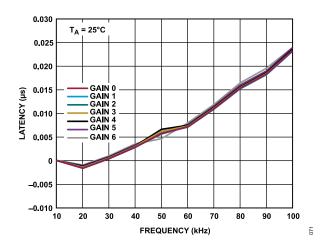

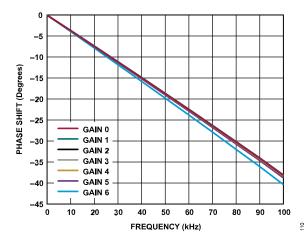

| Phase Angle Mismatch Over Gain                               | Sine wave, f <sub>IN</sub> = 20 kHz, single device, normalized to Gain 0, T <sub>A</sub> = 25°C |        |        |        |         |

|                                                              | Gain 1 mode                                                                                     | -0.030 | -0.019 | -0.008 | Degrees |

|                                                              | Gain 2 mode                                                                                     | -0.038 | -0.007 | 0.024  | Degrees |

|                                                              | Gain 3 mode                                                                                     | -0.055 | -0.023 | 0.008  | Degrees |

|                                                              | Gain 4 mode                                                                                     | 0.000  | 0.031  | 0.062  | Degrees |

|                                                              | Gain 5 mode                                                                                     | 0.084  | 0.115  | 0.146  | Degrees |

|                                                              | Gain 6 mode                                                                                     | 0.363  | 0.427  | 0.491  | Degrees |

| Phase Angle Drift                                            | f <sub>IN</sub> = 20 kHz                                                                        |        |        |        |         |

|                                                              | Gain 0 mode                                                                                     | 0.10   | 0.73   | 1.37   | m°/°C   |

|                                                              | Gain 1 mode                                                                                     | 0.16   | 0.77   | 1.39   | m°/°C   |

|                                                              | Gain 2 mode                                                                                     | 0.20   | 0.83   | 1.46   | m°/°C   |

|                                                              | Gain 3 mode                                                                                     | 0.25   | 0.88   | 1.51   | m°/°C   |

|                                                              | Gain 4 mode                                                                                     | 0.34   | 1.00   | 1.65   | m°/°C   |

|                                                              | Gain 5 mode                                                                                     | 0.55   | 1.24   | 1.94   | m°/°C   |

|                                                              | Gain 6 mode                                                                                     | 0.80   | 1.68   | 2.56   | m°/°C   |

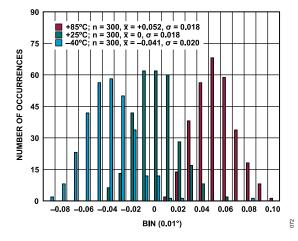

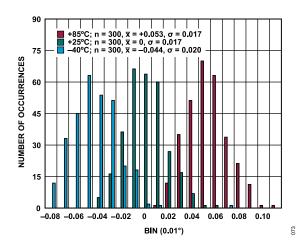

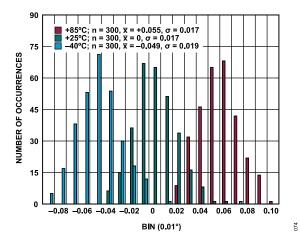

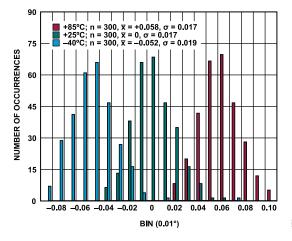

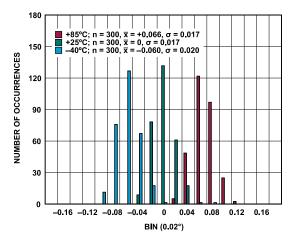

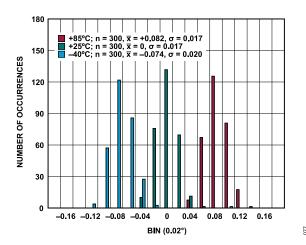

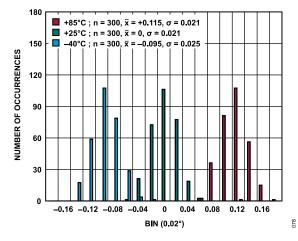

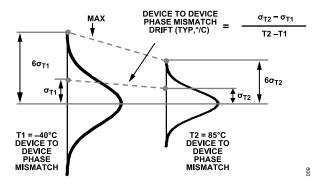

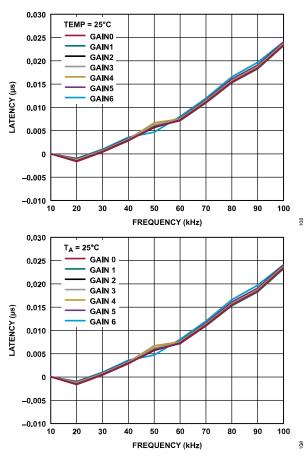

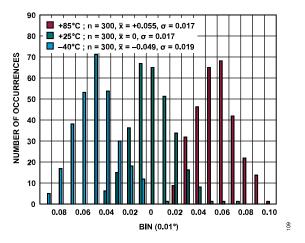

| Device-to-Device Phase Angle Mismatch                        | $f_{IN}$ = 20 kHz, typical = ±1 $\sigma$ , $T_A$ = 25°C                                         |        |        |        |         |

|                                                              | Gain 0 mode                                                                                     | -0.11  | ±0.018 | +0.11  | Degrees |

|                                                              | Gain 1 mode                                                                                     | -0.11  | ±0.017 | +0.11  | Degrees |

|                                                              | Gain 2 mode                                                                                     | -0.11  | ±0.017 | +0.11  | Degrees |

|                                                              | Gain 3 mode                                                                                     | -0.11  | ±0.017 | +0.11  | Degrees |

|                                                              | Gain 4 mode                                                                                     | -0.11  | ±0.017 | +0.11  | Degrees |

|                                                              | Gain 5 mode                                                                                     | -0.11  | ±0.017 | +0.11  | Degrees |

|                                                              | Gain 6 mode                                                                                     | -0.13  | ±0.021 | +0.13  | Degrees |

| Device-to-Device Phase Angle Mismatch Drift                  | f <sub>IN</sub> = 20 kHz, typical = change in  1σ  per °C                                       |        |        |        |         |

|                                                              | Gain 0 mode                                                                                     |        | -21    | -126   | μ°/°C   |

|                                                              | Gain 1 mode                                                                                     |        | -19    | -112   | μ°/°C   |

|                                                              | Gain 2 mode                                                                                     |        | -16    | -97    | μ°/°C   |

|                                                              | Gain 3 mode                                                                                     |        | -16    | -98    | μ°/°C   |

|                                                              | Gain 4 mode                                                                                     |        | -19    | -114   | μ°/°C   |

|                                                              | Gain 5 mode                                                                                     |        | -25    | -149   | μ°/°C   |

|                                                              | Gain 6 mode                                                                                     |        | -30    | -179   | μ°/°C   |

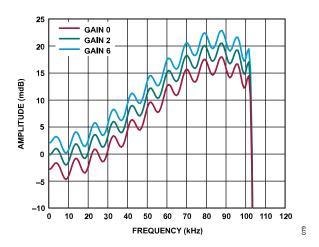

| Magnitude Flatness                                           | f <sub>IN</sub> = 20 kHz                                                                        |        | -2.3   |        | mdB     |

|                                                              | f <sub>IN</sub> = 100 kHz                                                                       |        | -20    |        | mdB     |

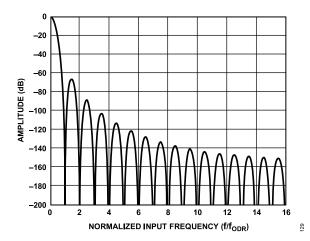

| Alias Rejection                                              | All gain modes, −20 dBFS input signal                                                           |        |        |        |         |

|                                                              | at 16.384 MHz                                                                                   |        | 100    |        | dB      |

analog.com Rev. 0 | 9 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                           | Test Conditions/Comments                              | Min           | Тур                 | Max                | Unit   |

|-------------------------------------|-------------------------------------------------------|---------------|---------------------|--------------------|--------|

|                                     | at 13.107 MHz                                         |               | 100                 |                    | dB     |

| ADC SPEED AND PERFORMANCE           |                                                       |               |                     |                    |        |

| Output Data Rate (ODR) <sup>5</sup> |                                                       |               |                     |                    |        |

|                                     | Wideband low ripple FIR                               | 1             |                     | 256                | kSPS   |

|                                     | Sinc5                                                 | 1             |                     | 1024               | kSPS   |

|                                     | Sinc3                                                 | 0.0125        |                     | 256                | kSPS   |

| No Missing Codes                    | Wideband low ripple FIR filter, decimation ratio ≥ 32 | 24            |                     |                    | Bits   |

|                                     | Sinc5 filter, decimation ratio ≥ 32                   | 24            |                     |                    | Bits   |

|                                     | Sinc3 filter, decimation ratio ≥ 64                   | 24            |                     |                    | Bits   |

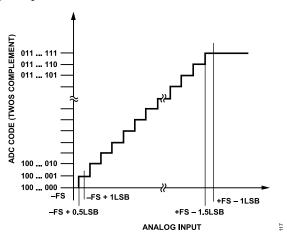

| Data Output Coding                  |                                                       | Twos compleme | nt MSR first        |                    | 2.10   |

| REFERENCE INPUT CHARACTERISTICS     |                                                       | Two compleme  | in, wob mot         |                    |        |

| REFIN Voltage                       | REFIN = (REF+) - (REF-)                               | 1             |                     | VDD_ADC -          | V      |

| KErin voltage                       | KELIN - (KELT) - (KELT)                               | '             |                     | AGND               | V      |

| Absolute REFIN Voltage Limit        | Reference unbuffered                                  | AGND - 0.05   |                     | VDD_ADC + 0.05     | V      |

|                                     | Reference buffer on                                   | AGND          |                     | VDD_ADC            | V      |

|                                     |                                                       | AGND          |                     | VDD_ADC<br>VDD_ADC | V      |

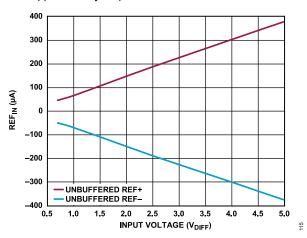

| Average DEEIN Current               | Reference precharge buffer on Reference unbuffered    | AGIND         | ±00                 | ADD_ADC            |        |

| Average REFIN Current               |                                                       |               | ±80                 |                    | uA/V   |

|                                     | Reference buffer on                                   |               | ±300                |                    | nA     |

|                                     | Reference precharge buffer on                         |               | ±20                 |                    | uA     |

| Average REFIN Current Drift         | Reference unbuffered                                  |               | ±1.7                |                    | nA/V/C |

|                                     | Reference buffer on                                   |               | 125                 |                    | nA/C   |

|                                     | Reference precharge buffer on                         |               | 4                   |                    | nA/C   |

| Common Mode Rejection               | Up to 10 MHz                                          |               | 100                 |                    | dB     |

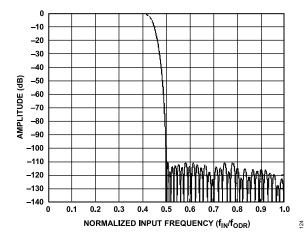

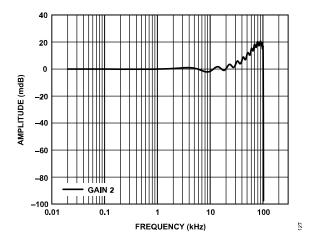

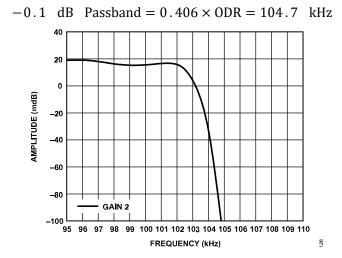

| DIGITAL FILTER RESPONSE             |                                                       |               |                     |                    |        |

| Wideband Low Ripple FIR Filter      |                                                       |               |                     |                    |        |

| Decimation Rate                     | 6 selectable decimation rates                         | 32            |                     | 1024               |        |

| Output Data Rate                    |                                                       |               |                     | 256                | kSPS   |

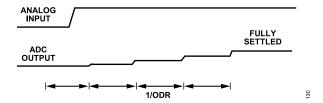

| Group Delay                         | Latency                                               |               | 34/ODR              |                    | Sec    |

| Settling Time                       | Complete settling                                     |               | 68/ODR              |                    | Sec    |

| Pass-Band Ripple                    |                                                       |               |                     | ±0.005             | dB     |

| Pass-Band                           | -0.005 dB                                             |               | 0.4 × ODR           |                    | Hz     |

|                                     | −0.1 dB pass-band                                     |               | 0.409 × ODR         |                    |        |

|                                     | -3 dB bandwidth                                       |               | 0.433 × ODR         |                    | Hz     |

| Stop-Band Frequency                 | Attenuation > 105 dB                                  |               | 0.499 × ODR         |                    | Hz     |

| Stop-Band Attenuation               |                                                       | 105           | +=                  |                    | dB     |

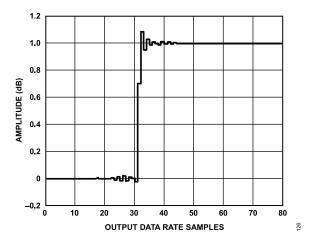

| Sinc5 Filter                        |                                                       |               |                     |                    |        |

| Decimation Rate                     | 8 selectable decimation rates                         | 8             |                     | 1024               |        |

| Output Data Rate                    | 5 Solodiable declination rates                        |               |                     | 1.024              | MSPS   |

| Group Delay                         | Latency                                               |               | < 3/ODR             | 1.021              | Sec    |

| •                                   | Complete settling                                     |               | < 6/ODR             |                    | Sec    |

| Settling Time Pass Band             | -0.1dB bandwidth                                      |               | < 6/ODR<br>0.0376 × |                    |        |

| Pass Dallu                          |                                                       |               | ODR                 |                    | Hz<br> |

| 0: 0.5"                             | −3dB bandwidth                                        |               | 0.204 × ODR         |                    | Hz     |

| Sinc3 Filter                        |                                                       |               |                     |                    |        |

| Decimation Rate                     | 1024 decimation rates                                 | 32            |                     | 185,280            |        |

| Output Data Rate                    |                                                       |               |                     | 256                | kSPS   |

| Group Delay                         | Latency                                               |               | 2/ODR               |                    | Sec    |

analog.com Rev. 0 | 10 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                                 | Test Conditions/Comments                                                             | Min           | Тур             | Max            | Unit    |

|-------------------------------------------|--------------------------------------------------------------------------------------|---------------|-----------------|----------------|---------|

| Settling Time                             | Complete settling to reject 50 Hz                                                    |               | 60              |                | ms      |

| Pass-Band                                 | −0.1dB bandwidth                                                                     |               | 0.0483 ×<br>ODR |                | Hz      |

|                                           | -3dB bandwidth                                                                       |               | 0.2617 ×<br>ODR |                | Hz      |

| CLOCK                                     |                                                                                      |               |                 |                |         |

| External Clock MCLK                       |                                                                                      | 0.6           | 16.384          | 17             | MHz     |

| Internal Clock MCLK                       |                                                                                      |               | 16.384          |                | MHz     |

| Input High Voltage                        | See logic input parameter.                                                           |               |                 |                |         |

| Duty Cycle                                | 16.384 MHz MCLK                                                                      | 25:75         | 50:50           | 25:75          | %       |

| MCLK Logic Low Pulse Width                |                                                                                      | 16            |                 |                | ns      |

| MCLK Logic High Pulse Width               |                                                                                      | 16            |                 |                | ns      |

| Crystal Frequency                         |                                                                                      | 8             | 16              | 17             | MHz     |

| Crystal Start-Up Time                     | Clock output valid                                                                   |               | 2               |                | ms      |

| ADC RESET                                 | ·                                                                                    |               |                 |                |         |

| ADC Start-Up Time after Reset             | Reset rising edge to first DRDY, PIN mode, decimate by 8                             |               | 100             |                | μs      |

| Minimum RESET Low Pulse Width             |                                                                                      | 0.0001        |                 | 100            | ms      |

| LOGIC INPUTS                              | Applies to all logic inputs, unless specified otherwise, voltage referenced to AGND. |               |                 |                |         |

| Input High Voltage, V <sub>INH</sub>      | 1.7 V ≤ VDD_IO ≤ 1.9 V                                                               | 0.65 × VDD IO |                 |                | V       |

|                                           | 2.22 V ≤ VDD_IO ≤ 3.6 V                                                              | 0.65 × VDD IO |                 |                | V       |

| Input Low Voltage, V <sub>INL</sub>       | 1.7 V ≤ VDD_IO ≤ 1.9 V                                                               | 0.00 1220     |                 | 0.35 × VDD 10  | V       |

| input 2011 Voltago, VINL                  | 2.22 V ≤ VDD_IO ≤ 3.6 V                                                              |               |                 | 0.7            | V       |

| Hysteresis                                | 2.22 V ≤ VDD_IO ≤ 3.6 V                                                              | 0.08          |                 | 0.25           | V       |

| Trybiologic                               | 1.7 V ≤ VDD IO < 1.9 V                                                               | 0.04          |                 | 0.2            | V       |

| Leakage Current                           | Excluding RESET pin                                                                  | -10           | +0.05           | +10            | μA      |

| Loukage Garrent                           | RESET pin pullup resistor                                                            | 10            | 1               | . 10           | kΩ      |

| GAIN0, GAIN1, GAIN2                       | Voltage referenced to AGND                                                           |               | '               |                | 1/22    |

| Input High Voltage                        | voltage folereneed to ACMB                                                           | 1.5           |                 |                | V       |

| Input Low Voltage                         |                                                                                      | 1.0           |                 | 0.6            | V       |

| Input Current                             | GAIN 0, GAIN 1, GAIN 2 = 5 V                                                         |               | 8               | 12             | μA      |

| EN_LDO                                    | Voltage referenced to AGND                                                           |               | U               | 12             | μΛ      |

| Input High Voltage                        | 5.1 V ≤ IN LDO ≤ 5.5 V                                                               | 1.2           |                 |                | V       |

| Input Low Voltage                         | 5.1 V ≤ IN LDO ≤ 5.5 V                                                               | 1.2           |                 | 0.4            | V       |

| Input Current                             | EN_LDO = IN_LDO or GND                                                               |               | 0.1             | 0.4            | μA      |

| LOGIC OUTPUTS                             | LIV_LDO = IIV_LDO 01 GIVD                                                            |               | 0.1             |                | μΛ      |

| Output High Voltage                       | 2.2 V ≤ VDD_IO < 3.6 V, I <sub>SOURCE</sub> = 500 µA, LV_BOOST_off                   | 0.8 × VDD_IO  |                 |                | V       |

|                                           | 1.7 V ≤ VDD_IO < 1.9 V, I <sub>SOURCE</sub> = 200 μA,<br>LV_BOOST_on                 | 0.8 × VDD_IO  |                 |                | V       |

| Output Low Voltage                        | 2.2 V ≤ VDD_IO < 3.6 V, I <sub>SINK</sub> = 1 mA,<br>LV_BOOST_off                    |               |                 | 0.4            | V       |

|                                           | 1.7 V ≤ VDD_IO < 1.9 V, I <sub>SINK</sub> = 400 μA,<br>LV_BOOST_on                   |               |                 | 0.4            | V       |

| Leakage Current                           | Floating state                                                                       | -10           |                 | +10            | μA      |

| Output Capacitance                        | Floating state                                                                       | '-            | 10              | · <del>-</del> | pF      |

| LDO CHARACTERISTIC                        |                                                                                      |               | · <del>·</del>  |                | I.      |

|                                           |                                                                                      | 5.1           |                 | 5.5            | V       |

|                                           | OUT I DO load current = 20 mΔ                                                        |               | 80              | 0.0            |         |

| Input Voltage Range IN_LDO Supply Current | OUT_LDO load current = 20 mA                                                         | 5.1           | 80              | 5.5            | V<br>µA |

analog.com Rev. 0 | 11 of 98

# **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                    | Test Conditions/Comments                                              | Min  | Тур       | Max          | Unit |

|------------------------------|-----------------------------------------------------------------------|------|-----------|--------------|------|

| OUT_LDO Voltage              |                                                                       | 4.80 | 4.90      | 5.03         | V    |

| Load Regulation              | I <sub>OUT</sub> = 1 mA to 20 mA                                      |      | 0.0005    |              | %/mA |

| Dropout Voltage <sup>6</sup> | I <sub>OUT</sub> = 20 mA                                              |      | 3         |              | mV   |

| Start-Up Time <sup>7</sup>   |                                                                       |      | 350       |              | μs   |

| Current Limit Threshold      |                                                                       |      | 500       |              | mA   |

| Thermal Shutdown Threshold   |                                                                       |      | 150       |              | °C   |

| Thermal Shutdown Hysteresis  |                                                                       |      | 15        |              | °C   |

| POWER REQUIREMENTS           |                                                                       |      |           |              |      |

| VDD_PGA                      | Referenced to AGND                                                    | 4.5  |           | 16           | V    |

| VSS_PGA                      | Referenced to AGND                                                    | -16  |           | <b>-</b> 4.5 | V    |

| VDD2_PGA                     | Referenced to AGND                                                    | 4.75 |           | 5.5          | V    |

| VDD_FDA                      | Referenced to AGND                                                    | 4.75 | 5         | 5.5          | V    |

| VDD_ADC                      | Referenced to AGND                                                    | 4.75 | 5         | 5.5          | V    |

| VDD2_ADC                     | Referenced to AGND                                                    | 2    | 2.5       | 5.5          | V    |

| _                            | Referenced to AGND                                                    | 1.7  | 1.8       | 3.6          | V    |

| VDD_IO                       | · · · · · · · · · · · · · · · · · · ·                                 | 1.7  | 1.0       | 3.0          | V    |

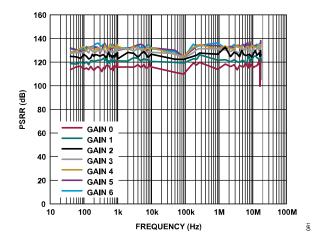

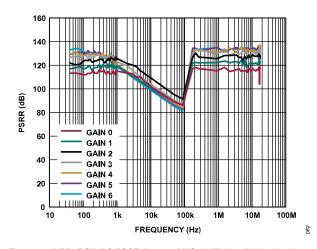

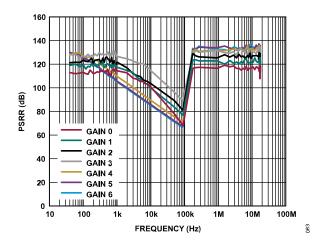

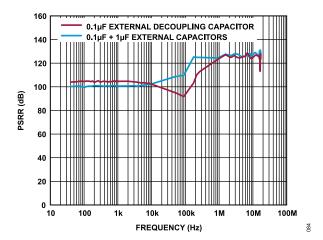

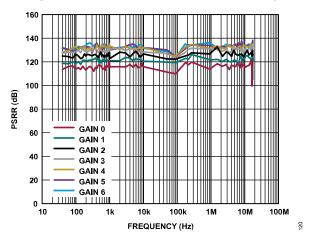

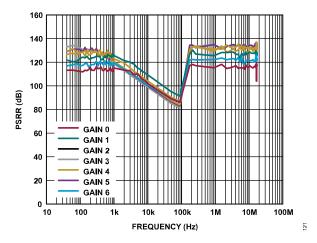

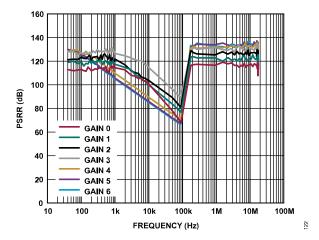

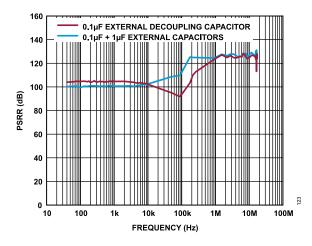

| POWER SUPPLY REJECTION       | Referred to output (RTO), DC to 100 Hz, V <sub>STEP</sub> = 0.4 V p-p |      |           |              |      |

| VDD_PGA and VSS_PGA          | Gain 0 mode                                                           |      | 112       |              | dB   |

|                              | Gain 6 mode                                                           |      | 130       |              | dB   |

| VDD2_PGA                     |                                                                       |      | 124       |              | dB   |

| VDD_FDA                      |                                                                       |      | 116       |              | dB   |

| VDD_ADC                      |                                                                       |      | 105       |              | dB   |

| VDD2_ADC                     |                                                                       |      | 124       |              | dB   |

| VDD_IO                       |                                                                       |      | 104       |              | dB   |

| LDO                          |                                                                       |      | 124       |              | dB   |

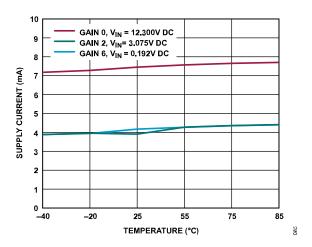

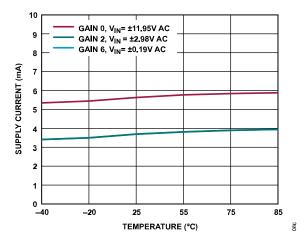

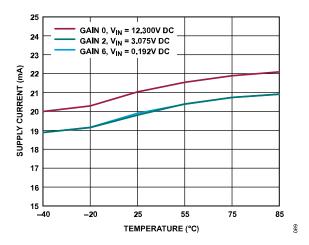

| POWER SUPPLY CURRENT         |                                                                       |      |           |              |      |

| VDD_PGA                      | IN+ = IN- = AGND                                                      |      | 3.1       |              | mA   |

|                              | Full-scale 1 kHz sine input with common mode = AGND, Gain 0 mode      |      | 6.5       |              | mA   |

|                              | Full-scale 1 kHz sine input with common mode = AGND, Gain 6 mode      |      | 3.4       |              | mA   |

|                              | Full-scale DC input with common mode = AGND, Gain 0 mode              | :    | 7.6       |              | mA   |

|                              | Full-scale DC input with common mode = AGND, Gain 6 mode              | :    | 4.1       |              | mA   |

|                              | Standby                                                               |      | 230       |              | μA   |

| VDD2_PGA                     | IN+ = IN- = AGND                                                      |      | 0.75      |              | mA   |

| VDD2_1 G/K                   | Full-scale 1 kHz sine input with common mode = AGND, Gain 0 mode      |      | 2.4       |              | mA   |

|                              | Full-scale 1 kHz sine input with common mode = AGND, Gain 6 mode      |      | 1.1       |              | mA   |

|                              | Full-scale DC input with common mode = AGND, Gain 0 mode              | :    | 3.3       |              | mA   |

|                              | Full-scale DC input with common mode = AGND, Gain 6 mode              | :    | 2         |              | mA   |

|                              | Standby                                                               |      | 1         |              | Ι.Δ  |

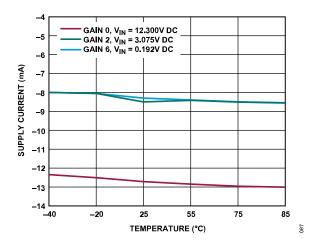

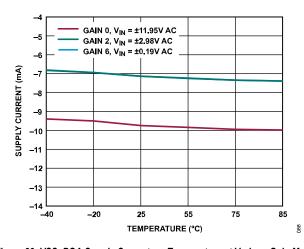

| VSS DCA                      | IN+ = IN- = AGND                                                      |      | ı<br>−5.9 |              | μA   |

| VSS_PGA                      |                                                                       |      |           |              | mA   |

|                              | Full-scale 1 kHz sine input with common mode = AGND, Gain 0 mode      |      | -10.3     |              | mA   |

analog.com Rev. 0 | 12 of 98

## **SPECIFICATIONS**

Table 1. (Continued)

| Parameter                      | Test Conditions/Comments                                         | Min | Тур  | Max | Unit |

|--------------------------------|------------------------------------------------------------------|-----|------|-----|------|

|                                | Full-scale 1 kHz sine input with common                          |     | -6.4 |     | mA   |

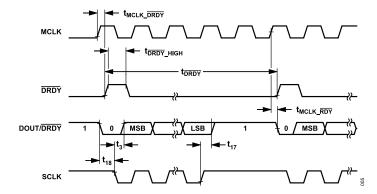

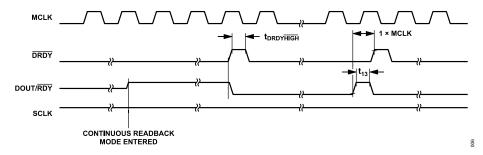

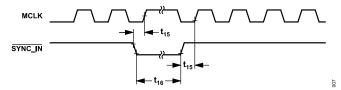

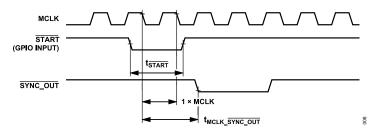

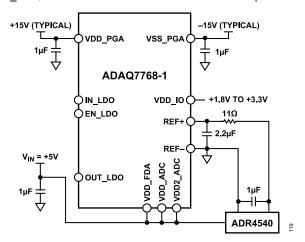

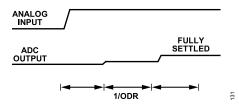

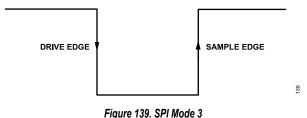

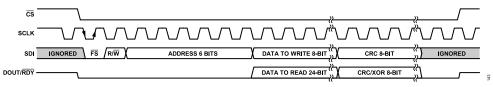

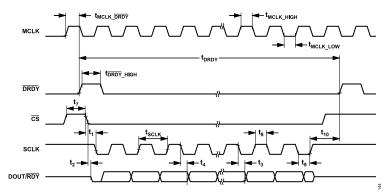

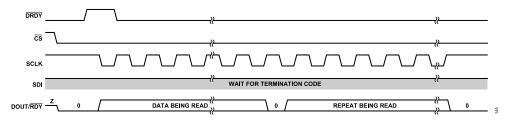

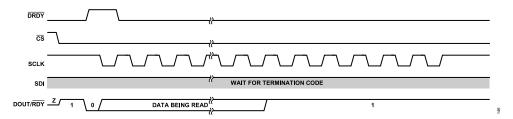

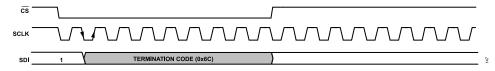

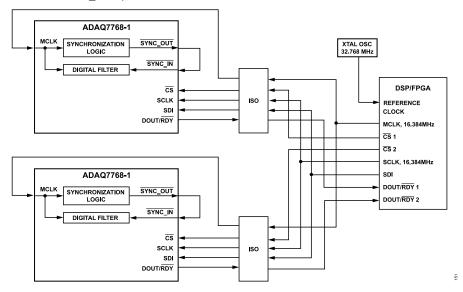

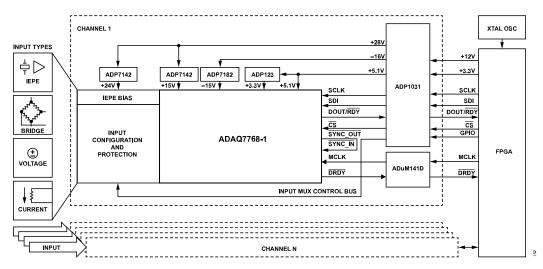

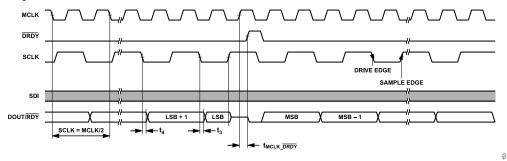

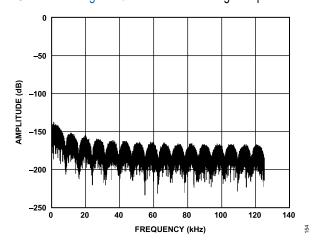

|                                | mode = AGND, Gain 6 mode                                         |     |      |     |      |