# EV-VN7040AJ

## VN7040AJ evaluation board

Data brief

## Features

| Max transient supply voltage      | V <sub>CC</sub>   | 40 V      |

|-----------------------------------|-------------------|-----------|

| Operating voltage range           | Vcc               | 4 to 28 V |

| Typ. on-state resistance (per Ch) | R <sub>ON</sub>   | 40 mΩ     |

| Current limitation (typ)          | ILIMH             | 34 A      |

| Stand-by current (max)            | I <sub>STBY</sub> | 0.5 µA    |

- Simple single IC application board dedicated for VN7040AJ-E

- Provides electrical connectivity and thermal heat-sinking for easy prototyping

- General device features

- Single channel smart high-side driver with MultiSense analog feedback

- Very low standby current

- Compatible with 3 V and 5 V CMOS outputs

- MultiSense diagnostic functions

- Multiplexed analog feedback of: load current with high precision proportional

current mirror,  $V_{CC}$  supply voltage and  $T_{CHIP}$  device temperature

- Overload and short to ground (power limitation) indication

- Thermal shutdown indication

- OFF-state open-load detection

- $\qquad \text{Output short to } V_{\text{CC}} \text{ detection} \\$

- Sense enable/disable

- Protections

- Undervoltage shutdown

- Overvoltage clamp

- Load current limitation

- Self limiting of fast thermal transients

- Configurable latch-off on overtemperature or power limitation with dedicated fault reset pin

- $\,$  Loss of ground and loss of V\_{CC}

- Reverse battery with external components

- Electrostatic discharge protection

## Applications

Typical applications are all types of automotive resistive, inductive and capacitive loads.

#### Description

This board provides you an easy way to connect STMicroelectronics  $^{\ensuremath{\mathbb{R}}}$  VIPower  $^{\ensuremath{\mathbb{R}}}$  M0-7 technology into your existing system.

#### Table 1: Device summary

| Order code  | Reference                 |

|-------------|---------------------------|

| EV-VN7040AJ | VN7040AJ evaluation board |

### 1 Overview

The board comes pre-assembled with VN7040AJ-E high-side driver. On board minimum set of electrical components (as for device datasheet recommendation) is enabling the user to directly connect the load, the power supply and the microcontroller without any additional effort in external component design and connection.

The VN7040AJ-E is a single channel high-side driver manufactured using ST proprietary VIPower<sup>®</sup> technology and housed in PowerSSO-16 package. The device is designed to drive 12 V automotive grounded loads through a 3 V and 5 V CMOS-compatible interface, providing protection and diagnostics.

The device integrates advanced protective functions such as load current limitation, overload active management by power limitation and overtemperature shutdown with configurable latch-off.

A FaultRST pin unlatches the output in case of fault or disables the latch-off functionality.

A dedicated multifunction multiplexed analog output pin delivers sophisticated diagnostic functions including high precision proportional load current sense, supply voltage feedback and chip temperature sense, in addition to the detection of overload and short circuit to ground, short to  $V_{CC}$  and OFF-state open-load. A sense enable pin allows OFF-state diagnosis to be disabled during the module low-power mode as well as external sense resistor sharing among similar devices.

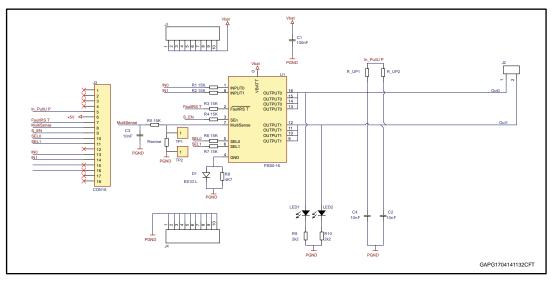

Figure 1: Evaluation board schematic

## 2 Board connections

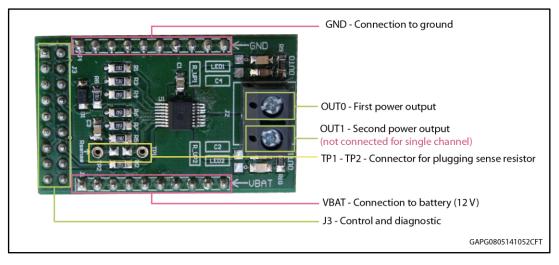

*Figure 2: "Evaluation board connections"* shows the placement of the connectors to be used for supplying the evaluation board, connecting the load and controlling the functionality and diagnostic of the device.

Figure 2: Evaluation board connections

| Connector | Pin<br>number | Pin name   | Pin function                                                                                                                                         |

|-----------|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| J3        | 14            | N/A        | Not connected                                                                                                                                        |

| J3        | 5             | IN_PullUP  | Connection to optional external pull-up resistor for open load detection in off-state.                                                               |

| J3        | 6             | +5V        | 5 V Power Supply                                                                                                                                     |

| J3        | 7             | FaultRST   | Active low compatible with 3 V and 5 V CMOS outputs pin; it unlatches the output in case of fault; If kept low, sets the outputs in auto-restart     |

| J3        | 8             | MultiSense | Multiplexed analog sense output pin; it delivers a current proportional to the selected diagnostic: load current, supply voltage or chip temperature |

| J3        | 9             | S_EN       | Active high compatible with 3 V and 5 V CMOS outputs pin; it enables the MultiSense diagnostic pin.                                                  |

| J3        | 10            | SEL0       | Active high compatible with 3 V and 5 V CMOS outputs pin; together with SEL1, it addresses the MultiSense multiplexer                                |

| J3        | 11            | SEL1       | Active high compatible with 3 V and 5 V CMOS outputs pin; together with SEL0, it addresses the MultiSense multiplexer                                |

| J3        | 12            | N/A        | Not connected                                                                                                                                        |

| J3        | 13            | IN0        | Voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. It controls OUT0 switch state                                |

| J3        | 14            | IN1        | Voltage controlled input pin with hysteresis, compatible with 3 V and 5 V CMOS outputs. It controls OUT1 switch state. $^{(1)}$                      |

EV-VN7040AJ

| Connector | Pin<br>number | Pin name | Pin function  |

|-----------|---------------|----------|---------------|

| J3        | 1518          | N/A      | Not connected |

#### Notes:

<sup>(1)</sup>Input not available for single channel.

In case the user wishes to utilize the Current Sense/MultiSense function of the device, it is necessary to plug a sense resistor in  $R_{SENSE}$ .

The package includes a through-hole resistor, to be mounted on TP1-TP2 (see *Figure 4: "Mounting through-hole sense resistor"*).

Different R<sub>SENSE</sub> values can be adopted based on user preference.

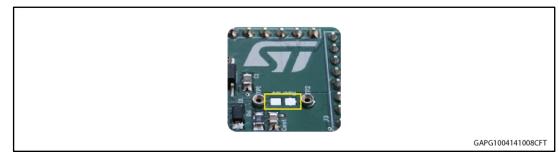

Another option is soldering an SMD resistor on the dedicated PCB pad, as shown in *Figure 5: "Pads for soldering SMD resistor"*.

Figure 3: No sense resistor

GAPG0904141657CFT

GAPG1004141007CFT

Figure 4: Mounting through-hole sense resistor

Figure 5: Pads for soldering SMD resistor

## 3 Thermal data

#### Table 3: Thermal data

| Symbol               | Parameter                                 | Max | Unit |

|----------------------|-------------------------------------------|-----|------|

| R <sub>thj-amb</sub> | Thermal resistance junction-ambient (MAX) | 39  | °C/W |

#### Table 4: PCB specifications

| P to                    | <b>W</b> ata    |

|-------------------------|-----------------|

| Parameter               | Value           |

| Board dimensions        | 25 mm x 41.5 mm |

| Number of Cu layer      | 2               |

| Layer Cu thickness      | 35 µm           |

| Board finish thickness  | 1.6 mm +/- 10%  |

| Board Material          | FR4             |

| Thermal vias separation | 1.1 mm          |

| Thermal vias diameter   | 0.5 mm          |

#### **Revision history** 4

Table 5: Revision history

| Date        | Revision | Changes                                        |

|-------------|----------|------------------------------------------------|

| 12-May-2014 | 1        | Initial release.                               |

| 21-Jul-2014 | 2        | Updated Figure 1: "Evaluation board schematic" |