# EV2149-J-00A

# 6V, Dual 1A Low Quiescent Current SYNC Buck Regulator

#### DESCRIPTION

The EV2149-J-00A is used for demonstrating the performance of MPS's MP2149, an internally compensated 1MHz fixed-frequency dual PWM synchronous step-down regulator.

MP2149 is ideal for powering portable equipment that runs from a single cell Lithium-Ion (Li+) Battery due to  $45\mu A$  low quiescent current. The output voltage can be regulated as low as 0.608V.

With peak current mode control and internal compensation, the MP2149 requires a minimum number of readily available standard external components and is available in an 8-pin TSOT23 package.

#### **ELECTRICAL SPECIFICATION**

| Parameter         | Symbol            | Value | Units |

|-------------------|-------------------|-------|-------|

| Input Voltage (1) | V <sub>IN</sub>   | 2.7-6 | ٧     |

| Output Valtage    | V <sub>OUT1</sub> | 1.8   | V     |

| Output Voltage    | V <sub>OUT2</sub> | 1.2   | V     |

| Output Current    | I <sub>OUT1</sub> | 1     | Α     |

| Output Current    | I <sub>OUT2</sub> | 1     | Α     |

#### Notes:

#### **FEATURES**

- Dual 1A Output Current

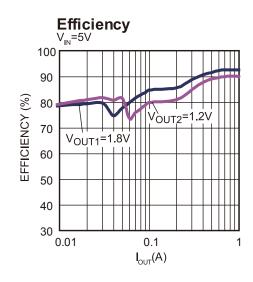

- >93% Peak Efficiency

- >80% Light Load Efficiency

- Wide 2.7V to 6V Operating Input Range

- 100mΩ and 40mΩ Internal Power MOSFET

- 1MHz Fixed Switching Frequency

- Adjustable Output from 0.608V to VIN

- 180° Phase-Shifted Operation

- 100% Duty Cycle Operation

- 45µA Quiescent Current

- Cycle-by-cycle Over Current Protection

- Short Circuit Protection with Hiccup Mode

- Thermal Shutdown

- Available in an 8-pin TSOT23 Package

#### **APPLICATIONS**

- Small/Handhold Devices

- DVD Drivers

- Portable Instruments

- Smartphone and Feature Phones

- Battery-Powered Devices

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

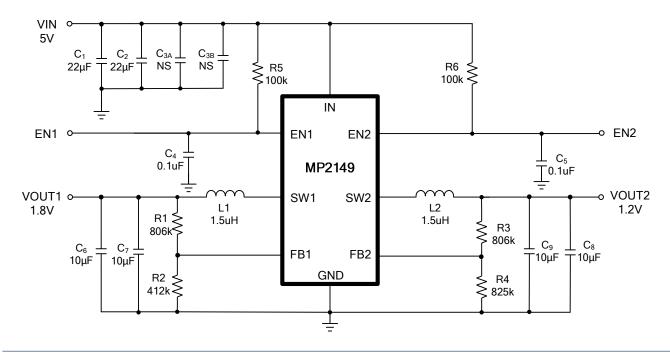

#### TYPICAL APPLICATION

| Board Number | MPS IC Number |  |  |

|--------------|---------------|--|--|

| EV2149-J-00A | MP2149GJ      |  |  |

<sup>1)</sup> V<sub>IN</sub> < 3V application may need more input capacitors.

## **EVALUATION BOARD SCHEMATIC**

#### **EV2149-J-00A BILL OF MATERIALS**

| Qty | Ref               | Value | Description                    | Package  | Manufacturer | Manufacturer P/N   |

|-----|-------------------|-------|--------------------------------|----------|--------------|--------------------|

| 1   | C1                | 22uF  | Ceramic Cap., 16V,<br>20%, X5R | 0805     | muRata       | GRM21BR60J226ME39L |

| 1   | C2                | 22uF  | Ceramic Cap., 16V,<br>20%, X5R | 0805     | muRata       | GRM21BR60J226ME39L |

| 0   | C3A               | NS    |                                |          |              |                    |

| 0   | C3B               | NS    |                                |          |              |                    |

| 2   | C4, C5            | 0.1uF | Ceramic Cap,<br>16V,X7R        | 0603     | muRata       | GRM188R71C104KA01D |

| 4   | C6, C7,<br>C8, C9 | 10uF  | Ceramic Cap,<br>16V, 20%, X5R  | 0805     | muRata       | GRM21BR61A106KE19L |

| 2   | R1, R3            | 806k  | Thick Film,<br>1/10W, 1%       | 0603     | royal        | RL0603FR-07806KL   |

| 1   | R2                | 412k  | Thick Film, 1/10W, 1%          | 0603     | royal        | RL0603FR-07412KL   |

| 1   | R4                | 825k  | Thick Film, 1/10W, 1%          | 0603     | royal        | RL0603FR-07825KL   |

| 2   | R5, R6            | 100k  | Thick Film, 1/10W, 1%          | 0603     | royal        | RL0603FR-07100KL   |

| 2   | L1, L2            | 1.5uH | Inductor, 9.57mohm,<br>11.5A   |          | Wurth        | 744312150          |

| 1   | U1                |       | DC-DC module                   | TSOT23-8 | MPS          | MP2149GJ           |

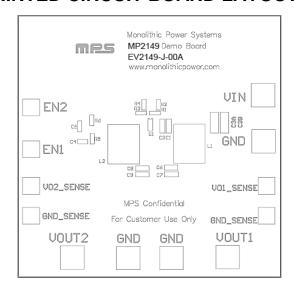

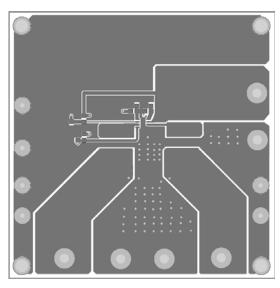

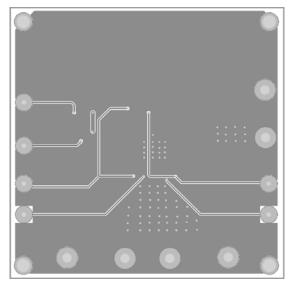

## PRINTED CIRCUIT BOARD LAYOUT

Figure 1—Top Silk Layer

Figure 2—Top Layer

Figure 3—Bottom Layer