# 24-Bit, 4-Channel Simultaneous Sampling 1.5 MSPS Precision Alias Free ADC

Data Sheet AD7134

#### **FEATURES**

Alias free: inherent antialias rejection high performance mode 102.5 dB, typical

**Excellent ac and dc performance**

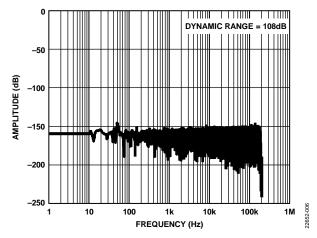

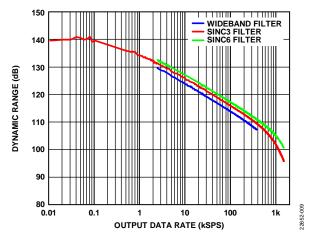

108 dB dynamic range at ODR = 374 kSPS, FIR filter, typical 137 dB dynamic range at ODR = 10 SPS, sinc3 filter, typical

THD: -120 dB typical with 1 kHz input tone

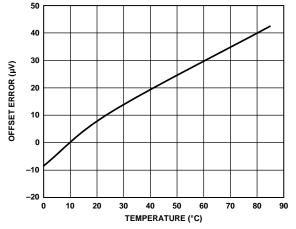

Offset error drift: 0.7  $\mu$ V/°C typical

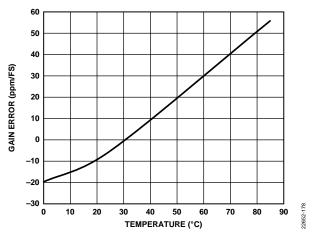

Gain drift: 2 ppm/°C typical INL: ±2 ppm of FSR typical

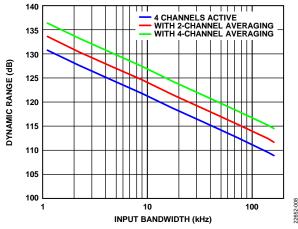

Dynamic range enhancement: 4:1 and 2:1 averaging mode

126 dB, A weighted dynamic range Resistive ADC and reference input

Easy to sync: asynchronous sample rate converter

Multidevice synchronization with one signal line

Programmable data rates from 0.01 kSPS to 1496 kSPS

with resolution of 0.01 SPS

Option to control output data rate by external signal

Linear phase digital filter options

Low ripple FIR filter: 32  $\mu dB$  pass-band ripple, dc to

161.942 kHz

Low latency sinc3 filter and sinc6 filter, dc to 391.5 kHz

Sinc3 filter with 50 Hz/60 Hz rejection

Crosstalk: 130.7 dBFS

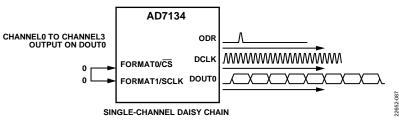

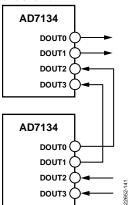

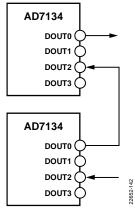

**Daisy-chaining**

CRC error checking on data and SPI interface

Two power modes: high performance mode and low power

mode

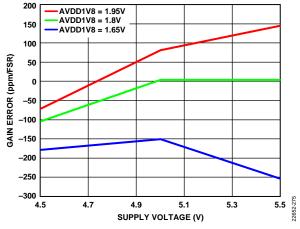

Power supply: 4.5 V to 5.5 V and 1.65 V to 1.95 V

1.8 V IOVDD level

External reference: 4.096 V or 5 V

Crystal or external CMOS clock of 48 MHz

SPI or pin (standalone) configurable operation

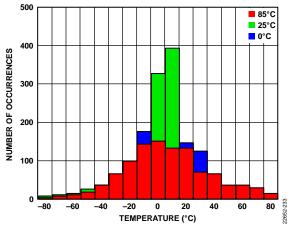

Operating temperature range: 0°C to 85°C

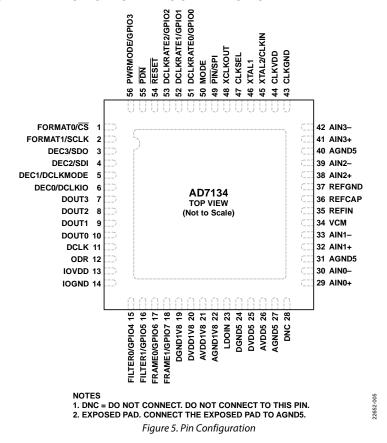

Available in 8 mm × 8 mm, 56-lead LFCSP with exposed pad

#### **APPLICATIONS**

**Electrical test and measurement**

**Audio test**

3-phase power quality analysis

Control and hardware in loop verification

**Sonars**

Condition monitoring for predictive maintenance

Acoustic and material science research and development

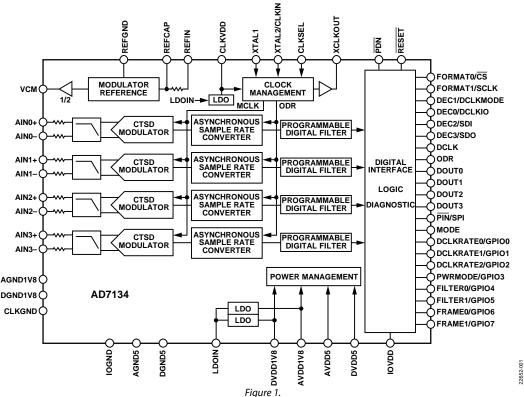

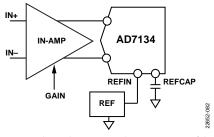

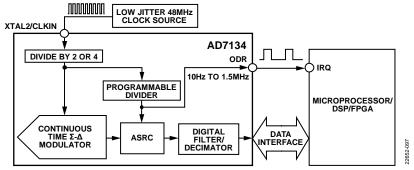

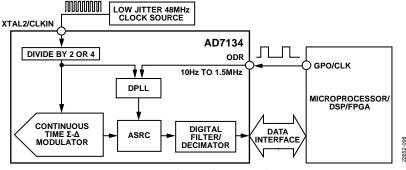

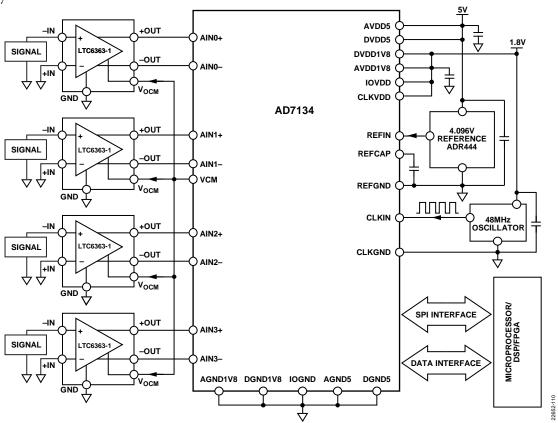

#### **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                    | ]  |

|---------------------------------------------|----|

| Applications                                | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| General Description                         | 3  |

| Specifications                              | 4  |

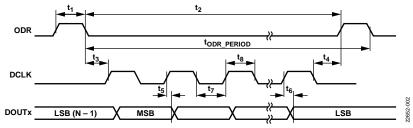

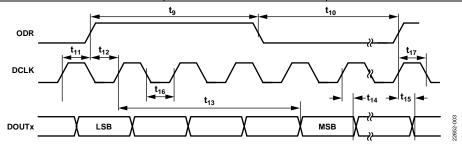

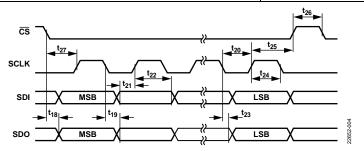

| Timing Specifications                       | 10 |

| Absolute Maximum Ratings                    | 12 |

| Thermal Resistance                          | 12 |

| ESD Caution                                 | 12 |

| Pin Configuration and Function Descriptions | 13 |

| Typical Performance Characteristics         | 17 |

| Terminology                                 | 26 |

| Theory of Operation                         | 28 |

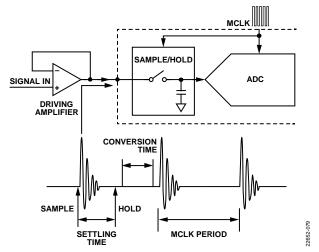

| Continuous Time Sigma-Delta Modulator       | 28 |

| Easy to Drive Input and Reference           | 28 |

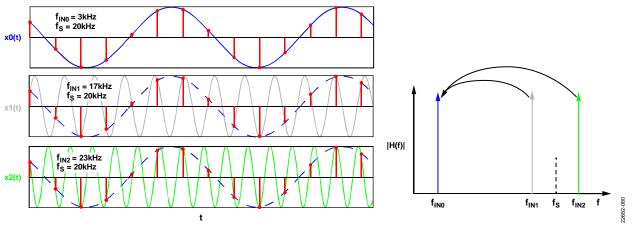

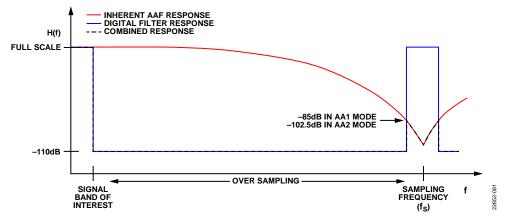

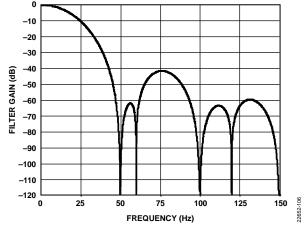

| Inherent Antialiasing Filter (AAF)          | 29 |

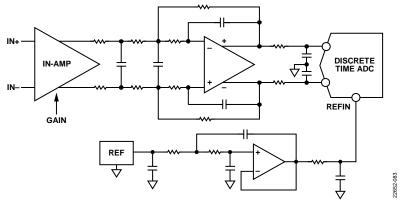

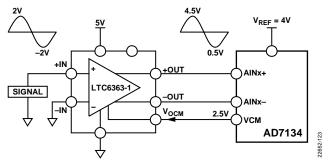

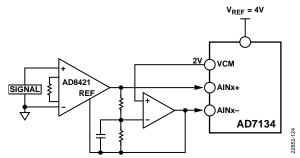

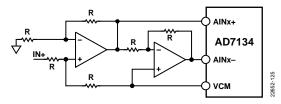

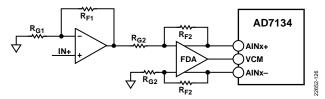

| Analog Front-End Design Simplification      | 30 |

| Noise Performance and Resolution            | 31 |

| Circuit Information                         | 35 |

| Core Signal Chain                           | 35 |

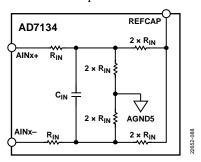

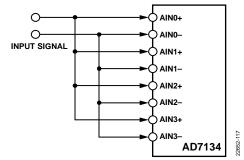

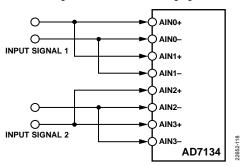

| Analog Inputs                               | 35 |

| VCM Output                                  | 35 |

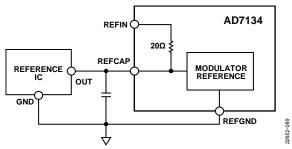

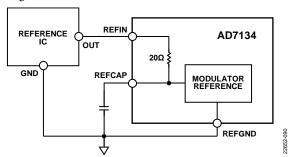

| Reference Input                             | 36 |

| Clock Input                                 | 36 |

| XCLKOUT Output                              | 36 |

| Power Options                               | 37 |

| Reset                                       | 37 |

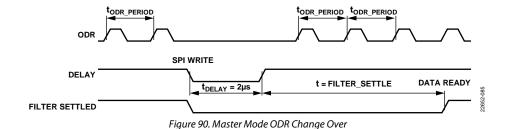

| Asynchronous Sample Rate Converter          | 37 |

| Digital Filters                             | 39 |

| Quick Start Guide                           | 42 |

| Standalone Mode                             | 43 |

| Low Latency Synchronous Data Acquisition    | 43 |

| Device Control                              | 44 |

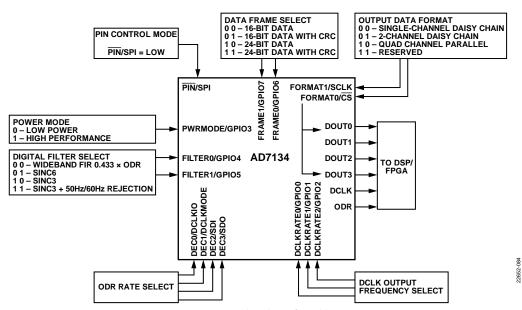

| Pin Control Mode                            | 44 |

| SPI Control Mode                            | 45 |

| Multifunction Pins                          | 45 |

| Device Configuration                        | 46 |

|                                             |    |

| Programming Output Data Rate and Clock46        |

|-------------------------------------------------|

| Programming Digital Filter                      |

| Programming Data Interface                      |

| Power Modes                                     |

| Inherent Antialiasing Filter Modes51            |

| Dynamic Range Enhancement, Channel Averaging 52 |

| Calibration53                                   |

| Offset Calibration53                            |

| Gain Calibration53                              |

| Applications Information54                      |

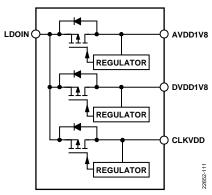

| Power Supply54                                  |

| Reference Noise Filtering                       |

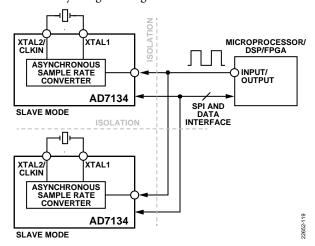

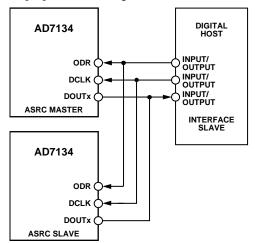

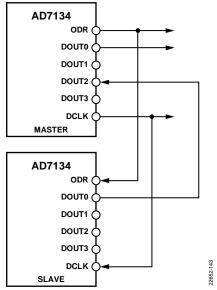

| Multidevice Synchronization55                   |

| Coherent Sampling                               |

| Low Latency Digital Control Loop55              |

| Automatic Gain Control                          |

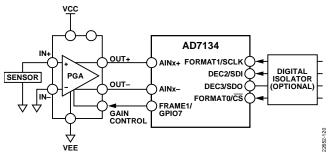

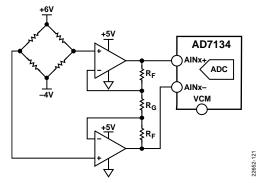

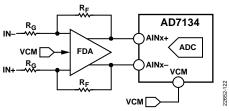

| Front-End Design Examples56                     |

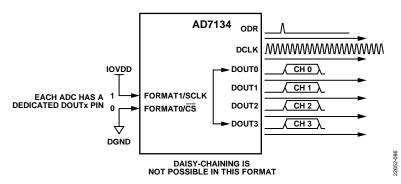

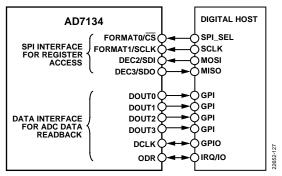

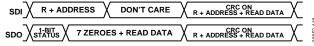

| Digital Interface                               |

| SPI Interface                                   |

| Data Interface59                                |

| Minimum I/O Mode64                              |

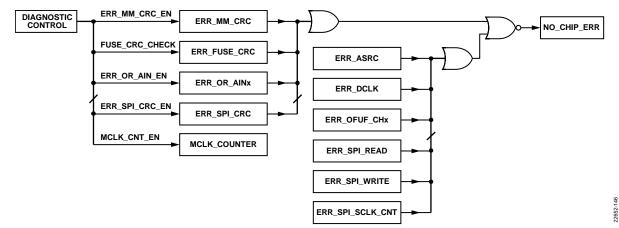

| Diagnostics                                     |

| Internal Fuse Integrity Check                   |

| Analog Input Overrange66                        |

| MCLK Counter                                    |

| SPI Interface Monitoring66                      |

| Memory Map Integrity Check66                    |

| ODR Input Frequency Check66                     |

| Digital Filter Overflow and Underflow67         |

| DCLK Error67                                    |

| GPIO Functionality                              |

| Pin Error Reporting                             |

| Register Map (SPI Control)69                    |

| Register Details71                              |

| Outline Dimensions                              |

| Ordering Guide86                                |

#### **REVISION HISTORY**

# **GENERAL DESCRIPTION**

The AD7134 is a quad channel, low noise, simultaneous sampling, precision analog-to-digital converter (ADC) that delivers on functionality, performance, and ease of use.

Based on the continuous time sigma-delta (CTSD) modulation scheme, the AD7134 removes the traditionally required switched capacitor circuitry sampling preceding the  $\Sigma\text{-}\Delta$  modulator, which leads to a relaxation of the ADC input driving requirement. The CTSD architecture also inherently rejects signals around the ADC aliasing frequency band, giving the device its inherent antialiasing capability, and removes the need for a complex external antialiasing filter.

The AD7134 has four independent converter channels in parallel, each with a CTSD modulator and a digital decimation and filtering path. The AD7134 enables simultaneous sampling of four separate signal sources, each supporting a maximum input bandwidth of 391.5 kHz and achieving tight phase matching between these four signal measurements. The high level of channel integration, together with its simplified analog frontend requirement, enables the AD7134 to provide a high density multichannel data acquisition solution in a small form factor.

The signal chain simplification property of the AD7134 also improves the system level performance through the reduction of noise, error, mismatch, and distortion that is normally introduced by the analog front-end circuitry.

The AD7134 offers excellent dc and ac performance. The bandwidth of each ADC channel ranges from dc to 391.5 kHz, making the device an ideal candidate for universal precision data acquisition solutions supporting a breadth of sensor types, from temperature and pressure to vibration and shock.

The AD7134 offers a large number of features and configuration options, giving the user the flexibility to achieve the optimal balance between bandwidth, noise, accuracy, and power for a given application.

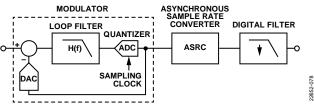

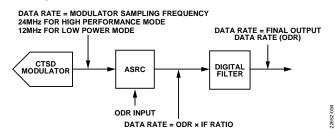

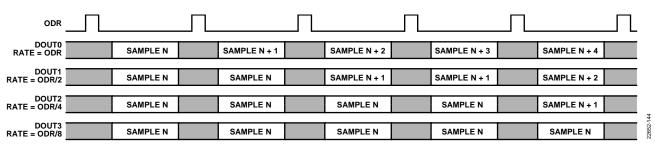

An integrated asynchronous sample rate converter (ASRC) allows the AD7134 to precisely control the decimation ratio and, in turn, the output data rate (ODR) using interpolation and resampling techniques. The AD7134 supports a wide range of ODR frequencies, from 0.01 kSPS to 1496 kSPS with less than 0.01 SPS adjustment resolution, allowing the user to granularly vary sampling speed to achieve coherent sampling. The ODR value can be controlled through the ODR\_VAL\_INT\_x and ODR\_VAL\_FLT\_x registers (Register 0x16 to Register 0x1C, ASRC master mode), or using an external clock source (ASRC slave mode). The ASRC slave mode operation enables synchronous sampling between multiple AD7134 devices to a single system clock. The ASRC simplifies the clock distribution requirement within a medium bandwidth data acquisition system because it

no longer requires a high frequency, low jitter master clock from the digital back end to be routed to each ADC.

The ASRC acts as a digital filter and decimates the oversampled data from the  $\Sigma$ - $\Delta$  modulator to a lower rate to favor higher precision. The ADC data is then further processed by one of the AD7134 user-selectable digital filter profiles to further reject the out of band signals and noises, and reduce the data rate to the final desired ODR value.

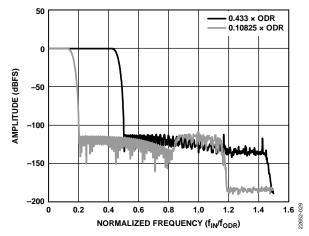

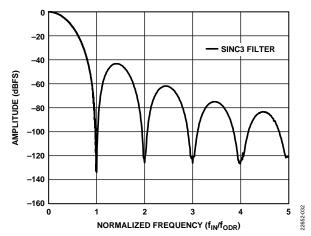

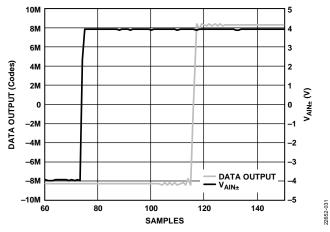

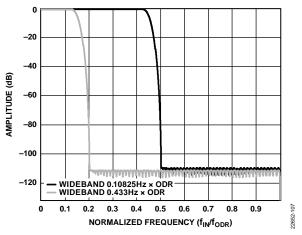

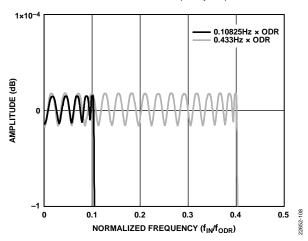

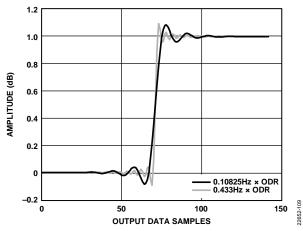

The AD7134 offers three main digital filter profile options: a wideband low ripple filter with a brick wall frequency profile and an ODR range from 2.5 kSPS to 374 kSPS that is suitable for frequency domain analysis, a fast responding sinc3 filter with an ODR range from 0.01 kSPS to 1496 kSPS that is suitable for low latency time domain analysis and low frequency high dynamic range input types, and a balanced sinc6 filter with an ODR range from 2.5 kSPS to 1.496 MSPS, offering optimal noise performance and response time.

The AD7134 is also capable of performing on-board averaging between two or four of its input channels. The result is a near 3 dB, if two channels are combined, or 6 dB, if all four channels are combined, improvement in dynamic range while maintaining the bandwidth.

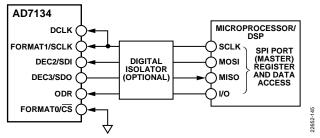

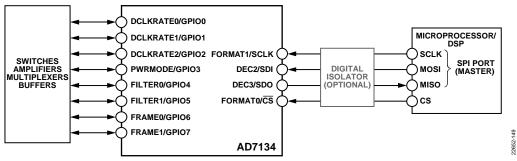

The AD7134 supports two device configuration schemes: serial peripheral interface (SPI) and hardware pin configuration (pin control mode). The SPI control mode offers access to all the features and configuration options available on the AD7134. SPI control mode also enables access to the on-board diagnostic features designed to enable a robust system design. Pin control mode offers the benefit of simplifying the device configuration, enabling the device to operate autonomously after power-up operating in a standalone mode.

In addition to the optional SPI, the AD7134 has a flexible and independent data interface for transmitting the ADC output data. The data interface can act as either a bus master or a slave with various clocking options to support multiple communication bus protocols. The data interface also supports daisy-chaining and an optional minimum input/output (I/O) mode designed to minimize the number of digital isolator channels required in isolated applications.

The AD7134 has an operating ambient temperature range from 0°C to 85°C. The device is housed in an 8 mm  $\times$  8 mm, 56-lead lead frame chip scale package (LFCSP).

Note that throughout this data sheet, multifunction pins, such as FORMAT1/SCLK, are referred to either by the entire pin name or by a single function of the pin, for example, SCLK, when only that function is relevant.

# **SPECIFICATIONS**

$AVDD5 = DVDD5 = 4.5 \text{ V to } 5.5 \text{ V, } AVDD1V8 = DVDD1V8 = 1.65 \text{ V to } 1.95 \text{ V, } CLKVDD = 1.65 \text{ V to } 1.95 \text{ V, } LDOIN = 2.6 \text{ V to } 5.5 \text{ V, } IOVDD = 1.65 \text{ V to } 1.95 \text{ V, } CLKIN = 48 \text{ MHz, } AGND5 = DGND5 = AGND1V8 = DGND1V8 = IOGND = CLKGND = 0 \text{ V, } REFIN \text{ voltage } (V_{REF}) = 4.096 \text{ V, high performance mode, input common-mode voltage } (V_{CM}) = 2.048 \text{ V, wideband } 0.433 \text{ Hz} \times ODR \text{ filter, } Antialiasing 1 (AA1) \text{ mode, unless otherwise noted.} Typical values are for $T_A = 25^{\circ}$C, $AVDD5 = DVDD5 = 5 \text{ V, } AVDD1V8 = DVDD1V8 = CLKVDD = 1.8 \text{ V, } LDOIN = 5 \text{ V, } IOVDD = 1.8 \text{ V, } unless \text{ otherwise noted.}$

Table 1.

| Parameter                                                       | Test Conditions/Comments                                                         | Min   | Тур                | Max       | Unit |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------|-------|--------------------|-----------|------|

| ADC SPEED AND DATA OUTPUT                                       |                                                                                  |       |                    |           |      |

| ODR                                                             |                                                                                  |       |                    |           |      |

| Wideband 0.10825 Hz ×<br>ODR and 0.433 Hz ×<br>ODR Filters 1, 2 |                                                                                  | 2.5   |                    | 374       | kSPS |

| Sinc6 Filter <sup>3</sup>                                       |                                                                                  | 2.5   |                    | 1496      | kSPS |

| Sinc3 Filter <sup>4</sup>                                       |                                                                                  | 0.01  |                    | 1496      | kSPS |

| –3 dB Bandwidth                                                 |                                                                                  |       |                    |           |      |

| Wideband 0.433 Hz $\times$ ODR Filter                           |                                                                                  | 1.08  |                    | 161.942   | kHz  |

| Wideband 0.10825 Hz<br>× ODR Filter                             |                                                                                  | 0.27  |                    | 40.48     | kHz  |

| Sinc6 Filter                                                    |                                                                                  | 0.47  |                    | 278.4     | kHz  |

| Sinc3 Filter                                                    |                                                                                  | 0.003 |                    | 391.5     | kHz  |

| Data Output Coding                                              |                                                                                  |       | Twos complement, I | MSB first |      |

| DYNAMIC PERFORMANCE                                             | More information is available in the Noise<br>Performance and Resolution section |       |                    |           |      |

| Dynamic Range (DR)                                              | Shorted input                                                                    |       |                    |           |      |

| High Performance                                                | ODR = 374 kSPS                                                                   | 105.7 | 108                |           | dB   |

| Mode                                                            | ODR = 10 SPS, sinc3 filter                                                       |       | 137                |           | dB   |

|                                                                 | A weighted, 1 kHz input, –60 dBFS, ODR = 48 kSPS                                 |       | 120                |           | dB   |

|                                                                 | 2:1 channel averaging, A weighted, 1 kHz input,<br>-60 dBFS, ODR = 48 kSPS       |       | 123                |           | dB   |

|                                                                 | 4:1 channel averaging, A weighted, 1 kHz input,<br>–60 dBFS, ODR = 48 kSPS       |       | 126                |           | dB   |

| Low Power Mode                                                  | ODR = 187 kSPS                                                                   | 102.7 | 106                |           | dB   |

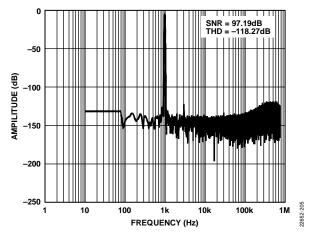

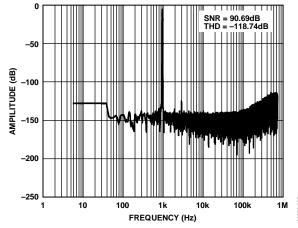

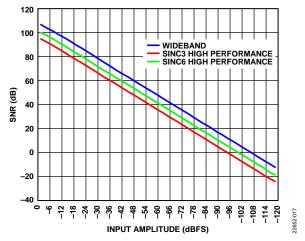

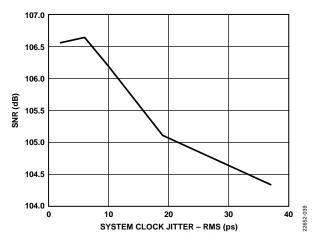

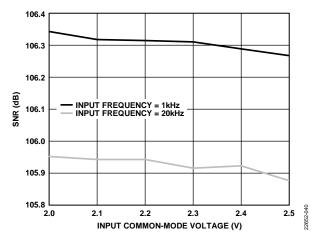

| Signal-to-Noise Ratio                                           | 1 kHz, –0.5 dBFS, sine wave input                                                |       |                    |           |      |

| High Performance Mode                                           | ODR = 374 kSPS                                                                   | 105.6 | 107                |           | dB   |

| Low Power Mode                                                  | ODR = 187 kSPS                                                                   | 105.3 | 106                |           | dB   |

| Signal-to-Noise-and-<br>Distortion Ratio (SINAD)                | 1 kHz, –0.5 dBFS, sine wave input                                                |       |                    |           |      |

| High Performance Mode                                           | ODR = 374 kSPS                                                                   |       | 106.5              |           | dB   |

| Low Power Mode                                                  | ODR = 187 kSPS                                                                   |       | 105.5              |           | dB   |

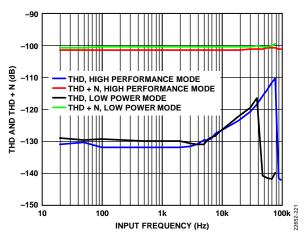

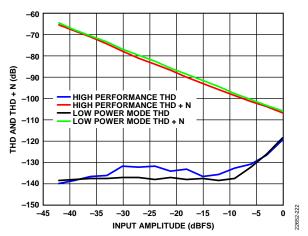

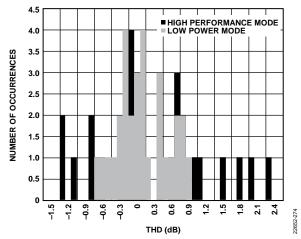

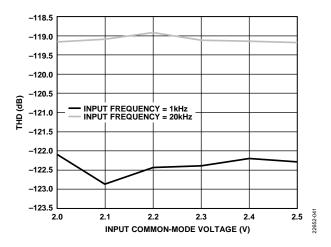

| Total Harmonic Distortion (THD)                                 | 1 kHz, –0.5 dBFS, sine wave input                                                |       |                    |           |      |

| High Performance Mode                                           |                                                                                  |       | -120               |           | dB   |

| Low Power Mode                                                  |                                                                                  |       | -119               |           | dB   |

| Spurious-Free Dynamic<br>Range <sup>5</sup> (SFDR)              | 1 kHz, –0.5 dBFS, sine wave input                                                |       |                    |           |      |

| High Performance Mode                                           |                                                                                  |       | 125                |           | dBc  |

| Low Power Mode                                                  |                                                                                  |       | 125                |           | dBc  |

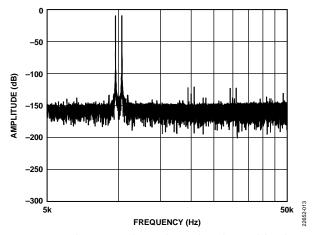

| INTERMODULATION                                                 | With input tone at 9.7 kHz and 10.3 kHz                                          |       |                    |           |      |

| DISTORTION (IMD)                                                | Second-order                                                                     |       | -122               |           | dB   |

|                                                                 | Third-order                                                                      |       | -125               |           | dB   |

| Parameter                                                        | Test Conditions/Comments                                                                                    | Min                  | Тур                | Max        | Unit          |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------|--------------------|------------|---------------|

| ACCURACY                                                         |                                                                                                             |                      |                    |            |               |

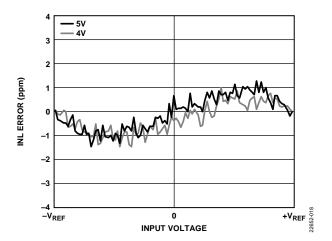

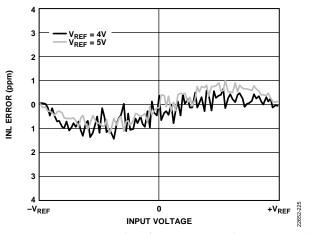

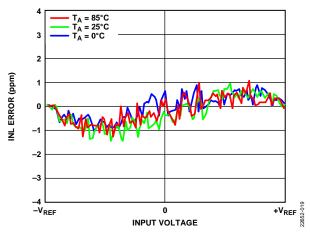

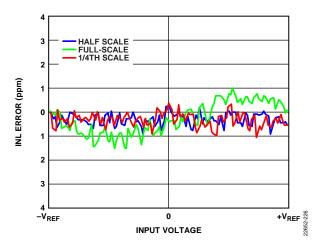

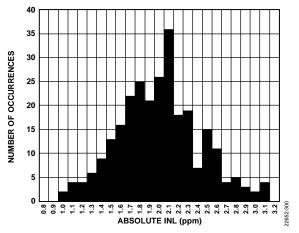

| Integral Nonlinearity (INL)                                      | End point method                                                                                            |                      |                    |            |               |

|                                                                  | High performance mode                                                                                       |                      | ±2                 |            | ppm of<br>FSR |

|                                                                  | Low power mode                                                                                              |                      | ±2                 |            | ppm of        |

|                                                                  |                                                                                                             |                      |                    |            | FSR           |

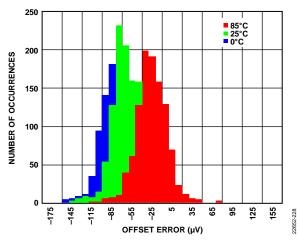

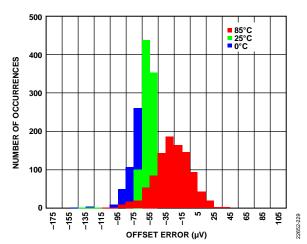

| Offset Error <sup>6</sup>                                        | High performance mode                                                                                       |                      | ±100               | ±700       | μV            |

| 200                                                              | Low power mode                                                                                              |                      | ±100               | ±700       | μV            |

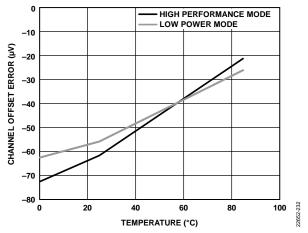

| Offset Error Drift                                               | High performance mode                                                                                       |                      | 0.7                | 3.7        | μV/°C         |

|                                                                  | Low power mode                                                                                              |                      | 0.8                | 2.7        | μV/°C         |

| Gain Error <sup>6</sup>                                          | High performance mode, master mode                                                                          |                      | 350                | 646        | ppm of<br>FSR |

|                                                                  | Low power mode, master mode                                                                                 |                      | 150                | 390        | ppm of<br>FSR |

| Gain Drift                                                       |                                                                                                             |                      | 2                  | 5.4        | ppm/°C        |

| Voltage Noise                                                    | 0.1 Hz to 10 Hz                                                                                             |                      | 1.01               |            | μV p-p        |

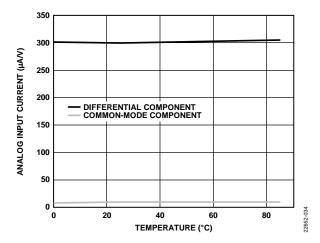

| ANALOG INPUTS                                                    |                                                                                                             |                      |                    |            | <u> </u>      |

| Differential Input Voltage<br>Range (V <sub>IN</sub> )           | -V <sub>REF</sub> is the negative reference voltage and +V <sub>REF</sub> is the positive reference voltage | -V <sub>REF</sub>    |                    | $+V_{REF}$ | V             |

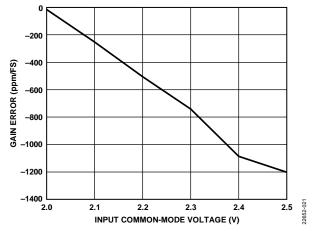

| Input Common-Mode<br>Voltage Range (V <sub>CM</sub> )            | is the positive reference voltage                                                                           |                      | $V_{\text{REF}}/2$ | AVDD5/2    | V             |

| Input Current                                                    |                                                                                                             |                      | 317                |            | μA/V          |

| Input Current Drift                                              |                                                                                                             |                      | 8.3                |            | nA/V/°C       |

| Differential Input                                               |                                                                                                             |                      | 6.25               |            | kΩ            |

| Resistance                                                       |                                                                                                             |                      | 0.23               |            | 1/22          |

| /CM PIN                                                          |                                                                                                             |                      |                    |            |               |

| Output Voltage                                                   |                                                                                                             | V <sub>REF</sub> /20 |                    | AVDD5/2    | V             |

| Load Regulation (ΔV <sub>OUT</sub> /ΔI <sub>L</sub> )            |                                                                                                             |                      | 313                |            | μV/mA         |

| Voltage Regulation<br>(ΔV <sub>OUT</sub> /ΔV <sub>AVDD5V</sub> ) |                                                                                                             |                      | 993                |            | μV/V          |

| Short-Circuit Current                                            |                                                                                                             |                      | 45                 |            | mA            |

| Loading Capacitance                                              |                                                                                                             |                      | 45                 | 200        | pF            |

| Additive Voltage Noise                                           |                                                                                                             |                      | 70                 | 200        | nV/√Hz        |

| Density                                                          |                                                                                                             |                      | , ,                |            | 1107 1112     |

| EXTERNAL REFERENCE                                               |                                                                                                             |                      |                    |            |               |

| REFIN Voltage (V <sub>REF</sub> )                                | REFIN to REFGND high performance mode                                                                       |                      | 4.096 or 5         |            | V             |

|                                                                  | REFIN to REFGND low power mode                                                                              |                      | 4.096 or 5         |            | V             |

| REFIN Current                                                    | All channels on, high performance mode                                                                      |                      | 5.85               |            | mA            |

|                                                                  | All channels on, low power mode                                                                             |                      | 3.22               |            | mA            |

|                                                                  | One channel on, high performance mode                                                                       |                      | 1.53               |            | mA            |

|                                                                  | One channel on, low power mode                                                                              |                      | 0.9                |            | mA            |

|                                                                  | REFIN off                                                                                                   |                      | 0.5                |            | μΑ            |

| REFIN Current Drift                                              |                                                                                                             |                      | 40                 |            | nA/V/°C       |

| REFIN Resistance                                                 | All channels on                                                                                             |                      | 0.7                |            | kΩ            |

|                                                                  | One channel on                                                                                              |                      | 2.66               |            | kΩ            |

|                                                                  | All channels on, low power mode                                                                             |                      | 1.27               |            | kΩ            |

| MODULATOR MAGNITUDE                                              | One channel on, low power mode                                                                              |                      | 4.79               |            | kΩ            |

| RESPONSE                                                         |                                                                                                             |                      |                    |            |               |

| High Performance Mode                                            | At 100 kHz, ODR = 374 kSPS                                                                                  |                      | -0.0202            |            | dB            |

|                                                                  | At 20 kHz, ODR = 374 kSPS                                                                                   |                      | -0.0024            |            | dB            |

| Low Power Mode                                                   | At 50 kHz, ODR = 187 kSPS                                                                                   |                      | -0.0122            |            | dB            |

|                                                                  | At 20 kHz, ODR = 187 kSPS                                                                                   |                      | -0.00189           |            | dB            |

| Parameter                                   | Test Conditions/Comments                                 | Min | Тур              | Max      | Unit  |

|---------------------------------------------|----------------------------------------------------------|-----|------------------|----------|-------|

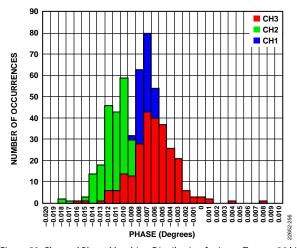

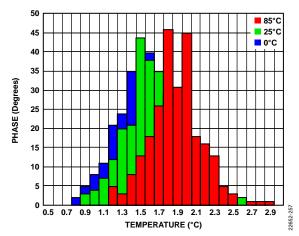

| SYNCHRONIZATION                             | At 20 kHz                                                |     |                  |          |       |

| Channel to Channel Phase                    |                                                          |     | 1.57             | 3.3      | ns    |

| Matching <sup>7</sup>                       |                                                          |     |                  |          | 10.0  |

| Channel to Channel<br>Phase Matching Drift  |                                                          |     | 4.17             |          | ps/°C |

| Device to Device Phase                      | ODR = 1496 kSPS                                          |     | 10               |          | ns    |

| Matching <sup>8</sup>                       |                                                          |     |                  |          |       |

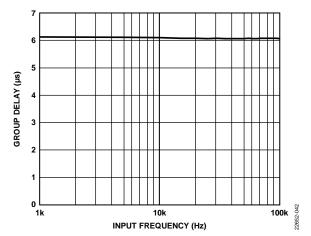

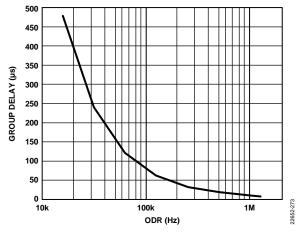

| DIGITAL FILTER RESPONSE                     |                                                          |     |                  |          |       |

| Low Ripple Wideband                         |                                                          |     |                  |          |       |

| Group Delay                                 |                                                          |     | 39.8/ODR         |          | sec   |

| Settling Time                               |                                                          |     | 79.6/ODR         |          | sec   |

| Pass-Band Ripple                            |                                                          |     | 32               |          | μdB   |

| Pass-Band Frequency                         |                                                          |     |                  |          |       |

| (f <sub>PASS</sub> )<br>Wideband 0.433 Hz×  | 122 udP page hand                                        |     | 0.4 × 000        |          | Hz    |

| ODR Filter                                  | ±32 µdB pass band                                        |     | 0.4 × ODR        |          | Hz    |

| ODITTILE                                    | -0.1 dB pass band                                        |     | 0.401 ×<br>ODR   |          | HZ    |

|                                             | -3 dB bandwidth                                          |     | 0.433×           |          | Hz    |

|                                             |                                                          |     | ODR              |          |       |

| Wideband 0.10825 Hz                         | ±32 μdB pass band                                        |     | $0.1 \times ODR$ |          | Hz    |

| × ODR Filter                                | -0.1 dB pass band                                        |     | 0.101 ×          |          | Hz    |

|                                             |                                                          |     | ODR              |          |       |

|                                             | -3 dB bandwidth                                          |     | 0.10825 ×        |          | Hz    |

| 6. 5. 15                                    |                                                          |     | ODR              |          |       |

| Stop Band Frequency<br>(f <sub>STOP</sub> ) |                                                          |     |                  |          |       |

| Wideband 0.433 Hz ×                         |                                                          |     | 0.499×           |          | Hz    |

| ODR Filter                                  |                                                          |     | ODR              |          | ' ' ' |

| Wideband 0.10825 Hz                         |                                                          |     | 0.2 × ODR        |          | Hz    |

| × ODR Filter                                |                                                          |     |                  |          |       |

| Stop Band Attenuation                       |                                                          |     | 110              |          | dB    |

| Sinc6                                       |                                                          |     |                  |          |       |

| Group Delay                                 |                                                          |     | 3.25/ODR         |          |       |

| Settling Time                               |                                                          |     | 6.5/ODR          |          |       |

| Pass Band                                   | -3 dB bandwidth                                          |     | 0.1861 ×         |          | sec   |

| <i>c</i> : 2                                |                                                          |     | ODR              |          |       |

| Sinc3                                       |                                                          |     | 4.75/000         |          |       |

| Group Delay (GD)                            | Latency                                                  |     | 1.75/ODR         |          | sec   |

| Settling Time                               | Complete settling  –3 dB bandwidth                       |     | 3.5/ODR          |          | sec   |

| Pass Band                                   | -3 dB bandwidth                                          |     | 0.2617 ×<br>ODR  |          | sec   |

| Attenuation                                 |                                                          |     | ODI              |          |       |

| At 50 Hz                                    | 50 SPS, 50 Hz ± 1 Hz                                     |     | 102              |          | dB    |

| At 60 Hz                                    | 60 SPS, 60 Hz ± 1 Hz                                     |     | 106              |          | dB    |

| At 50 Hz, 60 Hz                             | 10 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz                       |     | 102              |          | dB    |

| At 50 Hz, 60 Hz                             | 50 SPS, 50 Hz ± 1 Hz, 60 Hz ± 1 Hz, sinc3                |     | 67               |          | dB    |

| ,                                           | rejection, and 50 Hz/60 Hz rejection filter <sup>1</sup> |     |                  |          |       |

| COMBINED RESPONSE                           |                                                          |     |                  |          |       |

| Overall Group Delay                         | Sinc3 filter, slave gated mode                           |     |                  | 8/ODR    | sec   |

|                                             | Sinc6 filter, slave gated mode                           |     |                  | 10.5/ODR | sec   |

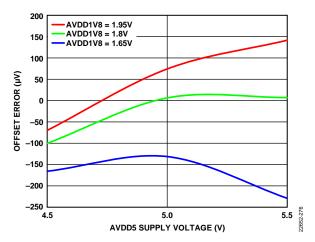

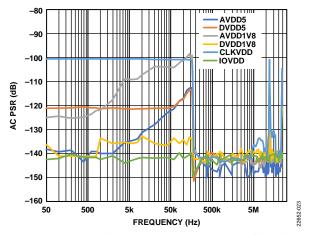

| REJECTION                                   | High performance mode                                    |     |                  |          |       |

| Power Supply Rejection                      |                                                          |     |                  |          |       |

| Ratio                                       |                                                          |     |                  |          |       |

| DC                                          |                                                          |     |                  |          |       |

| AVDD5                                       |                                                          |     | 101.8            |          | dB    |

| DVDD5                                       | Rev. 0   Page 6 of 86                                    |     | 80.4             |          | dB    |

Rev. 0 | Page 6 of 86

| Parameter                                            | Test Conditions/Comments                                                                        | Min            | Тур   | Max           | Unit |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------|-------|---------------|------|

| AVDD1V8                                              |                                                                                                 |                | 87.2  |               | dB   |

| DVDD1V8                                              |                                                                                                 |                | 100   |               | dB   |

| IOVDD                                                |                                                                                                 |                | 102   |               | dB   |

| LDOIN                                                |                                                                                                 |                | 116.6 |               | dB   |

| CLKVDD                                               |                                                                                                 |                | 61    |               | dB   |

| Power Supply                                         | 100 mV p-p, 1 MHz signal on supply with no                                                      |                |       |               |      |

| Rejection AC                                         | decoupling capacitor, value with respect to full-<br>scale input                                |                |       |               |      |

| AVDD5                                                |                                                                                                 |                | 101   |               | dB   |

| DVDD5                                                |                                                                                                 |                | 102   |               | dB   |

| AVDD1V8                                              |                                                                                                 |                | 104   |               | dB   |

| DVDD1V8                                              |                                                                                                 |                | 101   |               | dB   |

| IOVDD                                                |                                                                                                 |                | 114   |               | dB   |

| CLKVDD                                               |                                                                                                 |                | 103   |               | dB   |

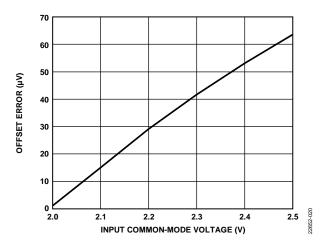

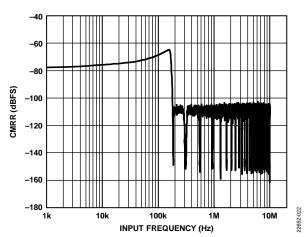

| Common-Mode Rejection<br>Ratio (CMRR)                | 100 mV p-p on V <sub>CM</sub> with no decoupling capacitor                                      |                |       |               |      |

| DC                                                   |                                                                                                 |                | 78.4  |               | dB   |

| AC                                                   | Up to 10 kHz                                                                                    |                | 74.5  |               | dB   |

| Crosstalk                                            | –0.5 dBFS, 1 kHz input on adjacent channels                                                     |                | 130.7 |               | dBFS |

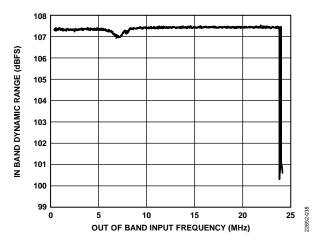

| Input Signal Alias Rejection<br>(AA <sub>REJ</sub> ) | , , , , , , , , , , , , , , , , , , , ,                                                         |                |       |               |      |

| High Performance Mode                                | -6 dBFS output of band tone from master clock<br>(MCLK) – 160 kHz to MCLK + 160 kHz, AA1 mode   |                | 85.4  |               | dB   |

|                                                      | -6 dBFS output of band tone from MCLK - 160 kHz<br>to MCLK + 160 kHz, Antialiasing 2 (AA2) mode |                | 102.5 |               | dB   |

| Low Power Mode                                       | -6 dBFS output of band tone from MCLK – 80 kHz to MCLK + 80 kHz, AA1 mode                       |                | 87.4  |               | dB   |

|                                                      | -6 dBFS output of band tone from MCLK – 80 kHz to MCLK + 80 kHz, AA2 mode                       |                | 97.2  |               | dB   |

| EXTERNAL CLOCK INPUT                                 |                                                                                                 |                |       |               |      |

| Frequency                                            |                                                                                                 | 47.9           | 48    | 48.1          | MHz  |

| Duty Cycle                                           |                                                                                                 | 40             | 50:50 | 60            | %    |

| Input Voltage High                                   |                                                                                                 | 0.65 × CLKVDD  |       |               | V    |

| Input Voltage Low                                    |                                                                                                 | 0.0077 02.7722 |       | 0.35 × CLKVDD | V    |

| Input Capacitance                                    |                                                                                                 |                | 10    | 0.55 × CERVED | pF   |

| CRYSTAL OSCILLATOR                                   |                                                                                                 |                | 10    |               | Pi   |

| Frequency                                            | ±100 ppm                                                                                        |                | 48    |               | MHz  |

| Start-Up Time                                        | _ 100 ββιτι                                                                                     |                | 4.4   |               | ms   |

| CLKSEL INPUT LOGIC                                   |                                                                                                 |                | 4.4   |               | 1115 |

|                                                      |                                                                                                 | 0.7101/00      |       |               | .,   |

| Input High Voltage (V <sub>INH</sub> )               |                                                                                                 | 0.7 × IOVDD    |       | 0.2 10)/00    | V    |

| Input Low Voltage (V <sub>INL</sub> )                |                                                                                                 |                |       | 0.3 × IOVDD   | ٧.   |

| Leakage Currents                                     |                                                                                                 | <b>-1</b>      |       | +1            | μΑ   |

| XCLKOUT PIN                                          |                                                                                                 |                |       |               |      |

| Output Frequency                                     |                                                                                                 |                | 48    |               | MHz  |

| Rise Time/Fall Time (20% to 80%)                     | 45 pF load                                                                                      |                | 0.85  |               | ps   |

| Duty Cycle                                           | External clock input duty cycle = 50:50                                                         |                | 53.8  |               | %    |

| Output Voltage High                                  | Source current (I <sub>SOURCE</sub> ) = 100 μA                                                  | CLKVDD – 0.2   |       |               | V    |

| Output Voltage Low                                   | Sink current (I <sub>SINK</sub> ) = 100 μA                                                      |                |       | 0.2           | V    |

| ODR PIN                                              |                                                                                                 |                |       |               |      |

| Output Frequency                                     |                                                                                                 | 0.01           |       | 1496          | kHz  |

| Output Rise Time/Fall<br>Time (20% to 80%)           | 45 pF load                                                                                      |                | 2.8   |               | ns   |

| Output Voltage High                                  | $I_{SOURCE} = 100 \mu A$                                                                        | IOVDD - 0.2    |       |               | V    |

| Parameter                                  | Test Conditions/Comments                                             | Min         | Тур   | Max                | Unit |

|--------------------------------------------|----------------------------------------------------------------------|-------------|-------|--------------------|------|

| Output Voltage Low                         | $I_{SINK} = 100 \mu A$                                               |             |       | 0.2                | ٧    |

| Input Frequency (f <sub>IN</sub> )         |                                                                      | 0.01        |       | 1496               | kHz  |

| V <sub>INH</sub>                           |                                                                      | 0.7 × IOVDD |       |                    | ٧    |

| $V_{INL}$                                  |                                                                      |             |       | $0.3 \times IOVDD$ | ٧    |

| Input Capacitance                          | Pin configured as input                                              |             | 10    |                    | pF   |

| DCLK PIN                                   |                                                                      |             |       |                    |      |

| Output Frequency                           |                                                                      | 2.93        |       | 48000              | kHz  |

| Output Rise Time/Fall<br>Time (20% to 80%) | 45 pF load                                                           |             | 2.8   |                    | ns   |

| Output Duty Cycle                          |                                                                      |             | 50:50 |                    | %    |

| Output Voltage High                        | $I_{SOURCE} = 100 \mu A$                                             | IOVDD - 0.2 |       |                    | V    |

| Output Voltage Low                         | $I_{SINK} = 100 \mu A$                                               |             |       | 0.2                | ٧    |

| $f_{IN}$                                   |                                                                      |             |       | 50,000             | kHz  |

| V <sub>INH</sub>                           |                                                                      | 0.7 × IOVDD |       |                    | ٧    |

| $V_{INL}$                                  |                                                                      |             |       | $0.3 \times IOVDD$ | ٧    |

| Input Capacitance                          | Pin configured as input                                              |             | 10    |                    | pF   |

| LOGIC INPUTS                               |                                                                      |             |       |                    |      |

| V <sub>INH</sub>                           |                                                                      | 0.7 × IOVDD |       |                    | ٧    |

| $V_{INL}$                                  |                                                                      |             |       | $0.2 \times IOVDD$ | ٧    |

| Leakage Currents                           |                                                                      | -10         |       | +10                | μΑ   |

| LOGIC OUTPUTS                              |                                                                      |             |       |                    |      |

| Output High Voltage (V <sub>OH</sub> )     | $I_{SOURCE} = 100 \mu A$                                             | IOVDD - 0.2 |       |                    | ٧    |

| Output Low Voltage (V <sub>OL</sub> )      | I <sub>SINK</sub> = 100 μA                                           |             |       | 0.2                | ٧    |

| INTEGRATED LOW DROPOUT                     |                                                                      |             |       |                    |      |

| (LDO) REGULATOR                            |                                                                      |             |       |                    |      |

| Output Voltage                             |                                                                      |             | 1.85  |                    | V    |

| Input Voltage                              |                                                                      | 2.6         |       | 5.5                | V    |

| POWER SUPPLY VOLTAGE                       |                                                                      |             |       |                    |      |

| AVDD5 to AGND5                             |                                                                      | 4.5         | 5     | 5.5                | ٧    |

| DVDD5 to DGND5                             |                                                                      | 4.5         | 5     | 5.5                | ٧    |

| AVDD5 to AGND5                             | $V_{REF} = 5 V$                                                      | 4.7         | 5     | 5.5                | V    |

| DVDD5 to DGND5                             | $V_{REF} = 5 V$                                                      | 4.7         | 5     | 5.5                | V    |

| DVDD1V8 to DGND                            |                                                                      | 1.65        | 1.8   | 1.95               | ٧    |

| AVDD1V8 to AGND1V8                         |                                                                      | 1.65        | 1.8   | 1.95               | V    |

| AVDD1V8 to AGND1V8                         | $V_{REF} = 5 V$                                                      | 1.8         | 1.85  | 1.95               | V    |

| DVDD1V8 to DGND                            | $V_{REF} = 5 V$                                                      | 1.8         | 1.85  | 1.95               | V    |

| IOVDD to IOGND                             |                                                                      | 1.65        | 1.8   | 1.95               | ٧    |

| CLKVDD to CLKGND                           |                                                                      | 1.65        | 1.8   | 1.95               | ٧    |

| CLKVDD to CLKGND                           | $V_{REF} = 5 V$                                                      | 1.8         | 1.85  | 1.95               | V    |

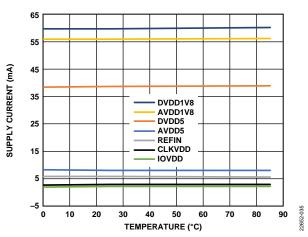

| POWER SUPPLY CURRENT                       | 4 channels active, internal LDO regulator bypassed, XCLKOUT disabled |             |       |                    |      |

| High Performance Mode                      | ODR = 374 kSPS                                                       |             |       |                    |      |

| AVDD5                                      |                                                                      |             | 8.2   | 10.3               | mA   |

| DVDD5                                      |                                                                      |             | 38.6  | 44.8               | mA   |

| AVDD1V8                                    |                                                                      |             | 56    | 73.9               | mA   |

| DVDD1V8                                    | Sinc3 filter, ODR = 1496 kSPS                                        |             | 60    | 70.6               | mA   |

|                                            | Sinc6 filter, ODR = 1496 kSPS                                        |             | 60.9  | 71.8               | mA   |

|                                            | Wideband 0.433 Hz × ODR filter                                       |             | 90    | 105.5              | mA   |

| IOVDD                                      |                                                                      |             | 2.25  | 3.17               | mA   |

| CLKVDD                                     |                                                                      |             | 2.8   | 3.53               | mA   |

| Low Power Mode                             | ODR = 187 kSPS                                                       |             |       |                    |      |

| AVDD5                                      |                                                                      |             | 8.2   | 10.3               | mA   |

| DVDD5                                      |                                                                      |             | 14.1  | 16.5               | mA   |

| AVDD1V8                                    |                                                                      |             | 51    | 69                 | mA   |

Rev. 0 | Page 8 of 86

| Parameter                  | Test Conditions/Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min | Тур  | Max  | Unit |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|

| DVDD1V8                    | Sinc3 filter, ODR = 1496 kSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 30.6 | 36   | mA   |

|                            | Sinc6 filter, ODR = 1496 kSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 38.5 | 45.2 | mA   |

|                            | Wideband 0.433 Hz × ODR filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     | 48.5 | 56.8 | mA   |

| IOVDD                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 1.27 | 1.7  | mA   |

| CLKVDD                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     | 1.89 | 2.3  | mA   |

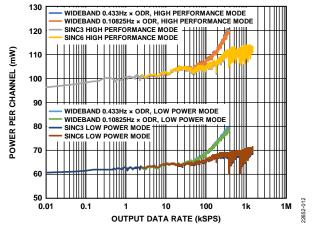

| TOTAL POWER<br>CONSUMPTION | External LDO mode: AVDD5 = DVDD5 = 5 V, AVDD1V8 = DVDD1V8 = CLKVDD = IOVDD = LDOIN = 1.8 V, internal LDO regulator bypassed, XCLKOUT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |      |      |      |

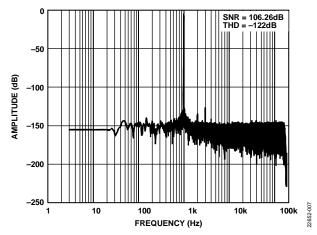

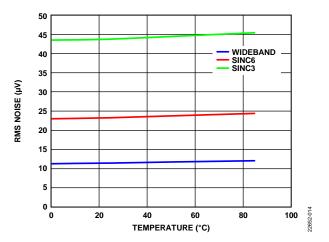

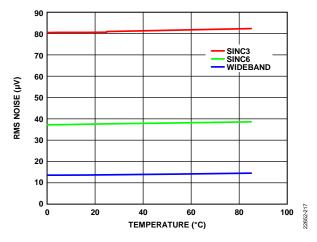

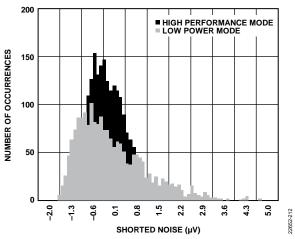

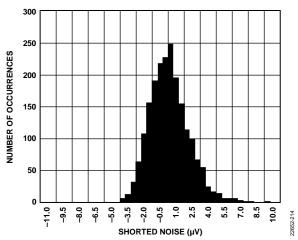

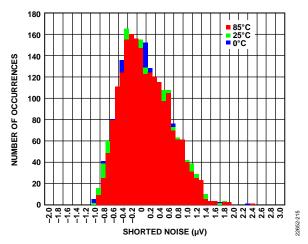

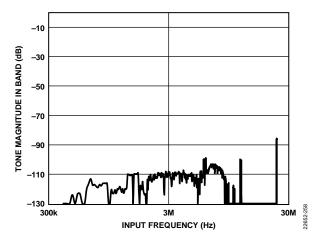

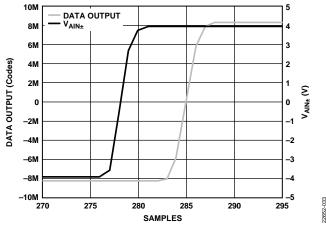

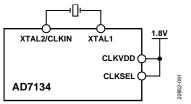

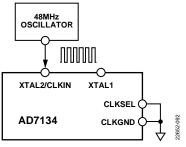

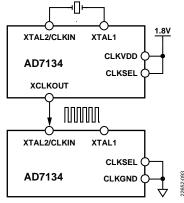

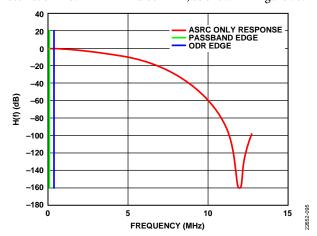

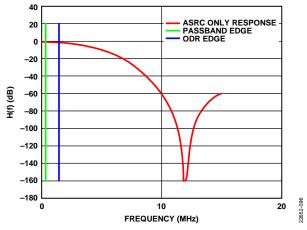

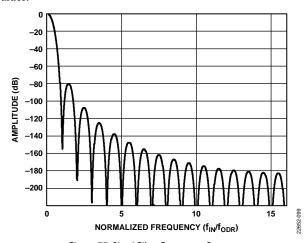

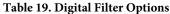

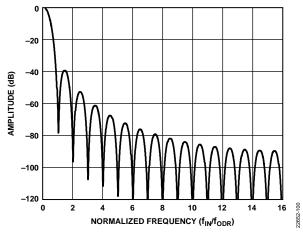

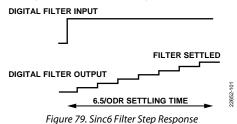

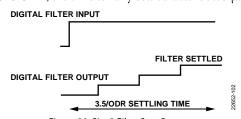

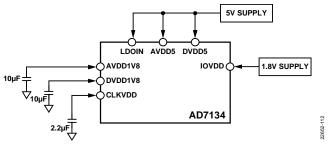

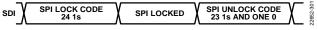

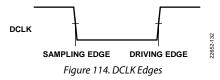

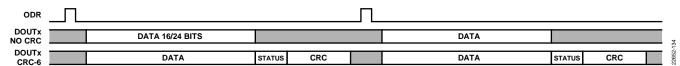

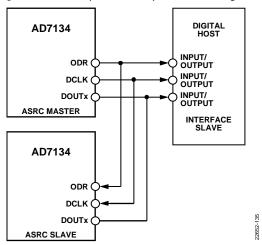

| High Performance Mode      | $ODR = 374$ kSPS, wideband 0.433 Hz $\times$ ODR filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |      |      |